## **ULTRASONIC-SENSOR SIGNAL CONDITIONER**

Check for Samples: PGA450-Q1

#### **FEATURES**

- Dual NMOS Low-Side Drivers

- Configurable Burst Generator

- Low-Noise Amplifier

- 12-Bit SAR ADC

- · Configurable Digital Band-Pass Filter

- Digital Signal Envelope Detect

- On-Chip 8-Bit Microprocessor

- LIN 2.1 Physical Interface and Protocol

- Watchdog Timer

- Four-Wire SPI for Testability / Programming

- 8K Bytes OTP

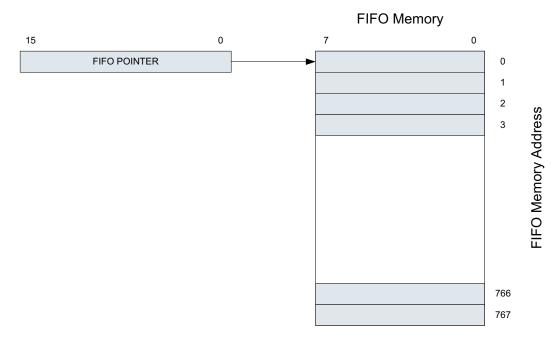

- 768 Bytes of FIFO RAM

- 256 Bytes Scratchpad RAM

- 8K Bytes of Development RAM

- 32 Bytes of EEPROM for Application

#### **APPLICATIONS**

- Automotive Park Distance

- Blind Spot Detection

- Object Detection Applications

#### DESCRIPTION

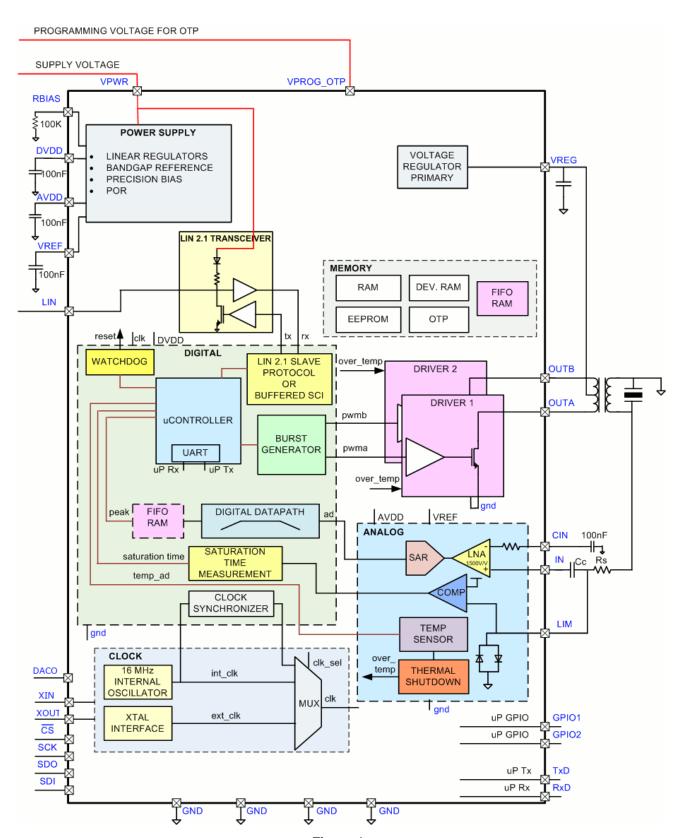

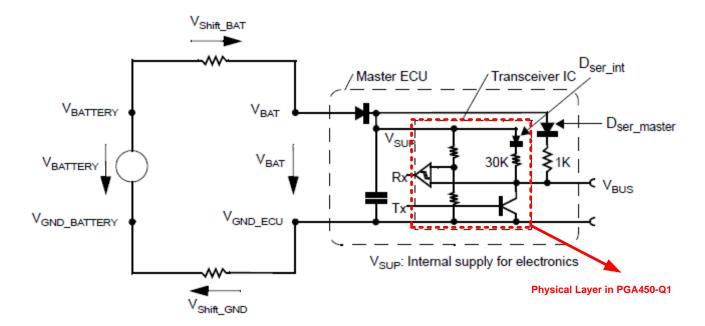

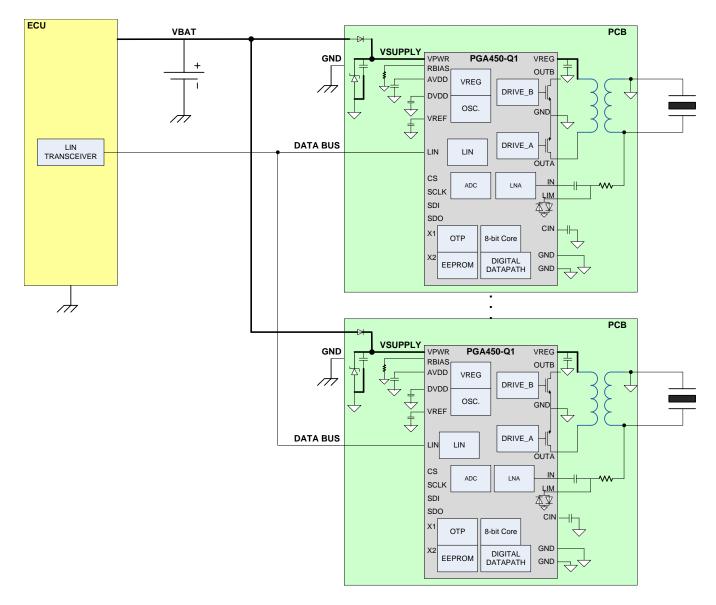

The PGA450-Q1 is a fully integrated interface device for ultrasonic transducers used in automotive park distance or object detection applications. It incorporates these system blocks: voltage regulators, a 12-bit SAR ADC, an 8-bit microcontroller, a digital band-pass filter, a DAC, dual NMOS low-side drivers, a low-noise amplifier, an oscillator, and a LIN 2.1 physical interface and protocol for interfacing.

The PGA450-Q1 possesses an 8-bit microcontroller and OTP memory for program storage for processing the echo signal and calculating the distance between the transducer and the object. This data is transmitted through the LIN 2.1 communication protocol. The LIN 2.1 physical layer is slave-only and does not implement the LIN wake-up feature. All other LIN 2.1 features can be implemented in software.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

**Table 1. TERMINAL FUNCTIONS**

| PIN NO.       | PIN NAME     | DESCRIPTION                         |

|---------------|--------------|-------------------------------------|

| 1             | VPWR         | Supply voltage                      |

| 2             | VREG         | Regulated voltage for transducer    |

| 3             | LIN          | LIN communication bus               |

| 4, 15, 18, 24 | GND          | Ground                              |

| 5             | DVDD         | Regulated voltage for digital core  |

| 6             | XIN          | Crystal input                       |

| 7             | XOUT         | Crystal out                         |

| 8, 9          | GPIO1, GPIO2 | General-purpose I/O 1 and 2         |

| 10            | RxD          | 8051W UART Rx (Port 3_0)            |

| 11            | TxD          | 8051W UART Tx (Port 3_1)            |

| 12            | CIN          | Input capacitor                     |

| 13            | IN           | Transducer receive input            |

| 14            | LIM          | Transducer receive limit            |

| 16            | DACO         | DAC output                          |

| 17            | RBIAS        | Bias resistor (100 kΩ to ground)    |

| 19            | CS           | SPI chip select                     |

| 20            | SCLK         | SPI clock                           |

| 21            | SDI          | SPI slave data in                   |

| 22            | SDO          | SPI slave data out                  |

| 23            | OUTB         | Transducer drive output B           |

| 25            | OUTA         | Transducer drive output A           |

| 26            | VPROG_OTP    | OTP programming voltage             |

| 27            | VREF         | Reference voltage for A/D converter |

| 28            | AVDD         | Regulated voltage for analog        |

#### **ELECTRICAL SPECIFICATIONS**

#### ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                                                                                 | CONDITIONS      | MIN  | MAX | UNIT |

|-------------------|-------------------------------------------------------------------------------------------|-----------------|------|-----|------|

| VPWR              | Power-supply voltage                                                                      |                 | -0.3 | 40  | V    |

| VREG              | Voltage on VREG, VPROG_OTP pin                                                            |                 | -0.3 | 10  | V    |

| VLIN              | Voltage on LIN                                                                            |                 | -27  | 40  | V    |

| VBIAS             | Voltage on RBIAS, CIN, IN                                                                 | Dalatina ta CND | -0.3 | 3   | V    |

| VDVDD             | Voltage on DVDD, XIN, XOUT                                                                | Relative to GND | -0.3 | 2   | V    |

| VOUT              | Voltage on OUTA, OUTB                                                                     |                 | -0.3 | 40  | V    |

| VLIM              | Voltage on LIM                                                                            |                 | -1.5 | 1.5 | V    |

| VMAX              | Voltage on all other pins                                                                 |                 | -0.3 | 6   | V    |

| IFET              | Low-side FET current                                                                      |                 |      | 1.5 | Α    |

|                   | ESD – HBM on all pins                                                                     |                 |      | 2   | kV   |

|                   | ESD – HBM on LIN, per IEC61000-4-2:1995 specification, contact with no external capacitor | AEC-Q100-002    |      | 8   | kV   |

|                   | ESD – CDM all pins                                                                        | AEC 0400 044    |      | 500 | V    |

|                   | ESD – CDM corner pins                                                                     | AEC-Q100-011    |      | 750 | V    |

| T <sub>Jmax</sub> | Maximum operating junction temperature                                                    |                 | -40  | 150 | °C   |

| T <sub>stg</sub>  | Storage temperature                                                                       |                 | -40  | 125 | °C   |

<sup>(1)</sup> Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" are not implied. Exposure to Absolute-Maximum-Rated conditions for extended periods may affect device reliability.

## THERMAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                                 | TYP  | UNIT |

|------------------|-------------------------------------------|------|------|

| R <sub>θJA</sub> | Junction-to-ambient thermal resistance    | 68.7 | °C/W |

| R <sub>0JC</sub> | Junction-to-case (top) thermal resistance | 11.6 | °C/W |

| R <sub>0JB</sub> | Junction-to-board thermal resistance      | 27.6 | °C/W |

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                   | CONDITIONS                                                                                | MIN | TYP | MAX | UNIT |

|---------------------|---------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| VPWR                | Power-supply voltage                        |                                                                                           | 7   |     | 18  | V    |

|                     |                                             | Power up, T <sub>A</sub> = 105°C                                                          |     |     | 50  | mA   |

| IPWR                | Power-supply current                        | Active mode <sup>(1)</sup> temperature sensor off,<br>T <sub>A</sub> = 105°C, VPWR = 18 V |     |     | 15  | mA   |

|                     |                                             | Quiet mode <sup>(2)</sup> , T <sub>A</sub> = 105°C, VPWR = 18<br>V                        |     |     | 7.5 | mA   |

| IPWR <sub>AVG</sub> | Average power-supply current <sup>(3)</sup> |                                                                                           |     |     | 10  | mA   |

| T <sub>A</sub>      | Operating ambient temperature               |                                                                                           | -40 |     | 105 | °C   |

| C <sub>VREG</sub>   | Capacitance on VREG pin                     |                                                                                           | 10  |     | 470 | μF   |

| C <sub>VPWR</sub>   | Capacitance on VPWR pin <sup>(4)</sup>      |                                                                                           | 47  |     | 100 | μF   |

| C <sub>ESR</sub>    | ESR of capacitor on VREG pin                |                                                                                           |     | 2   |     | Ω    |

<sup>(1)</sup> The entire device is active.

LNA, A/D, digital data path, and OUTA/B are OFF. Microprocessor and LIN are still active. Add 100 mA to these currents if capacitor on

The average current is defined as:  $I_{pwr}(Average) = 0.3I_{active} + 0.7I_{quiet}$ The capacitor value must allow a discharge rate on VPWR to be 1 V/ms.

## FLECTRICAL CHARACTERISTICS

|                        | PARAMETER                                              |                   | CONDITIONS                                                                                            | MIN         | TYP  | MAX  | UNIT     |

|------------------------|--------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|-------------|------|------|----------|

| POWER SUPP             | PLY                                                    | •                 |                                                                                                       |             |      |      |          |

| VPWR <sub>POR</sub>    | VPWR voltage for POR to occur                          | POR is de         | easserted                                                                                             | 3           |      | 4.2  | V        |

| V <sub>AVDD</sub>      | AVDD pin voltage                                       | IAVDD =           | 5 mA                                                                                                  | 4.75        | 5    | 5.25 | V        |

| $I_{AVDD}$             | AVDD pin load current                                  |                   |                                                                                                       |             |      | 5    | mA       |

| $V_{DVDD}$             | DVDD pin voltage                                       |                   |                                                                                                       |             | 1.8  |      | V        |

| VREF                   | VREF pin voltage                                       |                   |                                                                                                       |             | 3    |      | V        |

| t <sub>PU</sub>        | Power-up time – AVDD and DVDD reach regulation levels. | VPWR = regulation | 7 V to 18 V, VREG is not in                                                                           |             |      | 10   | ms       |

| VREG                   |                                                        | 1                 |                                                                                                       |             |      |      |          |

| VREG <sub>TOL</sub>    | Transducer primary voltage tolerance                   | IREG =<br>100 μA  | VPWR = 7V<br>VREG_SEL = 0_XXX for 4.7<br>V-5.4 V<br>VPWR = 10V<br>VREG_SEL = 1_XXX for 7.7<br>V-8.4 V |             | ±100 |      | mV       |

| VREG <sub>CHARGE</sub> | Transducer voltage droop while charging                | IREG = 1          | 00 mA, below VREG_SEL setting                                                                         |             | 500  |      | mV       |

| VREG <sub>READY</sub>  | VREG_READY threshold                                   | Below VR          | EG_SEL setting                                                                                        |             | 250  |      | <b>-</b> |

|                        | VDFO autout august                                     | VPWR >            | VREG_SEL + 2.5 V                                                                                      | 90          | 100  | 110  | mA       |

| I <sub>VREG</sub>      | VREG output current                                    | VPWR >            | VREG_SEL + 2 V                                                                                        | 100         |      |      | μA       |

| VREG <sub>I_S2G</sub>  | VREG short-to-ground protection current                | VPWR =            | 16 V, T <sub>A</sub> = 105 °C, no burst                                                               |             |      | 110  | mA       |

| CLOCK                  |                                                        |                   |                                                                                                       |             |      |      |          |

| Fosc                   | Internal oscillator frequency                          | 25°C              |                                                                                                       | 15.8        | 16   | 16.2 | MHz      |

| F <sub>DUTY</sub>      | Internal oscillator duty cycle                         |                   |                                                                                                       |             | 50   |      | %        |

|                        | Internal oscillator frequency                          | Before LI         | N sync                                                                                                | -4          |      | 4    | %        |

|                        | accuracy                                               | LIN baud          | rate = 19.2 kBPS, after LIN sync                                                                      | -0.5        |      | 0.5  | %        |

|                        | IVE MOSFETs                                            |                   | A T 405.00                                                                                            |             |      | 4.0  |          |

| r <sub>ds(on)</sub>    | FET ON resistance                                      |                   | 0 mA, T <sub>A</sub> = 105 °C                                                                         |             |      | 1.2  | Ω        |

| I <sub>PULSE</sub>     | Drain pulse current                                    | 50 kHz            | / L 40 ··· A                                                                                          | 40          |      | 1.5  | A<br>V   |

|                        | Drive clamping voltage                                 | vgs = 0 v         | $I_{dd} = 10 \text{ mA}$                                                                              | 40          |      |      |          |

| 1 0 1 1 1 1 1 1 1      | Leakage current                                        |                   |                                                                                                       |             |      | 5    | μA       |

| LOW NOISE A            | MPLIFIER                                               | 1 N/A - O A /     | N W Ol-OO                                                                                             | 4000        | 4750 | 1000 |          |

|                        |                                                        |                   | N setting = 0b00                                                                                      | 1680        | 1750 | 1820 |          |

| A <sub>V</sub>         | Gain                                                   |                   | N setting = 0b01                                                                                      | 892         | 930  | 968  | V/V      |

|                        |                                                        |                   | N Setting = 0b10                                                                                      | 496         | 517  | 538  |          |

| D                      | Innut impedance                                        |                   | N Setting = 0b11                                                                                      | 99          | 104  | 109  | 1.0      |

| R <sub>IN</sub>        | Input impedance Clamp voltage                          | 40 kHz            |                                                                                                       | 100<br>–1.5 |      | 1 F  | kΩ<br>V  |

| l                      | Input current limit                                    |                   |                                                                                                       | -1.5        |      | 200  | mA       |

| I <sub>LIM</sub>       | Noise (input-referred of the                           | IN pip – (        | CND T = 105 °C contor                                                                                 |             |      | 200  | IIIA     |

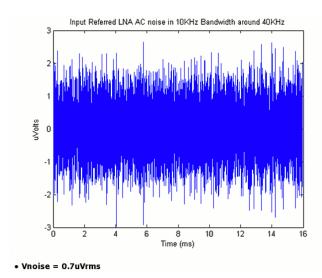

|                        | signal chain)                                          | frequency         | GND, T <sub>A</sub> = 105 °C, center<br>y = 40 kHz, Bandwidth = 10 kHz                                |             | 0.7  |      | μVrms    |

| 40 1.1/ 4/5 0 = 1      | Input-referred PSRR                                    | VPWR =            | 7 V, LNA gain setting = 0b00                                                                          |             | 93   |      | dB       |

| 12-bit A/D CO          |                                                        |                   |                                                                                                       |             |      |      |          |

| V <sub>ADCREF</sub>    | Input voltage range                                    |                   |                                                                                                       | 0           |      | 3    | V        |

|                        | Conversion time                                        | 0001              | 20/ 1                                                                                                 |             | 1    |      | μs       |

|                        | DNL                                                    |                   | 0% input range                                                                                        |             | 2.5  |      | LSB      |

|                        | INL                                                    |                   | 0% input range, best-fit curve                                                                        |             | 4    |      | LSB      |

|                        | Gain                                                   | Best-fit cu       | ırve                                                                                                  | 1373        | 1378 | 1383 | LSB/V    |

## **ELECTRICAL CHARACTERISTICS (continued)**

|                       | PARAMETER                              | CONDITIONS                                                                                                    | MIN        | TYP   | MAX   | UNIT          |

|-----------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------|------------|-------|-------|---------------|

|                       | Offset                                 | Best-fit curve                                                                                                |            | -15   |       | LSB           |

| 8-bit D/A CO          | NVERTER                                |                                                                                                               |            |       |       | ·             |

| V <sub>DAC_MAX</sub>  | Output range                           |                                                                                                               | 0.133      |       | 1.125 | V             |

|                       | Gain                                   |                                                                                                               |            | 3.9   |       | mV/Code       |

|                       | Settling time                          | Code 0x00 to 0xFF step. Output is 90% of full scale. $R_{load}$ = $k\Omega$ to GND. $C_{load}$ = 10 pF to GND |            |       | 20    | μs            |

|                       | Offset voltage                         | Output when DAC code is 000h at $R_{load}$ = 100 k $\Omega$ to GND                                            |            | 0.133 |       | V             |

|                       | Full-scale voltage                     | Output when DAC code is 0xFF $R_{load}$ = 100 $k\Omega$ to GND                                                |            | 1.125 |       | V             |

| I <sub>DAC</sub>      | Output current                         | DAC Code = $0x00$<br>DAC Code = $0xFF$ , $R_{load} = 100 \text{ k}\Omega$                                     |            |       | 12.5  | μΑ            |

|                       | INL                                    |                                                                                                               | -2         |       | 2     | LSB           |

|                       | DNL                                    |                                                                                                               | -1         |       | 1     | LSB           |

|                       | Capacitance load                       |                                                                                                               |            | 10    |       | pF            |

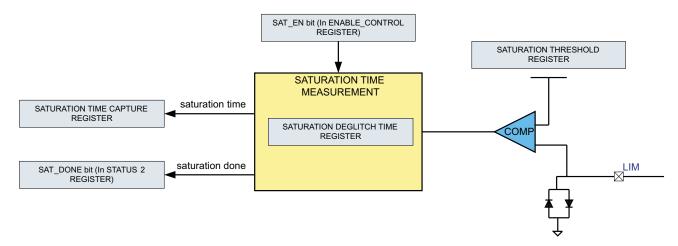

| TRANSDUCE             | ER SATURATION TIME                     |                                                                                                               |            |       |       | ·             |

|                       |                                        | SAT_SEL = 200 mV                                                                                              |            | 200   |       | mV            |

| M                     | Caturation throughold                  | SAT_SEL = 300 mV                                                                                              |            | 300   |       | mV            |

| V <sub>SAT_TH</sub>   | Saturation threshold                   | SAT_SEL = 400 mV                                                                                              |            | 400   |       | mV            |

|                       |                                        | SAT_SEL = 600 mV                                                                                              |            | 600   |       | mV            |

| TEMPERATU             | JRE SENSOR                             |                                                                                                               |            |       |       | •             |

|                       | Temperature sensor range               |                                                                                                               | -40        |       | 140   | °C            |

|                       | Temperature accuracy                   | -40°C to 105°C                                                                                                | <b>-</b> 5 |       | 5     | °C            |

|                       | Temperature sensor code                | 30°C                                                                                                          |            | 0     |       | LSB           |

|                       | Temperature sensor LSB                 |                                                                                                               |            | 1.75  |       | °C/LSB        |

| GPIOs, 8051           | UART Tx & Rx                           |                                                                                                               |            |       |       |               |

| VIH                   | — GPIO input mode, Rx                  | $R_{load} > 10 k\Omega$                                                                                       | 3.5        |       | 5.3   | V             |

| VIL                   | GF10 Input mode, KX                    |                                                                                                               | -0.3       |       | 1.5   | V             |

| R <sub>PULLUP</sub>   | Internal pullup on input               | Pullup is to AVDD                                                                                             |            | 100   |       | ΚΩ            |

| VOH                   | — GPIO strong-mode output, Tx          | $I_{OH} = 5 \text{ mA}$                                                                                       | 4          |       |       | V             |

| VOL                   | GFIO strong-mode output, 1x            | $I_{OL} = 5 \text{ mA}$                                                                                       |            |       | 0.8   | V             |

|                       | Total current on GPIO1 + GPIO2 +Tx pin | No load on AVDD pin                                                                                           |            |       | 5     | mA            |

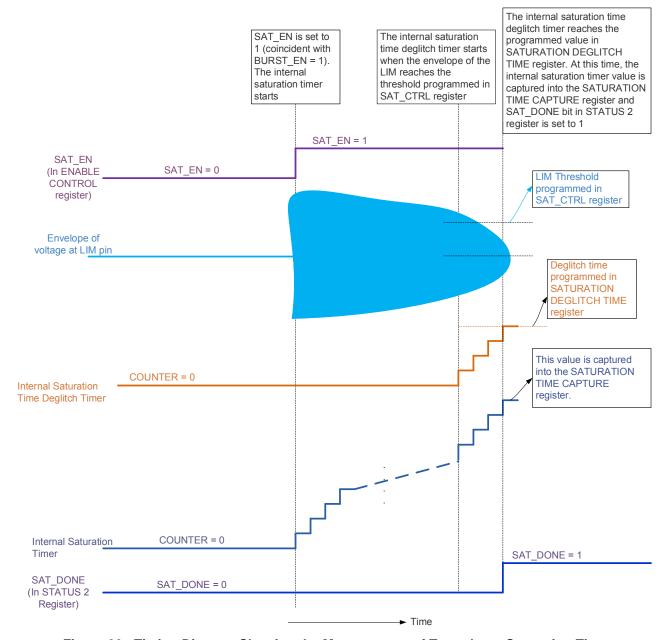

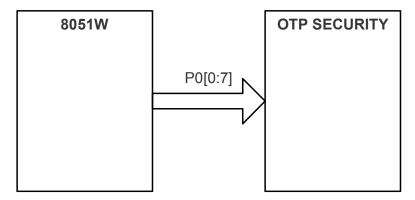

| 8051W WAR             | P CORE                                 |                                                                                                               |            |       |       |               |

| F <sub>CORE_CLK</sub> | Core frequency                         |                                                                                                               |            | 16    |       | MHz           |

|                       | Memory interface                       |                                                                                                               |            | 1     |       | Wait<br>State |

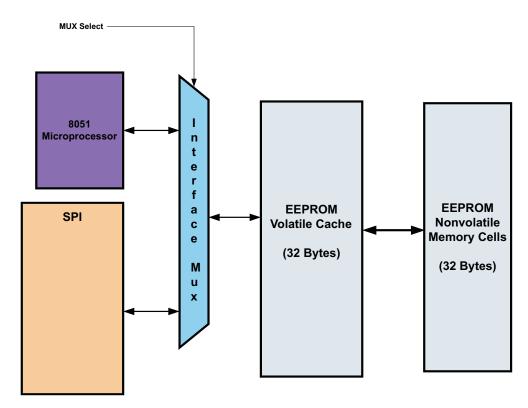

| MEMORY                |                                        |                                                                                                               |            |       |       |               |

|                       | OTP programming voltage                |                                                                                                               | 7.5        | 8     | 8.5   | V             |

|                       | OTP programming current                |                                                                                                               | 2          |       | 5     | mA            |

|                       | OTP programming time                   | 1 byte                                                                                                        | 100        |       |       | μs            |

|                       | OTP data retention years               | 105 °C                                                                                                        |            |       | 10    | Years         |

|                       | EEPROM R/W cycles                      |                                                                                                               |            |       | 1000  | Cycles        |

|                       | EEPROM data retention                  | 105 °C                                                                                                        |            |       | 10    | Years         |

|                       | EEPROM programming time                | 32 Bytes                                                                                                      |            |       | 70    | ms            |

| DIAGNOSTIC            | cs                                     |                                                                                                               |            |       |       |               |

| VPWR_OV               | VPWR overvoltage level                 |                                                                                                               | 25         | 28    | 32    | V             |

| AVDD_UV               | VPWR for AVDD undervoltage             |                                                                                                               |            | 5.6   |       | V             |

| AVDD_OC               | AVDD Overcurrent                       |                                                                                                               | 45         | 55    | 65    | mA            |

## **ELECTRICAL CHARACTERISTICS (continued)**

|          | PARAMETER                            | CONDITIONS                      | MIN | TYP | MAX | UNIT |

|----------|--------------------------------------|---------------------------------|-----|-----|-----|------|

| RBIAS_OC | RBIAS Overcurrent                    |                                 | 65  | 80  | 90  | uA   |

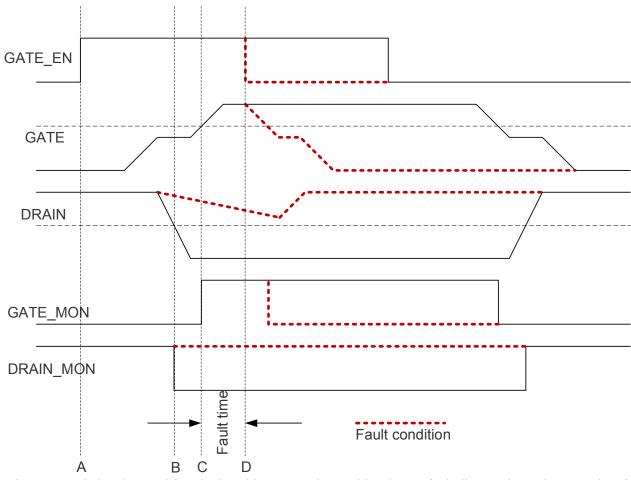

|          | Low-side driver A/B drain monitor    |                                 | 2.2 | 2.5 | 2.8 | V    |

|          | Low-side driver A/B monitor          |                                 | 2.2 | 2.5 | 2.8 | V    |

|          | Low-side driver A/B fault            | LS_FAULT_TIMER_2 = 1 µs setting |     | 1   |     | μs   |

|          | deglitch time                        | LS_FAULT_TIMER_2 = 2 µs setting |     | 2   |     | μs   |

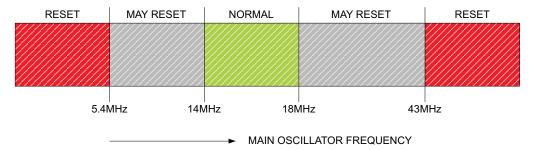

|          | Main oscillator underfrequency fault |                                 |     |     | 14  | MHz  |

|          | Main oscillator overfrequency fault  |                                 | 18  |     |     | MHz  |

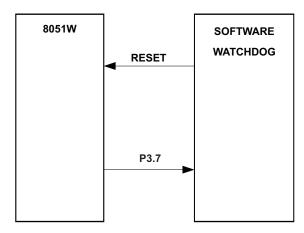

|          | Software watchdog time-out           |                                 |     | 250 |     | ms   |

|          | Over temperature shut-off protection |                                 | 150 |     | 200 | °C   |

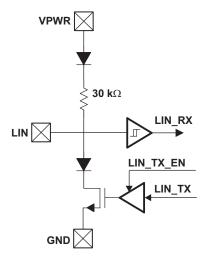

#### **ELECTRICAL CHARACTERISTICS – LIN 2.1 SLAVE/BUFFERED SCI**

| PARAMETER | CONDITION | MIN | TYP | MAX | UNIT |

|-----------|-----------|-----|-----|-----|------|

| LIN Mode: |           |     |     |     |      |

LIN 2.1 physical layer and LIN protocol (Section 2.1 of LIN 2.1) specification

Exceptions: No wake-up (Section 2.6.2 of LIN 2.1)

No transport layer in digital logic (Section 3 of LIN 2.1)

No node configuration and identification services in digital (Section 4 of LIN 2.1)

No diagnostic layer in digital logic (Section 5 of LIN 2.1)

The device is not certified for LIN compliance. Communication baud rate is fixed at 19.2 kBPS.

#### SCI Mode:

None

| NOHE                     |          |                                                                                                                                                                                                                                                                                                                                                                                               |       |     |       |           |

|--------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-----------|

| I <sub>BUS_LIM</sub>     | Param 12 | V <sub>BUS</sub> = 18 V                                                                                                                                                                                                                                                                                                                                                                       | 40    |     | 200   | mA        |

| I <sub>BUS_PAS_dom</sub> | Param 13 | Driver off, V <sub>BUS</sub> = 0V, V <sub>PWR</sub> = 12 V                                                                                                                                                                                                                                                                                                                                    | -1    |     |       | mA        |

| I <sub>BUS_PAS_rec</sub> | Param 14 | Driver off, 7 V < $V_{PWR}$ < 18 V, 8 V < $V_{BUS}$ < 18 V, $V_{BUS}$ > $V_{PWR}$                                                                                                                                                                                                                                                                                                             |       |     | 20    | μΑ        |

| I <sub>BUS_NO_GND</sub>  | Param 15 | GND <sub>Device</sub> = V <sub>PWR</sub> , 0 < V <sub>BUS</sub> < 18 V, V <sub>PWR</sub> = 12 V                                                                                                                                                                                                                                                                                               | -1    |     | 1     | mA        |

| I <sub>BUS_NO_BAT</sub>  | Param 16 | V <sub>PWR</sub> = GND, 0 < V <sub>BUS</sub> < 18 V                                                                                                                                                                                                                                                                                                                                           |       |     | 100   | μΑ        |

| $V_{BUSdom}$             | Param 17 | Receiver dominant state                                                                                                                                                                                                                                                                                                                                                                       |       |     | 0.4   | $V_{PWR}$ |

| V <sub>BUSrec</sub>      | Param 18 | Receiver recessive state                                                                                                                                                                                                                                                                                                                                                                      | 0.6   |     |       | $V_{PWR}$ |

| V <sub>BUS_CNT</sub>     | Param 19 | $V_{BUS\_CNT} = (V_{th\_dom} + V_{th\_rec})/2$                                                                                                                                                                                                                                                                                                                                                | 0.475 | 0.5 | 0.525 | $V_{PWR}$ |

| V <sub>HYS</sub>         | Param 20 | $V_{HYS} = V_{th\_rec} - V_{th\_dom}$                                                                                                                                                                                                                                                                                                                                                         |       |     | 0.175 | $V_{PWR}$ |

| R <sub>Slave</sub>       | Param 26 | Serial resistor                                                                                                                                                                                                                                                                                                                                                                               | 20    | 30  | 60    | ΚΩ        |

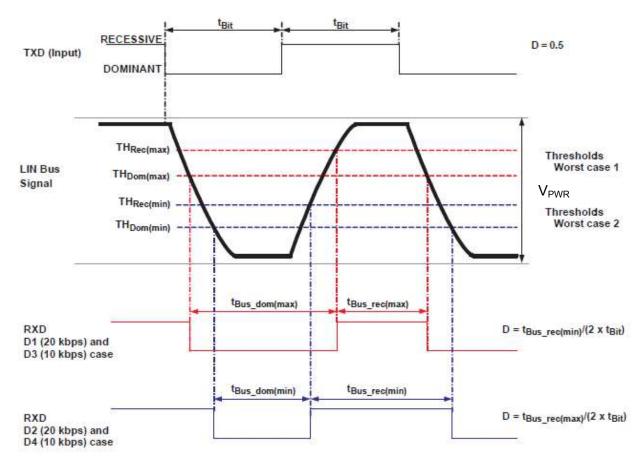

| D1                       | Param 27 | $\begin{array}{l} TH_{Rec(max)} = 0.744 \times V_{PWR}; \ TH_{Dom(max)} = 0.581 \times V_{PWR}; \\ V_{PWR} = 7 \ V18 \ V; \ t_{Bit} = 50 \ \mu s; \ D1 = t_{Bus\_rec(min)} / \ (2 \times t_{Bit}) \ Load_1; \\ C_{BUS} = 1 \ nF; \ R_{BUS} = 1 K\Omega \ Load_2; \\ C_{BUS} = 6.8 \ nF; \ R_{BUS} = 660 \ \Omega \ Load_3; \ C_{BUS} = 10 \ nF; \ R_{BUS} = 500 \ \Omega \end{array}$         | 0.396 |     |       |           |

| D2                       | Param 28 | $ \begin{array}{l} TH_{Rec(min)} = 0.522 \times V_{PWR}; \ TH_{Dom(min)} = 0.284 \times V_{PWR}; \\ V_{PWR} = 7.6 \ V18 \ V; \ t_{Bit} = 50 \ \mu s; \ D2 = t_{Bus\_rec(max)} / \ (2 \times t_{Bit}) \\ Load_1; \\ C_{BUS} = 1 \ nF; \ R_{BUS} = 1 \ k\Omega \ Load_2; \\ C_{BUS} = 6.8 \ nF; \ R_{BUS} = 660 \ \Omega \ Load_3; \ C_{BUS} = 10 \ nF; \ R_{BUS} = 500 \\ \Omega \end{array} $ |       |     | 0.581 |           |

| D3                       | Param 29 | $ \begin{array}{l} TH_{Rec(max)} = 0.778 \times V_{PWR}; \ TH_{Dom(max)} = 0.616 \times V_{PWR}; \ V_{PWR} = 7 \ V18 \ V; \\ t_{Bit} = 96 \ \mu s; \ D4 = t_{Bus\_rec(min)} \ / \ (2 \times t_{Bit}) \ Load_1; \ C_{BUS} = 1 \ nF; \\ R_{BUS} = 1 \ k\Omega \ Load_2; \\ C_{BUS} = 6.8 \ nF; \ R_{BUS} = 660 \ \Omega \ Load_3; \ C_{BUS} = 10 \ nF; \ R_{BUS} = 500 \\ \Omega \end{array} $  | 0.417 |     |       |           |

## **ELECTRICAL CHARACTERISTICS – LIN 2.1 SLAVE/BUFFERED SCI (continued)**

| PAI                 | RAMETER  | CONDITION                                                                                                                                                                                                                                                                                                                                                                                                      | MIN | TYP | MAX   | UNIT |

|---------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|------|

| D4                  | Param 30 | $ \begin{aligned} & TH_{Rec(min)} = 0.389 \times V_{PWR}; \ TH_{Dom(min)} = 0.251 \times V_{PWR}; \ V_{PWR} = \\ & 7.6 \ V18 \ V; \\ & t_{Bit} = 96 \ \mu s; \ D4 = t_{Bus\_rec(max)} \ / \ (2 \times t_{Bit}) \ Load_1; \ C_{BUS} = 1 \ nF; \\ & R_{BUS} = 1 \ k\Omega \ Load_2; \\ & C_{BUS} = 6.8 \ nF; \ R_{BUS} = 660 \ \Omega \ Load_3; \ C_{BUS} = 10 \ nF; \ R_{BUS} = 500 \\ & \Omega \end{aligned} $ |     |     | 0.590 |      |

| t <sub>rx_pd</sub>  | Param 31 | Propagation delay of receiver $R_{RXD} = 2.4 \text{ k}\Omega; C_{RXD} = 20 \text{ pF}$                                                                                                                                                                                                                                                                                                                         |     |     | 6     | μs   |

| t <sub>rx_sym</sub> | Param 32 | Symmetry of receiver propagation delay rising edge with respect to falling edge $R_{RXD} = 2.4 \ k\Omega; C_{RXD} = 20 \ pF$                                                                                                                                                                                                                                                                                   | -2  |     | 2     | μs   |

| C <sub>IN</sub>     |          | Input capacitance on LIN pin                                                                                                                                                                                                                                                                                                                                                                                   |     | 60  |       | pF   |

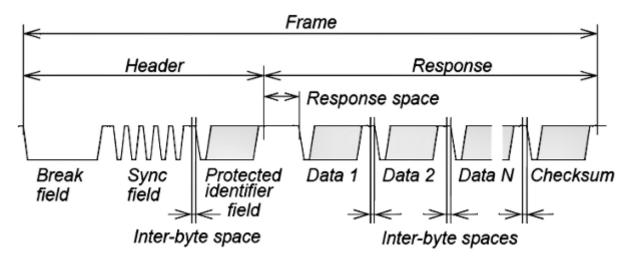

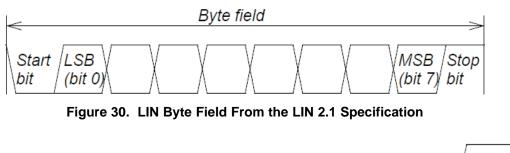

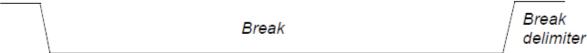

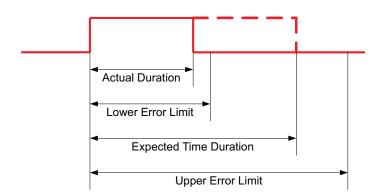

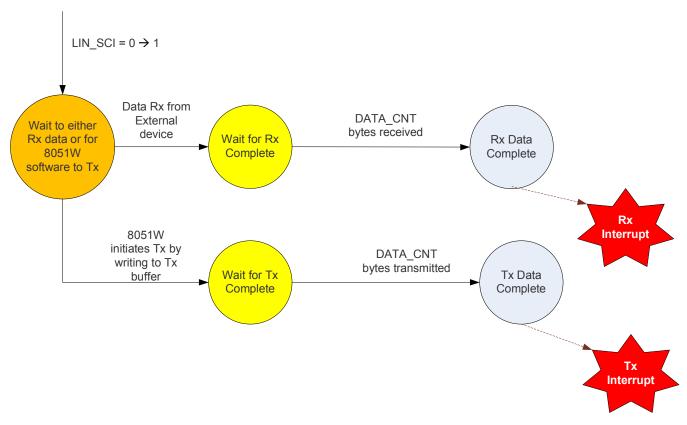

Figure 2 summarizes the LIN timing details.

Figure 2. LIN Timing Diagram

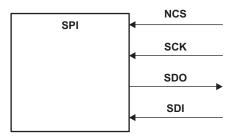

## **ELECTRICAL CHARACTERISTICS - SPI INTERFACE**

| PARAMETER                                                    | CONDITION | MIN | TYP | MAX | UNIT |

|--------------------------------------------------------------|-----------|-----|-----|-----|------|

| High-level voltage ( $\overline{\text{CS}}$ , SCK, SDI, SDO) |           | 3.5 |     |     | V    |

| Low-level voltage (CS, SCK, SSDO)                            | OI,       |     |     | 1.5 | V    |

| f <sub>SCK</sub> SPI frequency                               |           |     |     | 8   | MHz  |

Copyright © 2012, Texas Instruments Incorporated

## **ELECTRICAL CHARACTERISTICS – SPI INTERFACE (continued)**

|                     | PARAMETER                                                  | CONDITION               | MIN  | TYP | MAX | UNIT |

|---------------------|------------------------------------------------------------|-------------------------|------|-----|-----|------|

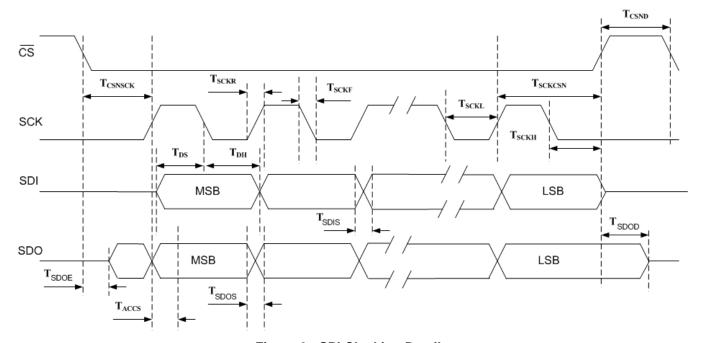

| tcssck              | CS low to first SCK rising edge                            |                         | 125  |     |     | ns   |

| t <sub>SCK</sub> CS | Last SCK rising edge to $\overline{\text{CS}}$ rising edge |                         | 125  |     |     | ns   |

| tcsD                | CS disable time                                            |                         | 375  |     |     | ns   |

| t <sub>DS</sub>     | SDI setup time                                             |                         | 25   |     |     | ns   |

| t <sub>DH</sub>     | SDI hold time                                              |                         | 25   |     |     | ns   |

| t <sub>SDIS</sub>   | SDI fall/rise time                                         |                         |      |     | 25  | ns   |

| t <sub>SCKR</sub>   | SCK rise time                                              |                         |      |     | 7   | ns   |

| t <sub>SCKF</sub>   | SCK fall time                                              |                         |      |     | 7   | ns   |

| t <sub>SCKH</sub>   | SCK high time                                              |                         | 62.5 |     |     | ns   |

| t <sub>SCKL</sub>   | SCK low time                                               |                         | 62.5 |     |     | ns   |

| t <sub>SDO</sub>    | SDO enable time                                            |                         |      |     | 25  | ns   |

| t <sub>ACCS</sub>   | SCK rising edge to SDO data valid                          |                         |      |     | 25  | ns   |

| t <sub>SDOD</sub>   | SDO disable time                                           |                         |      |     | 25  | ns   |

| t <sub>SDOS</sub>   | SDO rise/fall time                                         | C <sub>SDO</sub> = 10pF | 1    |     | 15  | ns   |

| C <sub>L(SDO)</sub> | Capacitive load for data output (SDO)                      |                         |      | 10  |     | pF   |

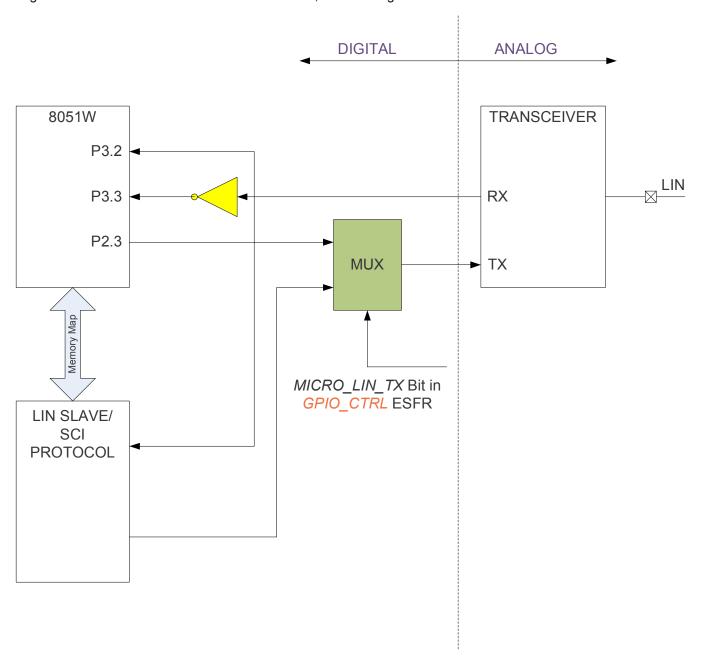

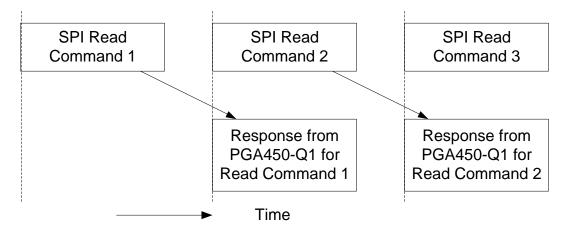

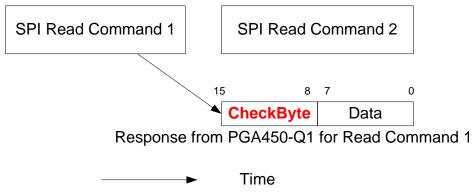

Figure 3 summarizes the SPI clocking details.

Figure 3. SPI Clocking Details

## **Typical Characteristics**

VPWR = 12 V, T<sub>A</sub> = 25°C

Figure 4. LNA Noise

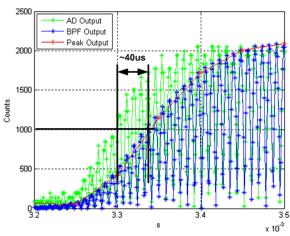

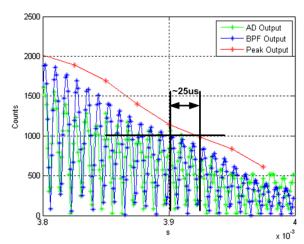

- BPF Center Frequency = 58KHz

- BPF Bandwidth = 7KHz

Figure 6. Data-Path Output, Downsample Rate = 40

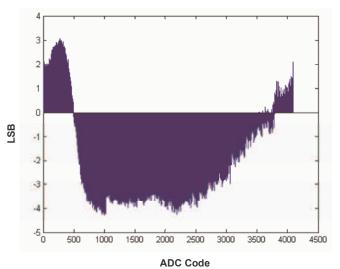

Figure 5. ADC INL

- BPF Center Frequency = 58KHz

- BPF Bandwidth = 7KHz

Figure 7. Data-Path Output, Downsample Rate = 25

### **Function Description**

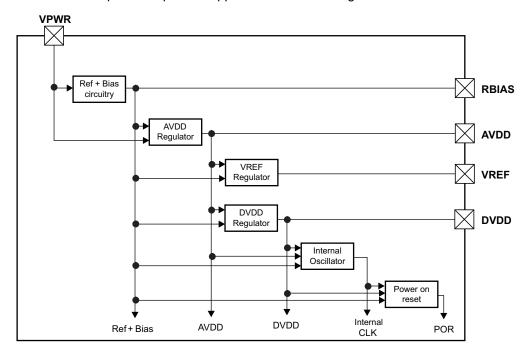

## **Power Supply Block**

PGA450-Q1 uses three internal regulators (AVDD, DVDD, and VREF) as supplies for all the internal circuits. The power-supply block also generates a precision voltage reference, current bias, and internal clock. The internal power-on-reset (POR) signal is released when the internal power supplies, voltage reference, current bias, and internal clock come into regulation.

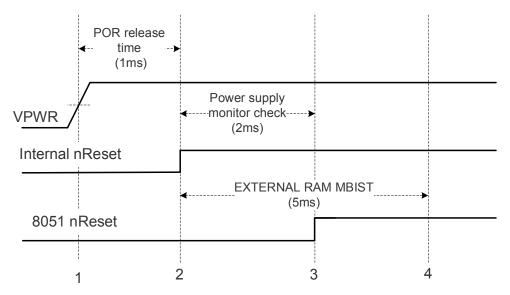

Figure 8 shows the relationships of the power supplies and the POR signal in the PGA450-Q1.

Figure 8. Power-Supply Block

The PGA450-Q1 begins to power up once a voltage is applied to the VPWR pin. A typical power-up diagram is shown in Figure 9. Power-up time is typically about 3 ms.

- 1. VPWR ramp reached POR level

- 2. Internal reset to the digital core is released and EXTERNAL RAM MBIST is initiated. SPI communication is available

- 3. 8051W Reset is deasserted. Software starts execution

- 4. EXTERNAL RAM MBIST complete. External Scratchpad RAM and FIFO RAM available for use

Figure 9. Power-Up Waveforms

The PGA450-Q1 provides two power-control bits for enabling different analog blocks to manage the total current consumption of the device. On power up, the device is in the *QUIET* mode with only the 8051W and LIN transceiver turned on. All other analog blocks are disabled. Setting the active bit enables the low-side drivers required for bursting as well as the echo-processing circuitry that includes the LNA and the ADC. In addition, a separate control bit is provided to enable the VREG circuitry, which is used to charge the external capacitor used during bursting.

The AVDD pin can be used to source current for up to 5 mA for resistive loads, including the loads on the GPIO and Tx pins.

CONTROL BIT DEFAULT FUNCTION

1 VREG\_EN Disabled Enables the VREG circuitry that provides the 100-mA current to charge the external capacitor used during bursting

2 ACTIVE\_EN<sup>(1)</sup> Disabled Enables the LNA, ADC, ADC REF and other support circuitry related to burst generation and echo processing

**Table 2. Power Modes**

(1) ACTIVE\_EN bit must be set before enabling the burst / saturation or echo-enable bits.

## **VREG**

The PGA450-Q1 provides a regulated voltage output which, along with an external capacitor, can be used to drive the primary of the transformer used to excite the transducer. The VREG regulator provides a 100-mA current, sourced from VPWR, to charge the external capacitor. The user can select the desired VREG voltage by setting the VREG\_SEL register to the appropriate value.

Note that for VREG to be regulated to the selected voltage, VPWR must be at least 2 V above the selected VREG voltage.

The energy needed for the burst comes from the external capacitor. The device has a VREG\_READY status bit in the STATUS2 register to indicate when the capacitor is fully charged and has reached the regulation voltage.

This block is disabled by default. Setting the VREG\_EN bit in the PWR\_MODE register to high, enables this regulator.

#### Clock

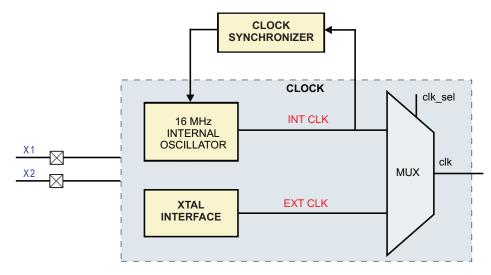

The clock block generates the system clock that is used in the generation of burst, communication, echo time measurement, and the microprocessor clock. Figure 10 shows the clock block in the PGA450-Q1.

Figure 10. Clock Block in PGA450-Q1

The clk signal provided to various blocks inside the device is derived of one of the following sources:

- 1. Internal oscillator without synchronization with communication: In this mode, the internal oscillator output is the source for the system clock.

- 2. Internal oscillator with synchronization with communication: In this mode, the internal oscillator output is corrected for inaccuracy using time measurements of the communication bus. Note that this mode requires the implementation of CLOCK SYNCHRONIZER logic in the digital control block. The clock synchronizer uses the SYNC FIELD to measure the timer value and adjust the internal oscillator output

- 3. External crystal: In this mode, a 16-MHz external crystal is the source of system clock.

The clock source is controlled by the CLK\_SEL register. Table 3 describes the settings of the CLK\_SEL bits and the corresponding clock mode.

| CLK_SEL BIT VALUES CLOCK SOURCE |                                                                            |

|---------------------------------|----------------------------------------------------------------------------|

| 0b00                            | Internal clock. Ignore the synchronization pulse received on the LIN bus.  |

| 0b01                            | Internal clock. Process the synchronization pulse received on the LIN bus. |

| 0b10                            | External crystal clock                                                     |

| 0b11                            | Internal clock. Ignore the synchronization pulse received on the LIN bus.  |

**Table 3. Clock Selection**

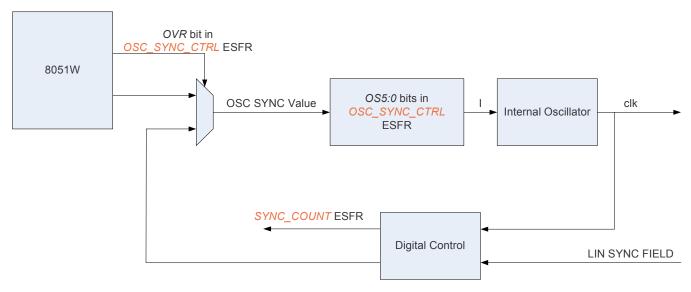

### Clock Synchronizer Using the SYNC Field in the LIN Bus

The clock synchronizer block adjusts the internal oscillator based on a SYNC field in the LIN frame received in the communication line. The internal clock is trimmed to 16 MHz with ±4% tolerance in the TI factory.

The clock synchronizer improves the instantaneous accuracy of the internal oscillator frequency to 16 MHz ±0.5% using the LIN SYNC field, assuming an ideal LIN baud rate of 19.2 kBPS. The synchronization algorithm uses the time between two falling edges of the LIN SYNC field to adjust the internal oscillator.

The SYNC\_COUNT is available for the 8051W to determine the effectiveness of the synchronization process based on the LIN SYNC field. That is, if the synchronization was effective, then the SYNC COUNT value should be close to 1667 ±8 counts.

This OSC SYNC value can also be updated by the 8051W microprocessor; this field can be updated by the 8051W by setting the OVR bit in OSC SYNC CTRL ESFR.

Figure 11. PGA450-Q1 Internal Clock Synchronization Control

The following table describes the value of OS<5:0> and the resulting change in frequency.

Table 4. OS<5:0> versus Delta System Clock Frequency

| OS<5:0> | Delta Frequency |

|---------|-----------------|

| 0       | −3.84 MHz       |

|         |                 |

| 31      | –120 kHz        |

| 32      | 0 kHz           |

| 33      | 120 kHz         |

|         |                 |

| 63      | 3.72 MHz        |

#### NOTE

The clock synchronization feature is not available if the device is configured in SCI buffered mode. (See LIN 2.1 Slave/Buffered SCI for details.)

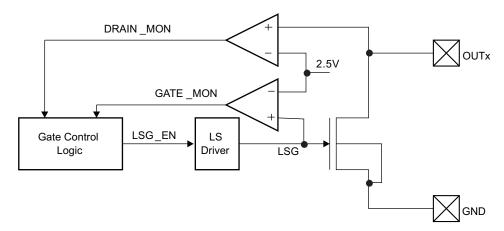

#### **Low-Side Drive FETs**

The PGA450-Q1 provides two low-side drivers for driving the primary of a transformer or an equivalent load. The control/drive modes for the low-side drive are described in the Burst Generator section.

The low driver block also has diagnostics. See the *Diagnostics* section for a description of the diagnostics.

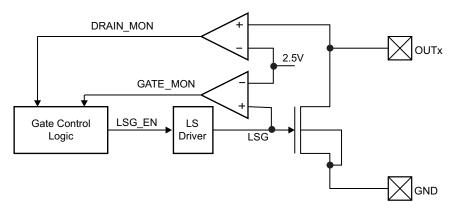

Figure 12 shows the schematic of the low side drive

Figure 12. Low-Side Drive Block Diagram

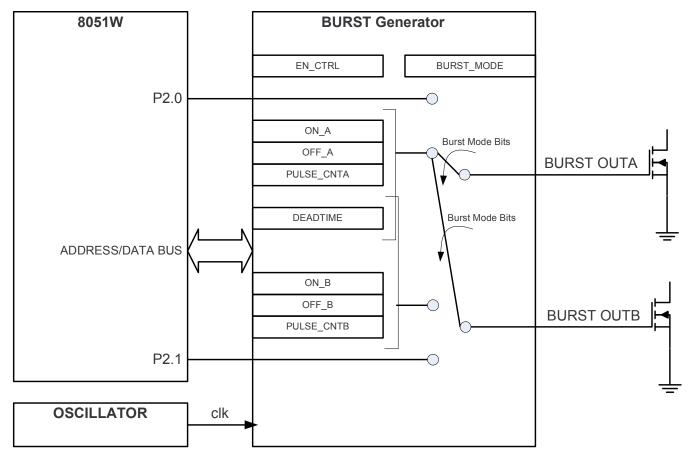

#### **Burst Generator**

The burst generator block generates the high-frequency pulses used to drive the gates of the low-side FETs. The low-side FETs ultimately drive the transducer by modulating the primary of the transformer.

The PGA450-Q1 provides MODE bits in the BURST MODE register (see Programmer's Guide, SLDU006) to configure each low-side drive MOSFET in three possible drive modes.

The three possible drive modes are:

- 1. Single-ended: In this mode, one low-side switch is used to turn current on and off in the primary of the transformer. The rate of change of current in the primary generates a voltage in the secondary of the transformer, which is connected to the transducer.

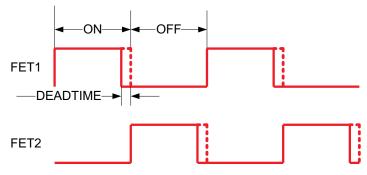

- 2. Push-pull: In this mode, two low-side switches are used to turn current on and off in two primary coils in the transformer. The primary coils have the same number of turns. The rate of change of current in the primary generates a voltage in the secondary of the transformer, which is connected to the transducer. The direction of current in the secondary generates voltages of opposite polarity in the secondary, effectively doubling the peak-to-peak voltage in the secondary.

- 3. 8051W port drive: In this mode, the low-side switches are controlled via an 8051W port pin.

Figure 13 shows the block diagram of the burst generator. The figure shows that the burst generator has a number of registers which the user software must configure.

Figure 13. Burst Generator

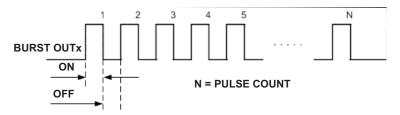

The PGA450-Q1 provides 3 MODE bits in the BURST MODE register to select from the five burst configurations available. Table 5 describes the modes of operation of the two low-side gate drives of the burst generator. For an understanding of the configurations, see Figure 14 and for an understanding of the waveforms, see Figure 15.

Table 5. Low-Side MOSFET Gate Drive Modes

| ITEM                                  | DESCRIPTION                                                                                                         |  |  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| Mode Bits in BURST_MODE Register: 000 |                                                                                                                     |  |  |

| Mode description                      | LS A and B are in push-pull                                                                                         |  |  |

| Low-side A trigger                    | Write 1 to BURST_A_EN bit in ENABLE CONTROL register                                                                |  |  |

| Low-side B trigger                    | Write 1 to BURST_A_EN bit in ENABLE CONTROL register                                                                |  |  |

| No. of pulses on A                    | Set by PULSE COUNT A (0-63 pulses) register                                                                         |  |  |

| No. of pulses on B                    | Set by PULSE COUNT B (0-63 pulses) register                                                                         |  |  |

| Low-side A frequency                  | Set by registers:  • BURST_ONA (11 bits at 16 MHz)  • BURST_OFFA (11 bits at 16 MHz)  • DEADTIME (8 bits at 16 MHz) |  |  |

| Low-side B frequency                  | Set by registers: BURST_ONA (11 bits at 16 MHz), BURST_OFFA (11 bits at 16 MHz), DEADTIME (8 bits at 16 MHz)        |  |  |

| Mode Bits in BURST_MODE Register:     | 001                                                                                                                 |  |  |

| Mode description                      | LS A is controlled by burst generator A<br>LS B through the internal micro P2.1 port                                |  |  |

| Low-side A trigger                    | Write 1 to BURST_A_EN bit in ENABLE CONTROL register                                                                |  |  |

| Low-side B trigger                    | Controlled by 8051W software                                                                                        |  |  |

Copyright © 2012, Texas Instruments Incorporated

## Table 5. Low-Side MOSFET Gate Drive Modes (continued)

| ITEM                                  | DESCRIPTION                                                                            |

|---------------------------------------|----------------------------------------------------------------------------------------|

| No. of pulses on A                    | Set by PULSE COUNT A (0-63 pulses) register                                            |

| No. of pulses on B                    | Controlled by 8051W software                                                           |

| Low-side A frequency                  | Set by registers:  BURST_ONA (11 bits at 16 MHz)  BURST_OFFA (11 bits at 16 MHz)       |

| Low-side B frequency                  | Controlled by 8051W software                                                           |

| Mode Bits in BURST_MODE Register: 010 |                                                                                        |

| Mode description                      | LS A through the internal micro P2.0 port<br>LS B is controlled by burst generator B   |

| Low-side A trigger                    | Controlled by 8051W software                                                           |

| Low-side B trigger                    | Write 1 to BURST_B_EN bit in ENABLE CONTROL register                                   |

| No. of pulses on A                    | Controlled by 8051W software                                                           |

| No. of pulses on B                    | Set by SFR, PULSE COUNT B (0-63 pulses) register                                       |

| Low-side A frequency                  | Controlled by 8051W software                                                           |

| Low-side B frequency                  | Set by registers: BURST_ONB (11 bits at 16 MHz) and BURST_OFFB (11 bits at 16 MHz)     |

| Mode Bits in BURST_MODE Register: 011 |                                                                                        |

| Mode description                      | LS A is controlled by burst generator A<br>LS B is controlled by burst generator B     |

| Low-side A trigger                    | Write 1 to BURST_A_EN bit in ENABLE CONTROL register                                   |

| Low-Side B trigger                    | Write 1 to BURST_B_EN bit in ENABLE CONTROL register                                   |

| No. of pulses on A                    | Set by SFR, PULSE COUNT A (0-63 pulses) register                                       |

| No. of pulses on B                    | Set by SFR, PULSE COUNT B (0-63 pulses) register                                       |

| Low-side A frequency                  | Set by registers: BURST_ONA (11 bits at 16 MHz) and BURST_OFFA (11 bits at 16 MHz)     |

| Low-side B frequency                  | Set by registers: BURST_ONB (11 bits at 16 MHz) and BURST_OFFB (11 bits at 16 MHz)     |

| Mode Bits in BURST_MODE Register: 100 |                                                                                        |

| Mode description                      | LS A through the internal micro P2.0 port<br>LS B through the internal micro P2.1 port |

| Low-side A trigger                    | Controlled by 8051W software                                                           |

| Low-side B trigger                    | Controlled by 8051W software                                                           |

| No. of pulses on A                    | Controlled by 8051W software                                                           |

| No. of pulses on B                    | Controlled by 8051W software                                                           |

| Low-side A frequency                  | Controlled by 8051W software                                                           |

| Low-side B frequency                  | Controlled by 8051W software                                                           |

| Mode Bits in BURST_MODE Register: 101 | ·                                                                                      |

| Mode description                      | For TI Use Only                                                                        |

| Low-side A trigger                    |                                                                                        |

| Low-side B trigger                    |                                                                                        |

| No. of pulses on A                    |                                                                                        |

| No. of pulses on B                    |                                                                                        |

| Low-side A frequency                  |                                                                                        |

| Low-side B frequency                  |                                                                                        |

| Mode Bits in BURST_MODE Register: 110 |                                                                                        |

| Mode description                      | Reserved                                                                               |

| Mode Bits in BURST_MODE Register: 111 |                                                                                        |

| Mode description                      | Reserved                                                                               |

The relationship of BURST\_OUTx is shown in Figure 14.

Figure 14. Timing Diagram Showing the Usage of ON Register, OFF Register and PULSE COUNT Register Values

The relationship between ONTIME, OFFTIME and DEADTIME values in the push-pull configuration is shown in Figure 15.

Figure 15. Timing Diagram Showing the Relationship Between ONTIME, OFFTIME, and DEADTIME Registers in the Push-Pull Configuration

In the 8051W drive mode, the 8051W port pins used to drive the OUTA and OUTB pins are listed in Table 6.

Table 6. OUTA/OUTB Pin Map

| PGA450-Q1 PIN | 8051W PORT |

|---------------|------------|

| OUTA          | 2.0        |

| OUTB          | 2.1        |

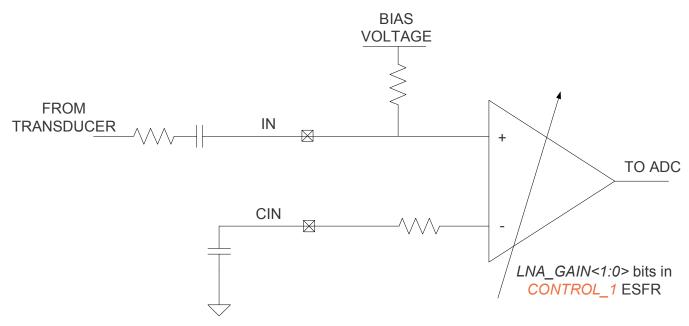

#### **Low-Noise Amplifier**

This block is the analog front-end that interfaces with the transducer directly. The echo signal is coupled through an external capacitor so that only the ac component of the transducer voltage is passed to the low-noise amplifier (LNA). The LNA outputs an amplified version of the transducer voltage with a dc offset that is equal to the mid-scale of the A/D converter.

The LNA gain is configurable by setting the LNA\_GAIN1 and LNA\_GAIN0 bits in the CONTROL\_1 register to the appropriate values.

Copyright © 2012, Texas Instruments Incorporated

Figure 16. Low-Noise Amplifier

## A/D Converter

The 12-bit successive approximation register (SAR) analog-to-digital converter converts the analog voltage from the echo-processing circuit into a digital word. The converted digital word is processed by the band-pass filter. The ADC is dedicated to the echo-processing signal path and is only enabled in active mode.

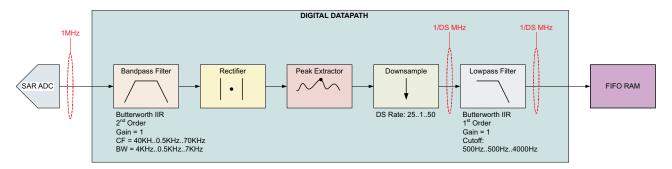

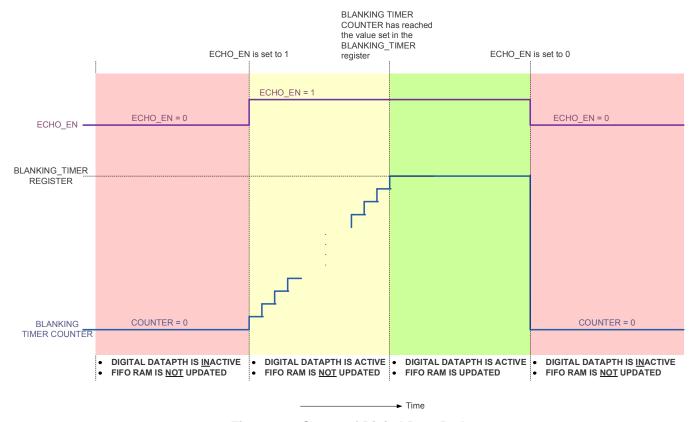

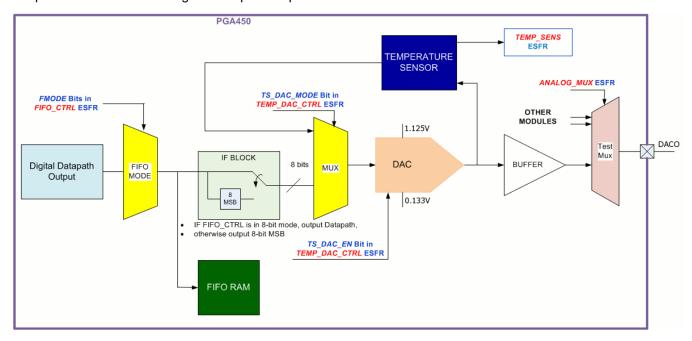

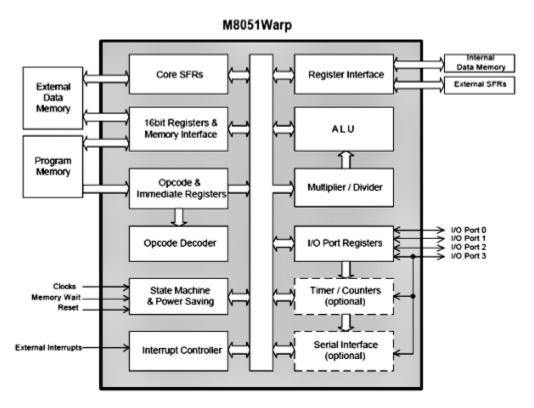

### **Digital Data Path**

The digital data path processes the A/D sample to extract the peak profile of the echo. The output of the digital data path is stored in the FIFO RAM.

Figure 17 summarizes the digital data path.

Figure 17. Digital Data Path

The digital data path has the following components:

- Band-pass filter

- Rectifier

- · Peak extractor

- Downsampler

- · Low-pass filter

**Table 7. Digital Data-Path Filter Summary**

| PARAMETER                                   | SYMBOL           | CONDITION    | MIN                             | TYP | MAX | UNIT    |

|---------------------------------------------|------------------|--------------|---------------------------------|-----|-----|---------|

|                                             | Band-pass filter |              |                                 |     |     |         |

| Band-pass filter                            |                  |              | Second-order Butterworth filter |     |     |         |

| Banl-pass center frequency                  |                  | Programmable | 40                              |     | 70  | kHz     |

| Band-pass center-<br>frequency step<br>size |                  | Programmable |                                 | 0.5 |     | kHz     |

| Band-pass filter bandwidth                  |                  | Programmable | 4                               |     | 7   | kHz     |

| Band-pass filter<br>bandwidth step<br>size  |                  | Programmable |                                 | 0.5 |     | kHz     |

| BPF gain                                    |                  |              |                                 | 0   |     | dB      |

|                                             |                  |              | Downsample                      |     |     |         |

| Downsample rate                             |                  |              | 25                              |     | 50  | Samples |

| Downsample-rate step size                   |                  |              |                                 | 1   |     |         |

|                                             |                  |              | Low-pass filter                 |     |     |         |

| LPF cutoff frequency                        |                  |              | 0.5                             |     | 4   | KHz     |

| LPF cutoff<br>frequency step<br>size        |                  | Programmable |                                 | 0.5 |     | KHz     |

| LPF gain                                    |                  |              |                                 | 0   |     | dB      |

Copyright © 2012, Texas Instruments Incorporated

Each of the digital data-path components is described in the following subsections.

## **Band-Pass Filter (BPF)**

The echo signal is an amplitude-modulated signal with the underlying carrier frequency equal to the drive frequency of the ultrasonic transducer. The band-pass filter block allows frequencies near the drive frequency to pass to downstream signal blocks.

The band-pass filter is a second-order Butterworth IIR filter. The user can configure the center frequency and the bandwidth of the filter by writing specific values to coefficient registers BPF\_B1, BPF\_A2, and BPF\_A3.

Table 9 lists the values (in hex) that must be written to the coefficient registers to realize a bandpass filter of specific center frequency and bandwidth (or Q). It is noted that the stability of the filter is not assured if values other than those listed in Table 9 are written to the registers.

**Table 8. Band-Pass Filter Coefficient Values**

| BW (kHz) | B1 (Hex) | A3 (Hex) |

|----------|----------|----------|

| 4.0      | 32D      | F9A5     |

| 4.5      | 392      | F8DD     |

| 5.0      | 3F6      | F815     |

| 5.5      | 459      | F74D     |

| 6.0      | 4BD      | F687     |

| 6.5      | 520      | F5C1     |

| 7.0      | 582      | F4FB     |

**Table 9. Band-Pass Filter Coefficient Values**

| CF (kHz) | BW (kHz) | A2 (Hex) |

|----------|----------|----------|

| 00       | 4        | F54A     |

|          | 5        | F48B     |

| 39       | 6        | F3CD     |

|          | 7        | F311     |

|          | 4        | F4E6     |

| 40       | 5        | F427     |

| 40       | 6        | F36A     |

|          | 7        | F2AE     |

|          | 4        | F480     |

| 44       | 5        | F3C1     |

| 41       | 6        | F304     |

|          | 7        | F249     |

|          | 4        | F417     |

| 42       | 5        | F358     |

| 42       | 6        | F29C     |

|          | 7        | F1E1     |

|          | 4        | F3AC     |

| 43       | 5        | F2ED     |

| 43       | 6        | F231     |

|          | 7        | F176     |

|          | 4        | F33E     |

| 44       | 5        | F280     |

| 44       | 6        | F1C4     |

|          | 7        | F10A     |

Table 9. Band-Pass Filter Coefficient Values (continued)

| CF (kHz) | BW (kHz) | A2 (Hex) |

|----------|----------|----------|

| 45       | 4        | F2CE     |

|          | 5        | F210     |

| 45       | 6        | F154     |

|          | 7        | F09A     |

|          | 4        | F25B     |

| 46       | 5        | F19E     |

| 40       | 6        | F0E2     |

|          | 7        | F029     |

|          | 4        | F1E6     |

| 47       | 5        | F129     |

| 47       | 6        | F06E     |

|          | 7        | EFB5     |

|          | 4        | F16E     |

| 48       | 5        | F0B2     |

| 40       | 6        | EFF7     |

|          | 7        | EF3E     |

|          | 4        | F0F4     |

| 40       | 5        | F038     |

| 49       | 6        | EF7E     |

|          | 7        | EEC5     |

|          | 4        | F078     |

| 50       | 5        | EFBC     |

| 50       | 6        | EF02     |

|          | 7        | EE4A     |

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Table 9. Band-Pass Filter Coefficient Values (continued)

| CF (kHz) | BW (kHz) | A2 (Hex) |

|----------|----------|----------|

|          | 4        | EFF9     |

| 51       | 5        | EF3E     |

|          | 6        | EE84     |

|          | 7        | EDCC     |

|          | 4        | EF78     |

| 50       | 5        | EEBD     |

| 52       | 6        | EE03     |

|          | 7        | ED4C     |

|          | 4        | EEF4     |

| 53       | 5        | EE39     |

| 55       | 6        | ED80     |

|          | 7        | ECC9     |

|          | 4        | EE6E     |

| 54       | 5        | EDB4     |

| 04       | 6        | ECFB     |

|          | 7        | EC44     |

|          | 4        | EDE5     |

| 55       | 5        | ED2B     |

| 00       | 6        | EC73     |

|          | 7        | EBBD     |

|          | 4        | ED5A     |

| 56       | 5        | ECA1     |

| 00       | 6        | EBE9     |

|          | 7        | EB33     |

|          | 4        | ECCD     |

| 57       | 5        | EC14     |

| 01       | 6        | EB5D     |

|          | 7        | EAA7     |

|          | 4        | EC3D     |

| 58       | 5        | EB85     |

|          | 6        | EACE     |

|          | 7        | EA19     |

|          | 4        | EBAB     |

| 59       | 5        | EAF3     |

|          | 6        | EA3D     |

|          | 7        | E988     |

|          | 4        | EB16     |

| 60       | 5        | EA5F     |

|          | 6        | E9A9     |

|          | 7        | E8F5     |

Table 9. Band-Pass Filter Coefficient Values (continued)

| CF (kHz) | BW (kHz) | A2 (Hex) |

|----------|----------|----------|

|          | 4        | EA7F     |

| 61       | 5        | E9C8     |

|          | 6        | E913     |

|          | 7        | E85F     |

|          | 4        | E9E6     |

| 00       | 5        | E930     |

| 62       | 6        | E87B     |

|          | 7        | E7C7     |

|          | 4        | E94B     |

| 60       | 5        | E894     |

| 63       | 6        | E7E0     |

|          | 7        | E72D     |

|          | 4        | E8AD     |

| 64       | 5        | E7F7     |

| 64       | 6        | E743     |

|          | 7        | E691     |

|          | 4        | E80C     |

| C.F.     | 5        | E757     |

| 65       | 6        | E6A4     |

|          | 7        | E5F2     |

|          | 4        | E769     |

| 66       | 5        | E6B5     |

| 00       | 6        | E602     |

|          | 7        | E551     |

|          | 4        | E6C4     |

| 67       | 5        | E610     |

| 07       | 6        | E55E     |

|          | 7        | E4AD     |

|          | 4        | E61D     |

| 68       | 5        | E569     |

| 00       | 6        | E4B8     |

|          | 7        | E407     |

|          | 4        | E573     |

| 69       | 5        | E4C0     |

| 09       | 6        | E40F     |

|          | 7        | E35F     |

|          | 4        | E4C7     |

| 70       | 5        | E415     |

| 70       | 6        | E364     |

|          | 7        | E2B5     |

Copyright © 2012, Texas Instruments Incorporated

#### Rectifier

The output of the band-pass filter is a signed number. The rectifier rectifies the output of the band-pass filter to create a positive number.

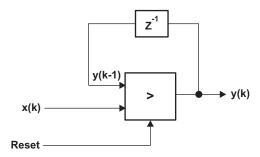

#### **Peak Extractor**

The peak extractor in the PGA450-Q1 is a simple moving-peak algorithm. Specifically, the output of the peak extractor is updated if the input to the peak extractor is greater than the previous output of the peak extractor. This algorithm is summarized in Equation 1:

$$y[k] = \{y[k-1], \text{ if } y[k-1] > Px[k], \text{ otherwise } x[k]\}$$

(1)

where y is the output of the Peak Extractor, x is the input to the Peak Extractor, and k is the discrete-time step.

The peak extractor algorithm is shown pictorially in Figure 18.

Figure 18. Peak Extractor

### **Downsample**

The downsample block performs two functions:

- Generate reset signal for the peak extractor shown in Figure 18.

- Generate output

The downsample rate can be configured by the user by writing to the downsample register. If the output of the peak extractor must be low-pass filtered before storing it in the FIFO, then the allowable values for the downsample register for the low-pass filter correctly are from 25 to 50; that is,

25 ≤ DOWNSAMPLE ≤ 50

However, if the user does not need to low-pass filter the output before storing to the FIFO, then the user can configure the DOWNSAMPLE register value to any value between 1 and 63.

The downsample block has a counter which starts at 0 and counts up to the values programmed in the DOWNSAMPLE register. When the count reaches the value in the DOWNSAMPLE register, the counter inside the downsample block is reset to 0. Furthermore, the downsample block generates a reset to the peak extractor. This reset signal sets the output of the peak extractor to 0.

The data output rate of the downsample block is:

OUTPUT RATE OF DOWNSAMPLE RATE =  $DOWNSAMPLE \times 1 \mu s$ .

#### Low-Pass Filter

The output of the downsample block can be filtered by a low-pass filter. The low -ass filter in the PGA450-Q1 is a first-order Butterworth IIR filter with configurable cutoff frequency.

The user can configure the cutoff frequency of the filter by writing specific values to coefficient registers LPF\_B1 and LPF\_A2. Note that for the same desired cutoff frequency, the coefficient values depend on the configured DOWNSAMPLE register.

Table 10 lists the values (in hex) that must be written to the coefficient registers to realize a low-pass filter of specific cutoff frequency. Note that the stability of the filter is not assured if values other than those listed in the table are written to the registers.

4 Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

www.ti.com

## **Table 10. Low-Pass Filter Coefficient Values**

| CUTOFF<br>(kHz) | DOWNSAMPLE (Hex) | B1 (Hex) | A2 (Hex) |

|-----------------|------------------|----------|----------|

| 0.5             | 19               | 4D7      | 7652     |

|                 | 1A               | 506      | 75F3     |

|                 | 1B               | 536      | 7594     |

|                 | 1C               | 565      | 7535     |

|                 | 1D               | 595      | 74D7     |

|                 | 1E               | 5C4      | 7479     |

|                 | 1F               | 5F3      | 741B     |