SLLS177H - MARCH 1994 - REVISED JANUARY 2006

- Programmable Auto-RTS and Auto-CTS

- In Auto-CTS Mode, CTS Controls Transmitter

- In Auto-RTS Mode, RCV FIFO Contents and Threshold Control RTS

- Serial and Modem Control Outputs Drive a RJ11 Cable Directly When Equipment Is on the Same Power Drop

- Capable of Running With All Existing TL16C450 Software

- After Reset, All Registers Are Identical to the TL16C450 Register Set

- Up to 16-MHz Clock Rate for up to 1-Mbaud Operation

- In the TL16C450 Mode, Hold and Shift Registers Eliminate the Need for Precise Synchronization Between the CPU and Serial Data

- Programmable Baud Rate Generator Allows Division of Any Input Reference Clock by 1 to (2<sup>16</sup> -1) and Generates an Internal 16× Clock

- Standard Asynchronous Communication Bits (Start, Stop, and Parity) Added to or Deleted From the Serial Data Stream

- 5-V and 3.3-V Operation

- Independent Receiver Clock Input

- Transmit, Receive, Line Status, and Data Set Interrupts Independently Controlled

- Fully Programmable Serial Interface Characteristics:

- 5-, 6-, 7-, or 8-Bit Characters

- Even-, Odd-, or No-Parity Bit Generation and Detection

- 1-, 1 1/2-, or 2-Stop Bit Generation

- Baud Generation (dc to 1 Mbit/s)

- False-Start Bit Detection

- Complete Status Reporting Capabilities

- 3-State Output TTL Drive Capabilities for Bidirectional Data Bus and Control Bus

- Line Break Generation and Detection

- Internal Diagnostic Capabilities:

- Loopback Controls for Communications Link Fault Isolation

- Break, Parity, Overrun, and Framing Error Simulation

- Fully Prioritized Interrupt System Controls

- Modem Control Functions (CTS, RTS, DSR, DTR, RI, and DCD)

#### description

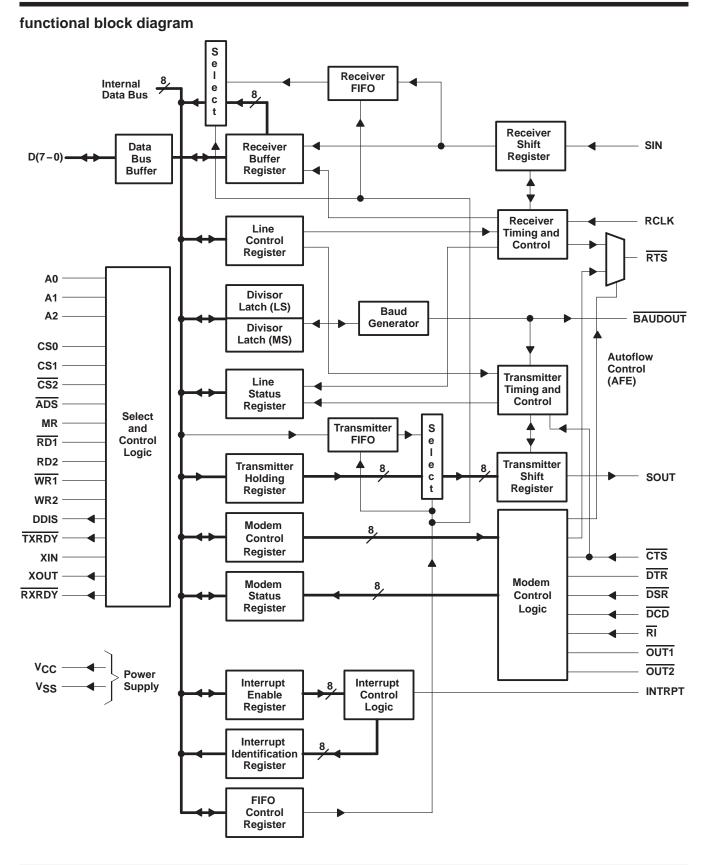

The TL16C550C and the TL16C550CI are functional upgrades of the TL16C550B asynchronous communications element (ACE), which in turn is a functional upgrade of the TL16C450. Functionally equivalent to the TL16C450 on power up (character or TL16C450 mode), the TL16C550C and the TL16C550CI, like the TL16C550B, can be placed in an alternate FIFO mode. This relieves the CPU of excessive software overhead by buffering received and transmitted characters. The receiver and transmitter FIFOs store up to 16 bytes including three additional bits of error status per byte for the receiver FIFO. In the FIFO mode, there is a selectable autoflow control feature that can significantly reduce software overload and increase system efficiency by automatically controlling serial data flow using RTS output and CTS input signals.

The TL16C550C and TL16C550Cl perform serial-to-parallel conversions on data received from a peripheral device or modem and parallel-to-serial conversion on data received from its CPU. The CPU can read the ACE status at any time. The ACE includes complete modem control capability and a processor interrupt system that can be tailored to minimize software management of the communications link.

Both the TL16C550C and the TL16C550Cl ACE include a programmable baud rate generator capable of dividing a reference clock by divisors from 1 to 65535 and producing a  $16\times$  reference clock for the internal transmitter logic. Provisions are included to use this  $16\times$  clock for the receiver logic. The ACE accommodates a 1-Mbaud serial rate (16-MHz input clock) so that a bit time is 1  $\mu$ s and a typical character time is 10  $\mu$ s (start bit, 8 data bits, stop bit).

Two of the TL16C450 terminal functions on the TL16C550C and the TL16C550CI have been changed to TXRDY and RXRDY, which provide signaling to a DMA controller.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

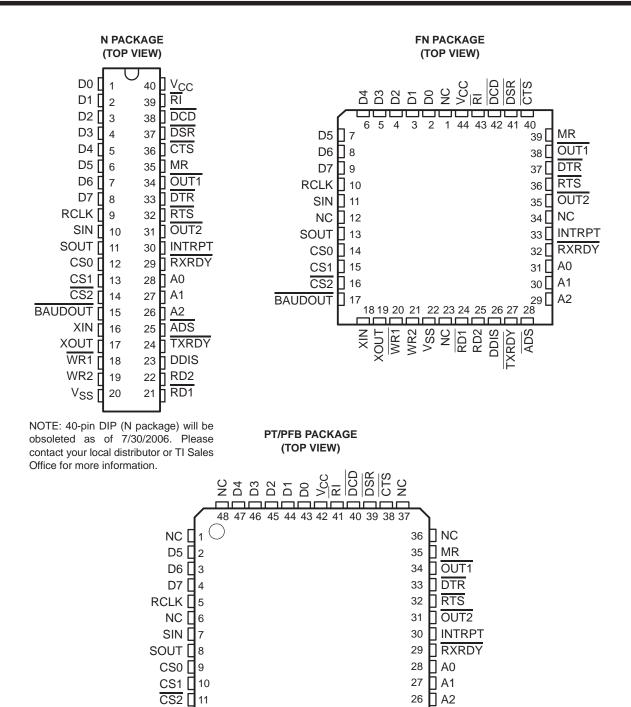

NC-No internal connection

BAUDOUT 12

13 14 15 16 17 18 19 20 21 22 23 24

25 NC

DDIS

# detailed description

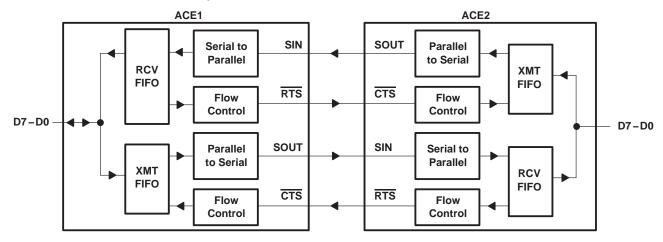

#### autoflow control (see Figure 1)

Autoflow control is comprised of auto-\overline{CTS} and auto-\overline{RTS}. With auto-\overline{CTS} input must be active before the transmitter FIFO can emit data. With auto-\overline{RTS}, \overline{RTS} becomes active when the receiver needs more data and notifies the sending serial device. When \overline{RTS} is connected to \overline{CTS}, data transmission does not occur unless the receiver FIFO has space for the data; thus, overrun errors are eliminated using ACE1 and ACE2 from a TLC16C550C with the autoflow control enabled. If not, overrun errors occur when the transmit data rate exceeds the receiver FIFO read latency.

Figure 1. Autoflow Control (Auto-RTS and Auto-CTS) Example

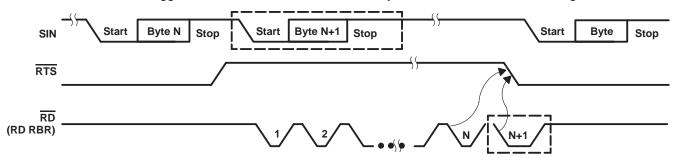

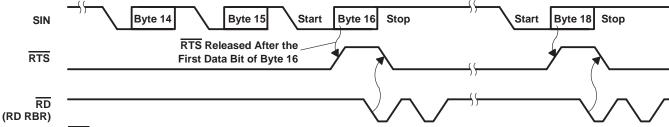

# auto-RTS (see Figure 1)

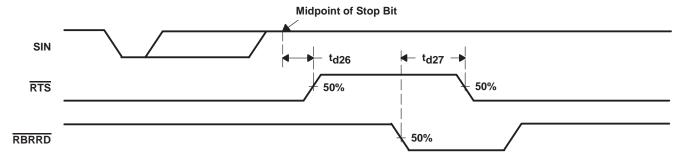

Auto-RTS data flow control originates in the receiver timing and control block (see functional block diagram) and is linked to the programmed receiver FIFO trigger level. When the receiver FIFO level reaches a trigger level of 1, 4, or 8 (see Figure 3), RTS is deasserted. With trigger levels of 1, 4, and 8, the sending ACE may send an additional byte after the trigger level is reached (assuming the sending ACE has another byte to send) because it may not recognize the deassertion of RTS until after it has begun sending the additional byte. RTS is automatically reasserted once the RCV FIFO is emptied by reading the receiver buffer register.

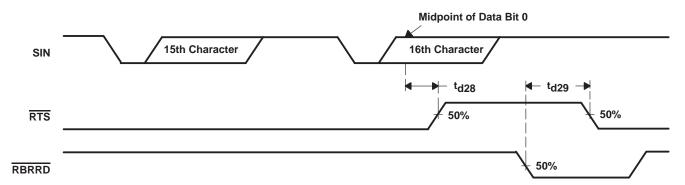

When the trigger level is 14 (see Figure 4), RTS is deasserted after the first data bit of the 16th character is present on the SIN line. RTS is reasserted when the RCV FIFO has at least one available byte space.

# auto-CTS (see Figure 1)

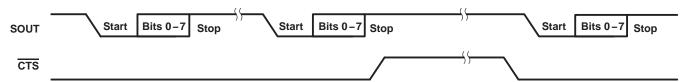

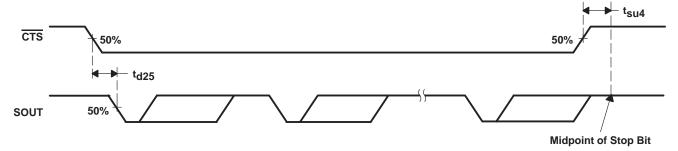

The transmitter circuitry checks  $\overline{\text{CTS}}$  before sending the next data byte. When  $\overline{\text{CTS}}$  is active, it sends the next byte. To stop the transmitter from sending the following byte,  $\overline{\text{CTS}}$  must be released before the middle of the last stop bit that is currently being sent (see Figure 2). The auto- $\overline{\text{CTS}}$  function reduces interrupts to the host system. When flow control is enabled,  $\overline{\text{CTS}}$  level changes do not trigger host interrupts because the device automatically controls its own transmitter. Without auto- $\overline{\text{CTS}}$ , the transmitter sends any data present in the transmit FIFO and a receiver overrun error may result.

#### enabling autoflow control and auto-CTS

Autoflow control is enabled by setting modem control register bits 5 (autoflow enable or AFE) and 1 (RTS) to a 1. Autoflow incorporates both auto-RTS and auto-CTS. When only auto-CTS is desired, bit 1 in the modem control register should be cleared (this assumes that a control signal is driving CTS).

# auto-CTS and auto-RTS functional timing

NOTES: A. When CTS is low, the transmitter keeps sending serial data out.

- B. If CTS goes high before the middle of the last stop bit of the current byte, the transmitter finishes sending the current byte but it does not send the next byte.

- C. When CTS goes from high to low, the transmitter begins sending data again.

Figure 2. CTS Functional Timing Waveforms

The receiver FIFO trigger level can be set to 1, 4, 8, or 14 bytes. These are described in Figures 3 and 4.

NOTES: A. N = RCV FIFO trigger level (1, 4, or 8 bytes)

B. The two blocks in dashed lines cover the case where an additional byte is sent as described in the preceding auto-RTS section.

Figure 3. RTS Functional Timing Waveforms, RCV FIFO Trigger Level = 1,4, or 8 Bytes

- NOTES: A. RTS is deasserted when the receiver receives the first data bit of the sixteenth byte. The receive FIFO is full after finishing the sixteenth byte.

- B. RTS is asserted again when there is at least one byte of space available and no incoming byte is in processing or there is more than one byte of space available.

- C. When the receive FIFO is full, the first receive buffer register read reasserts RTS.

Figure 4. RTS Functional Timing Waveforms, RCV FIFO Trigger Level = 14 Bytes

# **Terminal Functions**

| TERMINAL                                     |                                      | /INAL                           |                                           | ΓERMINAL |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  | TERMINAL |  |  | TERMINAL |  |  |  |

|----------------------------------------------|--------------------------------------|---------------------------------|-------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------|--|--|----------|--|--|--|

| NAME                                         | NO.<br>N <sup>†</sup>                | NO.<br>FN                       | NO.<br>PT                                 | 1/0      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |          |  |  |          |  |  |  |

| A0<br>A1<br>A2                               | 28<br>27<br>26                       | 31<br>30<br>29                  | 28<br>27<br>26                            | I        | Register select. A0-A2 are used during read and write operations to select the ACE register to read from or write to. Refer to Table 1 for register addresses and refer to ADS description.                                                                                                                                                                                                                                                                                                                                                                                                               |  |          |  |  |          |  |  |  |

| ADS                                          | 25                                   | 28                              | 24                                        | I        | Address strobe. When $\overline{ADS}$ is active (low), A0, A1, and A2 and CS0, CS1, and $\overline{CS2}$ drive the internal select logic directly; when $\overline{ADS}$ is high, the register select and chip select signals are held at the logic levels they were in when the low-to-high transition of $\overline{ADS}$ occurred.                                                                                                                                                                                                                                                                     |  |          |  |  |          |  |  |  |

| BAUDOUT                                      | 15                                   | 17                              | 12                                        | 0        | Baud out. BAUDOUT is a 16× clock signal for the transmitter section of the ACE. The clock rate is established by the reference oscillator frequency divided by a divisor specified by the baud generator divisor latches. BAUDOUT may also be used for the receiver section by tying this output to RCLK.                                                                                                                                                                                                                                                                                                 |  |          |  |  |          |  |  |  |

| CS0<br><u>CS1</u><br>CS2                     | 12<br>13<br>14                       | 14<br>15<br>16                  | 9<br>10<br>11                             | I        | Chip select. When CS0 and CS1 are high and CS2 is low, these three inputs select the ACE. When any of these inputs are inactive, the ACE remains inactive (refer to ADS description).                                                                                                                                                                                                                                                                                                                                                                                                                     |  |          |  |  |          |  |  |  |

| CTS                                          | 36                                   | 40                              | 38                                        | I        | Clear to send. $\overline{\text{CTS}}$ is a modem status signal. Its condition can be checked by reading bit 4 (CTS) of the modem status register. Bit 0 ( $\Delta$ CTS) of the modem status register indicates that $\overline{\text{CTS}}$ has changed states since the last read from the modem status register. If the modem status interrupt is enabled when $\overline{\text{CTS}}$ changes levels and the auto- $\overline{\text{CTS}}$ mode is not enabled, an interrupt is generated. $\overline{\text{CTS}}$ is also used in the auto- $\overline{\text{CTS}}$ mode to control the transmitter. |  |          |  |  |          |  |  |  |

| D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 2<br>3<br>4<br>5<br>6<br>7<br>8 | 43<br>44<br>45<br>46<br>47<br>2<br>3<br>4 | I/O      | Data bus. Eight data lines with 3-state outputs provide a bidirectional path for data, control, and status information between the ACE and the CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |          |  |  |          |  |  |  |

| DCD                                          | 38                                   | 42                              | 40                                        | I        | Data carrier detect. $\overline{DCD}$ is a modem status signal. Its condition can be checked by reading bit 7 (DCD) of the modem status register. Bit 3 ( $\Delta DCD$ ) of the modem status register indicates that $\overline{DCD}$ has changed states since the last read from the modem status register. If the modem status interrupt is enabled when $\overline{DCD}$ changes levels, an interrupt is generated.                                                                                                                                                                                    |  |          |  |  |          |  |  |  |

| DDIS                                         | 23                                   | 26                              | 22                                        | 0        | Driver disable. DDIS is active (high) when the CPU is not reading data. When active, DDIS can disable an external transceiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |          |  |  |          |  |  |  |

| DSR                                          | 37                                   | 41                              | 39                                        | I        | Data set ready. $\overline{DSR}$ is a modem status signal. Its condition can be checked by reading bit 5 (DSR) of the modem status register. Bit 1 ( $\Delta DSR$ ) of the modem status register indicates $\overline{DSR}$ has changed levels since the last read from the modem status register. If the modem status interrupt is enabled when $\overline{DSR}$ changes levels, an interrupt is generated.                                                                                                                                                                                              |  |          |  |  |          |  |  |  |

| DTR                                          | 33                                   | 37                              | 33                                        | 0        | Data terminal ready. When active (low), $\overline{\text{DTR}}$ informs a modem or data set that the ACE is ready to establish communication. $\overline{\text{DTR}}$ is placed in the active level by setting the DTR bit of the modem control register. $\overline{\text{DTR}}$ is placed in the inactive level either as a result of a master reset, during loop mode operation, or clearing the DTR bit.                                                                                                                                                                                              |  |          |  |  |          |  |  |  |

| INTRPT                                       | 30                                   | 33                              | 30                                        | 0        | Interrupt. When active (high), INTRPT informs the CPU that the ACE has an interrupt to be serviced. Four conditions that cause an interrupt to be issued are: a receiver error, received data that is available or timed out (FIFO mode only), an empty transmitter holding register, or an enabled modem status interrupt. INTRPT is reset (deactivated) either when the interrupt is serviced or as a result of a master reset.                                                                                                                                                                         |  |          |  |  |          |  |  |  |

| MR                                           | 35                                   | 39                              | 35                                        | I        | Master reset. When active (high), MR clears most ACE registers and sets the levels of various output signals (refer to Table 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |          |  |  |          |  |  |  |

The N package is **Not Recommended for New Designs**.

# TL16C550C, TL16C550CI ASYNCHRONOUS COMMUNICATIONS ELEMENT WITH AUTOFLOW CONTROL SLLS177H - MARCH 1994 - REVISED JANUARY 2006

# **Terminal Functions (Continued)**

| TERMINAL     |          |           |           |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|----------|-----------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO.<br>N | NO.<br>FN | NO.<br>PT | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OUT1<br>OUT2 | 34<br>31 | 38<br>35  | 34<br>31  | 0   | Outputs 1 and 2. These are user-designated output terminals that are set to the active (low) level by setting respective modem control register (MCR) bits (OUT1 and OUT2). OUT1 and OUT2 are set to inactive the (high) level as a result of master reset, during loop mode operations, or by clearing bit 2 (OUT1) or bit 3 (OUT2) of the MCR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RCLK         | 9        | 10        | 5         | -1  | Receiver clock. RCLK is the 16× baud rate clock for the receiver section of the ACE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RD1<br>RD2   | 21<br>22 | 24<br>25  | 19<br>20  | I   | Read inputs. When either RD1 or RD2 is active (low or high respectively) while the ACE is selected, the CPU is allowed to read status information or data from a selected ACE register. Only one of these inputs is required for the transfer of data during a read operation; the other input should be tied to its inactive level (i.e., RD2 tied low or RD1 tied high).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RI           | 39       | 43        | 41        | I   | Ring indicator. $\overline{RI}$ is a modem status signal. Its condition can be checked by reading bit 6 (RI) of the modem status register. Bit 2 (TERI) of the modem status register indicates that $\overline{RI}$ has transitioned from a low to a high level since the last read from the modem status register. If the modem status interrupt is enabled when this transition occurs, an interrupt is generated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RTS          | 32       | 36        | 32        | 0   | Request to send. When active, RTS informs the modem or data set that the ACE is ready to receive data. RTS is set to the active level by setting the RTS modem control register bit and is set to the inactive (high) level either as a result of a master reset or during loop mode operations or by clearing bit 1 (RTS) of the MCR. In the auto-RTS mode, RTS is set to the inactive level by the receiver threshold control logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RXRDY        | 29       | 32        | 29        | 0   | Receiver ready. Receiver direct memory access (DMA) signalling is available with \$\overline{RXRDY}\$. When operating in the FIFO mode, one of two types of DMA signalling can be selected using the FIFO control register bit 3 (FCR3). When operating in the TL16C450 mode, only DMA mode 0 is allowed. Mode 0 supports single-transfer DMA in which a transfer is made between CPU bus cycles. Mode 1 supports multitransfer DMA in which multiple transfers are made continuously until the receiver FIFO has been emptied. In DMA mode 0 (FCR0 = 0 or FCR0 = 1, FCR3 = 0), when there is at least one character in the receiver FIFO or receiver holding register, \$\overline{RXRDY}\$ is active (low). When \$\overline{RXRDY}\$ has been active but there are no characters in the FIFO or holding register, \$\overline{RXRDY}\$ goes inactive (high). In DMA mode 1 (FCR0 = 1, FCR3 = 1), when the trigger level or the time-out has been reached, \$\overline{RXRDY}\$ goes active (low); when it has been active but there are no more characters in the FIFO or holding register, it goes inactive (high). |

| SIN          | 10       | 11        | 7         | ı   | Serial data input. SIN is serial data input from a connected communications device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SOUT         | 11       | 13        | 8         | 0   | Serial data output. SOUT is composite serial data output to a connected communication device. SOUT is set to the marking (high) level as a result of master reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TXRDY        | 24       | 27        | 23        | 0   | Transmitter ready. Transmitter DMA signalling is available with TXRDY. When operating in the FIFO mode, one of two types of DMA signalling can be selected using FCR3. When operating in the TL16C450 mode, only DMA mode 0 is allowed. Mode 0 supports single-transfer DMA in which a transfer is made between CPU bus cycles. Mode 1 supports multitransfer DMA in which multiple transfers are made continuously until the transmit FIFO has been filled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VCC          | 40       | 44        | 42        |     | 5-V supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VSS          | 20       | 22        | 18        |     | Supply common                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| WR1<br>WR2   | 18<br>19 | 20<br>21  | 16<br>17  | I   | Write inputs. When either WR1 or WR2 is active (low or high respectively) and while the ACE is selected, the CPU is allowed to write control words or data into a selected ACE register. Only one of these inputs is required to transfer data during a write operation; the other input should be tied to its inactive level (i.e., WR2 tied low or WR1 tied high).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| XIN<br>XOUT  | 16<br>17 | 18<br>19  | 14<br>15  | I/O | External clock. XIN and XOUT connect the ACE to the main timing reference (clock or crystal).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

The N package is Not Recommended for New Designs.

SLLS177H - MARCH 1994 - REVISED JANUARY 2006

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub> (see Note 1)                                         | 0.5 V to 7 V  |

|--------------------------------------------------------------------------------------------|---------------|

| Input voltage range at any input, V <sub>I</sub>                                           | 0.5 V to 7 V  |

| Output voltage range, V <sub>O</sub>                                                       | 0.5 V to 7 V  |

| Operating free-air temperature range, T <sub>A</sub> , TL16C550C                           | 0°C to 70°C   |

| TL16C550CI                                                                                 | –40°C to 85°C |

| Storage temperature range, T <sub>stg</sub>                                                | 65°C to 150°C |

| Case temperature for 10 seconds, T <sub>C</sub> : FN package                               | 260°C         |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: N <sup>†</sup> or PT package | 260°C         |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

The N package is Not Recommended for New Designs.

NOTE 1: All voltage values are with respect to VSS.

### recommended operating conditions

## low voltage (3.3 V nominal)

|                                                         | MIN                 | NOM | MAX                 | UNIT |

|---------------------------------------------------------|---------------------|-----|---------------------|------|

| Supply voltage, V <sub>CC</sub>                         | 3                   | 3.3 | 3.6                 | V    |

| Input voltage, V <sub>I</sub>                           | 0                   |     | VCC                 | V    |

| High-level input voltage, V <sub>IH</sub> (see Note 2)  | 0.7 V <sub>CC</sub> |     |                     | V    |

| Low-level input voltage, V <sub>IL</sub> (see Note 2)   |                     |     | 0.3 V <sub>CC</sub> | V    |

| Output voltage, VO (see Note 3)                         | 0                   |     | VCC                 | V    |

| High-level output current, IOH (all outputs)            |                     |     | 1.8                 | mA   |

| Low-level output current, IOL (all outputs)             |                     |     | 3.2                 | mA   |

| Input capacitance                                       |                     |     | 1                   | pF   |

| Operating free-air temperature, T <sub>A</sub>          | 0                   | 25  | 70                  | °C   |

| Junction temperature range, T <sub>J</sub> (see Note 4) | 0                   | 25  | 115                 | °C   |

| Oscillator/clock speed                                  |                     |     | 14.9                | MHz  |

NOTES: 2. Meets TTL levels,  $V_{IHmin} = 2 V$  and  $V_{ILmax} = 0.8 V$  on nonhysteresis inputs

- 3. Applies for external output buffers

- 4. These junction temperatures reflect simulated conditions. Absolute maximum junction temperature is 150°C. The customer is responsible for verifying junction temperature.

#### standard voltage (5 V nominal)

|                                           |                |     | MIN   | NOM | MAX                  | UNIT     |  |

|-------------------------------------------|----------------|-----|-------|-----|----------------------|----------|--|

| Supply voltage, V <sub>CC</sub>           |                |     | 4.75  | 5   | 5.25                 | V        |  |

| Input voltage, V <sub>I</sub>             |                |     | 0     |     | Vcc                  | V        |  |

| High-level input voltage, V <sub>IH</sub> | Except XIN     |     | 2     |     |                      | .,       |  |

|                                           | XIN            | 0.7 | 7 VCC |     |                      | <b>V</b> |  |

| Lave lave Paradovska na M                 | Except XIN     |     |       |     | 0.8                  |          |  |

| Low-level input voltage, V <sub>IL</sub>  | XIN            |     |       |     | 0.3 V <sub>C</sub> C | V        |  |

| Output voltage, VO (see Note 5            |                |     | 0     |     | Vcc                  | V        |  |

| High-level output current, IOH (          | all outputs)   |     |       |     | 4                    | mA       |  |

| Low-level output current, IOL (a          | Il outputs)    |     |       |     | 4                    | mA       |  |

| Input capacitance                         |                |     |       |     | 1                    | pF       |  |

| Operating free-air temperature,           | T <sub>A</sub> |     | 0     | 25  | 70                   | °C       |  |

NOTE 5: Applies for external output buffers

SLLS177H - MARCH 1994 - REVISED JANUARY 2006

# standard voltage (5 V nominal) (continued)

|                                                         | M | IN | NOM | MAX | UNIT |

|---------------------------------------------------------|---|----|-----|-----|------|

| Junction temperature range, T <sub>J</sub> (see Note 6) |   | 0  | 25  | 115 | °C   |

| Oscillator/clock speed                                  |   |    |     | 16  | MHz  |

NOTE 6: These junction temperatures reflect simulated conditions. Absolute maximum junction temperature is 150°C. The customer is responsible for verifying junction temperature.

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

### low voltage (3.3 V nominal)

|                     | PARAMETER                           | TEST CO                                                                                                  | ONDITIONS                                            | MIN | TYP <sup>†</sup> | MAX | UNIT |

|---------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----|------------------|-----|------|

| V <sub>OH</sub> ‡   | High-level output voltage           | I <sub>OH</sub> = -1 mA                                                                                  |                                                      | 2.4 |                  |     | V    |

| V <sub>OL</sub> ‡   | Low-level output voltage            | I <sub>OL</sub> = 1.6 mA                                                                                 |                                                      |     |                  | 0.5 | V    |

| II                  | Input current                       | V <sub>CC</sub> = 3.6 V,<br>V <sub>I</sub> = 0 to 3.6 V,                                                 | V <sub>SS</sub> = 0,<br>All other terminals floating |     |                  | 10  | μΑ   |

| loz                 | High-impedance-state output current | V <sub>CC</sub> = 3.6 V,<br>V <sub>O</sub> = 0 to 3.6 V,<br>Chip selected in write mod                   | $V_{SS} = 0$ , de or chip deselect                   |     |                  | ±20 | μА   |

| lcc                 | Supply current                      | V <sub>CC</sub> = 3.6 V,<br>SIN, DSR, DCD, CTS, and<br>All other inputs at 0.8 V,<br>No load on outputs, | d RI at 2 V,                                         |     |                  | 8   | mA   |

| C <sub>i(CLK)</sub> | Clock input capacitance             |                                                                                                          |                                                      |     | 15               | 20  | pF   |

| C <sub>o(CLK)</sub> | Clock output capacitance            | V <sub>CC</sub> = 0,<br>f = 1 MHz,                                                                       | $V_{SS} = 0,$ $T_{SS} = 250C$                        |     | 20               | 30  | pF   |

| Ci                  | Input capacitance                   | All other terminals ground                                                                               | T <sub>A</sub> = 25°C,<br>ed                         |     | 6                | 10  | pF   |

| Co                  | Output capacitance                  |                                                                                                          |                                                      |     | 10               | 20  | pF   |

$<sup>\</sup>uparrow$  All typical values are at V<sub>CC</sub> = 3.3 V and T<sub>A</sub> = 25°C.

#### standard voltage (5 V nominal)

|                     | PARAMETER                           | TEST CONDITIONS                                                                                           |                                                      |     | TYP† | MAX | UNIT |

|---------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----|------|-----|------|

| V <sub>OH</sub> ‡   | High-level output voltage           | I <sub>OH</sub> = -1 mA                                                                                   |                                                      | 2.4 |      |     | V    |

| V <sub>OL</sub> ‡   | Low-level output voltage            | I <sub>OL</sub> = 1.6 mA                                                                                  |                                                      |     |      | 0.4 | V    |

| II                  | Input current                       | V <sub>CC</sub> = 5.25 V,<br>V <sub>I</sub> = 0 to 5.25 V,                                                | V <sub>SS</sub> = 0,<br>All other terminals floating |     |      | 10  | μΑ   |

| loz                 | High-impedance-state output current | V <sub>CC</sub> = 5.25 V,<br>V <sub>O</sub> = 0 to 5.25 V,<br>Chip selected in write mod                  | V <sub>SS</sub> = 0,<br>de or chip deselect          |     |      | ±20 | μΑ   |

| ICC                 | Supply current                      | V <sub>CC</sub> = 5.25 V,<br>SIN, DSR, DCD, CTS, and<br>All other inputs at 0.8 V,<br>No load on outputs, | d RI at 2 V,                                         |     |      | 10  | mA   |

| C <sub>i(CLK)</sub> | Clock input capacitance             |                                                                                                           |                                                      |     | 15   | 20  | рF   |

| C <sub>o(CLK)</sub> | Clock output capacitance            | $V_{CC} = 0$                                                                                              | $V_{SS} = 0,$                                        |     | 20   | 30  | рF   |

| Ci                  | Input capacitance                   | f = 1 MHz,<br>All other terminals ground                                                                  | $T_A = 25$ °C, ed                                    |     | 6    | 10  | рF   |

| Co                  | Output capacitance                  | ]                                                                                                         |                                                      |     | 10   | 20  | рF   |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

<sup>&</sup>lt;sup>‡</sup>These parameters apply for all outputs except XOUT.

<sup>‡</sup> These parameters apply for all outputs except XOUT.

SLLS177H - MARCH 1994 - REVISED JANUARY 2006

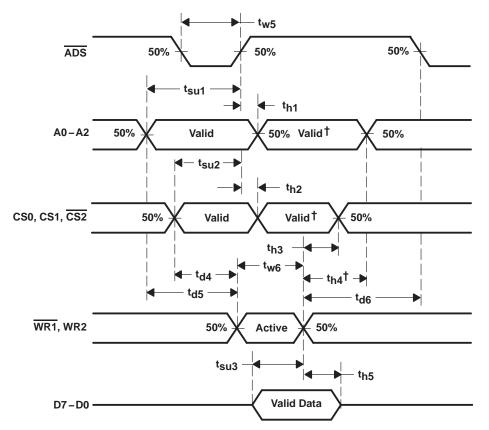

# system timing requirements over recommended ranges of supply voltage and operating free-air temperature

|                   |                                                                                                                                    | ALT. SYMBOL      | FIGURE | TEST CONDITIONS       | MIN MAX | UNIT |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------|--------|-----------------------|---------|------|

| t <sub>cR</sub>   | Cycle time, read (t <sub>W7</sub> + t <sub>d8</sub> + t <sub>d9</sub> )                                                            | RC               |        |                       | 87      | ns   |

| t <sub>cW</sub>   | Cycle time, write (t <sub>w6</sub> + t <sub>d5</sub> + t <sub>d6</sub> )                                                           | WC               |        |                       | 87      | ns   |

| t <sub>w1</sub>   | Pulse duration, clock high                                                                                                         | tXH              | _      | f = 16 MHz Max,       | 0.5     |      |

| t <sub>w2</sub>   | Pulse duration, clock low                                                                                                          | tXL              | 5      | $V_{CC} = 5 V$        | 25      | ns   |

| t <sub>w5</sub>   | Pulse duration, ADS low                                                                                                            | t <sub>ADS</sub> | 6, 7   |                       | 9       | ns   |

| tw6               | Pulse duration, WR                                                                                                                 | tWR              | 6      |                       | 40      | ns   |

| t <sub>w7</sub>   | Pulse duration, RD                                                                                                                 | t <sub>RD</sub>  | 7      |                       | 40      | ns   |

| t <sub>w8</sub>   | Pulse duration, MR                                                                                                                 | t <sub>MR</sub>  |        |                       | 1       | μs   |

| t <sub>su1</sub>  | Setup time, address valid before ADS↑                                                                                              | t <sub>AS</sub>  | 0.7    |                       |         |      |

| t <sub>su2</sub>  | Setup time, CS valid before ADS↑                                                                                                   | tCS              | 6, 7   |                       | 8       | ns   |

| t <sub>su3</sub>  | Setup time, data valid before WR1↑ or WR2↓                                                                                         | t <sub>DS</sub>  | 6      |                       | 15      | ns   |

| t <sub>su4</sub>  | Setup time, CTS↑ before midpoint of stop bit                                                                                       |                  | 17     |                       | 10      | ns   |

| t <sub>h1</sub>   | Hold time, address low after ADS↑                                                                                                  | <sup>t</sup> AH  | 6.7    |                       |         |      |

| t <sub>h2</sub>   | Hold time, CS valid after ADS↑                                                                                                     | <sup>t</sup> CH  | 6, 7   |                       | 0       | ns   |

| t <sub>h3</sub>   | Hold time, CS valid after WR1↑ or WR2↓                                                                                             | twcs             |        |                       | 10      |      |

| t <sub>h4</sub>   | Hold time, address valid after WR1↑ or WR2↓                                                                                        | t <sub>WA</sub>  | 6      |                       | 10      | ns   |

| t <sub>h5</sub>   | Hold time, data valid after WR1↑ or WR2↓                                                                                           | <sup>t</sup> DH  | 6      |                       | 5       | ns   |

| th6               | Hold time, chip select valid after RD1↑ or RD2↓                                                                                    | tRCS             | 7      |                       | 10      | ns   |

| t <sub>h7</sub>   | Hold time, address valid after RD1↑ or RD2↓                                                                                        | t <sub>RA</sub>  | 7      |                       | 20      | ns   |

| t <sub>d4</sub> † | Delay time, CS valid before WR1↓ or WR2↑                                                                                           | tcsw             | 6      |                       | 7       | no   |

| t <sub>d5</sub> † | Delay time, address valid before WR1↓ or WR2↑                                                                                      | tAW              | 0      |                       | 7       | ns   |

| t <sub>d6</sub> † | Delay time, write cycle, $\overline{\text{WR1}}\uparrow$ or $\overline{\text{WR2}}\downarrow$ to $\overline{\text{ADS}}\downarrow$ | tWC              | 6      |                       | 40      | ns   |

| t <sub>d7</sub> † | Delay time, CS valid to RD1↓ or RD2↑                                                                                               | tCSR             | 7      |                       | 7       |      |

| t <sub>d8</sub> † | Delay time, address valid to RD1↓ or RD2↑                                                                                          | t <sub>AR</sub>  | /      |                       | ,       | ns   |

| t <sub>d</sub> 9  | Delay time, read cycle, $\overline{\text{RD1}}\uparrow$ or $\overline{\text{RD2}}\downarrow$ to $\overline{\text{ADS}}\downarrow$  | tRC              | 7      |                       | 40      | ns   |

| t <sub>d10</sub>  | Delay time, RD1↓ or RD2↑ to data valid                                                                                             | tRVD             | 7      | $C_L = 75 \text{ pF}$ | 45      | ns   |

| t <sub>d11</sub>  | Delay time, RD1↑ or RD2↓ to floating data                                                                                          | tHZ              | 7      | $C_L = 75 \text{ pF}$ | 20      | ns   |

<sup>†</sup>Only applies when ADS is low

# system switching characteristics over recommended ranges of supply voltage and operating free-air temperature (see Note 7)

| PARAMETER                                                                                                            | ALT. SYMBOL      | FIGURE | TEST CONDITIONS        | MIN MAX | UNIT |

|----------------------------------------------------------------------------------------------------------------------|------------------|--------|------------------------|---------|------|

| $t_{dis(R)}$ Disable time, $\overline{RD1}\downarrow\uparrow$ or $RD2\uparrow\downarrow$ to $DDIS\uparrow\downarrow$ | t <sub>RDD</sub> | 7      | C <sub>L</sub> = 75 pF | 20      | ns   |

NOTE 7: Charge and discharge times are determined by VOL, VOH, and external loading.

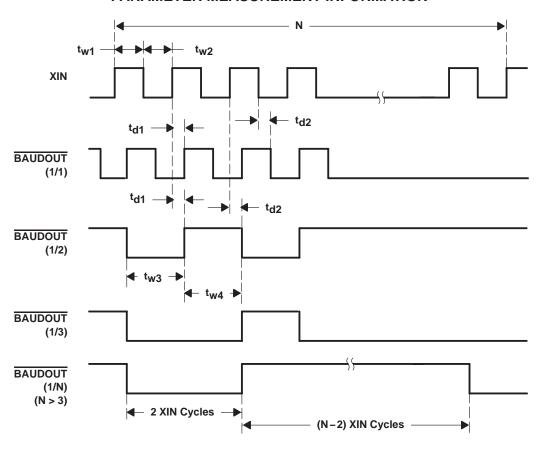

# baud generator switching characteristics over recommended ranges of supply voltage and operating free-air temperature, $C_L = 75 \text{ pF}$

|                 | PARAMETER                     | ALT. SYMBOL      | FIGURE | TEST CONDITIONS       | MIN | MAX | UNIT |

|-----------------|-------------------------------|------------------|--------|-----------------------|-----|-----|------|

| t <sub>w3</sub> | Pulse duration, BAUDOUT low   | tLW              | 5      | f = 16 MHz, CLK + 2,  | 50  |     |      |

| t <sub>w4</sub> | Pulse duration, BAUDOUT high  | tHW              | 5      | V <sub>CC</sub> = 5 V | 50  |     | ns   |

| t <sub>d1</sub> | Delay time, XIN↑ to BAUDOUT↑  | <sup>t</sup> BLD | 5      |                       |     | 45  | ns   |

| t <sub>d2</sub> | Delay time, XIN↑↓ to BAUDOUT↓ | <sup>t</sup> BHD | 5      |                       |     | 45  | ns   |

SLLS177H - MARCH 1994 - REVISED JANUARY 2006

# receiver switching characteristics over recommended ranges of supply voltage and operating free-air temperature (see Note 8)

|                  | PARAMETER                                                                     | ALT. SYMBOL       | FIGURE              | TEST CONDITIONS        | MIN | MAX | UNIT          |

|------------------|-------------------------------------------------------------------------------|-------------------|---------------------|------------------------|-----|-----|---------------|

| t <sub>d12</sub> | Delay time, RCLK to sample                                                    | tSCD              | 8                   |                        |     | 10  | ns            |

| t <sub>d13</sub> | Delay time, stop to set INTRPT or read RBR to LSI interrupt or stop to RXRDY↓ | <sup>t</sup> SINT | 8, 9, 10,<br>11, 12 |                        |     | 1   | RCLK<br>cycle |

| t <sub>d14</sub> | Delay time, read RBR/LSR to reset INTRPT                                      | <sup>t</sup> RINT | 8, 9, 10,<br>11, 12 | C <sub>L</sub> = 75 pF |     | 70  | ns            |

NOTE 8: In the FIFO mode, the read cycle (RC) = 425 ns (min) between reads of the receive FIFO and the status registers (interrupt identification register or line status register).

# transmitter switching characteristics over recommended ranges of supply voltage and operating free-air temperature

|                  | PARAMETER                                                              | ALT. SYMBOL      | FIGURE | TEST CONDITIONS        | MIN | MAX | UNIT              |

|------------------|------------------------------------------------------------------------|------------------|--------|------------------------|-----|-----|-------------------|

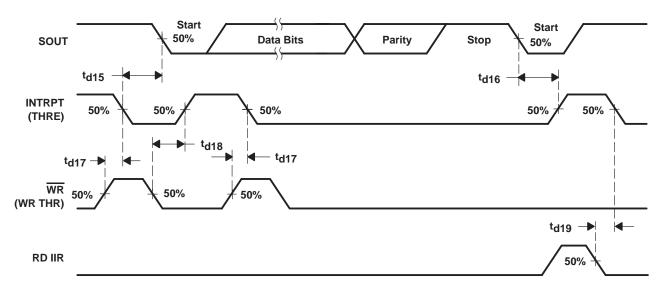

| <sup>t</sup> d15 | Delay time, initial write to transmit start                            | <sup>t</sup> IRS | 13     |                        | 8   | 24  | baudout cycles    |

| <sup>t</sup> d16 | Delay time, start to INTRPT                                            | <sup>t</sup> STI | 13     |                        | 8   | 10  | baudout cycles    |

| t <sub>d17</sub> | Delay time, WR (WR THR) to reset INTRPT                                | <sup>t</sup> HR  | 13     | C <sub>L</sub> = 75 pF |     | 50  | ns                |

| <sup>t</sup> d18 | Delay time, initial write to INTRPT (THRE <sup>†</sup> )               | <sup>t</sup> SI  | 13     |                        | 16  | 34  | baudout cycles    |

| t <sub>d19</sub> | Delay time, read IIR <sup>†</sup> to reset INTRPT (THRE <sup>†</sup> ) | <sup>t</sup> IR  | 13     | C <sub>L</sub> = 75 pF |     | 35  | ns                |

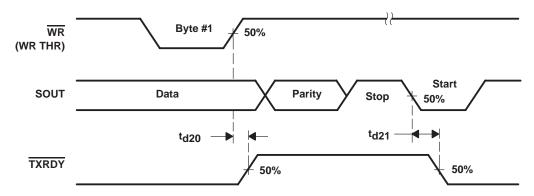

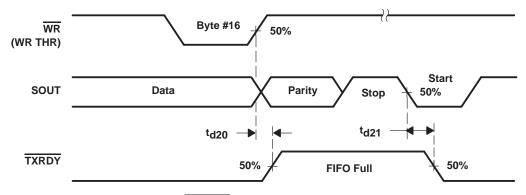

| t <sub>d20</sub> | Delay time, write to TXRDY inactive                                    | t <sub>WXI</sub> | 14,15  | C <sub>L</sub> = 75 pF |     | 35  | ns                |

| <sup>t</sup> d21 | Delay time, start to TXRDY active                                      | tSXA             | 14,15  | C <sub>L</sub> = 75 pF |     | 9   | baudout<br>cycles |

<sup>&</sup>lt;sup>†</sup> THRE = transmitter holding register empty; IIR = interrupt identification register.

# modem control switching characteristics over recommended ranges of supply voltage and operating free-air temperature, $C_1 = 75 \text{ pF}$

|                  | PARAMETER                                                                           | ALT. SYMBOL      | FIGURE | MIN MAX | UNIT              |

|------------------|-------------------------------------------------------------------------------------|------------------|--------|---------|-------------------|

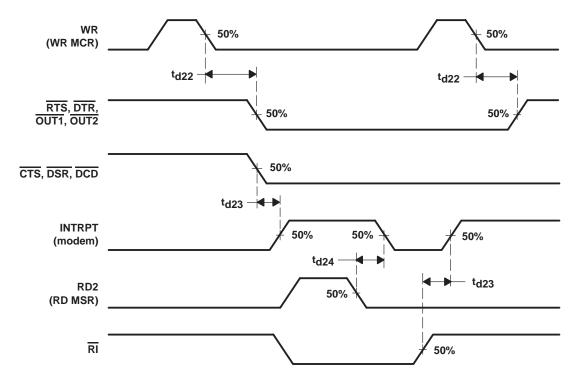

| t <sub>d22</sub> | Delay time, WR MCR to output                                                        | tMDO             | 16     | 50      | ns                |

| t <sub>d23</sub> | Delay time, modem interrupt to set INTRPT                                           | t <sub>SIM</sub> | 16     | 35      | ns                |

| t <sub>d24</sub> | Delay time, RD MSR to reset INTRPT                                                  | <sup>t</sup> RIM | 16     | 40      | ns                |

| td25             | Delay time, CTS low to SOUT↓                                                        |                  | 17     | 24      | baudout<br>cycles |

| <sup>t</sup> d26 | Delay time, RCV threshold byte to RTS↑                                              |                  | 18     | 2       | baudout<br>cycles |

| t <sub>d27</sub> | Delay time, read of last byte in receive FIFO to $\overline{\text{RTS}} \downarrow$ |                  | 18     | 2       | baudout<br>cycles |

| t <sub>d28</sub> | Delay time, first data bit of 16th character to RTS↑                                |                  | 19     | 2       | baudout<br>cycles |

| t <sub>d29</sub> | Delay time, RBRRD low to RTS↓                                                       |                  | 19     | 2       | baudout<br>cycles |

# PARAMETER MEASUREMENT INFORMATION

Figure 5. Baud Generator Timing Waveforms

# PARAMETER MEASUREMENT INFORMATION

† Applicable only when  $\overline{ADS}$  is low

Figure 6. Write Cycle Timing Waveforms

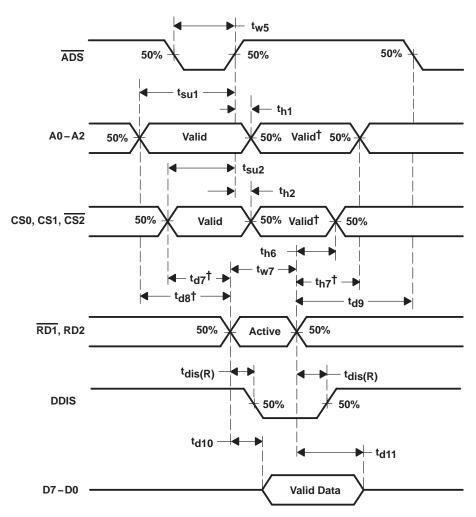

# PARAMETER MEASUREMENT INFORMATION

<sup>†</sup> Applicable only when  $\overline{\text{ADS}}$  is low

Figure 7. Read Cycle Timing Waveforms

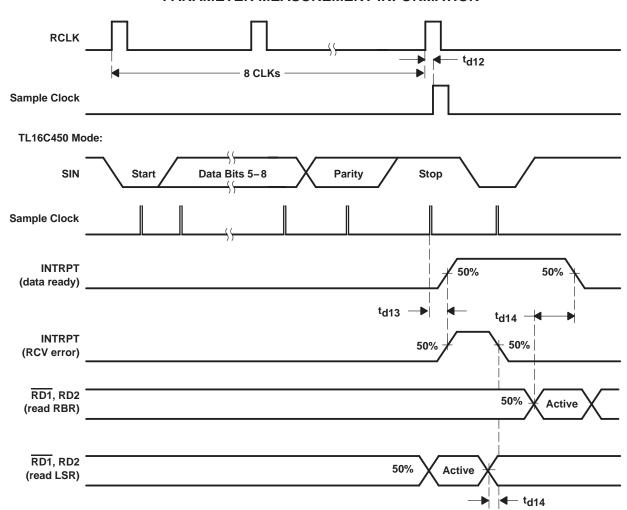

# PARAMETER MEASUREMENT INFORMATION

Figure 8. Receiver Timing Waveforms

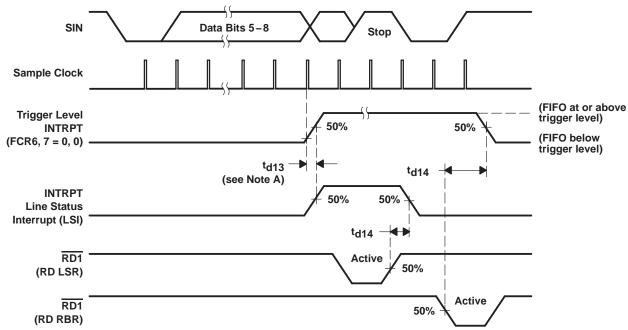

### PARAMETER MEASUREMENT INFORMATION

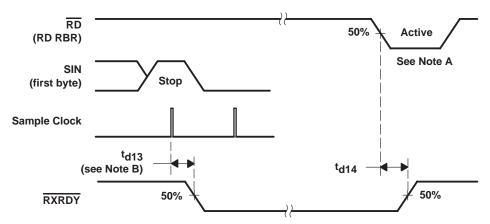

NOTE A: For a time-out interrupt,  $t_{d13} = 9$  RCLKs.

Figure 9. Receive FIFO First Byte (Sets DR Bit) Waveforms

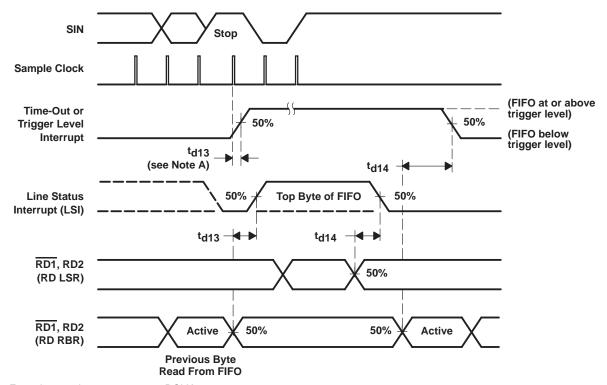

NOTE A: For a time-out interrupt,  $t_{d13} = 9$  RCLKs.

Figure 10. Receive FIFO Bytes Other Than the First Byte (DR Internal Bit Already Set) Waveforms

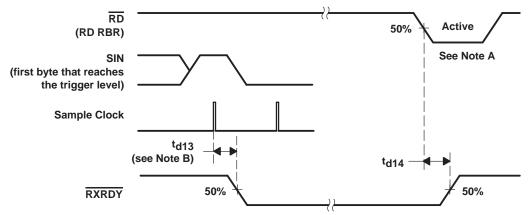

# PARAMETER MEASUREMENT INFORMATION

NOTE A: This is the reading of the last byte in the FIFO.

Figure 11. Receiver Ready (RXRDY) Waveforms, FCR0 = 0 or FCR0 = 1 and FCR3 = 0 (Mode 0)

NOTES: A. This is the reading of the last byte in the FIFO.

B. For a time-out interrupt,  $t_{d13} = 9$  RCLKs.

Figure 12. Receiver Ready (RXRDY) Waveforms, FCR0 = 1 and FCR3 = 1 (Mode 1)

# PARAMETER MEASUREMENT INFORMATION

**Figure 13. Transmitter Timing Waveforms**

Figure 14. Transmitter Ready (TXRDY) Waveforms, FCR0 = 0 or FCR0 = 1 and FCR3 = 0 (Mode 0)

Figure 15. Transmitter Ready (TXRDY) Waveforms, FCR0 = 1 and FCR3 = 1 (Mode 1)

# PARAMETER MEASUREMENT INFORMATION

**Figure 16. Modem Control Timing Waveforms**

Figure 17. CTS and SOUT Autoflow Control Timing (Start and Stop) Waveforms

Figure 18. Auto-RTS Timing for RCV Threshold of 1, 4, or 8 Waveforms

# PARAMETER MEASUREMENT INFORMATION

Figure 19. Auto-RTS Timing for RCV Threshold of 14 Waveforms

### **APPLICATION INFORMATION**

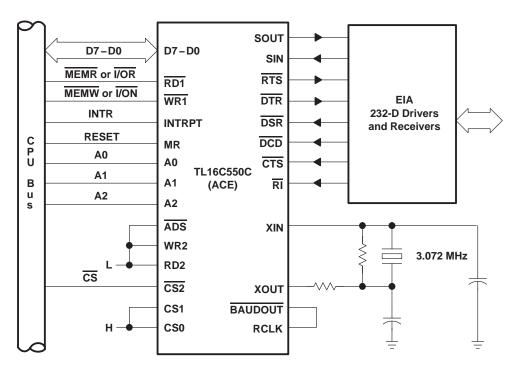

Figure 20. Basic TL16C550C Configuration

# **APPLICATION INFORMATION**

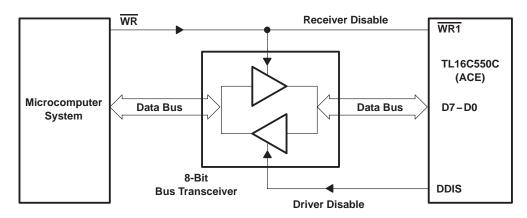

Figure 21. Typical Interface for a High Capacity Data Bus

# **APPLICATION INFORMATION**

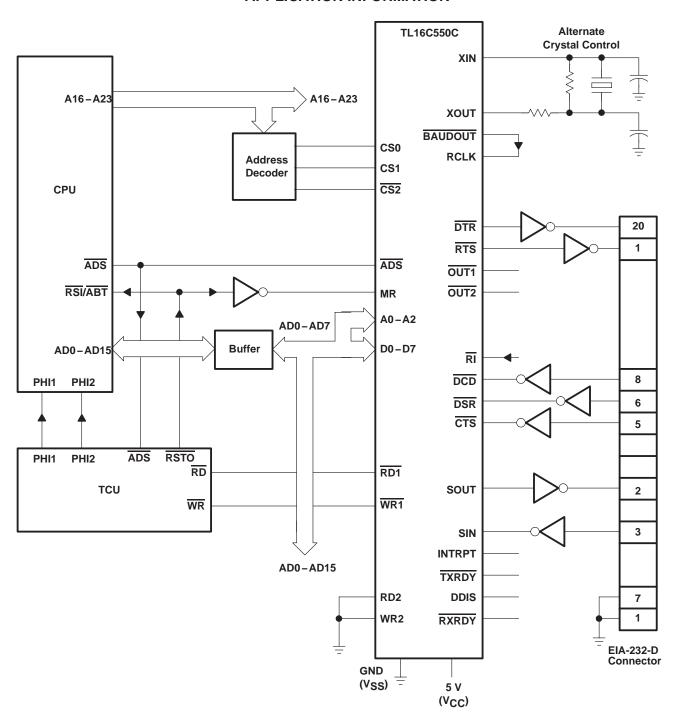

Figure 22. Typical TL16C550C Connection to a CPU

# **PRINCIPLES OF OPERATION**

**Table 1. Register Selection**

| DLAB† | A2 | A1 | A0 | REGISTER                                                     |  |

|-------|----|----|----|--------------------------------------------------------------|--|

| 0     | L  | L  | L  | Receiver buffer (read), transmitter holding register (write) |  |

| 0     | L  | L  | Н  | Interrupt enable register                                    |  |

| Х     | L  | Н  | L  | Interrupt identification register (read only)                |  |

| Х     | L  | Н  | L  | FIFO control register (write)                                |  |

| Х     | L  | Н  | Н  | Line control register                                        |  |

| Х     | Н  | L  | L  | Modem control register                                       |  |

| Х     | Н  | L  | Н  | Line status register                                         |  |

| Х     | Н  | Н  | L  | Modem status register                                        |  |

| Х     | Н  | Н  | Н  | Scratch register                                             |  |

| 1     | L  | L  | L  | Divisor latch (LSB)                                          |  |

| 1     | L  | L  | Н  | Divisor latch (MSB)                                          |  |

<sup>†</sup> The divisor latch access bit (DLAB) is the most significant bit of the line control register. The DLAB signal is controlled by writing to this bit location (see Table 4).

# **Table 2. ACE Reset Functions**

| REGISTER/SIGNAL                             | RESET CONTROL        | RESET STATE                                                                            |

|---------------------------------------------|----------------------|----------------------------------------------------------------------------------------|

| Interrupt enable register                   | Master reset         | All bits cleared (0-3 forced and 4-7 permanent)                                        |

| Interrupt identification register           | Master reset         | Bit 0 is set, bits 1, 2, 3, 6, and 7 are cleared, and bits 4-5 are permanently cleared |

| FIFO control register                       | Master reset         | All bits cleared                                                                       |

| Line control register                       | Master reset         | All bits cleared                                                                       |

| Modem control register                      | Master reset         | All bits cleared (6-7 permanent)                                                       |

| Line status register                        | Master reset         | Bits 5 and 6 are set; all other bits are cleared                                       |

| Modem status register                       | Master reset         | Bits 0-3 are cleared; bits 4-7 are input signals                                       |

| SOUT                                        | Master reset         | High                                                                                   |

| INTRPT (receiver error flag)                | Read LSR/MR          | Low                                                                                    |

| INTRPT (received data available)            | Read RBR/MR          | Low                                                                                    |

| INTRPT (transmitter holding register empty) | Read IR/write THR/MR | Low                                                                                    |

| INTRPT (modem status changes)               | Read MSR/MR          | Low                                                                                    |

| OUT2                                        | Master reset         | High                                                                                   |

| RTS                                         | Master reset         | High                                                                                   |

| DTR                                         | Master reset         | High                                                                                   |

| OUT1                                        | Master reset         | High                                                                                   |

| Scratch register                            | Master reset         | No effect                                                                              |

| Divisor latch (LSB and MSB) registers       | Master reset         | No effect                                                                              |

| Receiver buffer register                    | Master reset         | No effect                                                                              |

| Transmitter holding register                | Master reset         | No effect                                                                              |

| RCVR FIFO                                   | MR/FCR1−FCR0/∆FCR0   | All bits cleared                                                                       |

| XMIT FIFO                                   | MR/FCR2−FCR0/∆FCR0   | All bits cleared                                                                       |

### PRINCIPLES OF OPERATION

# accessible registers

The system programmer, using the CPU, has access to and control over any of the ACE registers that are summarized in Table 2. These registers control ACE operations, receive data, and transmit data. Descriptions of these registers follow Table 3.

**Table 3. Summary of Accessible Registers**

|            | REGISTER ADDRESS                                 |                                                       |                                                                |                                                   |                                                |                                             |                                        |                                              |                                              |                     |                           |                |

|------------|--------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------|------------------------------------------------|---------------------------------------------|----------------------------------------|----------------------------------------------|----------------------------------------------|---------------------|---------------------------|----------------|

|            | 0 DLAB = 0                                       | 0 DLAB = 0                                            | 1 DLAB = 0                                                     | 2                                                 | 2                                              | 3                                           | 4                                      | 5                                            | 6                                            | 7                   | 0 DLAB = 1                | 1 DLAB = 1     |

| BIT<br>NO. | Receiver<br>Buffer<br>Register<br>(Read<br>Only) | Transmitter<br>Holding<br>Register<br>(Write<br>Only) | Interrupt<br>Enable<br>Register                                | Interrupt<br>Ident.<br>Register<br>(Read<br>Only) | FIFO<br>Control<br>Register<br>(Write<br>Only) | Line<br>Control<br>Register                 | Modem<br>Control<br>Register           | Line<br>Status<br>Register                   | Modem<br>Status<br>Register                  | Scratch<br>Register | Divisor<br>Latch<br>(LSB) | Latch<br>(MSB) |

|            | RBR                                              | THR                                                   | IER                                                            | IIR                                               | FCR                                            | LCR                                         | MCR                                    | LSR                                          | MSR                                          | SCR                 | DLL                       | DLM            |

| 0          | Data Bit 0 <sup>†</sup>                          | Data Bit 0                                            | Enable<br>Received<br>Data<br>Available<br>Interrupt<br>(ERBI) | 0 if<br>Interrupt<br>Pending                      | FIFO<br>Enable                                 | Word<br>Length<br>Select<br>Bit 0<br>(WLS0) | Data<br>Terminal<br>Ready<br>(DTR)     | Data<br>Ready<br>(DR)                        | Delta<br>Clear<br>to Send<br>(ΔCTS)          | Bit 0               | Bit 0                     | Bit 8          |

| 1          | Data Bit 1                                       | Data Bit 1                                            | Enable Transmitter Holding Register Empty Interrupt (ETBEI)    | Interrupt<br>ID<br>Bit 1                          | Receiver<br>FIFO<br>Reset                      | Word<br>Length<br>Select<br>Bit 1<br>(WLS1) | Request<br>to Send<br>(RTS)            | Overrun<br>Error<br>(OE)                     | Delta Data Set Ready (\(\D\)SR)              | Bit 1               | Bit 1                     | Bit 9          |

| 2          | Data Bit 2                                       | Data Bit 2                                            | Enable Receiver Line Status Interrupt (ELSI)                   | Interrupt<br>ID<br>Bit 2                          | Transmitter<br>FIFO<br>Reset                   | Number<br>of<br>Stop Bits<br>(STB)          | OUT1                                   | Parity<br>Error<br>(PE)                      | Trailing<br>Edge Ring<br>Indicator<br>(TERI) | Bit 2               | Bit 2                     | Bit 10         |

| 3          | Data Bit 3                                       | Data Bit 3                                            | Enable<br>Modem<br>Status<br>Interrupt<br>(EDSSI)              | Interrupt<br>ID<br>Bit 3<br>(see<br>Note 9)       | DMA<br>Mode<br>Select                          | Parity<br>Enable<br>(PEN)                   | OUT2                                   | Framing<br>Error<br>(FE)                     | Delta<br>Data<br>Carrier<br>Detect<br>(ΔDCD) | Bit 3               | Bit 3                     | Bit 11         |

| 4          | Data Bit 4                                       | Data Bit 4                                            | 0                                                              | 0                                                 | Reserved                                       | Even<br>Parity<br>Select<br>(EPS)           | Loop                                   | Break<br>Interrupt<br>(BI)                   | Clear<br>to<br>Send<br>(CTS)                 | Bit 4               | Bit 4                     | Bit 12         |

| 5          | Data Bit 5                                       | Data Bit 5                                            | 0                                                              | 0                                                 | Reserved                                       | Stick<br>Parity                             | Autoflow<br>Control<br>Enable<br>(AFE) | Transmitter<br>Holding<br>Register<br>(THRE) | Data<br>Set<br>Ready<br>(DSR)                | Bit 5               | Bit 5                     | Bit 13         |

| 6          | Data Bit 6                                       | Data Bit 6                                            | 0                                                              | FIFOs<br>Enabled<br>(see<br>Note 9)               | Receiver<br>Trigger<br>(LSB)                   | Break<br>Control                            | 0                                      | Transmitter<br>Empty<br>(TEMT)               | Ring<br>Indicator<br>(RI)                    | Bit 6               | Bit 6                     | Bit 14         |