# Evaluation Board User Guide

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

## **Evaluating the AD5415 Serial Input, Dual-Channel Current Output DAC**

#### **FEATURES**

Full-featured evaluation board for the AD5415

Graphic user interface software for board control and data analysis

Connector to EVAL-SDP-CB1Z system demonstration platform board

Various power supply options

#### **APPLICATIONS**

Portable battery-powered applications

Waveform generators

Analog processing

Instrumentation applications

Programmable amplifiers and attenuators

Digitally controlled calibration

Programmable filters and oscillators

Composite video

Ultrasound

Gain, offset, and voltage trimming

#### **GENERAL DESCRIPTION**

The AD5415 is a CMOS, 12-bit, dual-channel, current output digital-to-analog converter. This device operates from a 2.5 V to

5.5 V power supply, making it suited to battery-powered and other applications.

As a result of being manufactured on a CMOS submicron process, this part offers excellent four-quadrant multiplication characteristics, with large signal multiplying bandwidths of 10 MHz.

The applied external reference input voltage ( $V_{\text{REFX}}$ ) determines the full-scale output current. An integrated feedback resistor ( $R_{\text{FBX}}$ ) provides temperature tracking and full-scale voltage output when combined with an external current-to-voltage precision amplifier. In addition, this device contains the four-quadrant resistors necessary for bipolar operation and other configuration modes.

This DAC uses a double-buffered, 3-wire serial interface that is compatible with SPI, QSPI™, MICROWIRE®, and most DSP interface standards. In addition, a serial data out pin (SDO) allows daisy-chaining when multiple packages are used. Data readback allows the user to read the contents of the DAC register via the SDO pin. On power-up, the internal shift register and latches are filled with 0s, and the DAC outputs are at zero scale. The AD5415 DAC is available in a 24-lead TSSOP package.

The evaluation board, EV-AD5415/49SDZ, is available for evaluating the performance of the AD5415 DAC.

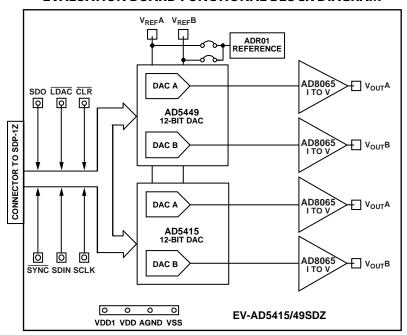

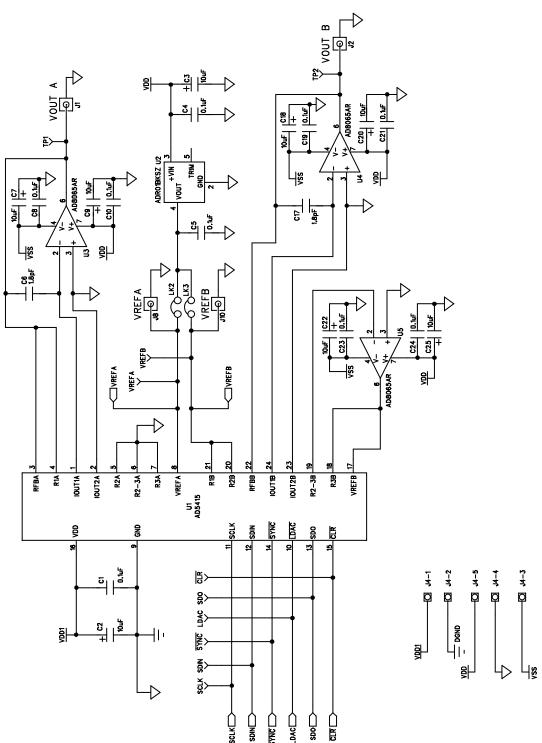

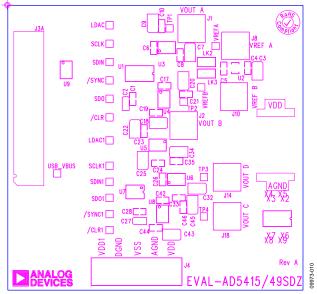

#### **EVALUATION BOARD FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **TABLE OF CONTENTS**

| Features1                                                 |

|-----------------------------------------------------------|

| Applications1                                             |

| General Description1                                      |

| Evaluation Board Functional Block Diagram1                |

| Revision History2                                         |

| Evaluation Board3                                         |

| System Demonstration Platform                             |

| EVAL-AD5415/AD5449SDZ to SPORT Interface                  |

| Operating the Evaluation Board3                           |

| Serial Interface                                          |

| Microprocessor Interfacing                                |

| REVISION HISTORY                                          |

| 5/13—Rev. B to Rev. C                                     |

| Changed EVAL-AD5415SDZ to EV-AD5415/49SDZ                 |

| Universal                                                 |

| 3/12—Rev. A to Rev. B                                     |

| Changed EVAL-AD5415/AD5449SDZ to EVAL-AD5415SDZ           |

| Throughout1                                               |

| Change to Figure 11                                       |

| Changed ADSP-BF5xx to ADSP-BF527 Throughout 3             |

| Change to Figure 23                                       |

| Changes to Figure 3 and Installing the Software Section 4 |

| Changes to Using the Evaluation Board Software Section 5  |

| Changes to Evaluation Board Schematics and Artwork        |

| Evaluation Board Software                | 4  |

|------------------------------------------|----|

| Installing the Software                  | 4  |

| Running the Software                     | 4  |

| Using the Evaluation Board Software      | 5  |

| Evaluation Board Functions and Registers | 5  |

| Evaluation Board Schematics and Artwork  | 8  |

| Schematics                               | 8  |

| Evaluation Board Layout                  | 10 |

| Related Links                            | 11 |

#### 6/11—Rev. 0 to Rev. A

3/10—Revision 0: Initial Version

#### **EVALUATION BOARD**

The EV-AD5415/49SDZ board consists of an AD5449 DAC, an AD5415 DAC, and AD8065 current-to-voltage amplifiers. Included on the evaluation board is a 10 V reference, the ADR01. An external reference can also be applied via an SMB input. The evaluation kit consists of a CD-ROM with self-installing PC software to control the DAC. The software allows the user to write a code to the device.

The EV-AD5415/49SDZ board is used in conjunction with the EVAL-SDP-CB1Z system demonstration platform (SDP) board available from Analog Devices, Inc., which is purchased separately from the evaluation board. The USB-to-SPI communication to the AD5415 is completed using this Blackfin\*-based demonstration board. The software offers a waveform generator.

#### SYSTEM DEMONSTRATION PLATFORM

The SDP is a hardware and software evaluation tool for use in conjunction with product evaluation boards. The SDP board is based on the Blackfin ADSP-BF527 processor with USB connectivity to the PC through a USB 2.0 high speed port. For more information about this device, see the system demonstration platform web page at www.analog.com/EVAL-SDP-CB1Z.

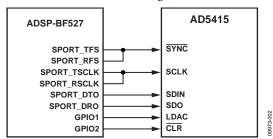

#### **EV-AD5415/49SDZ TO SPORT INTERFACE**

The Analog Devices SDP has one SPORT serial port. The SPORT interface is used to control the AD5415, allowing clock frequencies of up to 30 MHz.

#### **OPERATING THE EVALUATION BOARD**

The board requires  $\pm 12$  V and 5 V supplies. The +12 V V<sub>DD</sub> and -12 V V<sub>SS</sub> are used to power the output amplifier; the 5 V supply is used to power the DAC (V<sub>DD</sub>) and transceivers (V<sub>CC</sub>).

Both supplies are decoupled to their respective ground plane with 10  $\mu F$  tantalum and 0.1  $\mu F$  ceramic capacitors.

#### **SERIAL INTERFACE**

The AD5415 has an interface that is compatible with SPI, QSPI, MICROWIRE, and most DSP interface standards. Data is written to the device in 16-bit words. Each 16-bit word consists of four control bits and 12 data bits for the AD5415. Control bits allow control of various functions on the DAC.

#### MICROPROCESSOR INTERFACING

Microprocessor interfacing to the AD5415 DAC is through a serial bus that uses a standard protocol compatible with microcontrollers and DSP processors.

The SDP is a hardware and software platform that provides a means to communicate from the PC to Analog Devices products and systems that require digital control and/or readback. The SDP has a Blackfin processor (ADSP-BF527) at its core.

The ADSP-BF527 processor incorporates channel synchronous serial ports (SPORT) and general-purpose input/output (GPIO) pins. A serial interface between the Blackfin processor and the AD5415 DAC is shown in Figure 2.

For more details about the system demonstration platform, see the EVAL-SDP-CB1Z at www.analog.com/EVAL-SDP-CB1Z.

Figure 2. ADSP-BF527-to-AD5415 Interface

#### **EVALUATION BOARD SOFTWARE**

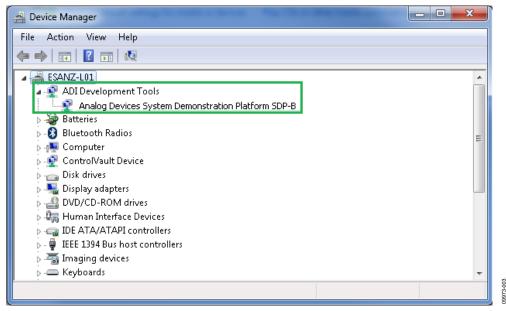

Figure 3. Device Manager Showing the SDP Board Connected

#### INSTALLING THE SOFTWARE

The EV-AD5415/49SDZ kit includes the software and drivers on a CD. To install the software, follow these steps:

- 1. Install the software before connecting the SDP board to the USB port of the PC.

- 2. Start the Windows® operating system and insert the EV-AD5415/49SDZ kit CD.

- 3. Download the EV-AD5415/49SDZ LabVIEW™ software. The correct driver for the SDP board, SDPDriversNET, should download automatically after LabVIEW is downloaded, supporting both 32-bit and 64-bit systems. However, if the drivers do not download automatically, the driver executable file can also be found in the All Programs/Analog Devices folder from the Start menu. Follow the on-screen prompts to install it.

- 4. After installation of the software and drivers is complete, plug the EV-AD5415/49SDZ into the SDP board and the SDP board into the PC using the USB cable included in the kit. Confirm that the SDP board has been recognized and is displayed in the Device Manager dialog box by clicking Start/Control Panel/System (Hardware)/Device Manager (see Figure 3).

- 5. When the software detects the evaluation board, proceed through any dialog boxes that appear to finalize the

installation (Found New Hardware Wizard/Install the Software Automatically and so on).

#### **RUNNING THE SOFTWARE**

To run the evaluation board program, do the following:

- Click Start/All Programs/Analog Devices/EV-AD5415/49SDZ.

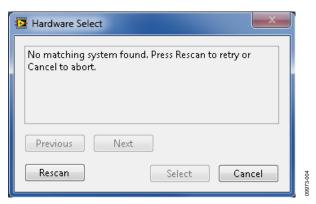

- If the SDP board is not connected to the USB port when the software is launched, a connectivity error displays (see Figure 4.). Simply connect the evaluation board to the USB port of the PC, wait a few seconds, click **Rescan**, and follow the instructions.

Figure 4. Connectivity Error

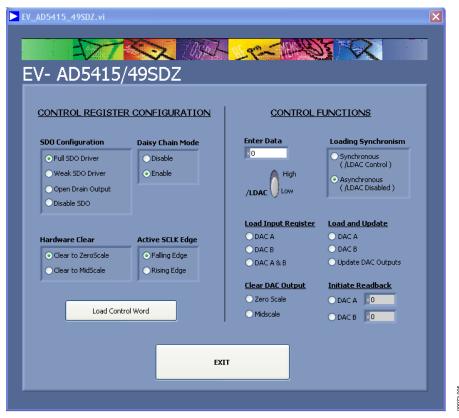

# **USING THE EVALUATION BOARD SOFTWARE**

Figure 5. Evaluation Software Window

To operate the evaluation software,

- Ensure that the PC is connected to the system demonstration platform, EVAL-SDP-CB1Z, and the EVAL-SDP-CB1Z to the evaluation board via the USB cable provided in the kit.

- Run the program file from Start/All Programs/Analog

Devices. The EV-AD5415/49SDZwindow opens, as shown in Figure 5.

# **EVALUATION BOARD FUNCTIONS AND REGISTERS**

From the AD5415 evaluation software window, you can write a data-word to either DAC A or DAC B or both DACs. Type the 12-bit data-word in hexadecimal format in the **Enter Data** box of the **CONTROL FUNCTIONS** panel.

The AD5415 evaluation software window allows you to evaluate all the functions of the AD5415.

#### Example 1

#### Asynchronous Mode

Complete the following steps in the **CONTROL FUNCTIONS** panel of the evaluation software window:

Select /LDAC High to tie the load DAC input high for the asynchronous loading mode, specify quarter scale (0x400, 1024 decimal) in the Enter Data box, and select DAC A under Load Input Register. The value is kept in the register, and the DAC does not update until you click Update DAC Outputs under Load and Update. The expected output obtained is

$$V_{OUT} = -V_{REF} \times \frac{D}{4096} = -10 \times \frac{1024}{4096} = -2.5 V$$

2. Select **Zero Scale** under **Clear DAC Output** to clear the DAC outputs to 0 V.

#### **Synchronous Mode**

Change Loading Synchronism to Synchronous (/LDAC Control), write 0xC00 (3072 decimal) in the Enter Data box, and select DAC A under Load Input Register. The output does not change until you select /LDAC Low. The expected output for this case is

$$V_{OUT} = -V_{REF} \times \frac{D}{4096} = -10 \times \frac{3072}{4096} = -7.5 V$$

2. Click **DAC A** under **Initiate Readback** to confirm that the last value loaded in the DAC A register is the same as the one read and shown in the **DAC A** numeric indicator text box.

#### Example 2

#### **Control Register Configuration**

1. Working in asynchronous mode, load and update DAC B with full scale (0xFFF). The expected output is

$$V_{OUT} = \left(V_{REF} \times \frac{D}{2^{n-1}}\right) - V_{REF} = \left(10 \times \frac{4095}{2048}\right) - 10 = +10 \text{ V}$$

- Click Clear to MidScale under Hardware Clear and Disable under Daisy Chain Mode in the CONTROL REGISTER CONFIGURATION panel. Next, click the Load Control Word button. The DAC B outputs change to midscale (0x800), and the signal in the SDO pin maintains a constant value until the daisy-chain mode is enabled again.

- 3. Click **EXIT** when you complete your evaluation.

Table 1 and Table 2 describe the control functions and control registers, respectively. The disable daisy-chain and clock data to shift register on rising edge mode functions are loaded with the control register. Although they can also be implemented loading the specified control bits for these functions, they are only available within the control word for the software provided.

#### **Table 1. Control Functions**

|                                                    | 14014 17 0041011 44141010                                                                                             |  |  |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| Control Function                                   | Description                                                                                                           |  |  |

| Load and Update, DAC A                             | Loads the DAC A register with the entered data-word and updates the DAC A output, irrespective of the state of /LDAC. |  |  |

| Initiate Readback, DAC A                           | Reads the contents of the DAC A register and displays the value on screen.                                            |  |  |

| Load Input Register, DAC A                         | Loads the DAC A input register with the entered data-word. The DAC A output is updated only if /LDAC is low.          |  |  |

| Load and Update, DAC B                             | Loads the DAC B register with the entered data-word and updates the DAC B output, irrespective of the state of /LDAC. |  |  |

| Initiate Readback, DAC B                           | Reads the contents of the DAC B register and displays the value on screen.                                            |  |  |

| Load Input Register, DAC B                         | Loads the DAC B input register with the entered data-word. The DAC B output is updated only if <b>/LDAC</b> is low.   |  |  |

| Load and Update, Update DAC<br>Outputs (Both DACs) | Updates both DAC outputs with the entered data-word, irrespective of the state of /LDAC.                              |  |  |

| Load Input Register, DAC A and DAC B               | Loads the input registers of both DACs with the entered data-word. Both outputs are updated only if /LDAC is low.     |  |  |

| Clear DAC Output, Zero Scale<br>(Both Outputs)     | Loads both DACs and updates their outputs with zero-scale code, irrespective of the state of /LDAC.                   |  |  |

| Clear DAC Output, Midscale<br>(Both Outputs)       | Loads both DACs and updates their outputs with midscale code, irrespective of the state of /LDAC.                     |  |  |

#### Table 2.

| Table 2.          |                                                                                                                                                                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Register  | Description                                                                                                                                                                                                                                                  |

| SDO Configuration | The SDO bits enable you to control the SDO output driver strength, disable the SDO output, or configure the SDO as an open-drain driver. The strength of the SDO driver affects timing. A stronger SDO output driver allows a faster clock cycle to be used. |

| Daisy Chain Mode  | Enables or disables daisy-chain functionality.                                                                                                                                                                                                               |

| Hardware Clear    | Sets the value to which the outputs are cleared on the falling edge of the CLR signal. The value can be either zero scale or midscale.                                                                                                                       |

| Active SCLK Edge  | Selects the edge of SCLK on which data is clocked into the input register. Data is clocked out from SDO on the opposite edge.                                                                                                                                |

| Load Control Word | Loads control register mode.                                                                                                                                                                                                                                 |

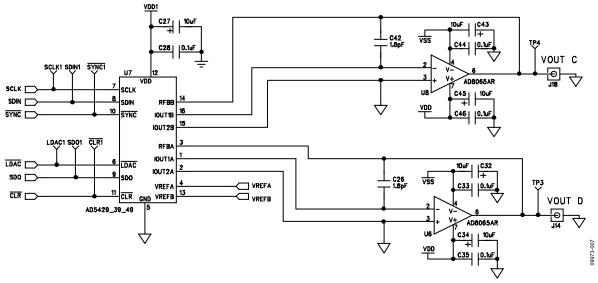

# **EVALUATION BOARD SCHEMATICS AND ARTWORK SCHEMATICS**

900-87660

Figure 6. Evaluation Board Schematic Part A (AD5415)

VIN: Use this pin to power

the SDP requires 5V 200mA

NC VIN

Figure 7. Evaluation Board Schematic Part B (AD5449)

BMODE1: Pull up with a 10K resistor to set SDP to boot from a SPI FLASH on the daughter board

60 59 RESET\_IN UART\_RX GND BMODE1 UART\_TX Board ID EEPROM (24LC64) must be on I2C bus 0, ODE1 61 62 63 GND 64 NC 65 NC 66 NC 66 3.3V\_BF | 57 NC 56 NC 55 NC 554 NC 53 NC 53 NC 51 NC 50 NC 49 TMR\_A 47 GPIO6 U9 SDP STANDARD CONNECTOR VCC WP SCL SDA ĄΟ NC NC NC GND NC NC TMR\_D TMR\_B GPIO7 24LC64 TMR B 74 GPI07 GPI 48 I MR \_ A

47 T MR \_ A

47 T MR \_ A

47 T MR \_ A

46 GPI06

45 GPI04 GE

44 GPI04 INPUT

42 GPI00

43 GPI00

41 SDA\_1

40 SDA\_1

40 SDA\_1

40 SDA\_1

40 SDA\_1

38 SPI\_SEL1/SPI\_SS

37 SPI\_SEL\_C

36 SPI\_SEL\_B

35 SPORT\_DT3\*

33 SPORT\_DT3\*

33 SPORT\_DT3\*

33 SPORT\_DT2\*

33 SPORT\_DT2\*

37 SPORT\_DT2\*

37 SPORT\_DT3\*

39 SPORT\_DT1\*

29 SPORT\_DT1\*

29 SPORT\_DR1

29 SPORT\_DR1

29 SPORT\_DR3\*

29 PAR\_SS1

24 PAR\_AS1

27 PAR\_FS1

27 PAR\_AS

27 PAR\_AS1

28 PAR\_AS1

29 PAR\_AS1

21 PAR\_CS

21 PAR\_CS **TIMERS** GENERAL INPUT/OUTPUT CLR \_ LDAC 12C Main I2C bus (Connected to blackfin TWI — Pull up resistors not required) I2C bus 1 is common across both connectors on SDP - Pull up resistors required SPI (connected to blackfin GPIO - use I2C\_O first) STNC SPORT PAR\_FS2

PAR\_A0

PAR\_A2

GND

PAR\_INT

PAR\_WR

PAR\_D0

PAR\_D4

GND

PAR\_D6

PAR\_D6 PAR DI PARALLEL PORT GND PAR\_D7 PAR\_D9 PAR\_D12 | 103 PAR\_D15 | 111 \*PAR\_D16 | 112 \*PAR\_D20 | 113 \*PAR\_D20 | 113 \*PAR\_D20 | 115 VIO(+3.3V) | 117 GND | 118 GND | 118 GND | 119 DP NC | 120 USB\_VBUS 3.3V\_BF 7 PAR\_D23\* 5 GND 4 USB\_VBUS 3 GND 2 GND -PAR D23 VIO: USE to set IO voltage max draw 20mA

Figure 8. Evaluation Board Schematic Part C (SDP Board) Rev. C | Page 9 of 12

\*NC on BLACKFIN SDP

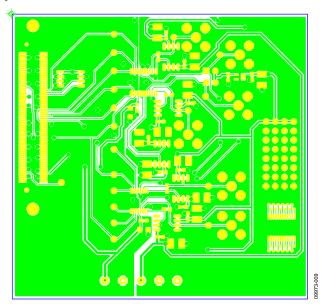

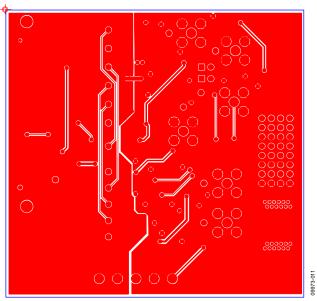

#### **EVALUATION BOARD LAYOUT**

Figure 9. Component-Side Artwork

Figure 10. Silkscreen—Component-Side View (Top)

Figure 11. Solder-Side Artwork

#### **RELATED LINKS**

| Resource | Description                                                                                                         |

|----------|---------------------------------------------------------------------------------------------------------------------|

| AD5415   | Product Page, AD5415 Dual 12-Bit, High Bandwidth, Multiplying DAC with Four-Quadrant Resistors and Serial Interface |

| AD5449   | Product Page, AD5449 Dual 12-Bit, High Bandwidth Multiplying DAC with Serial Interface                              |

| ADR01    | Product Page, ADR01 Ultracompact, Precision 10.0 V Voltage Reference                                                |

| AD8065   | Product Page, AD8065 High Performance, 145 MHz <i>FastFET™</i> Op Amp                                               |

UG-296

**Evaluation Board User Guide**

#### **NOTES**

#### ESD Caution

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### Legal Terms and Conditions

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2010–2013 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. UG09973-0-5/13(C)

www.analog.com

# AMEYA360 Components Supply Platform

# **Authorized Distribution Brand:**

### Website:

Welcome to visit www.ameya360.com

#### Contact Us:

#### > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

#### > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

#### Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com