# SPI configurable stepper and DC multi motor driver

Data brief

### **Features**

- Operating voltage supply from 13 V to 40 V

- 4 full bridge driver configurable in multi-motor application to drive:

- 2 DC and 1 stepper motor

- 4 DC motor

- Bridge 1 and 2 ( $R_{DSon} = 0.60 \Omega$ ) can be configured to work as:

- Dual full bridge driver

- Super DC driver

- 2 half bridge driver

- 1 super half bridge

- 2 power switches

- 1 super power switch

- Bridge 3 and 4 ( $R_{DSon} = 0.75 \Omega$ ) can be configured to work as:

- Same as bridges 1 and 2, listed above

- 2 buck regulators (bridge 3)

- 1 super buck regulator

- Battery charger (bridge 4)

- Power supply management

- One switching buck regulator

- One switching regulator controller

- One linear regulator

- One battery charger

- Fully protected through

- Thermal warning and shutdown

- Overcurrent protection

- Undervoltage lock-out

- 16 bit SPI interface

- Programmable watchdog function

- Integrated power sequencing and supervisory functions with fault signaling through serial interface and external reset pin

- Very low power dissipation in shut-down mode (~35 mW)

- Aux features

- Multi-channels 9 bit ADC

- 2 operational amplifiers

- Digital comparator

- 2 low voltage power switches

- 3 general purpose PWM generators

- 14 GPIOs

## **Description**

The L6460 is optimized to control and drive multimotor system providing a unique level of integration in term of control, power and auxiliary features. Thanks to the high configurability L6460 can be customized to drive different motor architectures and to optimize the number of embedded features, such as the voltage regulators, the high precision A/D converter, the OP amp and the voltage comparators. The possibility to drive simultaneously stepper and DC motor makes L6460 the ideal solution for all the application featuring multi motors.

Table 1. Device summary

| Order code | Package | Packing |

|------------|---------|---------|

| L6460      | TQFP64  | Tray    |

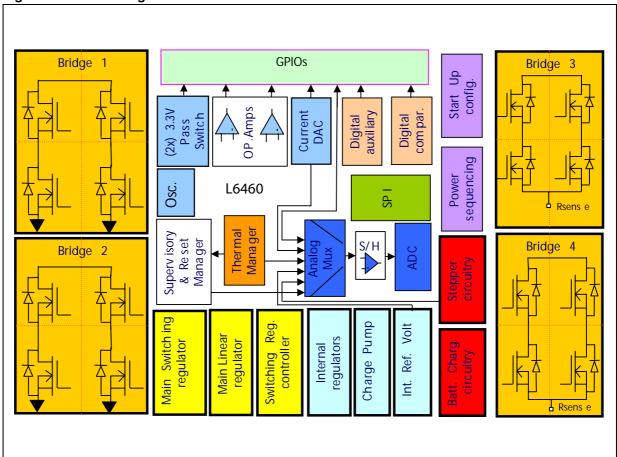

Block diagram L6460

# 1 Block diagram

Figure 1. Block diagram

# 1.1 Functional description

L6460 offers the possibility to control and power multi motor systems, through the management of simultaneous driving of stepper and DC motor. A number of features can be configured through the digital interface (SPI), including 3 voltage regulators, 1 high precision A/D converter, 2 operational amplifiers and 14 configurable GPIOs.

The high flexibility allows the possibility to configure two, one full or half bridge to work as power stage featuring additional voltage buck regulators.

L6460 Block diagram

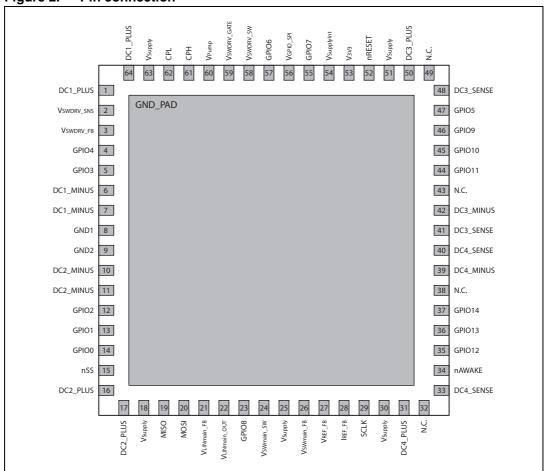

# 1.2 Pin connection

Figure 2. Pin connection

# 1.3 Pin list

Table 2. Pins configuration

| Pin # | Pin name               | Description                                 | Туре                        |

|-------|------------------------|---------------------------------------------|-----------------------------|

| 1     | DC1_PLUS               | Bridge 1 phase "plus" output                | Output                      |

| 2     | V <sub>SWDRV_SNS</sub> | Switching regulator controller sense        | Analog input                |

| 3     | V <sub>SWDRV_FB</sub>  | Switching regulator controller feedback     | Analog input                |

| 4     | GPIO4                  | General purpose I/O                         | Analog In/Out - CMOS bi-dir |

| 5     | GPIO3                  | General purpose I/O                         | Analog In/Out - CMOS bi-dir |

| 6     | DC1_MINUS              | Bridge 1 phase "minus" output               | Output                      |

| 7     | DC1_MINUS              | Bridge 1 phase "minus" output               | Output                      |

| 8     | GND1                   | Ground pin for bridge1 <sup>(1)(2)(3)</sup> | Power/digital               |

| 9     | GND2                   | Ground pin for bridge2 <sup>(1)(2)(3)</sup> | Power/digital               |

Block diagram L6460

Table 2. Pins configuration (continued)

| Pin # | Pin name                 | Description                               | Туре                        |

|-------|--------------------------|-------------------------------------------|-----------------------------|

| 10    | DC2_MINUS                | Bridge 2 phase "minus" output             | Output                      |

| 11    | DC2_MINUS                | Bridge 2 phase "minus" output             | Output                      |

| 12    | GPIO2                    | General purpose I/O                       | Analog In/Out - CMOS bi-dir |

| 13    | GPIO1                    | General purpose I/O                       | Analog In/Out - CMOS bi-dir |

| 14    | GPIO0                    | General purpose I/O                       | Analog Input - CMOS input   |

| 15    | nSS                      | SPI chip select pin                       | CMOS input                  |

| 16    | DC2_PLUS                 | Bridge 2 phase "plus" output              | Output                      |

| 17    | DC2_PLUS                 | Bridge 2 phase "plus" output              | Output                      |

| 18    | V <sub>Supply</sub>      | Main voltage supply                       | Power input                 |

| 19    | MISO                     | SPI serial data output                    | CMOS output                 |

| 20    | MOSI                     | SPI serial data input                     | CMOS input                  |

| 21    | V <sub>LINmain_FB</sub>  | Linear main regulator feedback            | Analog input                |

| 22    | V <sub>LINmain_OUT</sub> | Linear main regulator output              | Power output                |

| 23    | GPIO 8                   | General purpose I/O                       | Analog In/Out - CMOS bi-dir |

| 24    | V <sub>SWmain_SW</sub>   | Main switching regulator switching output | Power output                |

| 25    | V <sub>Supply</sub>      | Main voltage supply                       | Power Input                 |

| 26    | V <sub>SWmain_FB</sub>   | Main switching regulator feedback pin     | Analog input                |

| 27    | V <sub>REF_FB</sub>      | Regulator voltage feedback                | Analog input                |

| 28    | I <sub>REF_FB</sub>      | Regulator current feedback                | Analog input                |

| 29    | SCLK                     | SPI input clock pin                       | CMOS input                  |

| 30    | $V_{Supply}$             | Main voltage supply                       | Power input                 |

| 31    | DC4_PLUS                 | Bridge 4 phase "plus" output              | Output                      |

| 32    | N.C.                     | Not connected                             |                             |

| 33    | DC4_SENSE                | Bridge 4 sense output <sup>(4)</sup>      | Output                      |

| 34    | nAWAKE                   | Device wake up                            | CMOS input                  |

| 35    | GPIO12                   | General purpose I/O                       | Analog In/Out - CMOS bi-dir |

| 36    | GPIO13                   | General purpose I/O                       | Analog In/Out - CMOS bi-dir |

| 37    | GPIO14                   | General purpose I/O                       | Analog In/Out - CMOS bi-dir |

| 38    | N.C.                     | Not connected                             |                             |

| 39    | DC4_MINUS                | Bridge 4 phase "minus" output             | Output                      |

| 40    | DC4_SENSE                | Bridge 4 sense output <sup>(4)</sup>      | Output                      |

| 41    | DC3_SENSE                | Bridge 3 sense output <sup>(4)</sup>      | Output                      |

| 42    | DC3_MINUS                | Bridge 3 phase "minus" output             | Output                      |

| 43    | N.C.                     | Not connected                             |                             |

| 44    | GPIO11                   | General purpose I/O                       | Analog In/Out - CMOS bi-dir |

L6460 Block diagram

Table 2. Pins configuration (continued)

| Pin # | Pin name                | Description                                 | Туре                        |

|-------|-------------------------|---------------------------------------------|-----------------------------|

| 45    | GPIO10                  | General purpose I/O                         | Analog In/Out - CMOS bi-dir |

| 46    | GPIO9                   | General purpose I/O                         | Analog In/Out - CMOS bi-dir |

| 47    | GPIO5                   | General purpose I/O                         | Analog In/Out - CMOS bi-dir |

| 48    | DC3_SENSE               | Bridge 3 sense output <sup>(4)</sup>        | Output                      |

| 49    | N.C.                    | Not connected                               |                             |

| 50    | DC3_PLUS                | Bridge 3 phase "plus" output                | Output                      |

| 51    | V <sub>Supply</sub>     | Main voltage supply                         | Power input                 |

| 52    | nRESET                  | Open drain system reset pin                 | CMOS Input/output           |

| 53    | V <sub>3v3</sub>        | Internal 3.3 volt regulator                 | Power Input/output          |

| 54    | V <sub>SupplyInt</sub>  | Internal voltage supply                     | Power Input                 |

| 55    | GPIO7                   | General purpose I/O                         | Analog In/Out - CMOS bi-dir |

| 56    | V <sub>GPIO_SPI</sub>   | Low voltage pins power supply               | Power input                 |

| 57    | GPIO6                   | General purpose I/O                         | Analog In/Out - CMOS bi-dir |

| 58    | V <sub>SWDRV_SW</sub>   | Switching regulator controller source input | Power input                 |

| 59    | V <sub>SWDRV_GATE</sub> | Switching driver gate drive pin             | Analog output               |

| 60    | $V_{Pump}$              | Charge pump voltage                         | Power Input/output          |

| 61    | CPH                     | Charge pump high switch pin                 | Power Input/output          |

| 62    | CPL                     | Charge pump low switch pin                  | Power Input/output          |

| 63    | V <sub>Supply</sub>     | Main voltage supply                         | Power input                 |

| 64    | DC1_plus                | Bridge 1 phase "plus" output                | Output                      |

| E_Pad | GND_PAD                 | (1)(2)(3)                                   |                             |

<sup>1.</sup> These pins must be connected all together to a unique PCB ground.

Bridges1 and 2 have 2 ground pads: one is bonded to the relative ground pin (GND1 or GND2) and the

other is connected to exposed pad (E\_Pad) ground ring. This makes the bond wires testing possible by

forcing a current between E-Pad and GND1 or GND2 pins and using the other pin as sense pin to measure

the resistance of E-Pad bonding. (N.B: grounds of two bridges are internally connected together).

<sup>3.</sup> The analog ground is connected to exposed pad E-Pad.

<sup>4.</sup> The pin must be tied to ground if bridge is not used as a stepper motor.

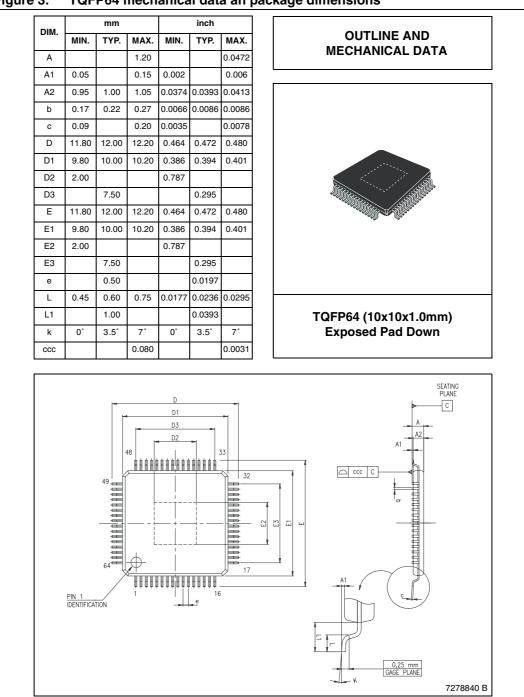

# 2 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

Figure 3. TQFP64 mechanical data an package dimensions

L6460 Revision history

# 3 Revision history

Table 3. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 30-Oct-2009 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

8/8

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 16587 Rev 1

# AMEYA360 Components Supply Platform

# **Authorized Distribution Brand:**

## Website:

Welcome to visit www.ameya360.com

## Contact Us:

## Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

## > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

# Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com