SBOS424B-MARCH 2008-REVISED SEPTEMBER 2008

# Zerø-Drift PROGRAMMABLE GAIN AMPLIFIER with MUX

#### **FEATURES**

- Rail-to-Rail Input/Output

- Offset: 25μV (typ), 100μV (max)

- Zerø Drift: 0.35μV/°C (typ), 1.2μV/°C (max)

- Low Noise: 12nV/√Hz

- Input Offset Current: ±5nA max (+25°C)

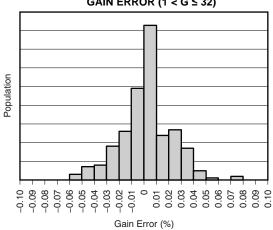

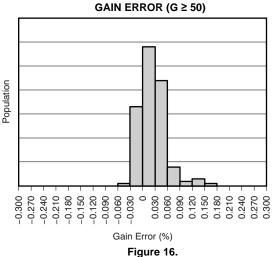

- Gain Error: 0.1% max (G ≤ 32),

0.3% max (G > 32)

- Binary Gains: 1, 2, 4, 8, 16, 32, 64, 128 (PGA112, PGA116)

- Scope Gains: 1, 2, 5, 10, 20, 50, 100, 200 (PGA113, PGA117)

- Gain Switching Time: 200ns

- Two Channel MUX: PGA112, PGA113 10 Channel MUX: PGA116, PGA117

- Four Internal Calibration Channels

- Amplifier Optimized for Driving CDAC ADCs

- Output Swing: 50mV to Supply Rails

- AV<sub>DD</sub> and DV<sub>DD</sub> for Mixed Voltage Systems

- I<sub>Q</sub> = 1.1mA (typ)

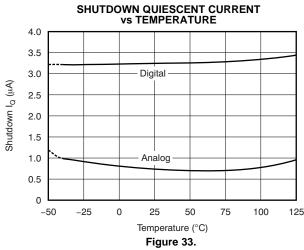

- Software/Hardware Shutdown: I<sub>Q</sub> ≤ 4μA (typ)

- Temperature Range: -40°C to +125°C

- SPI™ Interface (10MHz) with Daisy-Chain Capability

## **APPLICATIONS**

- Remote e-Meter Reading

- Automatic Gain Control

- Portable Data Acquisition

- PC-Based Signal Acquisition Systems

- Test and Measurement

- Programmable Logic Controllers

- Battery-Powered Instruments

- Handheld Test Equipment

#### DESCRIPTION

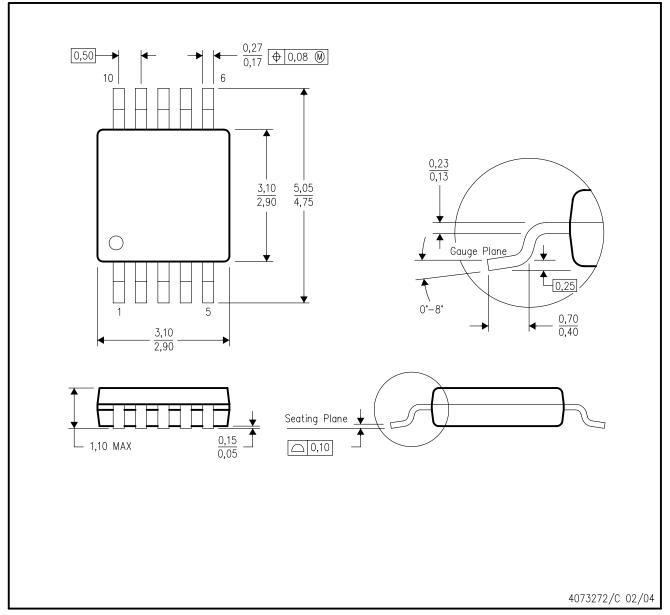

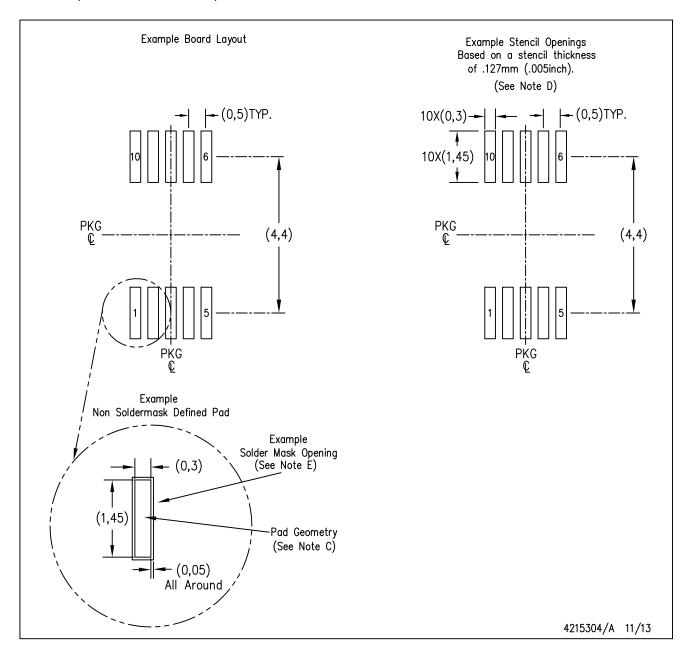

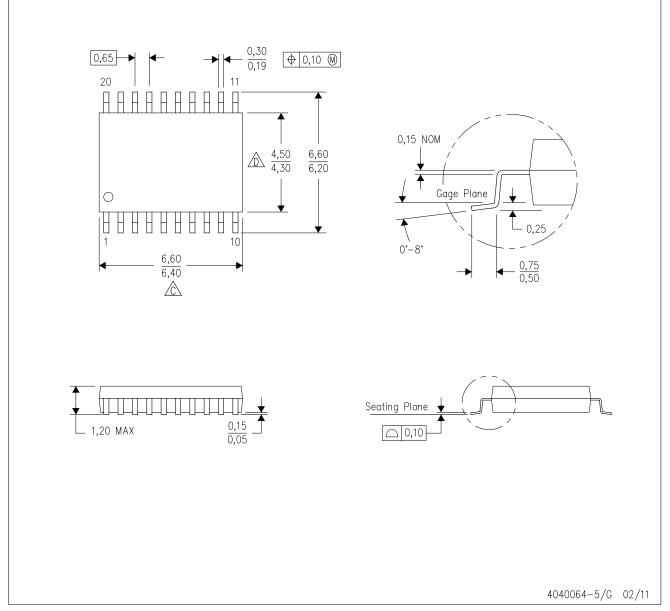

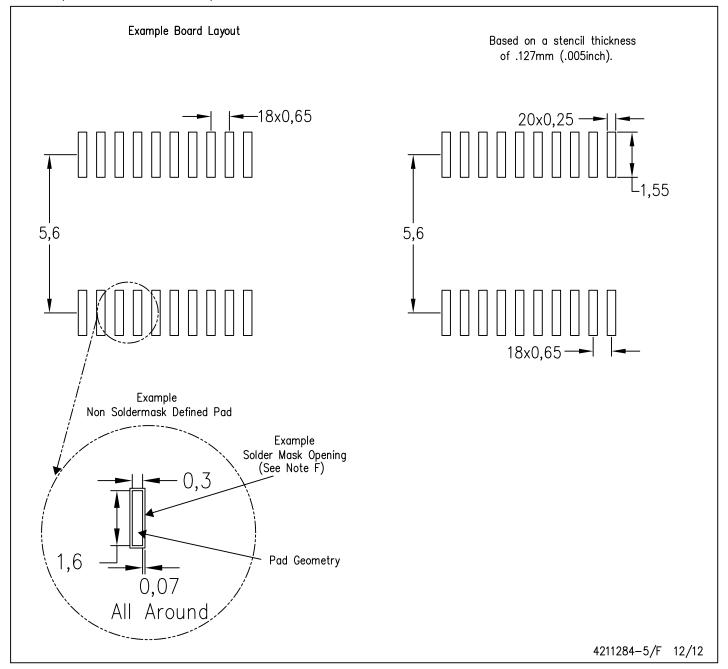

The PGA112 and PGA113 (binary/scope gains) offer two analog inputs, a three-pin SPI interface, and software shutdown in an MSOP-10 package. The PGA116 and PGA117 (binary/scope gains) offer 10 analog inputs, a four-pin SPI interface with daisy-chain capability, and hardware and software shutdown in a TSSOP-20 package.

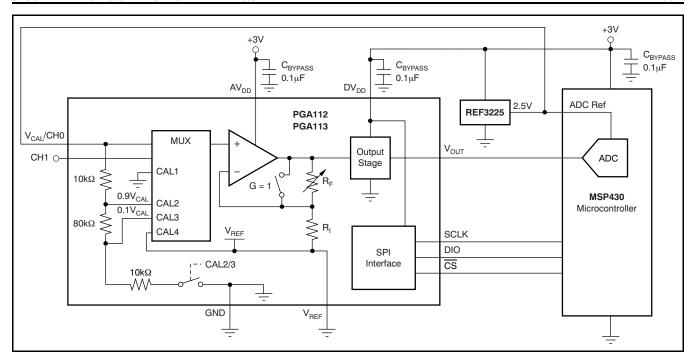

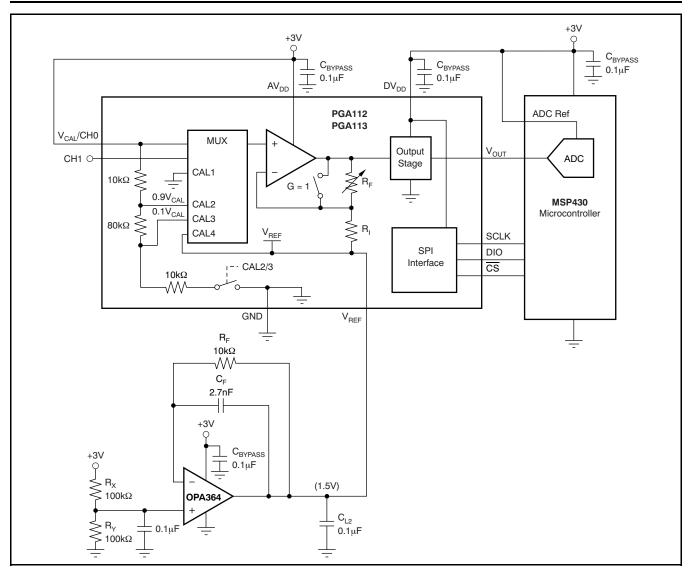

All versions provide internal calibration channels for system-level calibration. The channels are tied to GND,  $0.9V_{CAL}$ ,  $0.1V_{CAL}$ , and  $V_{REF}$ , respectively.  $V_{CAL}$ , an external voltage connected to Channel 0, is used as the system calibration reference. Binary gains are: 1, 2, 4, 8, 16, 32, 64, and 128; scope gains are: 1, 2, 5, 10, 20, 50, 100, and 200.

$\triangle$

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SPI is a trademark of Motorola.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## PACKAGE AND MODEL COMPARISON

|        | # OF MUX | GAINS        | SPI         | SHUT     |          |          |

|--------|----------|--------------|-------------|----------|----------|----------|

| DEVICE | INPUTS   | (Eight Each) | DAISY-CHAIN | HARDWARE | SOFTWARE | PACKAGE  |

| PGA112 | Two      | Binary       | No          | No       | ✓        | MSOP-10  |

| PGA113 | Two      | Scope        | No          | No       | ✓        | MSOP-10  |

| PGA116 | 10       | Binary       | ✓           | ✓        | ✓        | TSSOP-20 |

| PGA117 | 10       | Scope        | ✓           | ✓        | <b>√</b> | TSSOP-20 |

#### ORDERING INFORMATION(1)

| PRODUCT | DESCRIPTION (Gains/Channels)       | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | PACKAGE<br>MARKING |

|---------|------------------------------------|--------------|-----------------------|--------------------|

| PGA112  | Binary (2)/2 Channels              | MSOP-10      | DGS                   | P112               |

| PGA113  | Scope (3)/2 Channels               | MSOP-10      | DGS                   | P113               |

| PGA116  | Binary <sup>(2)</sup> /10 Channels | TSSOP-20     | PW                    | PGA116             |

| PGA117  | Scope (3)/10 Channels              | TSSOP-20     | PW                    | PGA117             |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

# **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range, unless otherwise noted.

|                   |                                | PGA112, PGA113, PGA116, PGA117         | UNIT       |  |  |  |

|-------------------|--------------------------------|----------------------------------------|------------|--|--|--|

| Supply Voltage    |                                | +7                                     | V          |  |  |  |

| Signal Input Terr | minals, Voltage <sup>(2)</sup> | GND – 0.5 to (AV <sub>DD</sub> ) + 0.5 | V          |  |  |  |

| Signal Input Terr | minals, Current <sup>(2)</sup> | ±10                                    | mA         |  |  |  |

| Output Short-Cir  | cuit                           | Continuous                             | Continuous |  |  |  |

| Operating Temp    | erature                        | -40 to +125                            | °C         |  |  |  |

| Storage Temper    | ature                          | -65 to +150                            | °C         |  |  |  |

| Junction Tempe    | rature                         | +150                                   | °C         |  |  |  |

|                   | Human Body Model (HBM)         | 3000                                   | V          |  |  |  |

| ESD Ratings:      | Charged Device Model (CDM)     | 1000                                   | V          |  |  |  |

|                   | Machine Model (MM)             | 300                                    | V          |  |  |  |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

<sup>(2)</sup> Binary gains: 1, 2, 4, 8, 16, 32, 64, and 128.

<sup>(3)</sup> Scope gains: 1, 2, 5, 10, 20, 50, 100, and 200.

<sup>(2)</sup> Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.5V beyond the supply rails should be current limited to 10mA or less.

# ELECTRICAL CHARACTERISTICS: V<sub>S</sub> = AV<sub>DD</sub> = DV<sub>DD</sub> = +5V

|                                                     |                      |                                                                                                                                                                                                                                                | PGA112, PC | PGA112, PGA113, PGA116, PGA11 |                        |               |

|-----------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------|------------------------|---------------|

| PARAMETER                                           |                      | CONDITIONS                                                                                                                                                                                                                                     | MIN        | TYP                           | MAX                    | UNIT          |

| OFFSET VOLTAGE                                      |                      |                                                                                                                                                                                                                                                |            |                               |                        |               |

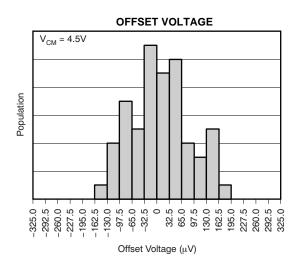

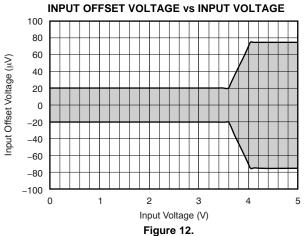

| Input Offset Voltage                                | V <sub>os</sub>      | $AV_DD = DV_DD = +5V, \ V_REF = V_IN = AV_DD/2, \ V_CM = 2.5V$                                                                                                                                                                                 |            | ±25                           | ±100                   | μV            |

|                                                     |                      | $AV_DD = DV_DD = +5V, \ V_REF = V_IN = AV_DD / 2, \ V_CM = 4.5V$                                                                                                                                                                               |            | ±75                           | ±325                   | μV            |

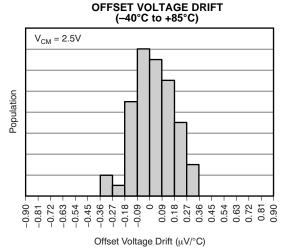

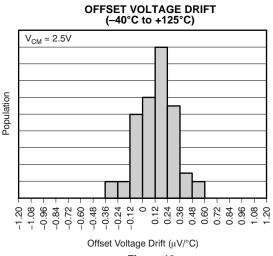

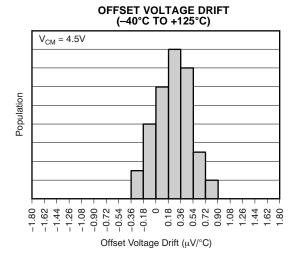

| vs Temperature, -40°C to +125°C                     | dV <sub>os</sub> /dT | $AV_{DD} = DV_{DD} = +5V$ , $V_{CM} = 2.5V$                                                                                                                                                                                                    |            | 0.35                          | 1.2                    | μ <b>۷/°C</b> |

| vs Temperature, -40°C to +85°C                      |                      | $AV_{DD} = DV_{DD} = +5V, V_{CM} = 2.5V$                                                                                                                                                                                                       |            | 0.15                          | 0.9                    | μV/°C         |

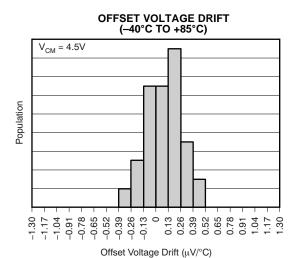

| vs Temperature, -40°C to +125°C                     |                      | $AV_{DD} = DV_{DD} = +5V$ , $V_{CM} = 4.5V$                                                                                                                                                                                                    |            | 0.6                           | 1.8                    | μ <b>۷/°C</b> |

| vs Temperature, -40°C to +85°C                      |                      | $AV_{DD} = DV_{DD} = +5V, V_{CM} = 4.5V$                                                                                                                                                                                                       |            | 0.3                           | 1.3                    | μV/°C         |

| vs Power Supply                                     | PSRR                 | $\begin{array}{c} {\rm AV_{DD} = DV_{DD} = +2.2V~to~+5.5V,~V_{CM} = 0.5V,} \\ {\rm V_{REF} = V_{IN} = AV_{DD}/2} \end{array}$                                                                                                                  |            | 5                             | 20                     | μV/V          |

| Over Temperature, -40°C to +125°C                   |                      | $\begin{array}{l} \textrm{AV}_\textrm{DD} = \textrm{DV}_\textrm{DD} = +2.2\textrm{V to } +5.5\textrm{V},  \textrm{V}_\textrm{CM} = 0.5\textrm{V}, \\ \textrm{V}_\textrm{REF} = \textrm{V}_\textrm{IN} = \textrm{AV}_\textrm{DD}/2 \end{array}$ |            | 5                             | 40                     | μ <b>V/V</b>  |

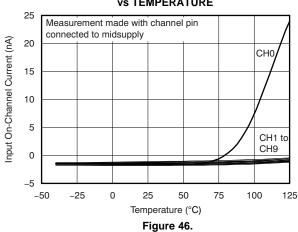

| INPUT ON-CHANNEL CURRENT                            |                      |                                                                                                                                                                                                                                                |            |                               |                        |               |

| Input On-Channel Current (Ch0, Ch1)                 | I <sub>IN</sub>      | $V_{REF} = V_{IN} = AV_{DD}/2$                                                                                                                                                                                                                 |            | ±1.5                          | ±5                     | nA            |

| Over Temperature, -40°C to +125°C                   |                      | $V_{REF} = V_{IN} = AV_{DD}/2$                                                                                                                                                                                                                 | See Ty     | oical Charac                  | teristics              | nA            |

| INPUT VOLTAGE RANGE                                 |                      |                                                                                                                                                                                                                                                |            |                               |                        |               |

| Input Voltage Range <sup>(1)</sup>                  | $I_{VR}$             |                                                                                                                                                                                                                                                | GND - 0.1  |                               | AV <sub>DD</sub> + 0.1 | V             |

| Overvoltage Input Range                             |                      | No Output Phase Reversal (2)                                                                                                                                                                                                                   | GND - 0.3  |                               | AV <sub>DD</sub> + 0.3 | V             |

| INPUT IMPEDANCE (Channel On)(3)                     |                      |                                                                                                                                                                                                                                                |            |                               |                        |               |

| Channel Input Capacitance                           | C <sub>CH</sub>      |                                                                                                                                                                                                                                                |            | 2                             |                        | pF            |

| Channel Switch Resistance                           | R <sub>sw</sub>      |                                                                                                                                                                                                                                                |            | 150                           |                        | Ω             |

| Amplifier Input Capacitance                         | C <sub>AMP</sub>     |                                                                                                                                                                                                                                                |            | 3                             |                        | pF            |

| Amplifier Input Resistance                          | R <sub>AMP</sub>     | Input Resistance to GND                                                                                                                                                                                                                        |            | 10                            |                        | GΩ            |

| V <sub>CAL</sub> /CH0                               | R <sub>IN</sub>      | CAL1 or CAL2 Selected                                                                                                                                                                                                                          |            | 100                           |                        | kΩ            |

| GAIN SELECTIONS                                     |                      |                                                                                                                                                                                                                                                |            |                               |                        |               |

| Nominal Gains                                       |                      | Binary gains: 1, 2, 4, 8, 16, 32, 64, 128                                                                                                                                                                                                      | 1          |                               | 128                    |               |

|                                                     |                      | Scope gains: 1, 2, 5, 10, 20, 50, 100, 200                                                                                                                                                                                                     | 1          |                               | 200                    |               |

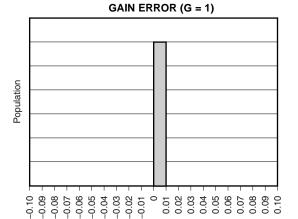

| DC Gain Error                                       | G = 1                | $V_{OUT} = GND + 85mV$ to $DV_{DD} - 85mV$                                                                                                                                                                                                     |            | 0.006                         | 0.1                    | %             |

|                                                     | 1 < G ≤ 32           | $V_{OUT} = GND + 85mV$ to $DV_{DD} - 85mV$                                                                                                                                                                                                     |            |                               | 0.1                    | %             |

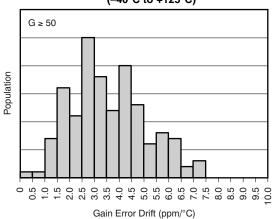

|                                                     | G ≥ 50               | $V_{OUT} = GND + 85mV \text{ to } DV_{DD} - 85mV$                                                                                                                                                                                              |            |                               | 0.3                    | %             |

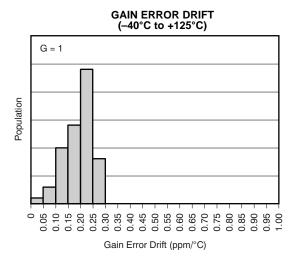

| DC Gain Drift                                       | G = 1                | V <sub>OUT</sub> = GND + 85mV to DV <sub>DD</sub> - 85mV                                                                                                                                                                                       |            | 0.5                           |                        | ppm/°C        |

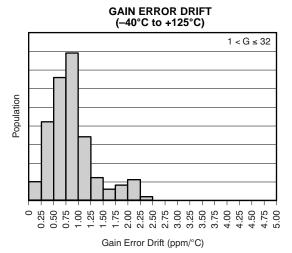

|                                                     | 1 < G ≤ 32           | V <sub>OUT</sub> = GND + 85mV to DV <sub>DD</sub> - 85mV                                                                                                                                                                                       |            | 2                             |                        | ppm/°C        |

|                                                     | G ≥ 50               | $V_{OUT} = GND + 85mV$ to $DV_{DD} - 85mV$                                                                                                                                                                                                     |            | 6                             |                        | ppm/°C        |

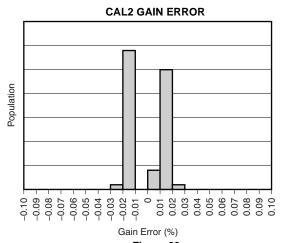

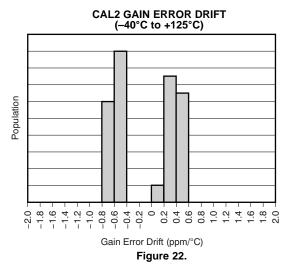

| CAL2 DC Gain Error <sup>(4)</sup>                   |                      | Op Amp + Input = $0.9V_{CAL}$ ,<br>$V_{REF} = V_{CAL} = AV_{DD}/2$ , G = 1                                                                                                                                                                     |            | 0.02                          |                        | %             |

| CAL2 DC Gain Drift <sup>(4)</sup>                   |                      | Op Amp + Input = $0.9V_{CAL}$ ,<br>$V_{REF} = V_{CAL} = AV_{DD}/2$ , G = 1                                                                                                                                                                     |            | 2                             |                        | ppm/°C        |

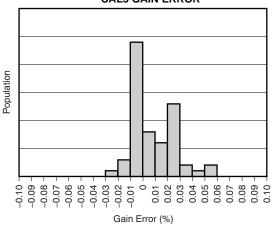

| CAL3 DC Gain Error <sup>(4)</sup>                   |                      | Op Amp + Input = $0.1V_{CAL}$ ,<br>$V_{REF} = V_{CAL} = AV_{DD}/2$ , G = 1                                                                                                                                                                     |            | 0.02                          |                        | %             |

| CAL3 DC Gain Drift <sup>(4)</sup>                   |                      | Op Amp + Input = $0.1V_{CAL}$ ,<br>$V_{REF} = V_{CAL} = AV_{DD}/2$ , G = 1                                                                                                                                                                     |            | 2                             |                        | ppm/°C        |

| INPUT IMPEDANCE (Channel Off)(3)                    |                      |                                                                                                                                                                                                                                                |            |                               |                        |               |

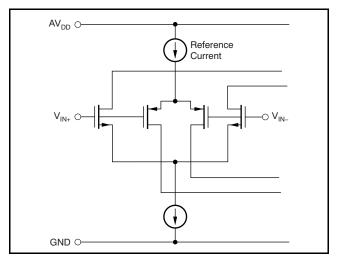

| Input Impedance                                     | C <sub>CH</sub>      | See Figure 1                                                                                                                                                                                                                                   |            | 2                             |                        | pF            |

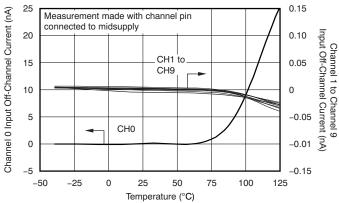

| INPUT OFF-CHANNEL CURRENT                           |                      |                                                                                                                                                                                                                                                |            |                               |                        |               |

| Input Off-Channel Current (Ch0, Ch1) <sup>(5)</sup> | I <sub>LKG</sub>     | $V_{REF} = GND$ , $V_{OFF-CHANNEL} = AV_{DD}/2$ ,<br>$V_{ON-CHANNEL} = AV_{DD}/2 - 0.1V$                                                                                                                                                       |            | ±0.05                         | ±1                     | nA            |

| Over Temperature, -40°C to +125°C                   |                      | $V_{REF} = GND$ , $V_{OFF-CHANNEL} = AV_{DD}/2$ ,<br>$V_{ON-CHANNEL} = AV_{DD}/2 - 0.1V$                                                                                                                                                       | See Typ    | See Typical Characteristics   |                        |               |

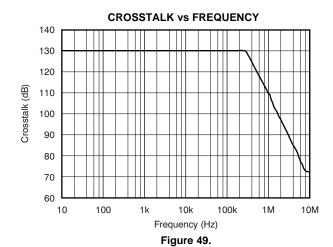

| Channel-to-Channel Crosstalk                        |                      |                                                                                                                                                                                                                                                |            | 130                           | 1                      | dB            |

Gain error is a function of the input voltage. Gain error outside of the range (GND + 85mV ≤ V<sub>OUT</sub> ≤ DV<sub>DD</sub> − 85mV) increases to 0.5% (typical).

Input voltages beyond this range must be current limited to < |10mA| through the input protection diodes on each channel to prevent permanent destruction of the device. See Figure 1.

Total V<sub>OUT</sub> error must be computed using input offset voltage error multiplied by gain. Includes op amp G = 1 error.

Maximum specification limitation limited by final test time and capability.

# ELECTRICAL CHARACTERISTICS: $V_S = AV_{DD} = DV_{DD} = +5V$ (continued)

|                                                                         |                                                                                                                      | PGA112, PGA113, PGA116, PGA117 |               |                                    |              |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------|------------------------------------|--------------|

| PARAMETER                                                               | CONDITIONS                                                                                                           | MIN                            | TYP           | MAX                                | UNIT         |

| ОИТРИТ                                                                  |                                                                                                                      |                                |               |                                    |              |

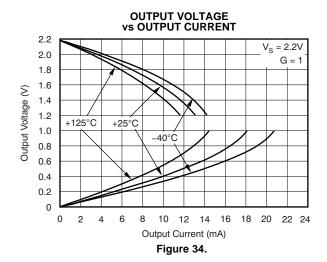

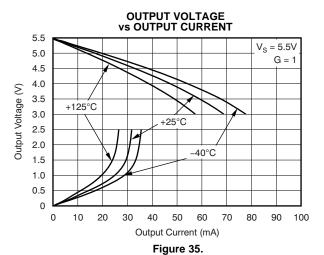

| Voltage Output Swing from Rail                                          | $I_{OUT} = \pm 0.25 \text{mA}, \ AV_{DD} \ge DV_{DD}^{(6)}$                                                          | GND + 0.05                     |               | $\mathrm{DV}_{\mathrm{DD}} - 0.05$ | V            |

|                                                                         | $I_{OUT} = \pm 5mA, AV_{DD} \ge DV_{DD}^{(6)}$                                                                       | GND + 0.25                     |               | $DV_{DD} - 0.25$                   | V            |

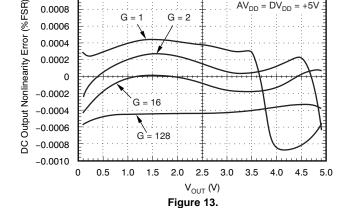

| DC Output Nonlinearity                                                  | $V_{OUT} = GND + 85mV$ to $DV_{DD} - 85mV^{(7)}$                                                                     |                                | 0.0015        |                                    | %FSR         |

| Short-Circuit Current I <sub>SC</sub>                                   |                                                                                                                      |                                | -30/+60       |                                    | mA           |

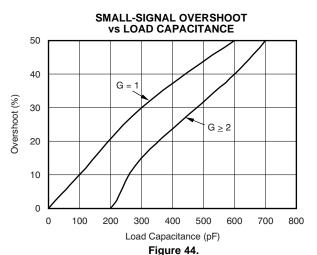

| Capacitive Load Drive C <sub>LOAD</sub>                                 |                                                                                                                      | See Ty                         | pical Charact | eristics                           |              |

| NOISE                                                                   |                                                                                                                      |                                |               |                                    |              |

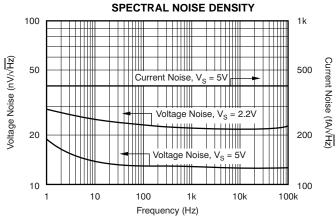

| Input Voltage Noise Density e <sub>n</sub>                              | $f > 10kHz, C_L = 100pF, V_S = 5V$                                                                                   |                                | 12            |                                    | nV/√Hz       |

|                                                                         | $f > 10kHz, C_L = 100pF, V_S = 2.2V$                                                                                 |                                | 22            |                                    | nV/√Hz       |

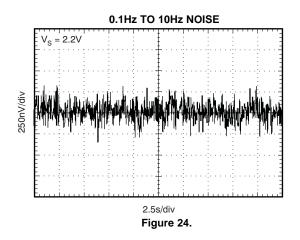

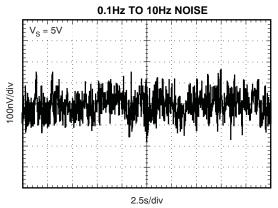

| Input Voltage Noise e <sub>n</sub>                                      | f = 0.1Hz to 10Hz, $C_L = 100pF$ , $V_S = 5V$                                                                        |                                | 0.362         |                                    | $\mu V_{PP}$ |

|                                                                         | $f=0.1Hz$ to 10Hz, $C_L=100pF,\ V_S=2.2V$                                                                            |                                | 0.736         |                                    | $\mu V_{PP}$ |

| Input Current Density In                                                | $f = 10kHz, C_L = 100pF$                                                                                             |                                | 400           |                                    | fA/√Hz       |

| SLEW RATE                                                               |                                                                                                                      |                                |               |                                    |              |

| Slew Rate SR                                                            |                                                                                                                      |                                | See Table 1   |                                    | V/μs         |

| SETTLING TIME                                                           |                                                                                                                      |                                |               |                                    |              |

| Settling Time t <sub>S</sub>                                            |                                                                                                                      |                                | See Table 1   |                                    | μs           |

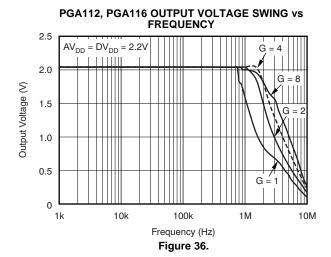

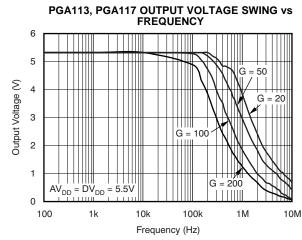

| FREQUENCY RESPONSE                                                      |                                                                                                                      |                                |               |                                    |              |

| Frequency Response                                                      |                                                                                                                      |                                | See Table 1   |                                    | MHz          |

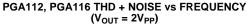

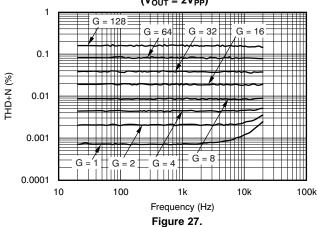

| THD + NOISE                                                             |                                                                                                                      |                                |               |                                    |              |

|                                                                         | G = 1, f = 1kHz, $V_{OUT} = 4V_{PP}$ at 2.5 $V_{DC}$ , $C_L = 100pF$                                                 |                                | 0.003         |                                    | %            |

|                                                                         | G = 10, f = 1kHz, $V_{OUT} = 4V_{PP}$ at $2.5V_{DC}$ , $C_L = 100pF$                                                 |                                | 0.005         |                                    | %            |

|                                                                         | G = 50, f = 1kHz, $V_{OUT}$ = $4V_{PP}$ at $2.5V_{DC}$ , $C_L$ = $100pF$                                             |                                | 0.03          |                                    | %            |

|                                                                         | G = 128, f = 1kHz, $V_{OUT}$ = $4V_{PP}$ at $2.5V_{DC}$ , $C_L$ = $100pF$                                            |                                | 0.08          |                                    | %            |

|                                                                         | G = 200, f = 1kHz, $V_{OUT} = 4V_{PP}$ at 2.5 $V_{DC}$ , $C_L = 100pF$                                               |                                | 0.1           |                                    | %            |

|                                                                         | G = 1, f = 20kHz, $V_{OUT} = 4V_{PP}$ at 2.5 $V_{DC}$ , $C_L = 100pF$                                                |                                | 0.02          |                                    | %            |

|                                                                         | G = 10, f = 20kHz, $V_{OUT}$ = $4V_{PP}$ at $2.5V_{DC}$ , $C_L$ = $100pF$                                            |                                | 0.01          |                                    | %            |

|                                                                         | G = 50, f = 20kHz, $V_{OUT}$ = $4V_{PP}$ at $2.5V_{DC}$ , $C_L$ = $100pF$                                            |                                | 0.03          |                                    | %            |

|                                                                         | G = 128, f = 20kHz, $V_{OUT}$ = 4 $V_{PP}$ at 2.5 $V_{DC}$ , $C_L$ = 100pF                                           |                                | 0.08          |                                    | %            |

|                                                                         | G = 200, f = 20kHz, $V_{OUT} = 4V_{PP}$ at 2.5 $V_{DC}$ , $C_L = 100pF$                                              |                                | 0.11          |                                    | %            |

| POWER SUPPLY                                                            |                                                                                                                      |                                |               |                                    |              |

| Operating Voltage Range <sup>(6)</sup> AV <sub>DD</sub>                 |                                                                                                                      | 2.2                            |               | 5.5                                | V            |

| $DV_{DD}$                                                               |                                                                                                                      | 2.2                            |               | 5.5                                | V            |

| Quiescent Current Analog I <sub>QA</sub>                                | $I_O = 0$ , $G = 1$ , $V_{OUT} = V_{REF}$                                                                            |                                | 0.33          | 0.45                               | mA           |

| Over Temperature, -40°C to +125°C                                       |                                                                                                                      |                                |               | 0.45                               | mA           |

| Quiescent Current Digital <sup>(8)(9)(10)</sup> I <sub>QD</sub>         | $I_O = 0$ , $G = 1$ , $V_{OUT} = V_{REF}$ , SCLK at 10MHz, $\overline{CS} = Logic 0$ , DIO or DIN = Logic 0          |                                | 0.75          | 1.2                                | mA           |

| Over Temperature, -40°C to +125°C <sup>(8)(9)(10)</sup>                 | $I_0 = 0$ , $G = 1$ , $V_{OUT} = V_{REF}$ , SCLK at 10MHz, $\overline{CS} = Logic 0$ , DIO or DIN = $Logic 0$        |                                |               | 1.2                                | mA           |

| Shutdown Current Analog + Digital <sup>(8)(9)</sup> $I_{SDA} + I_{SDD}$ | $I_O = 0$ , $V_{OUT} = V_{REF}$ , $G = 1$ , SCLK Idle                                                                |                                | 4             |                                    | μΑ           |

|                                                                         | $I_O = 0$ , $V_{OUT} = 0$ , $G = 1$ , SCLK at 10MHz,<br>$\overline{CS} = Logic 0$ , DIO or DIN = Logic 0             |                                | 245           |                                    | μΑ           |

| POWER-ON RESET (POR)                                                    |                                                                                                                      |                                |               |                                    |              |

| POR Trip Voltage                                                        | Digital interface disabled and Command Register set to POR values for $\mathrm{DV}_{\mathrm{DD}}$ < POR Trip Voltage |                                | 1.6           |                                    | V            |

When  ${\rm AV_{DD}}$  is less than  ${\rm DV_{DD}}$ , the output is clamped to  ${\rm AV_{DD}}$  + 300mV. Measurement limited by noise in test equipment and test time.

<sup>(7)</sup>

<sup>(8)</sup> Does not include current into or out of the V<sub>REF</sub> pin. Internal R<sub>F</sub> and R<sub>I</sub> are always connected between V<sub>OUT</sub> and V<sub>REF</sub>.

(9) Digital logic levels: DIO or DIN = logic 0. 10μA internal pull-down current source.

<sup>(10)</sup> Includes current from op amp output structure.

# ELECTRICAL CHARACTERISTICS: $V_S = AV_{DD} = DV_{DD} = +5V$ (continued)

|                                          |                                                                                                                                        | PGA112, PG          | A113, PGA1 | 13, PGA116, PGA117  |      |  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|---------------------|------|--|

| PARAMETER                                | CONDITIONS                                                                                                                             | MIN                 | TYP        | MAX                 | UNIT |  |

| TEMPERATURE RANGE                        |                                                                                                                                        |                     |            |                     |      |  |

| Specified Range                          |                                                                                                                                        | -40                 |            | +125                | °C   |  |

| Operating Range                          |                                                                                                                                        | -40                 |            | +125                | °C   |  |

| Thermal Resistance $\theta_{JA}$         |                                                                                                                                        |                     |            |                     |      |  |

| MSOP-10                                  |                                                                                                                                        |                     | 164        |                     | °C/W |  |

| DIGITAL INPUTS (SCLK, CS, DIO, DIN)      |                                                                                                                                        |                     |            |                     |      |  |

| Logic Low                                |                                                                                                                                        | 0                   |            | 0.3DV <sub>DD</sub> | V    |  |

| Input Leakage Current (SCLK and CS only) |                                                                                                                                        | -1                  |            | +1                  | μΑ   |  |

| Weak Pull-Down Current (DIO, DIN only)   |                                                                                                                                        |                     | 10         |                     | μΑ   |  |

| Logic High                               |                                                                                                                                        | 0.7DV <sub>DD</sub> |            | $DV_DD$             | V    |  |

| Hysteresis                               |                                                                                                                                        |                     | 700        |                     | mV   |  |

| DIGITAL OUTPUT (DIO, DOUT)               |                                                                                                                                        |                     |            |                     |      |  |

| Logic High                               | $I_{OH} = -3mA$ (sourcing)                                                                                                             | $DV_{DD} - 0.4$     |            | DV <sub>DD</sub>    | V    |  |

| Logic Low                                | I <sub>OL</sub> = +3mA (sinking)                                                                                                       | GND                 |            | GND + 0.4           | V    |  |

| CHANNEL AND GAIN TIMING                  |                                                                                                                                        |                     |            |                     |      |  |

| Channel Select Time                      |                                                                                                                                        |                     | 0.2        |                     | μs   |  |

| Gain Select Time                         |                                                                                                                                        |                     | 0.2        |                     | μs   |  |

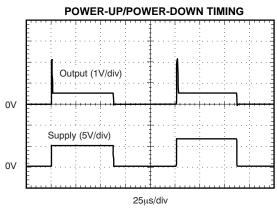

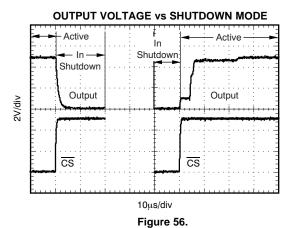

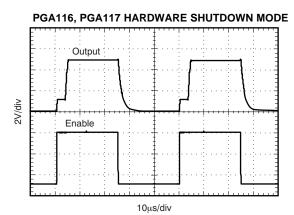

| SHUTDOWN MODE TIMING                     |                                                                                                                                        |                     |            |                     |      |  |

| Enable Time                              |                                                                                                                                        |                     | 4.0        |                     | μs   |  |

| Disable Time                             | $V_{\text{OUT}}$ goes high-impedance, $R_{\text{F}}$ and $R_{\text{I}}$ remain connected between $V_{\text{OUT}}$ and $V_{\text{REF}}$ |                     | 2.0        |                     | μs   |  |

| POWER-ON-RESET (POR) TIMING              |                                                                                                                                        |                     |            |                     |      |  |

| POR Power-Up Time                        | $DV_{DD} \ge 2V$                                                                                                                       |                     | 40         |                     | μs   |  |

| POR Power-Down Time                      | DV <sub>DD</sub> ≤ 1.5V                                                                                                                |                     | 5          |                     | μs   |  |

Table 1. Frequency Response versus Gain ( $C_L = 100pF$ ,  $R_L = 10k\Omega$ )

| BINARY<br>GAIN (V/V) | TYPICAL -3dB FREQUENCY (MHz) | SLEW<br>RATE-<br>FALL<br>(V/μs) | SLEW<br>RATE-<br>RISE<br>(V/μs) | 0.1%<br>SETTLING<br>TIME:<br>4V <sub>PP</sub><br>(μs) | 0.01%<br>SETTLING<br>TIME:<br>4V <sub>PP</sub><br>(μs) | SCOPE<br>GAIN<br>(V/V) | TYPICAL -3dB FREQUENCY (MHz) | SLEW<br>RATE-<br>FALL<br>(V/μs) | SLEW<br>RATE-<br>RISE<br>(V/µs) | 0.1%<br>SETTLING<br>TIME:<br>4V <sub>PP</sub><br>(μs) | 0.01%<br>SETTLING<br>TIME:<br>4V <sub>PP</sub><br>(μs) |

|----------------------|------------------------------|---------------------------------|---------------------------------|-------------------------------------------------------|--------------------------------------------------------|------------------------|------------------------------|---------------------------------|---------------------------------|-------------------------------------------------------|--------------------------------------------------------|

| 1                    | 10                           | 8                               | 3                               | 2                                                     | 2.55                                                   | 1                      | 10                           | 8                               | 3                               | 2                                                     | 2.55                                                   |

| 2                    | 3.8                          | 9                               | 6.4                             | 2                                                     | 2.6                                                    | 2                      | 3.8                          | 9                               | 6.4                             | 2                                                     | 2.6                                                    |

| 4                    | 2                            | 12.8                            | 10.6                            | 2                                                     | 2.6                                                    | 5                      | 1.8                          | 12.8                            | 10.6                            | 2                                                     | 2.6                                                    |

| 8                    | 1.8                          | 12.8                            | 10.6                            | 2                                                     | 2.6                                                    | 10                     | 1.8                          | 12.8                            | 10.6                            | 2.2                                                   | 2.6                                                    |

| 16                   | 1.6                          | 12.8                            | 12.8                            | 2.3                                                   | 2.6                                                    | 20                     | 1.3                          | 12.8                            | 9.1                             | 2.3                                                   | 2.8                                                    |

| 32                   | 1.8                          | 12.8                            | 13.3                            | 2.3                                                   | 3                                                      | 50                     | 0.9                          | 9.1                             | 7.1                             | 2.4                                                   | 3.8                                                    |

| 64                   | 0.6                          | 4                               | 3.5                             | 3                                                     | 6                                                      | 100                    | 0.38                         | 4                               | 3.5                             | 4.4                                                   | 7                                                      |

| 128                  | 0.35                         | 2.5                             | 2.5                             | 4.8                                                   | 8                                                      | 200                    | 0.23                         | 2.3                             | 2                               | 6.9                                                   | 10                                                     |

Figure 1. Equivalent Input Circuit

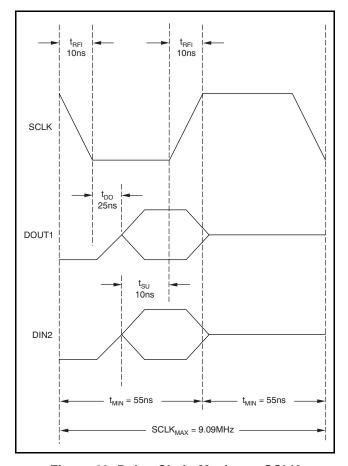

# SPI TIMING: $V_S = AV_{DD} = DV_{DD} = +2.2V$ to +5V

|                                                              |                   |                   |     | A112, PGA<br>A116, PGA |     |      |

|--------------------------------------------------------------|-------------------|-------------------|-----|------------------------|-----|------|

| PARAMETER                                                    |                   | TEST CONDITIONS   | MIN | TYP                    | MAX | UNIT |

| Input Capacitance (SCLK, CS, and DIO pins)                   |                   |                   |     | 1                      |     | pF   |

| Input Rise/Fall Time <sup>(1)</sup> (CS, SCLK, and DIO pins) | t <sub>RFI</sub>  |                   |     |                        | 2   | μs   |

| Output Rise/Fall Time (DIO pin) <sup>(1)</sup>               | t <sub>RFO</sub>  | $C_{LOAD} = 60pF$ |     |                        | 10  | ns   |

| CS High Time (CS pin) <sup>(1)</sup>                         | t <sub>CSH</sub>  |                   | 40  |                        |     | ns   |

| SCLK Edge to CS Fall Setup Time(1)                           | $t_{CSO}$         |                   | 10  |                        |     | ns   |

| CS Fall to First SCLK Edge Setup Time                        | t <sub>CSSC</sub> |                   | 10  |                        |     | ns   |

| SCLK Frequency <sup>(2)</sup>                                | f <sub>SCLK</sub> |                   |     |                        | 10  | MHz  |

| SCLK High Time <sup>(3)</sup>                                | t <sub>HI</sub>   |                   | 40  |                        |     | ns   |

| SCLK Low Time <sup>(3)</sup>                                 | $t_{LO}$          |                   | 40  |                        |     | ns   |

| SCLK Last Edge to CS Rise Setup Time (1)                     | t <sub>SCCS</sub> |                   | 10  |                        |     | ns   |

| CS Rise to SCLK Edge Setup Time (1)                          | t <sub>CS1</sub>  |                   | 10  |                        |     | ns   |

| DIN Setup Time                                               | t <sub>SU</sub>   |                   | 10  |                        |     | ns   |

| DIN Hold Time                                                | $t_{HD}$          |                   | 10  |                        |     | ns   |

| SCLK to DOUT Valid Propagation Delay <sup>(1)</sup>          | $t_{DO}$          |                   |     |                        | 25  | ns   |

| CS Rise to DOUT Forced to Hi-Z <sup>(1)</sup>                | t <sub>SOZ</sub>  |                   |     |                        | 20  | ns   |

Ensured by design; not production tested.

When using devices in daisy-chain mode, the maximum clock frequency for SCLK is limited by SCLK rise/fall time, DIN setup time, and DOUT propagation delay. See Figure 63. Based on this limitation, the maximum SCLK frequency for daisy-chain mode is 9.09MHz.

<sup>(3)</sup>  $t_{HI}$  and  $t_{LO}$  must not be less than 1/SCLK (max).

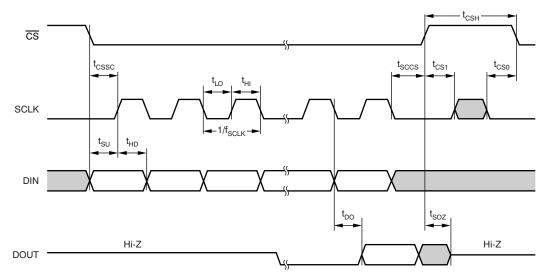

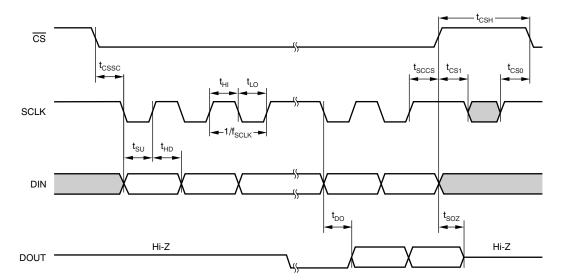

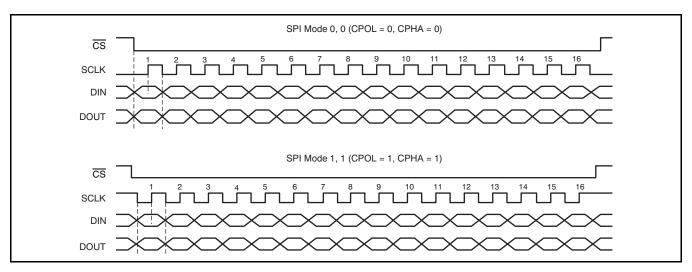

## **SPI TIMING DIAGRAMS**

Figure 2. SPI Mode 0, 0

Figure 3. SPI Mode 1, 1

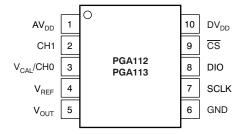

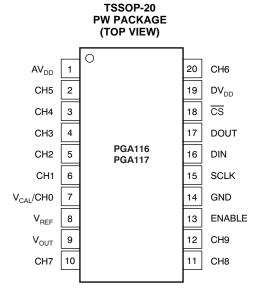

## **PIN CONFIGURATIONS**

#### MSOP-10 DGS PACKAGE (TOP VIEW)

# **PGA112, PGA113 TERMINAL FUNCTIONS**

| MSOP<br>PACKAGE<br>PIN # | NAME                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | AV <sub>DD</sub>      | Analog supply voltage (+2.2V to +5.5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2                        | CH1                   | Input MUX channel 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3                        | V <sub>CAL</sub> /CH0 | Input MUX channel 0 and $V_{CAL}$ input. For system calibration purposes, connect this pin to a low-impedance external reference voltage to use internal calibration channels. The four internal calibration channels are connected to GND, $0.9V_{CAL}$ , $0.1V_{CAL}$ , and $V_{REF}$ , respectively. $V_{CAL}$ is loaded with $100k\Omega$ (typical) when internal calibration channels CAL2 or CAL3 are selected. Otherwise, $V_{CAL}/CH0$ appears as high impedance.                                                                  |

| 4                        | V <sub>REF</sub>      | Reference input pin. Connect external reference for V <sub>OUT</sub> offset shift or to midsupply for midsupply referenced systems. V <sub>REF</sub> must be connected to a low-impedance reference capable of sourcing and sinking at least 2mA or V <sub>REF</sub> must be connected to GND.                                                                                                                                                                                                                                             |

| 5                        | V <sub>OUT</sub>      | Analog voltage output. When $AV_{DD} < DV_{DD}$ , $V_{OUT}$ is clamped to $AV_{DD} + 300$ mV.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6                        | GND                   | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7                        | SCLK                  | Clock input for SPI serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8                        | DIO                   | Data input/output for SPI serial interface. DIO contains a weak, 10µA internal pull-down current source.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9                        | <u>cs</u>             | Chip select line for SPI serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10                       | DV <sub>DD</sub>      | Digital and op amp output stage supply voltage (+2.2V to +5.5V). Useful in multi-supply systems to prevent overvoltage/lockup condition on an analog-to-digital (ADC) input (for example, a microcontroller with an ADC running on +3V and the PGA powered from +5V). Digital I/O levels to be relative to DV <sub>DD</sub> . DV <sub>DD</sub> should be bypassed with a 0.1µF ceramic capacitor, and DV <sub>DD</sub> must supply the current for the digital portion of the PGA as well as the load current for the op amp output stage. |

# **PGA116, PGA117 TERMINAL FUNCTIONS**

| TSSOP<br>PACKAGE<br>PIN # | NAME                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                         | AV <sub>DD</sub>      | Analog supply voltage (+2.2V to +5.5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2                         | CH5                   | Input MUX channel 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3                         | CH4                   | Input MUX channel 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4                         | CH3                   | Input MUX channel 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5                         | CH2                   | Input MUX channel 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6                         | CH1                   | Input MUX channel 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7                         | V <sub>CAL</sub> /CH0 | Input MUX channel 0 and $V_{CAL}$ input. For system calibration purposes, connect this pin to a low-impedance external reference voltage to use internal calibration channels. The four internal calibration channels are connected to GND, $0.9V_{CAL}$ , $0.1V_{CAL}$ , and $V_{REF}$ , respectively. $V_{CAL}$ is loaded with $100k\Omega$ (typical) when internal calibration channels CAL2 or CAL3 are selected. Otherwise, $V_{CAL}/CH0$ appears as high impedance.                                                   |

| 8                         | V <sub>REF</sub>      | Reference input pin. Connect external reference for $V_{\text{OUT}}$ offset shift or to midsupply for midsupply referenced systems. $V_{\text{REF}}$ must be connected to a low-impedance reference capable of sourcing and sinking at least 2mA or to GND.                                                                                                                                                                                                                                                                 |

| 9                         | V <sub>OUT</sub>      | Analog voltage output. When $AV_{DD} < DV_{DD}$ , $V_{OUT}$ is clamped to $AV_{DD} + 300$ mV.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10                        | CH7                   | Input MUX channel 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11                        | CH8                   | Input MUX channel 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12                        | CH9                   | Input MUX channel 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 13                        | ENABLE                | Hardware enable pin. Logic low puts the part into Shutdown mode ( $I_Q$ < 1 $\mu$ A).                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 14                        | GND                   | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 15                        | SCLK                  | Clock input for SPI serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16                        | DIN                   | Data input for SPI serial interface. DIN contains a weak, 10µA internal pull-down current source to allow for ease of daisy-chain configurations.                                                                                                                                                                                                                                                                                                                                                                           |

| 17                        | DOUT                  | Data output for SPI serial interface. DOUT goes to high-Z state when $\overline{\text{CS}}$ goes high for standard SPI interface.                                                                                                                                                                                                                                                                                                                                                                                           |

| 18                        | CS                    | Chip select line for SPI serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 19                        | DV <sub>DD</sub>      | Digital and op amp output stage supply voltage (+2.2V to +5.5V). Useful in multi-supply systems to prevent overvoltage/lockup condition on an ADC input (for example, a microcontroller with an ADC running on +3V and the PGA powered from +5V). Digital I/O levels to be relative to DV <sub>DD</sub> . DV <sub>DD</sub> should be bypassed with a $0.1\mu F$ ceramic capacitor, and DV <sub>DD</sub> must supply the current for the digital portion of the PGA as well as the load current for the op amp output stage. |

| 20                        | CH6                   | Input MUX channel 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

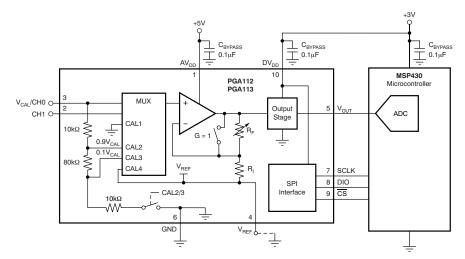

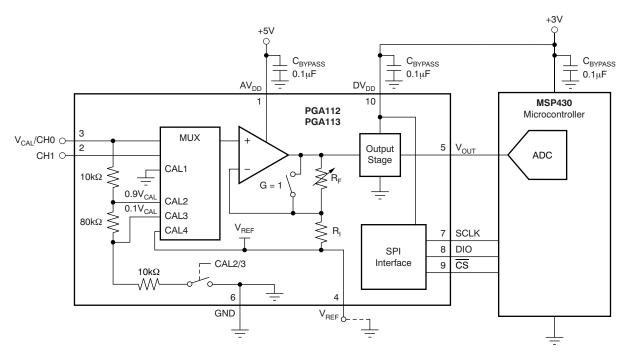

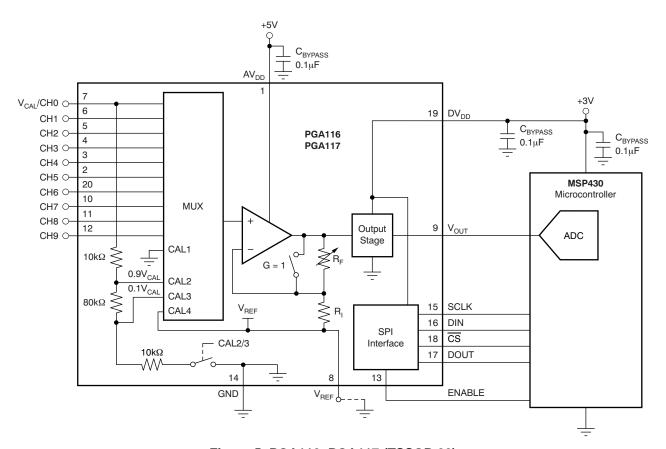

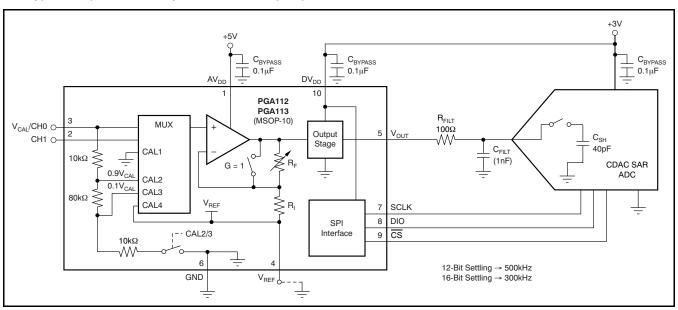

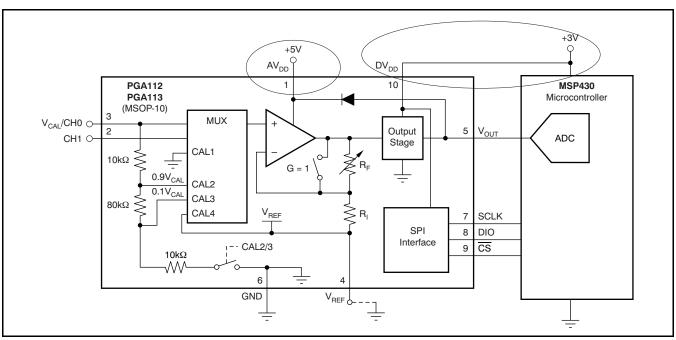

# **TYPICAL APPLICATION CIRCUITS**

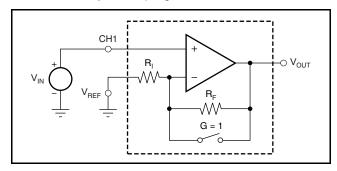

Figure 4. PGA112, PGA113 (MSOP-10)

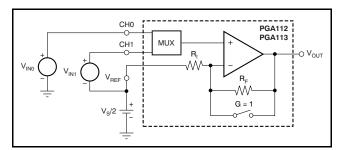

Figure 5. PGA116, PGA117 (TSSOP-20)

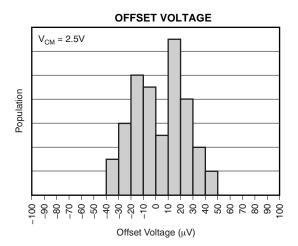

#### TYPICAL CHARACTERISTICS

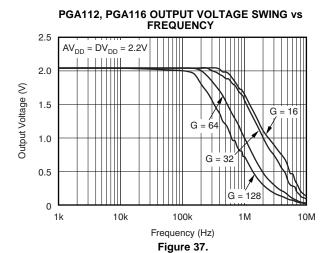

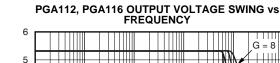

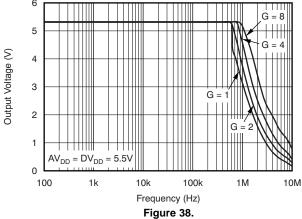

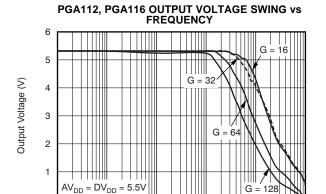

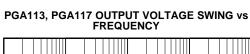

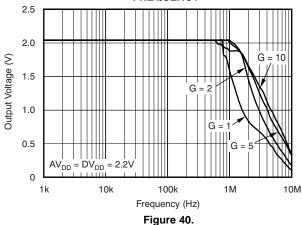

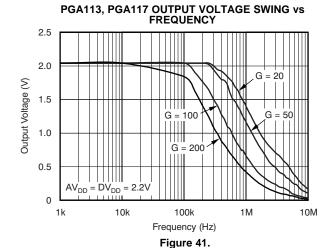

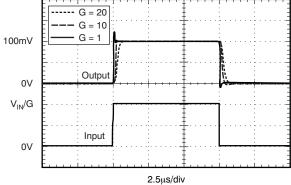

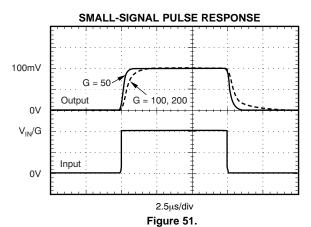

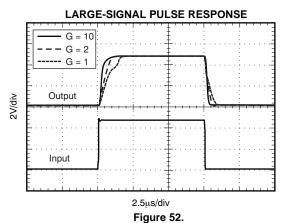

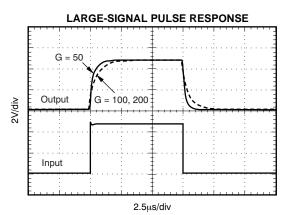

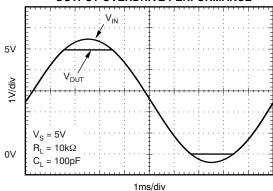

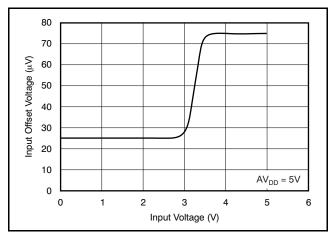

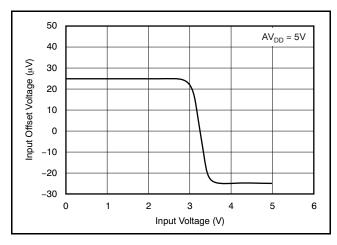

At  $T_A = +25$ °C,  $AV_{DD} = DV_{DD} = 5V$ ,  $R_L = 10k\Omega$  connected to  $DV_{DD}/2$ ,  $V_{REF} = GND$ , and  $C_L = 100pF$ , unless otherwise noted.

Figure 6.

Figure 8.

Figure 10.

Figure 7.

Figure 9.

Figure 11.

0.0010

0.0008

At  $T_A = +25^{\circ}C$ ,  $AV_{DD} = DV_{DD} = 5V$ ,  $R_L = 10k\Omega$  connected to  $DV_{DD}/2$ ,  $V_{REF} = GND$ , and  $C_L = 100pF$ , unless otherwise noted.

G

**PGA112/PGA116 NONLINEARITY**

G = 2

GAIN ERROR (1 < G ≤ 32)

Gain Error (%) Figure 14.

Figure 17.

At  $T_A = +25^{\circ}C$ ,  $AV_{DD} = DV_{DD} = 5V$ ,  $R_L = 10k\Omega$  connected to  $DV_{DD}/2$ ,  $V_{REF} = GND$ , and  $C_L = 100pF$ , unless otherwise noted.

Figure 18.

Figure 20.

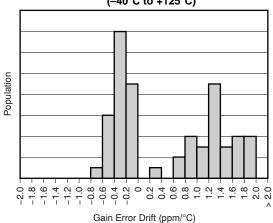

GAIN ERROR DRIFT (-40°C to +125°C)

Figure 19.

Figure 21.

#### CAL3 GAIN ERROR DRIFT (-40°C to +125°C)

Figure 23.

At  $T_A = +25^{\circ}C$ ,  $AV_{DD} = DV_{DD} = 5V$ ,  $R_L = 10k\Omega$  connected to  $DV_{DD}/2$ ,  $V_{REF} = GND$ , and  $C_L = 100pF$ , unless otherwise noted.

Figure 25.

Figure 26.

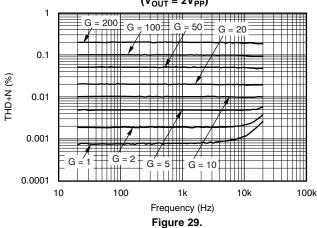

PGA113, PGA117 THD + NOISE vs FREQUENCY  $(V_{OUT} = 2V_{PP})$

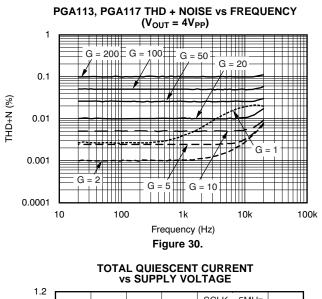

At  $T_A = +25$ °C,  $AV_{DD} = DV_{DD} = 5V$ ,  $R_L = 10k\Omega$  connected to  $DV_{DD}/2$ ,  $V_{REF} = GND$ , and  $C_L = 100pF$ , unless otherwise noted.

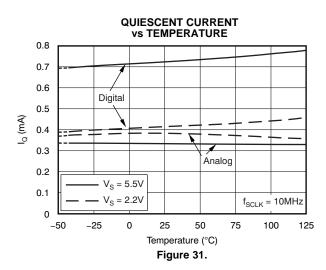

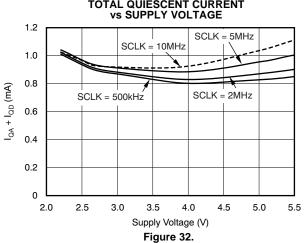

At  $T_A = +25^{\circ}C$ ,  $AV_{DD} = DV_{DD} = 5V$ ,  $R_L = 10k\Omega$  connected to  $DV_{DD}/2$ ,  $V_{REF} = GND$ , and  $C_L = 100pF$ , unless otherwise noted.

10k

100k

Frequency (Hz)

Figure 39.

1M

0

100

At  $T_A = +25^{\circ}C$ ,  $AV_{DD} = DV_{DD} = 5V$ ,  $R_L = 10k\Omega$  connected to  $DV_{DD}/2$ ,  $V_{REF} = GND$ , and  $C_L = 100pF$ , unless otherwise noted.

Figure 42.

Figure 43.

**GAIN vs SETTLING TIME**

INPUT ON-CHANNEL CURRENT vs TEMPERATURE

12  $C_L = 100pF//R_L = 10k\Omega$ 10  $V_{OUT} = 4V_{PP}$ 0.01%

2 0.1%

Gain Figure 45.

100

150

200

0

50

# INPUT OFF-CHANNEL LEAKAGE CURRENT vs TEMPERATURE

Figure 47.

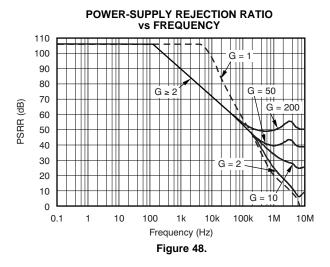

At  $T_A = +25^{\circ}C$ ,  $AV_{DD} = DV_{DD} = 5V$ ,  $R_L = 10k\Omega$  connected to  $DV_{DD}/2$ ,  $V_{REF} = GND$ , and  $C_L = 100pF$ , unless otherwise noted.

Figure 53.

At  $T_A$  = +25°C,  $AV_{DD}$  =  $DV_{DD}$  = 5V,  $R_L$  =  $10k\Omega$  connected to  $DV_{DD}/2$ ,  $V_{REF}$  = GND, and  $C_L$  = 100pF, unless otherwise noted.

**OUTPUT OVERDRIVE PERFORMANCE**

Figure 55.

Figure 57.

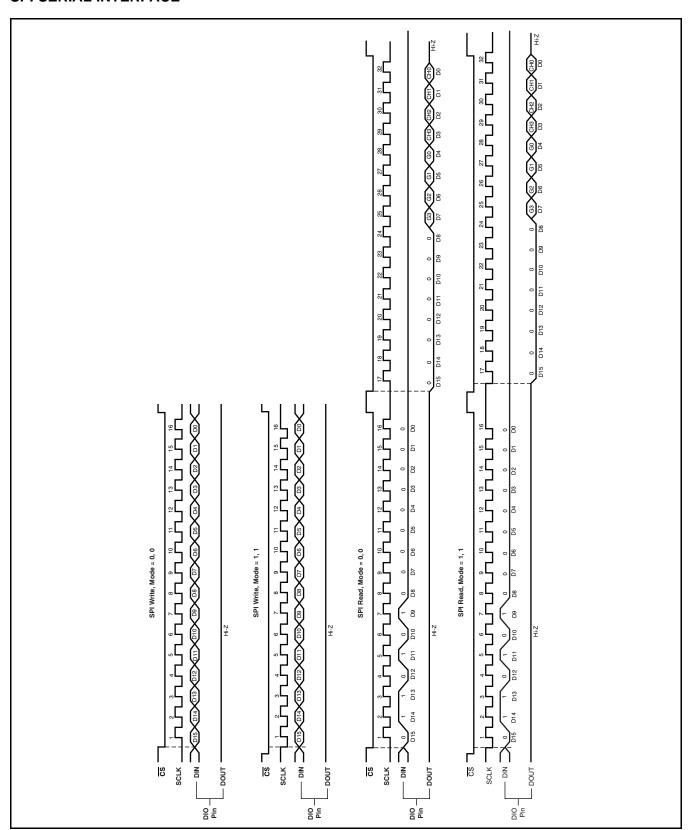

#### SERIAL INTERFACE INFORMATION

Figure 58. SPI Mode 0,0 and Mode 1,1

**Table 2. SPI Mode Setting Description**

| MODE | CPOL | СРНА             | CPOL DESCRIPTION | CPHA DESCRIPTION                                                                     |

|------|------|------------------|------------------|--------------------------------------------------------------------------------------|

| 0, 0 | 0    | 0 <sup>(1)</sup> | Clock idles low  | Data are read on the rising edge of clock. Data change on the falling edge of clock. |

| 1, 1 | 1    | 1 (2)            | Clock idles high | Data are read on the rising edge of clock. Data change on the falling edge of clock. |

- (1) CPHA = 0 means sample on first clock edge (rising or falling) after a valid  $\overline{CS}$ .

- (2) CPHA = 1 means sample on second clock edge (rising or falling) after a valid CS.

#### **SERIAL DIGITAL INTERFACE: SPI MODES**

The PGA uses a standard serial peripheral interface (SPI). Both SPI Mode 0,0 and Mode 1,1 are supported, as shown in Figure 58 and described in Table 2.

If there are not even-numbered increments of  $\frac{16}{\text{CS}}$  clocks (that is, 16, 32, 64, and  $\frac{1}{\text{SO}}$  forth) between  $\frac{1}{\text{CS}}$  going low (falling edge) and  $\frac{1}{\text{CS}}$  going high (rising edge), the device takes no action. This condition provides reliable serial communication. Furthermore, this condition also provides a way to quickly reset the SPI interface to a known starting condition for data synchronization. Transmitted  $\frac{1}{\text{CS}}$  data are latched internally on the rising edge of  $\frac{1}{\text{CS}}$ .

On the PGA116/PGA117,  $\overline{\text{CS}}$ , DIN, and SCLK are Schmitt-triggered CMOS logic inputs. DIN has a weak internal pull-down to support daisy-chain communications on the PGA116/PGA117. DOUT is a CMOS logic output. When  $\overline{\text{CS}}$  is high, the state of DOUT is high-impedance. When  $\overline{\text{CS}}$  is low, DOUT is driven as illustrated in Figure 59.

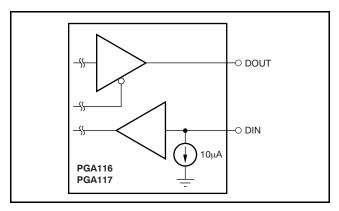

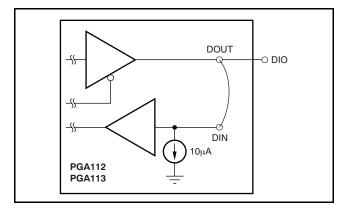

Figure 59. Digital I/O Structure—PGA116/PGA117

On the PGA112/PGA113, there are digital output and digital input gates both internally connected to the DIO pin. DIN is an input-only gate and DOUT is a digital output that can give a 3-state output. The DIO pin has a weak 10µA pull-down current source to prevent the pin from floating in systems with a high-impedance SPI DOUT line. When  $\overline{CS}$  is high, the state of the internal DOUT gate is high-impedance. When  $\overline{CS}$  is low, the state of DIO depends on the previous valid SPI communication; either DIO becomes an output to clock out data or it remains an input to receive data. This structure is shown in Figure 60.

Figure 60. Digital I/O Structure—PGA112/PGA113

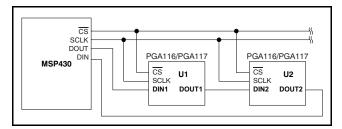

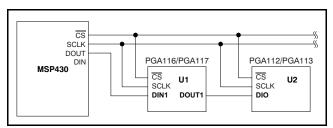

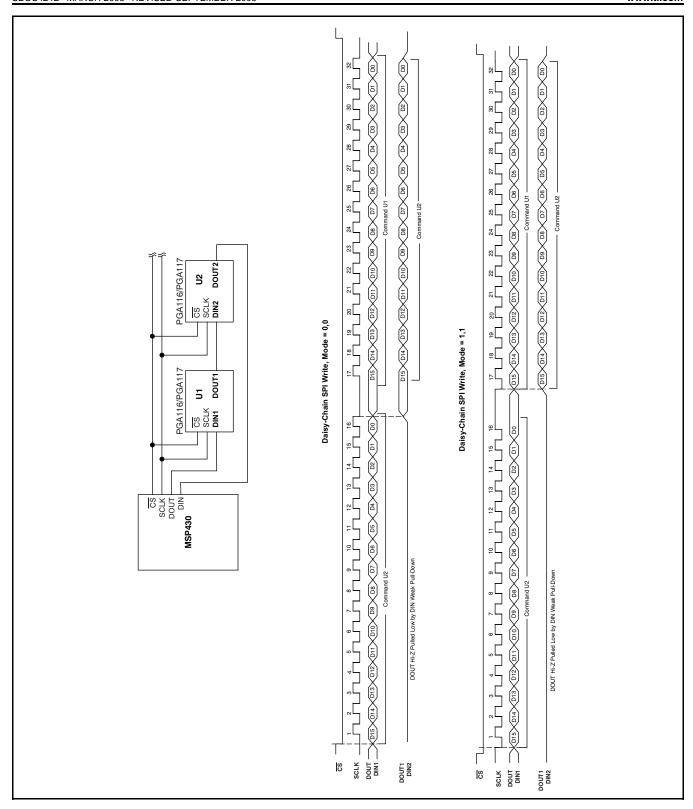

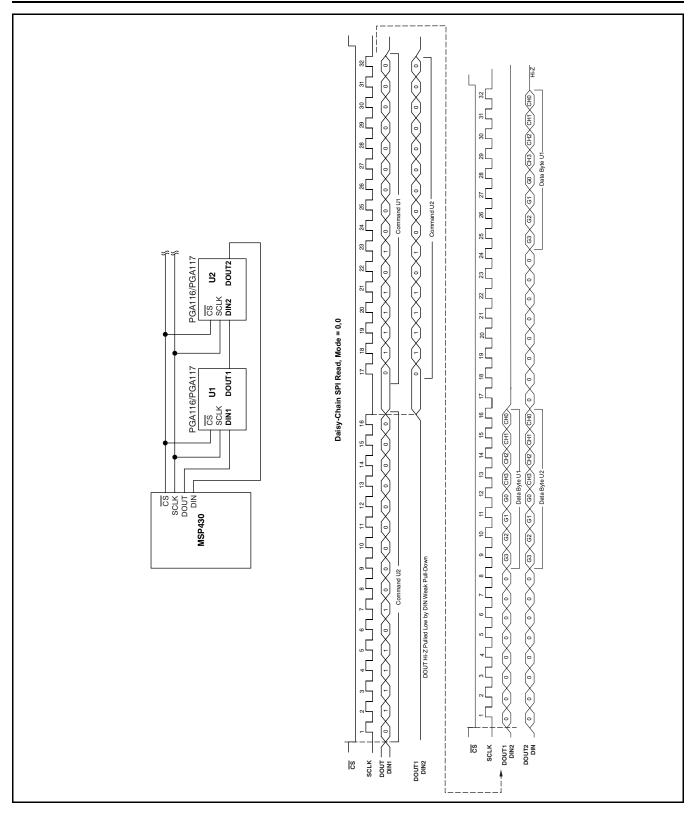

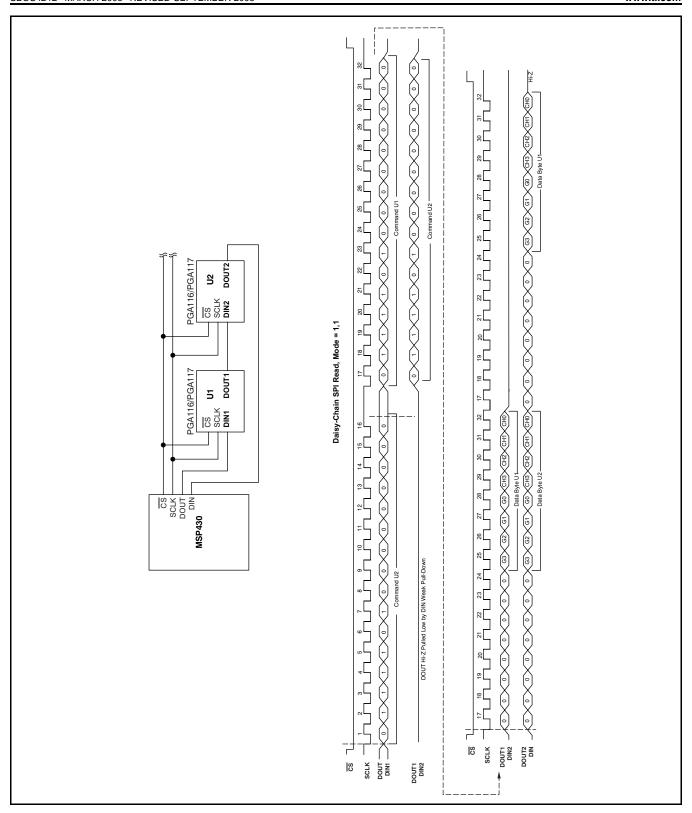

#### SERIAL DIGITAL INTERFACE: SPI DAISY-CHAIN COMMUNICATIONS

To reduce the number of I/O port pins used on a microcontroller, the PGA116/PGA117 support SPI daisy-chain communications with full read/write capability. A two-device daisy-chain configuration is shown in Figure 61, although any number of devices can be daisy-chained. The SPI daisy-chain communication uses a common SCLK and CS line for all devices in the daisy chain, rather than each device requiring a separate CS line. The daisy-chain mode of communication routes data serially through each device in the chain by using its respective DIN and DOUT pins as shown. Special commands are

used (see Table 4) to ensure that data are written or read in the proper sequence. There is a special daisy-chain NOP command (No OPeration) which, when presented to the desired device in the daisy-chain, causes no changes in that respective device. Detailed timing diagrams for daisy-chain operation are shown in Figure 65 through Figure 67.

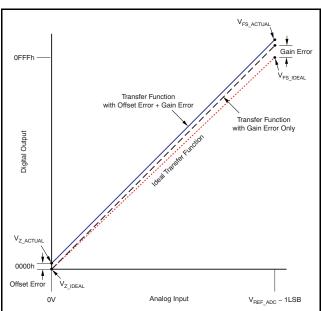

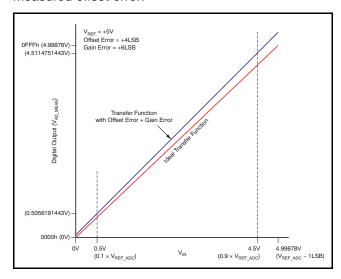

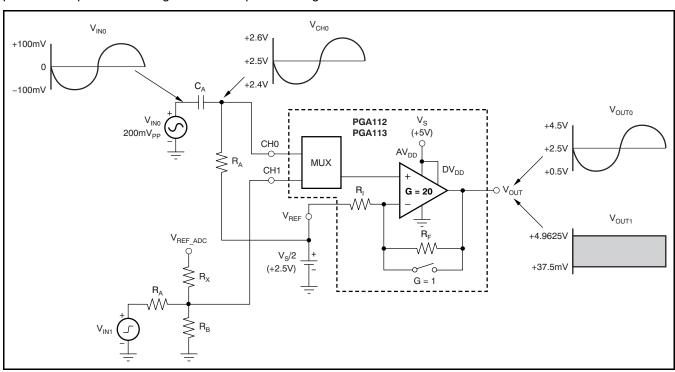

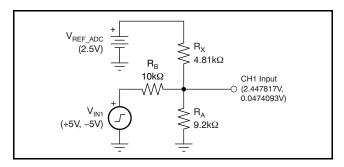

Figure 61. Daisy-Chain Read/Write Configuration