# 4 GHz to 18 GHz Divide-by-4 Prescaler

ADF5001

#### **FEATURES**

Divide-by-4 prescaler

High frequency operation: 4 GHz to 18 GHz

Integrated RF decoupling capacitors

Low power consumption

Active mode: 30 mA Power-down mode: 7 mA Low phase noise: –150 dBc/Hz

Single dc supply: 3.3 V compatible with ADF4xxx PLLs

Temperature range: -40°C to +105°C Small package: 3 mm × 3 mm LFCSP

#### **APPLICATIONS**

PLL frequency range extender Point-to-point radios VSAT radios Communications test equipment

#### **GENERAL DESCRIPTION**

The ADF5001 prescaler is a low noise, low power, fixed RF divider block that can be used to divide down frequencies as high as 18 GHz to a lower frequency suitable for input into a PLL IC, such as the ADF4156 or ADF4106. The ADF5001 provides a divide-by-4 function. The ADF5001 operates off a 3.3 V supply and has differential 100  $\Omega$  RF outputs to allow direct interface to the differential RF inputs of PLLs such as the ADF4156 and ADF4106.

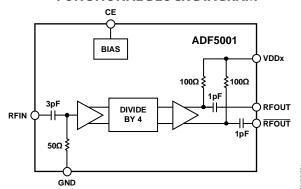

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **TABLE OF CONTENTS**

| reatures                 | J |

|--------------------------|---|

|                          |   |

| Applications             | ] |

| General Description      | 1 |

| Functional Block Diagram | 1 |

| Revision History         | 2 |

| Specifications           | 3 |

| Absolute Maximum Ratings | 4 |

| ESD Caution              | 4 |

|                          |   |

| Pin Configuration and Function Descriptions5 | , |

|----------------------------------------------|---|

| Typical Performance Characteristics6         | ó |

| Evaluation Board PCB                         | 7 |

| PCB Material Stack-Up7                       | 7 |

| Bill of Materials7                           | 7 |

| Application Circuit8                         | 3 |

| Outline Dimensions                           | ) |

| Ordering Guide9                              | ) |

#### **REVISION HISTORY**

#### 6/10—Rev. 0 to Rev. A

| Change to Features Section                    | 1 |

|-----------------------------------------------|---|

| Change to Applications Section                | 1 |

| Changes to Figure 1                           | 1 |

| Changes to Specifications Section             | 3 |

| Changes to Thermal Impedance Ratings, Table 2 | 4 |

| Changes to Figure 4 Through Figure 7          | 6 |

| Changes to Evaluation Board PCB Section       | 7 |

| Changes to Figure 8                           | 7 |

| Change to Table 4                             | 7 |

| Changes to Figure 10                          | 8 |

| Changes to Ordering Guide                     | 9 |

|                                               |   |

10/09—Revision 0: Initial Version

# **SPECIFICATIONS**

$VDD1 = VDD2 = 3.3 \ V \pm 10\%, GND = 0 \ V; dBm \ referred \ to \ 50 \ \Omega; \ T_A = T_{MIN} \ to \ T_{MAX}, unless \ otherwise \ noted. \ The \ operating \ temperature \ range \ is -40°C \ to +105°C.$

Table 1.

| Parameter                            | Min | Тур  | Max | Unit   | Test Conditions/Comments                                                                         |

|--------------------------------------|-----|------|-----|--------|--------------------------------------------------------------------------------------------------|

| RF CHARACTERISTICS                   |     |      |     |        |                                                                                                  |

| Input Frequency                      | 4   |      | 18  | GHz    |                                                                                                  |

| RF Input Sensitivity                 | -10 |      | +10 | dBm    | 4 GHz to 18 GHz                                                                                  |

| Output Power                         | -10 | -5   |     | dBm    | Single-ended output connected into 50 $\Omega$ load                                              |

|                                      | -7  | -2   |     | dBm    | Differential outputs connected into 100 $\Omega$ differential load                               |

| Output Voltage Swing                 | 200 | 330  |     | mV p-p | Peak-to-peak voltage swing on each single-ended output, connected into 50 $\Omega$ load          |

|                                      | 400 | 660  |     | mV p-p | Peak-to-peak voltage swing on differential output, connected into $100 \Omega$ differential load |

|                                      |     | 1000 |     | mV p-p | Peak-to-peak voltage swing on each single-<br>ended output, no load condition                    |

| Phase Noise                          |     | -150 |     | dBc/Hz | Input frequency $(f_{IN}) = 12$ GHz, offset = 100 kHz                                            |

| Reverse Leakage                      |     | -60  |     | dBm    | RF input power $(P_{IN}) = 0$ dBm, RF <sub>OUT</sub> = 4 GHz                                     |

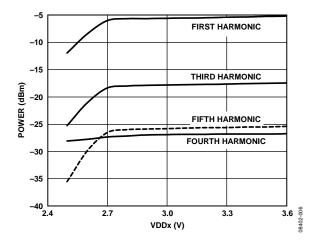

| Second Harmonic Content              |     | -38  |     | dBc    |                                                                                                  |

| Third Harmonic Content               |     | -12  |     | dBc    |                                                                                                  |

| Fourth Harmonic Content              |     | -20  |     | dBc    |                                                                                                  |

| Fifth Harmonic Content               |     | -19  |     | dBc    |                                                                                                  |

| CE INPUT                             |     |      |     |        |                                                                                                  |

| V <sub>IH</sub> , Input High Voltage | 2.2 |      |     | V      |                                                                                                  |

| V <sub>I</sub> ., Input Low Voltage  |     |      | 0.3 | V      |                                                                                                  |

| POWER SUPPLIES                       |     |      |     |        |                                                                                                  |

| Voltage Supply                       | 3.0 | 3.3  | 3.6 | V      |                                                                                                  |

| IDD (IDD1 + IDD2)                    |     |      |     |        |                                                                                                  |

| Active                               |     | 30   | 60  | mA     | CE is high                                                                                       |

| Power-Down                           |     | 7    | 25  | mA     | CE is low                                                                                        |

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| 14014 21                     |                  |

|------------------------------|------------------|

| Parameter                    | Rating           |

| VDDx to GND                  | -0.3 V to +3.9 V |

| RFIN                         | 10 dBm           |

| Operating Temperature Range  |                  |

| Industrial (B Version)       | −40°C to +105°C  |

| Storage Temperature Range    | −65°C to +150°C  |

| Maximum Junction Temperature | 150°C            |

| LFCSP Thermal Impedance      |                  |

| $\theta_{JA}$ (Ambient)      | 90°C/W           |

| $\theta_{JC}(Case)$          | 30°C/W           |

| Peak Temperature             | 260°C            |

| Time at Peak Temperature     | 40 sec           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device is a high performance RF integrated circuit with an ESD rating of 2 kV, human body model (HBM) and is ESD sensitive. Proper precautions should be taken for handling and assembly.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

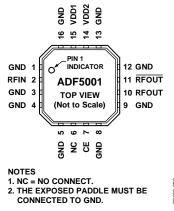

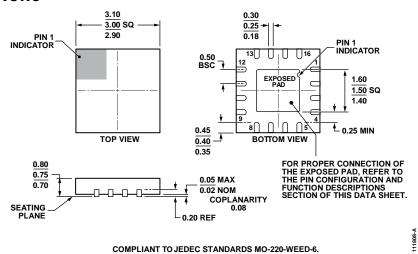

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 3. Pin Function Descriptions**

| Pin No.                         | Mnemonic | Description                                                                                                                                                                                                                                   |

|---------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 4, 5, 8, 9, 12,<br>13, 16 | GND      | RF Ground. All ground pins should be tied together.                                                                                                                                                                                           |

| 2                               | RFIN     | Single-Ended 50 $\Omega$ Input to the RF Prescaler. This pin is ac-coupled internally via a 3 pF capacitor.                                                                                                                                   |

| 6                               | NC       | No Connect. This pin can be left unconnected.                                                                                                                                                                                                 |

| 7                               | CE       | Chip Enable. This pin is active high. When CE is brought low, the part enters into power-down mode. If this functionality is not required, the pin can remain unconnected because it is pulled up internally through a weak pull-up resistor. |

| 10                              | RFOUT    | Divided Down Output of the Prescaler. This pin has an internal 100 $\Omega$ load resistor tied to VDD2 and an ac-coupling capacitor of 1 pF.                                                                                                  |

| 11                              | RFOUT    | Complementary Divided Down Output of the Prescaler. This pin has an internal 100 $\Omega$ load resistor tied to VDD2 and an ac-coupling capacitor of 1 pF.                                                                                    |

| 14                              | VDD2     | Voltage Supply for the Output Stage. Decouple this pin to ground with a 1 nF capacitor and tie it directly to VDD1.                                                                                                                           |

| 15                              | VDD1     | Voltage Supply for the Input Stage and Divider Block. Decouple this pin to ground with a 1 nF capacitor.                                                                                                                                      |

| N/A <sup>1</sup>                | EP       | The LFCSP package has an exposed paddle that must be connected to GND.                                                                                                                                                                        |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

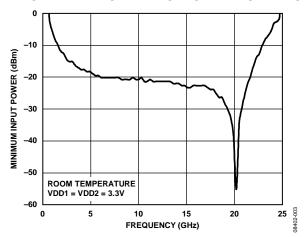

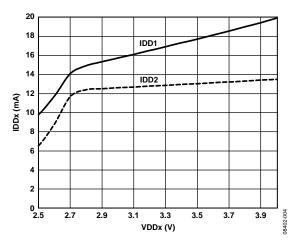

# TYPICAL PERFORMANCE CHARACTERISTICS

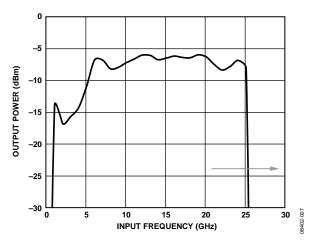

Figure 3. RFIN Sensitivity

Figure 4. IDD1 and IDD2 vs. VDDx

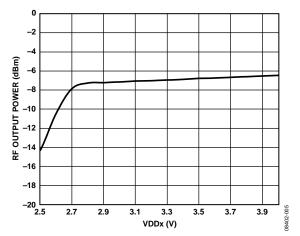

Figure 5. RFOUT Power (Single-Ended) vs. VDDx,  $f_{IN} = 10$  GHz,  $P_{IN} = 0$  dBm

Figure 6. RFOUT Harmonic Content

Figure 7. RFOUT Power vs. RFIN Frequency,  $f_{IN} = 10$  GHz,  $V_{DD} = 3.3$  V

## **EVALUATION BOARD PCB**

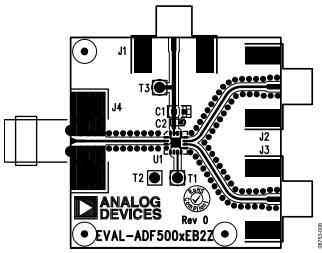

The evaluation board has four connectors as shown in Figure 8. The RF input connector (J4) is a high frequency precision SMA connector from Emerson. This connector is mechanically compatible with SMA/3.5 mm and 2.92 mm cables.

Figure 8. Evaluation Board Silkscreen—Top View

The evaluation board is powered from a single 3.0 V to 3.6 V supply, which should be connected to the J1 SMA connector. The power supply can also be connected using the T3 (VDDx) and T2 (GND) test points.

The differential RF outputs are brought out on the J2 and J3 SMA connectors. If only one of the outputs is being used, the unused output should be correctly terminated using a 50  $\Omega$  SMA termination.

The chip enable (CE) pin can be controlled using the T1 test point. If this function is not required, the test point can remain unconnected.

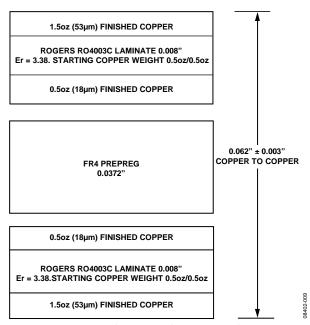

#### **PCB MATERIAL STACK-UP**

The evaluation board is built using Rogers RO4003C material (0.008 in.). RF track widths are 0.015 in. to achieve a controlled 50  $\Omega$  characteristic impedance. The complete PCB stack-up is shown in Figure 9.

Figure 9. Evaluation Board PCB Layer Stack-Up

#### **BILL OF MATERIALS**

Table 4.

| Qty. | Reference<br>Designator | Description Supplier/Part Numb |                                      |

|------|-------------------------|--------------------------------|--------------------------------------|

| 1    | C1                      | 0.1 μF, 0603<br>capacitor      | Murata<br>GRM188R71H104KA93D         |

| 1    | C2                      | 10 pF, 0402<br>capacitor       | Murata<br>GRM1555C1H100JZ01D         |

| 1    | J4                      | 3.5 mm RF SMA connector        | Emerson 142-0761-801                 |

| 3    | J1, J2, J3              | 3.5 mm RF SMA connector        | Johnson Components<br>142-0701-851   |

| 3    | T1, T2, T3              | Test points                    | Vero 20-2137                         |

| 1    | U1                      | ADF5001 RF<br>prescaler        | Analog Devices, Inc.,<br>ADF5001BCPZ |

## **APPLICATION CIRCUIT**

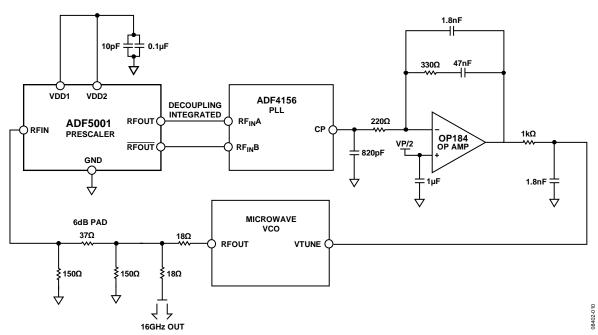

The ADF5001 can be connected either single-ended or differentially to any of the Analog Devices PLL family of ICs. It is recommended to use a differential connection for best performance and to achieve maximum power transfer. The application circuit shown in Figure 10 shows the ADF5001 used as the RF prescaler in a microwave 16 GHz PLL loop. The ADF5001 divides down the 16 GHz RF signal to 4 GHz, which is input differentially into the ADF4156 PLL. An active filter topology, using the OP184 op amp, is used to provide the wide tuning ranges

typically required by microwave VCOs. The positive input pin of the OP184 is biased at half the ADF4156 charge pump supply (VP). This can be easily achieved using a simple resistor divider, ensuring sufficient decoupling close to the +IN A pin of the OP184 thereby allowing the use of a single positive supply for the op amp. Alternatively, to optimize performance by ensuring a clean bias voltage, a low noise regulator like the ADP150 can be used to power the resistor divider network or the +IN A pin directly.

Figure 10. ADF5001 Used as the RF Prescaler in a Microwave 16 GHz PLL Loop

# **OUTLINE DIMENSIONS**

Figure 11. 16-Lead Lead Frame Chip Scale Package [LFCSP\_WQ] 3 mm × 3 mm Body, Very Very Thin Quad (CP-16-18) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature<br>Range | Package Description                                               | Package<br>Option | Branding |

|--------------------|----------------------|-------------------------------------------------------------------|-------------------|----------|

| ADF5001BCPZ        | −40°C to +105°C      | 16-Lead Lead Frame Chip Scale Package (LFCSP_WQ)                  | CP-16-18          | Q1S      |

| ADF5001BCPZ-RL7    | -40°C to +105°C      | 16-Lead Lead Frame Chip Scale Package (LFCSP_WQ), 7"Tape and Reel | CP-16-18          | Q1S      |

| EVAL-ADF5001EB2Z   |                      | Evaluation Board                                                  |                   |          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

**NOTES**

# **NOTES**

NOTES

# AMEYA360 Components Supply Platform

## **Authorized Distribution Brand:**

## Website:

Welcome to visit www.ameya360.com

## Contact Us:

## > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

## > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

## Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com