# Parallel RTC With CPU Supervisor

#### **Features**

- ➤ Real-Time Clock counts seconds through years in BCD format

- On-chip battery-backup switchover circuit with nonvolatile control for external SRAM

- ➤ Less than 500nA of clock operation current in backup mode

- ➤ Microprocessor reset valid to V<sub>CC</sub> = V<sub>SS</sub>

- ➤ Independent watchdog timer with a programmable time-out period

- ➤ Power-fail interrupt warning

- Programmable clock alarm interrupt active in battery-backup mode

- ➤ Programmable periodic interrupt

- ➤ Battery-low warning

## **General Description**

The bq4845 Real-Time Clock is a low-power microprocessor peripheral that integrates a time-of-day clock, a 100-year calendar, and a CPU supervisor in a 28-pin SOIC or DIP. The bq4845 is ideal for fax machines, copiers, industrial control systems, point-of-sale terminals, data loggers, and computers.

The bq4845 provides direct connections for a 32.768KHz quartz crystal and a 3V backup battery. Through the use of the conditional chip enable output  $(\overline{CE}_{OUT})$  and battery voltage output  $(V_{OUT})$  pins, the bq4845 can write-protect and make nonvolatile external SRAMs. The backup cell powers the real-time clock and maintains SRAM information in the absence of system voltage.

The bq4845 contains a temperaturecompensated reference and comparator circuit that monitors the status of its voltage supply. When the bq4845 detects an out-of-tolerance condition, it generates an interrupt warning and subsequently a microprocessor reset. The reset stays active for 200ms after  $V_{\rm CC}$  rises within tolerance, to allow for power supply and processor stabilization.

The bq4845 also has a built-in watchdog timer to monitor processor operation. If the microprocessor does not toggle the watchdog input (WDI) within the programmed time-out period, the bq4845 asserts WDO and RST. WDI unconnected disables the watchdog timer.

The bq4845 can generate other interrupts based on a clock alarm condition or a periodic setting. The alarm interrupt can be set to occur from once per second to once per month. The alarm can be made active in the battery-backup mode to serve as a system wake-up call. For interrupts at a rate beyond once per second, the periodic interrupt can be programmed with periods of  $30.5\mu s$  to 500ms.

## **Pin Connections**

#### 28 \ \ \ V\_CC Vout 📮 27 | WE X<sub>1</sub> $\Box$ 2 X<sub>2</sub> □ 26 🗆 CE<sub>IN</sub> WDO d 25 CEOUT <u>INT</u> ☐ 5 24 | BC 23 | WDI RST [ A<sub>3</sub> □ 22 D OE 21 CS 20 V<sub>SS</sub> A<sub>2</sub> □ 8 A<sub>1</sub> □ 9 A<sub>0</sub> 19 DQ<sub>7</sub> DQ<sub>0</sub> □ 11 18 DQ8 17 DQ5 DQ<sub>1</sub> 12 DQ<sub>2</sub> 13 16 DQ4 14 15 DQ<sub>3</sub> V<sub>SS</sub> □ 28-DIP or SOIC

Aug. 1995

### **Pin Names**

| A <sub>0</sub> -A <sub>3</sub>      | Clock/control address inputs | BC               | Backup battery input   |

|-------------------------------------|------------------------------|------------------|------------------------|

| DQ <sub>0</sub> –DQ <sub>7</sub>    | Data inputs/outputs          | $V_{\text{OUT}}$ | Back-up battery output |

| $\overline{\mathrm{WE}}$            | Write enable                 | ĪNT              | Interrupt output       |

| $\overline{\text{OE}}$              | Output enable                | RST              | Microprocessor reset   |

| CS                                  | Chip select input            | WDI              | Watchdog input         |

| $\overline{\text{CE}}_{\text{IN}}$  | External RAM chip enable     | WDO              | Watchdog output        |

| $\overline{\text{CE}}_{\text{OUT}}$ | Conditional RAM chip         | $V_{CC}$         | +5V supply             |

|                                     | enable                       | $V_{SS}$         | Ground                 |

| X1-X2                               | Crystal inputs               |                  |                        |

## **Functional Description**

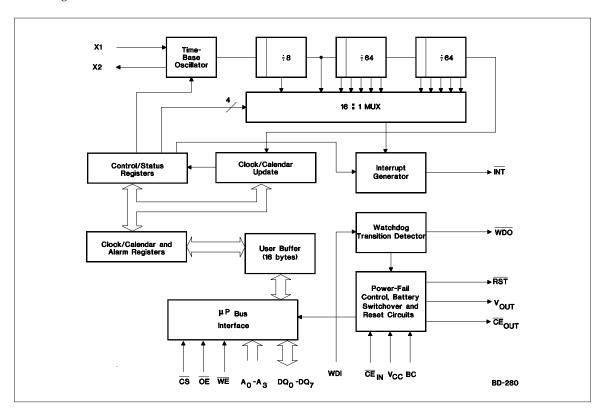

Figure 1 is a block diagram of the bq4845. The following sections describe the bq4845 functional operation including clock interface, data-retention modes,

power-on reset timing, watchdog timer activation, and interrupt generation.  $\,$

Figure 1. Block Diagram

## **Truth Table**

| V <sub>CC</sub>                             | CS                | ŌĒ           | WE           | CE <sub>OUT</sub>                  | V <sub>OUT</sub>  | Mode     | DQ                | Power               |

|---------------------------------------------|-------------------|--------------|--------------|------------------------------------|-------------------|----------|-------------------|---------------------|

| < V <sub>CC</sub> (max.)                    | $V_{\mathrm{IH}}$ | X            | X            | $\overline{\text{CE}}_{\text{IN}}$ | V <sub>OUT1</sub> | Deselect | High Z            | Standby             |

|                                             | $ m V_{IL}$       | X            | $V_{\rm IL}$ | $\overline{\text{CE}}_{\text{IN}}$ | V <sub>OUT1</sub> | Write    | $D_{\mathrm{IN}}$ | Active              |

| > V <sub>CC</sub> (min.)                    | $V_{\rm IL}$      | $V_{\rm IL}$ | $V_{IH}$     | $\overline{\text{CE}}_{\text{IN}}$ | V <sub>OUT1</sub> | Read     | D <sub>OUT</sub>  | Active              |

|                                             | $V_{IL}$          | $V_{IH}$     | $V_{IH}$     | $\overline{\text{CE}}_{\text{IN}}$ | V <sub>OUT1</sub> | Read     | High Z            | Active              |

| < V <sub>PFD</sub> (min.) > V <sub>SO</sub> | X                 | X            | X            | VoH                                | V <sub>OUT1</sub> | Deselect | High Z            | CMOS standby        |

| ≤ V <sub>SO</sub>                           | X                 | X            | X            | V <sub>OHB</sub>                   | V <sub>OUT2</sub> | Deselect | High Z            | Battery-backup mode |

## **Pin Descriptions**

#### X1-X2 Crystal inputs

X1–X2 are a direct connection for a 32.768kHZ, 6pF crystal.

#### **RST** Reset output

$\overline{RST}$  goes low whenever  $V_{CC}$  falls below the power fail threshold.  $\overline{RST}$  will remain low for 200ms typical after  $V_{CC}$  crosses the threshold on power-up.  $\overline{RST}$  also goes low whenever a watchdog timeout occurs.  $\overline{RST}$  is an opendrain output.

#### **INT** Interrupt output

$\overline{INT}$  goes low when a power fail, periodic, or alarm condition occurs.  $\overline{INT}$  is an open-drain output.

#### WDI Watchdog input

WDI is a three-level input. If WDI remains either high or low for longer than the watchdog time-out period (1.5 seconds default), WDO goes low. WDO remains low until the next transition at WDI. Leaving WDI unconnected disables the watchdog function. WDI connects to an internal voltage divider between  $V_{OUT}$  and  $V_{SS},$  which sets it to mid-supply when left unconnected.

#### WDO Watchdog output

WDO goes low if WDI remains either high or low longer than the watchdog time-out period. WDO returns high on the next transition at WDI. WDO remains high if WDI is unconnected.

#### A<sub>0</sub>-A<sub>3</sub> Clock address inputs

$A_0$ - $A_3$  allow access to the 16 bytes of real-time clock and control registers.

#### DQ<sub>0</sub>-DQ<sub>7</sub> Data input and output

$DQ_0\!-\!DQ_7$  provide x8 data for real-time clock information. These pins connect to the memory data bus.

#### V<sub>SS</sub> Ground

#### **CS** Chip select

#### Output enable

$\overline{\text{OE}}$  provides the read control for the RTC memory locations.

#### **CE**<sub>OUT</sub> Chip enable output

$\overline{CE}_{OUT}$  goes low only when  $\overline{CE}_{IN}$  is low and  $V_{CC}$  is above the power fail threshold. If  $\overline{CE}_{IN}$  is low, and power fail occurs,  $\overline{CE}_{OUT}$  stays low for 100µs or until  $\overline{CE}_{IN}$  goes high, whichever occurs first.

#### **CE**<sub>IN</sub> Chip enable input

$\overline{\text{CE}}_{IN}$  is the input to the chip-enable gating circuit.

#### BC Backup battery input

BC should be connected to a 3V backup cell. A voltage within the  $V_{BC}$  range on the BC pin should be present upon power up to provide proper oscillator start-up.

#### V<sub>OUT</sub> Output supply voltage

$V_{OUT}$  provides the higher of  $V_{CC}$  or  $V_{BC},\\$  switched internally, to supply external RAM.

#### WE Write enable

WE provides the write control for the RTC memory locations.

#### V<sub>CC</sub> Input supply voltage

+5V input

## **Address Map**

The bq4845 provides 16 bytes of clock and control status registers. Table 1 is a map of the bq4845 registers, and Table 2 describes the register bits.

## **Clock Memory Interface**

The bq4845 has the same interface for clock/calendar and control information as standard SRAM. To read and write to these locations, the user must put the bq4845 in the proper mode and meet the timing requirements.

#### **Read Mode**

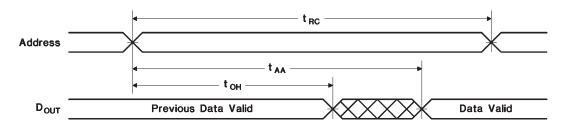

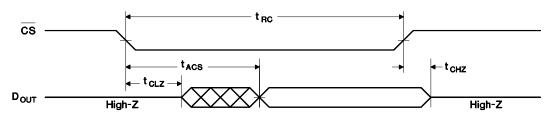

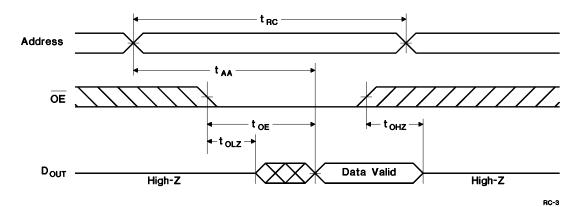

The bq4845 is in read mode whenever  $\overline{OE}$  (Output enable) is low and  $\overline{CS}$  (chip select) is low. The unique address, specified by the 4 address inputs, defines which one of the 16 clock/calendar bytes is to be accessed. The bq4845 makes valid data available at the data I/O pins within  $t_{AA}$  (address access time). This occurs after the last address input signal is stable, and providing the  $\overline{CS}$  and  $\overline{OE}$  (output enable) access times are met. If the  $\overline{CS}$  and  $\overline{OE}$  access times are not met, valid data is available after the latter of chip select access time ( $t_{ACS}$ ) or output enable access time ( $t_{OE}$ ).

$\overline{CS}$  and  $\overline{OE}$  control the state of the eight three-state data I/O signals. If the outputs are activated before  $t_{AA},$

Table 1. bq4845 Clock and Control Register Map

| Table 1. bq4043 Clock and Control Negister Map |        |         |          |          |                   |           |                    |                        |                      |                    |

|------------------------------------------------|--------|---------|----------|----------|-------------------|-----------|--------------------|------------------------|----------------------|--------------------|

| Ad-<br>dress<br>(h)                            | D7     | D6      | D5       | D4       | D3                | D2        | D1                 | D0                     | 12-Hour<br>Range (h) | Register           |

| 0                                              | 0      | 10-s    | second d | igit     |                   | 1-secon   | d digit            |                        | 00-59                | Seconds            |

| 1                                              | ALM1   | ALM0    | second d | igit     |                   | 1-secon   | ıd digit           |                        | 00-59                | Seconds alarm      |

| 2                                              | 0      |         |          | 0        |                   | 1         |                    |                        | 00–59                | Minutes            |

| 2                                              | U      | 10-1    | ninute d | igit     |                   | 1-mmu     | te digit           |                        | 00-39                | Minutes            |

| 3                                              | ALM1   | ALM0    |          |          |                   | 1-minu    | to digit           |                        | 00–59                | Minutes alarm      |

|                                                | ALIVII | 10-n    | ninute d | igit     |                   | 1-1111111 | te digit           |                        | 00-33                | Williates alai ili |

| 4                                              | PM/AM  | 0       | 10-hou   | ır digit |                   | 1-hou     | r digit            |                        | 01–12 AM/ 81– 92 PM  | Hours              |

| 5                                              | ALM1   | ALM0    | 10-hou   | ır digit | -                 |           | 01–12 AM/ 81–92 PM | Hours alarm            |                      |                    |

|                                                | PM/AM  |         |          |          |                   |           |                    |                        |                      |                    |

| 6                                              | 0      | 0       | 10-da    | y digit  |                   | 1-day     | digit              |                        | 01-31                | Day                |

| 7                                              | ALM1   | ALM0    | 10-da    | y digit  |                   | 1-day     | digit              |                        | 01-31                | Day alarm          |

| 8                                              | 0      |         | 0        |          | 0                 | Day-o     | of-week di         | igit                   | 01-07                | Day-of-week        |

| 9                                              | 0      | 0       | 0        | 10 mo.   |                   | 1-mont    | h digit            |                        | 01-12                | Month              |

| A                                              |        | 10-year | digit    |          |                   | 1-year    | digit              |                        | 00-99                | Year               |

| В                                              | *      | WD2     | WD1      | WD0      | RS3               | RS2       | RS1                | RS0                    |                      | Programmable rates |

| С                                              | *      |         | *        |          | AIE PIE PWRIE ABE |           |                    | Interrupt en-<br>ables |                      |                    |

| D                                              | *      |         | *        | ·        | AF                | PF        | PWRF               | BVF                    |                      | Flags              |

| E                                              | *      |         | *        |          | UTI               |           |                    |                        | Control              |                    |

| F                                              | *      | *       | *        | *        | *                 | *         | *                  | *                      |                      | Unused             |

Notes:

\* = Unused bits; unwritable and read as 0.

0 = should be set to 0 for valid time/calendar range.

Clock calendar data in BCD. Automatic leap year adjustment.

PM/AM = 1 for PM; PM/AM = 0 for AM.

DSE = 1 enables daylight savings adjustment.

24/12 = 1 enables 24-hour data representation; 24/12 = 0 enables 12-hour data representation.

Day-of-Week coded as Sunday = 1 through Saturday = 7.

BVF = 1 for valid battery.

$\overline{\text{STOP}} = 1 \text{ turns the RTC on; } \overline{\text{STOP}} = 0 \text{ stops the RTC in back-up mode.}$

**Table 2. Clock and Control Register Bits**

| Bits      | Description                                   |

|-----------|-----------------------------------------------|

| 24/12     | 24- or 12-hour representation                 |

| ABE       | Alarm interrupt enable in battery-backup mode |

| AF        | Alarm interrupt flag                          |

| AIE       | Alarm interrupt enable                        |

| ALM0-ALM1 | Alarm mask bits                               |

| BVF       | Battery-valid flag                            |

| DSE       | Daylight savings time enable                  |

| PF        | Periodic interrupt flag                       |

| PIE       | Periodic interrupt enable                     |

| PM/AM     | PM or AM indication                           |

| PWRF      | Power-fail interrupt flag                     |

| PWRIE     | Power-fail interrupt enable                   |

| RS0-RS3   | Periodic interrupt rate                       |

| STOP      | Oscillator stop and start                     |

| UTI       | Update transfer inhibit                       |

| WD0 - WD2 | Watchdog time-out rate                        |

the data lines are driven to an indeterminate state until  $t_{AA}$ . If the address inputs are changed while  $\overline{CS}$  and  $\overline{OE}$  remain low, output data remains valid for  $t_{OH}$  (output data hold time), but goes indeterminate until the next address access.

#### Write Mode

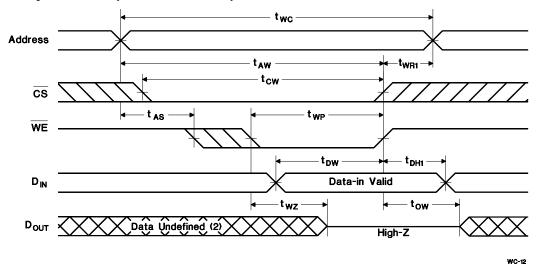

The bq4845 is in write mode whenever  $\overline{WE}$  and  $\overline{CS}$  are active. The start of a write is referenced from the latter-occurring falling edge of  $\overline{WE}$  or  $\overline{CS}$ . A write is terminated by the earlier rising edge of  $\overline{WE}$  or  $\overline{CS}$ . The addresses must be held valid throughout the cycle.  $\overline{CS}$  or  $\overline{WE}$  must return high for a minimum of  $t_{WR2}$  from  $\overline{CS}$  or  $t_{WR1}$  from  $\overline{WE}$  prior to the initiation of another read or write cycle.

Data-in must be valid  $t_{DW}$  prior to the end of write and remain valid for  $t_{DH1}$  or  $t_{DH2}$  afterward.  $\overline{OE}$  should be kept high during write cycles to avoid bus contention; although, if the output bus has been activated by a low on  $\overline{CS}$  and  $\overline{OE}$ , a low on  $\overline{WE}$  disables the outputs  $t_{WZ}$  after  $\overline{WE}$  falls.

#### Reading the Clock

Once every second, the user-accessible clock/calendar locations are updated simultaneously from the internal real time counters. To prevent reading data in transition, updates to the bq4845 clock registers should be halted. Updating is halted by setting the update transfer inhibit (UTI) bit D3 of the control register E. As long as the UTI bit is 1, updates to user-accessible clock locations are inhibited. Once the frozen clock information is retrieved by reading the appropriate clock memory locations, the UTI bit should be reset to 0 in order to allow updates to occur from the internal counters. Because the internal counters are not halted by setting the UTI bit, reading the clock locations has no effect on clock accuracy. Once the UTI bit is reset to 0, the internal registers update within one second the user-accessible registers with the correct time. A halt command issued during a clock update allows the update to occur before freezing the data.

#### **Setting the Clock**

The UTI bit must also be used to set the bq4845 clock. Once set, the locations can be written with the desired information in BCD format. Resetting the UTI bit to 0 causes the written values to be transferred to the internal clock counters and allows updates to the user-accessible registers to resume within one second.

#### Stopping and Starting the Clock Oscillator

The bq4845 clock can be programmed to turn off when the part goes into battery back-up mode by setting  $\overline{STOP}$  to 0 prior to power down. If the board using the bq4845 is to spend a significant period of time in storage, the  $\overline{STOP}$  bit can be used to preserve some battery capacity.  $\overline{STOP}$  set to 1 keeps the clock running when  $V_{CC}$  drops below  $V_{SO}$ . With  $V_{CC}$  greater than  $V_{SO}$ , the bq4845 clock runs regardless of the state of  $\overline{STOP}$ .

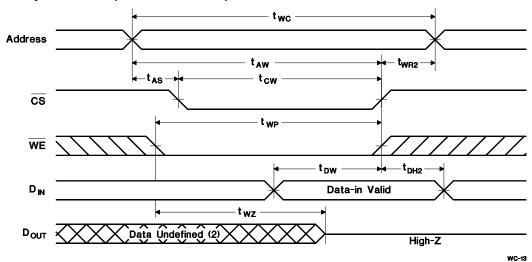

## Power-Down/Power-Up Cycle

The bq4845 continuously monitors  $V_{CC}$  for out-of-tolerance. During a power failure, when  $V_{CC}$  falls below  $V_{PFD}$ , the bq4845 write-protects the clock and storage registers. When  $V_{CC}$  is below  $V_{BC}$  (3V typical), the power source is switched to BC. RTC operation and storage data are sustained by a valid backup energy source. When  $V_{CC}$  is above  $V_{BC}$ , the power source is  $V_{CC}$ . Write-protection continues for  $t_{CSR}$  time after  $V_{CC}$  rises above  $V_{PFD}$ .

An external CMOS static RAM is battery-backed using the  $V_{OUT}$  and chip enable output pins from the bq4845. As the voltage input  $V_{CC}$  slews down during a power failure, the chip enable output,  $\overline{CE}_{O\underline{UT}}$  is forced inactive independent of the chip enable input  $\overline{CE}_{IN}$

This activity unconditionally write-protects the external SRAM as  $V_{CC}$  falls below  $V_{PFD}$ . If a memory access is in progress to the external SRAM during power-fail detection, that memory cycle continues to completion before the memory is write-protected. If the memory cycle is not terminated within time  $t_{WPT}$ , the chip enable output is unconditionally driven high, write-protecting the controlled SRAM.

As the supply continues to fall past  $V_{PFD}$ , an internal switching device forces  $V_{OUT}$  to the external backup energy source.  $\overline{CE}_{OUT}$  is held high by the  $V_{OUT}$  energy source.

During power-up,  $V_{OUT}$  is switched back to the 5V supply as  $V_{CC}$  rises above the backup cell input voltage sourcing  $V_{OUT}$ .  $\overline{CE}_{OUT}$  is held inactive for time  $t_{CER}$  after the power supply has reached  $V_{PFD}$ , independent of the  $\overline{CE}_{IN}$  input, to allow for processor stabilization.

During power-valid operation, the  $\overline{CE}_{IN}$  input is passed through to the  $\overline{CE}_{OUT}$  output with a propagation delay of less than 12ns.

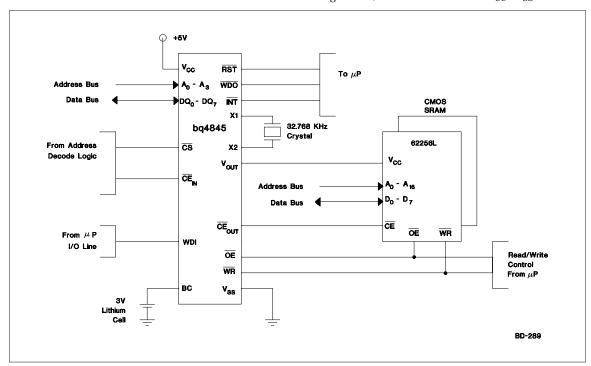

Figure 2 shows the hardware hookup for the external RAM, battery, and crystal.

A primary backup energy source input is provided on the bq4845. The BC input accepts a 3V primary battery, typically some type of lithium chemistry. Since the bq4845 provides for reverse battery charging protection, no diode or current limiting resistor is needed in series with the cell. To prevent battery drain when there is no valid data to retain,  $V_{\rm OUT}$  and  $\overline{\rm CE}_{\rm OUT}$  are internally isolated from BC by the initial connection of a battery. Following the first application of  $V_{\rm CC}$  above  $V_{\rm PFD}$ , this isolation is broken, and the backup cell provides power to  $V_{\rm OUT}$  and  $\overline{\rm CE}_{\rm OUT}$  for the external SRAM.

The crystal should be located as close to X1 and X2 as possible and meet the specifications in the Crystal Specification Table. With the specified crystal, the bq4845 RTC will be accurate to within one minute per month at room temperature. In the absence of a crystal, a 32.768 kHz waveform can be fed into X1 with X2 grounded.

#### **Power-On Reset**

$\begin{array}{l} \underline{The} \ \ bq4845 \ \ provides \ \ a \ \ power-on \ \ reset, \ which \ pulls \ the \\ \overline{RST} \ pin \ low \ on \ power-down \ and \ remains \ low \ on \ power-up \ for \ t_{RST} \ \ after \ V_{CC} \ passes \ V_{PFD}. \ With \ valid \ battery \ voltage \ on \ BC, \ \overline{RST} \ remains \ valid \ for \ V_{CC} = V_{SS}. \end{array}$

Figure 2. bq4845 Application Circuit

## **Watchdog Timer**

The watchdog monitors microprocessor activity through the Watchdog input (WDI). To use the watchdog function, connect WDI to a bus line or a microprocessor I/O line. If WDI remains high or low for longer than the watchdog time-out period (1.5 seconds default), the bq4845 asserts  $\overline{WDO}$  and  $\overline{RST}$ .

#### Watchdog Input

The bq4845 resets the watchdog timer if a change of state (high to low, low to high, or a minimum 100ns pulse) occurs at the Watchdog input (WDI) during the watchdog period. The watchdog time-out is set by WD0-WD2 in register B. The bq4845 maintains the watchdog time-out programming through power cycles. The default state (no valid battery power) of WD0-WD2 is 000 or 1.5s on power-up. Table 3 shows the programmable watchdog time-out rates. The watchdog time-out period immediately after a reset is equal to the programmed watchdog time-out.

To disable the watchdog function, leave WDI floating. An internal resistor network  $(100k\Omega)$  equivalent impedance

at WDI) biases WDI to approximately 1.6V. Internal comparators detect this level and disable the watchdog timer. When  $V_{\rm CC}$  is below the power-fail threshold, the bq4845 disables the watchdog function and disconnects WDI from its internal resistor network, thus making it high impedance.

#### **Watchdog Output**

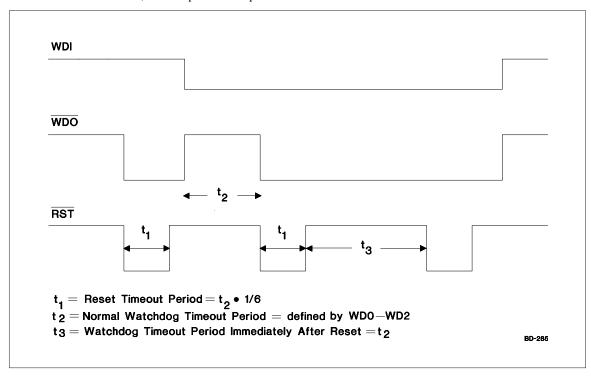

The Watchdog output  $(\overline{WDO})$  remains high if there is a transition or pulse at WDI during the watchdog time-out period. The bq4845 disables the watchdog function and  $\overline{WDO}$  is a logic high when  $V_{CC}$  is below the power fail threshold, battery-backup mode is enabled, or WDI is an open circuit. In watchdog mode, if no transition occurs at WDI during the watchdog time-out period, the bq4845 asserts  $\overline{RST}$  for the reset time-out period t1.  $\overline{WDO}$  goes low and remains low until the next transition at WDI. If WDI is held high or low indefinitely,  $\overline{RST}$  will generate pulses (t1 seconds wide) every t3 seconds. Figure 3 shows the watchdog timing.

Figure 3. Watchdog Time-out Period and Reset Active Time

### Interrupts

The bq4845 allows three individually selected interrupt events to generate an interrupt request on the  $\overline{INT}$  pin. These three interrupt events are:

- The periodic interrupt, programmable to occur once every 30.5µs to 500ms

- The alarm interrupt, programmable to occur once per second to once per month

- The power-fail interrupt, which can be enabled to be asserted when the bq4845 detects a power failure

The periodic, alarm, and power-fail interrupts are enabled by an individual interrupt-enable bit in register C, the interrupts register. When an event occurs, its event flag bit in the flags register, register D, is set. If the corresponding event enable bit is also set, then an interrupt request is generated. Reading the flags register clears all flag bits and makes  $\overline{\text{INT}}$  high impedance. To reset the flag register, the bq4845 addresses must be held stable at register D for at least 50ns to avoid inadvertent resets.

#### **Periodic Interrupt**

Bits RS3–RS0 in the interrupts register program the rate for the periodic interrupt. The user can interpret the interrupt in two ways: either by polling the flags register for PF assertion or by setting PIE so that  $\overline{INT}$  goes active when the bq4845 sets the periodic flag. Reading the flags register resets the PF bit and returns  $\overline{INT}$  to the high-impedance state. Table 4 shows the periodic rates.

#### **Alarm Interrupt**

Registers 1, 3, 5, and 7 program the real-time clock alarm. During each update cycle, the bq4845 compares the date, hours, minutes, and seconds in the clock regis-

ters with the corresponding alarm registers. If a match between all the corresponding bytes is found, the alarm flag AF in the flags register is set. If the alarm interrupt is enabled with AIE, an interrupt request is generated on  $\overline{INT}$ . The alarm condition is cleared by a read to the flags register. ALM1 – ALM0 in the alarm registers, mask each alarm compare byte. An alarm byte is masked by setting ALM1 (D7) and ALM0 (D6) to 1. Alarm byte masking can be used to select the frequency of the alarm interrupt, according to Table 5.

The alarm interrupt can be made active while the bq4845 is in the battery-backup mode by setting ABE in the interrupts register. Normally, the  $\overline{INT}$  pin goes high-impedance during battery backup. With ABE set, however,  $\overline{INT}$  is driven low if an alarm condition occurs and the AIE bit is set. Because the AIE bit is reset during power-on reset, an alarm generated during power-on reset updates only the flags register. The user can read the flags register during boot-up to determine if an alarm was generated during power-on reset.

#### **Power-Fail Interrupt**

When  $V_{CC}$  falls to the power-fail-detect point, the power-fail flag PWRF is set. If the power-fail interrupt enable bit (PWRIE) is also set, then  $\overline{INT}$  is asserted low. The power-fail interrupt occurs  $t_{WPT}$  before the bq4845 generates a reset and deselects. The PWRIE bit is cleared on power-up.

#### **Battery-Low Warning**

The bq4845 checks the battery on power-up. When the battery voltage is approximately 2.1V, the battery-valid flag BVF in the flags register is set to a 0 indicating that clock and RAM data may be invalid.

Table 3. Watchdog Time-out Rates

| WD2 | WD1 | WD0 | Normal Watchdog<br>Time-out Period (t <sub>2</sub> , t <sub>3</sub> ) | Reset Time-out<br>Period (t <sub>1</sub> ) |

|-----|-----|-----|-----------------------------------------------------------------------|--------------------------------------------|

| 0   | 0   | 0   | 1.5s                                                                  | 0.25s                                      |

| 0   | 0   | 1   | 23.4375ms                                                             | 3.9063ms                                   |

| 0   | 1   | 0   | 46.875ms                                                              | 7.8125ms                                   |

| 0   | 1   | 1   | 93.75ms                                                               | 15.625ms                                   |

| 1   | 0   | 0   | 187.5ms                                                               | 31.25ms                                    |

| 1   | 0   | 1   | 375ms                                                                 | 62.5ms                                     |

| 1   | 1   | 0   | 750ms                                                                 | 125ms                                      |

| 1   | 1   | 1   | 3s                                                                    | 0.5s                                       |

**Table 4. Periodic Interrupt Rates**

|     | Registe | Periodic In | iterrupt |          |       |

|-----|---------|-------------|----------|----------|-------|

| RS3 | RS2     | RS1         | RS0      | Period   | Units |

| 0   | 0       | 0           | 0        | None     |       |

| 0   | 0       | 0           | 1        | 30.5175  | μs    |

| 0   | 0       | 1           | 0        | 61.035   | μs    |

| 0   | 0       | 1           | 1        | 122.070  | μs    |

| 0   | 1       | 0           | 0        | 244.141  | μs    |

| 0   | 1       | 0           | 1        | 488.281  | μs    |

| 0   | 1       | 1           | 0        | 976.5625 | μs    |

| 0   | 1       | 1           | 1        | 1.95315  | ms    |

| 1   | 0       | 0           | 0        | 3.90625  | ms    |

| 1   | 0       | 0           | 1        | 7.8125   | ms    |

| 1   | 0       | 1           | 0        | 15.625   | ms    |

| 1   | 0       | 1           | 1        | 31.25    | ms    |

| 1   | 1       | 0           | 0        | 62.5     | ms    |

| 1   | 1       | 0           | 1        | 125      | ms    |

| 1   | 1       | 1           | 0        | 250 ms   |       |

| 1   | 1       | 1           | 1        | 500      | ms    |

Table 5. Alarm Frequency (Alarm Bits D6 and D7 of Alarm Registers)

| 1h        | 3h        | 5h        | 7h        |                                                     |

|-----------|-----------|-----------|-----------|-----------------------------------------------------|

| ALM1•ALM0 | ALM1•ALM0 | ALM1•ALM0 | ALM1•ALM0 | Alarm Frequency                                     |

| 1         | 1         | 1         | 1         | Once per second                                     |

| 0         | 1         | 1         | 1         | Once per minute when seconds match                  |

| 0         | 0         | 1         | 1         | Once per hour when minutes, and seconds match       |

| 0         | 0         | 0         | 1         | Once per day when hours, minutes, and seconds match |

| 0         | 0         | 0         | 0         | When date, hours, minutes, and seconds match        |

## **Absolute Maximum Ratings**

| Symbol              | Parameter                                                             | Value       | Unit | Conditions              |

|---------------------|-----------------------------------------------------------------------|-------------|------|-------------------------|

| V <sub>CC</sub>     | DC voltage applied on $V_{CC}$ relative to $V_{SS}$                   | -0.3 to 7.0 | V    |                         |

| $V_{\mathrm{T}}$    | DC voltage applied on any pin excluding $V_{CC}$ relative to $V_{SS}$ | -0.3 to 7.0 | V    | $V_T \leq V_{CC} + 0.3$ |

| Т                   | Operating temperature                                                 | 0 to +70    | °C   | Commercial              |

| Topr                | Operating temperature                                                 | -40 to +85  | °C   | Industrial              |

| T <sub>STG</sub>    | Storage temperature                                                   | -55 to +125 | °C   |                         |

| T <sub>BIAS</sub>   | Temperature under bias                                                | -40 to +85  | °C   |                         |

| T <sub>SOLDER</sub> | Soldering temperature                                                 | +260        | °C   | For 10 seconds          |

Note:

Permanent device damage may occur if **Absolute Maximum Ratings** are exceeded. Functional operation should be limited to the Recommended DC Operating Conditions detailed in this data sheet. Exposure to conditions beyond the operational limits for extended periods of time may affect device reliability.

## Recommended DC Operating Conditions (TA = TOPR)

| Symbol          | Parameter           | Minimum | Typical | Maximum               | Unit | Notes   |

|-----------------|---------------------|---------|---------|-----------------------|------|---------|

| Vcc             | Supply voltage      | 4.5     | 5.0     | 5.5                   | V    | bq4845Y |

| VCC             | Supply voltage      | 4.75    | 5.0     | 5.5                   | V    | bq4845  |

| V <sub>SS</sub> | Supply voltage      | 0       | 0       | 0                     | V    |         |

| V <sub>IL</sub> | Input low voltage   | -0.3    | -       | 0.8                   | V    |         |

| V <sub>IH</sub> | Input high voltage  | 2.2     | -       | V <sub>CC</sub> + 0.3 | V    |         |

| V <sub>BC</sub> | Backup cell voltage | 2.3     | -       | 4.0                   | V    |         |

Note: Typical values indicate operation at  $T_A$  = 25°C.

•

# DC Electrical Characteristics (TA = TOPR, $VCCmin \le VCC \le VCCmax$ )

| Symbol            | Parameter                   | Minimum                | Typical  | Maximum | Unit | Conditions/Notes                                                                                                                                |

|-------------------|-----------------------------|------------------------|----------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| $I_{LI}$          | Input leakage current       | -                      | -        | ± 1     | μΑ   | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                                   |

| $I_{LO}$          | Output leakage current      | -                      | -        | ± 1     | μΑ   | $\overline{CS} = V_{IH} \text{ or } \overline{OE} = V_{IH} \text{ or } \overline{WE}$ = $V_{IL}$                                                |

| VoH               | Output high voltage         | 2.4                    | -        | -       | V    | $I_{OH} = -2.0 \text{ mA}$                                                                                                                      |

| $V_{OHB}$         | V <sub>OH</sub> , BC Supply | V <sub>BC</sub> - 0.3  | -        | -       | V    | $V_{BC} > V_{CC}$ , $I_{OH} = -10\mu A$                                                                                                         |

| V <sub>OL</sub>   | Output low voltage          | -                      | -        | 0.4     | V    | $I_{OL} = 4.0 \text{ mA}$                                                                                                                       |

| $I_{CC}$          | Operating supply current    | -                      | 12       | 25      | mA   | $\frac{Min.\ cycle,\ duty=100\%,}{CS=V_{IL},\ I_{I/O}=0mA}$                                                                                     |

| I <sub>SB1</sub>  | Standby supply current      | -                      | 3        | -       | mA   | $\overline{\text{CS}} = V_{\text{IH}}$                                                                                                          |

| I <sub>SB2</sub>  | Standby supply current      | -                      | 1.5      | -       | mA   | $\label{eq:cs} \begin{split} \overline{CS} &\geq V_{CC} - 0.2V, \\ 0V &\leq V_{IN} \leq \ 0.2V, \\ or \ V_{IN} &\geq V_{CC} - 0.2V \end{split}$ |

| $V_{SO}$          | Supply switch-over voltage  | -                      | $V_{BC}$ | -       | V    |                                                                                                                                                 |

| $I_{CCB}$         | Battery operation current   | -                      | 0.3      | 0.5     | μΑ   | $V_{BC}$ = 3V, $T_{\underline{A}}$ = 25°C, no load on $V_{OUT}$ or $\overline{CE}_{OUT}$                                                        |

| <b>3</b> 7        | Power-fail-detect voltage   | 4.55                   | 4.62     | 4.75    | V    | bq4845                                                                                                                                          |

| V <sub>PFD</sub>  | Power-fail-detect voltage   | 4.30                   | 4.37     | 4.5     | V    | bq4845Y                                                                                                                                         |

| V <sub>OUT1</sub> | V <sub>OUT</sub> voltage    | V <sub>CC</sub> - 0.3V | -        | -       | V    | $I_{OUT} = 100 \text{mA}, V_{CC} > V_{BC}$                                                                                                      |

| V <sub>OUT2</sub> | V <sub>OUT</sub> voltage    | $V_{BC}$ - $0.3V$      | -        | -       | V    | $I_{OUT} = 100 \mu A$ , $V_{CC} < V_{BC}$                                                                                                       |

| V <sub>RST</sub>  | RST output voltage          | -                      | -        | 0.4V    | -    | $I_{RST} = 4mA$                                                                                                                                 |

| V <sub>INT</sub>  | INT output voltage          | -                      | -        | 0.4V    | -    | $I_{INT} = 4mA$                                                                                                                                 |

| * 7               | WDCttlt                     | -                      | -        | 0.4V    | 1    | I <sub>SINK</sub> = 4mA                                                                                                                         |

| V <sub>WDO</sub>  | WDO output voltage          | 2.4                    | -        | -       | -    | I <sub>SOURCE</sub> = 2mA                                                                                                                       |

| I <sub>WDIL</sub> | Watchdog input low current  | -50                    | -10      | -       | μA   | $0 < V_{WDI} < 0.8V$                                                                                                                            |

| I <sub>WDIH</sub> | Watchdog input high current | -                      | 20       | 50      | μA   | $2.2 < V_{WDI} < V_{CC}$                                                                                                                        |

$\label{eq:Notes:Typical values} \begin{array}{ll} \textbf{Notes:} & \underline{Typical\ values\ indicate\ operation\ at\ T_A=25^{\circ}C,\ V_{CC}=5V.} \\ \hline RST\ and\ \overline{INT}\ are\ open-drain\ outputs. \end{array}$

## Crystal Specifications (DT-26 or Equivalent)

| Symbol                         | Parameter                    | Minimum | Typical | Maximum | Unit   |

|--------------------------------|------------------------------|---------|---------|---------|--------|

| fo                             | Oscillation frequency        | -       | 32.768  | -       | kHz    |

| $C_{L}$                        | Load capacitance             | -       | 6       | -       | pF     |

| TP                             | Temperature turnover point   | 20      | 25      | 30      | °C     |

| k                              | Parabolic curvature constant | -       | -       | -0.042  | ppm/°C |

| Q                              | Quality factor               | 40,000  | 70,000  | -       |        |

| R <sub>1</sub>                 | Series resistance            | -       | -       | 45      | ΚΩ     |

| C <sub>0</sub>                 | Shunt capacitance            | -       | 1.1     | 1.8     | pF     |

| C <sub>0</sub> /C <sub>1</sub> | Capacitance ratio            | -       | 430     | 600     |        |

| $D_{L}$                        | Drive level                  | -       | -       | 1       | μW     |

| $\Delta f/f_{O}$               | Aging (first year at 25°C)   | -       | 1       | -       | ppm    |

## Capacitance (TA = 25°C, F = 1MHz, VCC = 5.0V)

| Symbol           | Parameter                | Minimum | Typical | Maximum | Unit | Conditions          |

|------------------|--------------------------|---------|---------|---------|------|---------------------|

| C <sub>I/O</sub> | Input/output capacitance | -       | -       | 7       | pF   | Output voltage = 0V |

| C <sub>IN</sub>  | Input capacitance        | -       | -       | 5       | pF   | Input voltage = 0V  |

Note: These parameters are sampled and not 100% tested.

## **AC Test Conditions**

| Parameter                                | Test Conditions                    |  |  |  |  |  |

|------------------------------------------|------------------------------------|--|--|--|--|--|

| Input pulse levels                       | 0V to 3.0V                         |  |  |  |  |  |

| Input rise and fall times                | 5 ns                               |  |  |  |  |  |

| Input and output timing reference levels | 1.5 V (unless otherwise specified) |  |  |  |  |  |

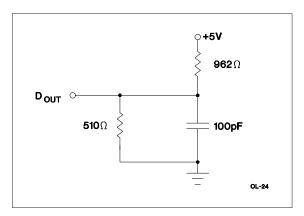

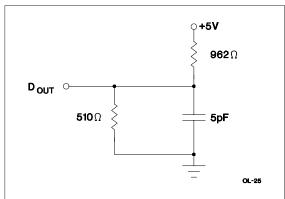

| Output load (including scope and jig)    | See Figures 4 and 5                |  |  |  |  |  |

Figure 4. Output Load A

Figure 5. Output Load B

## Read Cycle (TA = TOPR, VCCmin $\leq$ VCC $\leq$ VCCmax)

| Symbol           | Parameter                          | Min. | Max. | Unit | Conditions    |

|------------------|------------------------------------|------|------|------|---------------|

| $t_{RC}$         | Read cycle time                    | 70   | -    | ns   |               |

| t <sub>AA</sub>  | Address access time                | -    | 70   | ns   | Output load A |

| t <sub>ACS</sub> | Chip select access time            | -    | 70   | ns   | Output load A |

| toE              | Output enable to output valid      | -    | 35   | ns   | Output load A |

| t <sub>CLZ</sub> | Chip select to output in low Z     | 5    | -    | ns   | Output load B |

| tolz             | Output enable to output in low Z   | 0    | -    | ns   | Output load B |

| t <sub>CHZ</sub> | Chip deselect to output in high Z  | 0    | 25   | ns   | Output load B |

| t <sub>OHZ</sub> | Output disable to output in high Z | 0    | 25   | ns   | Output load B |

| toH              | Output hold from address change    | 10   | -    | ns   | Output load A |

## Write Cycle $(T_A = T_{OPR}, V_{CCmin} \le V_{CC} \le V_{CCmax})$

| Symbol           | Parameter                           | Min. | Max. | Unit | Conditions                                                                                            |

|------------------|-------------------------------------|------|------|------|-------------------------------------------------------------------------------------------------------|

| twc              | Write cycle time                    | 70   | -    | ns   |                                                                                                       |

| t <sub>CW</sub>  | Chip select to end of write         | 65   | -    | ns   | (1)                                                                                                   |

| t <sub>AW</sub>  | Address valid to end of write       | 65   | -    | ns   | (1)                                                                                                   |

| t <sub>AS</sub>  | Address setup time                  | 0    | -    | ns   | Measured from address valid to beginning of write. (2)                                                |

| twp              | Write pulse width                   | 55   | -    | ns   | Measured from beginning of write to end of write. (1)                                                 |

| t <sub>WR1</sub> | Write recovery time (write cycle 1) | 5    | -    | ns   | Measured from WE going high to end of write cycle. (3)                                                |

| t <sub>WR2</sub> | Write recovery time (write cycle 2) | 15   | -    | ns   | Measured from $\overline{CS}$ going high to end of write cycle. (3)                                   |

| $t_{\rm DW}$     | Data valid to end of write          | 30   | -    | ns   | Measured to first low-to-high transition of either $\overline{\text{CS}}$ or $\overline{\text{WE}}$ . |

| t <sub>DH1</sub> | Data hold time (write cycle 1)      | 0    | -    | ns   | Measured from WE going high to end of write cycle. (4)                                                |

| t <sub>DH2</sub> | Data hold time (write cycle 2)      | 10   | -    | ns   | Measured from $\overline{\text{CS}}$ going high to end of write cycle. (4)                            |

| twz              | Write enabled to output in high Z   | 0    | 25   | ns   | I/O pins are in output state. (5)                                                                     |

| tow              | Output active from end of write     | 0    | -    | ns   | I/O pins are in output state. (5)                                                                     |

## Notes:

- 1. A write ends at the earlier transition of  $\overline{\text{CS}}$  going high and  $\overline{\text{WE}}$  going high.

- 2. A write occurs during the overlap of a low  $\overline{CS}$  and a low  $\overline{WE}$ . A write begins at the later transition of  $\overline{CS}$  going low and  $\overline{WE}$  going low.

- 3. Either  $t_{WR1}$  or  $t_{WR2}$  must be met.

- 4. Either  $t_{DH1}$  or  $t_{DH2}$  must be met.

- 5. If  $\overline{CS}$  goes low simultaneously with  $\overline{WE}$  going low or after  $\overline{WE}$  going low, the outputs remain in high-impedance state.

# Read Cycle No. 1 (Address Access) 1,2

# Read Cycle No. 2 (CS Access) 1,3,4

# Read Cycle No. 3 (OE Access) 1,5

**Notes:**

- 1.  $\overline{\text{WE}}$  is held high for a read cycle.

- 2. Device is continuously selected:  $\overline{CS}$  =  $\overline{OE}$  =  $V_{IL}$ .

- 3. Address is valid prior to or coincident with  $\overline{\text{CS}}$  transition low.

- $4. \quad \overline{OE} = V_{IL}.$

- 5. Device is continuously selected:  $\overline{\text{CS}}$  =  $V_{IL}$ .

Aug. 1995

RC-1

RC-36

# Write Cycle No. 1 (WE-Controlled) 1,2,3

# Write Cycle No. 2 (CS-Controlled) 1,2,3,4,5

Notes:

- 1.  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  must be high during address transition.

- 2. Because I/O may be active ( $\overline{OE}$  low) during this period, data input signals of opposite polarity to the outputs must not be applied.

- 3. If  $\overline{\text{OE}}$  is high, the I/O pins remain in a state of high impedance.

- 4. Either twR1 or twR2 must be met.

- 5. Either  $t_{DH1}$  or  $t_{DH2}$  must be met.

## Power-Down/Power-Up Timing (TA = TOPR)

| Symbol           | Parameter                                                          | Minimum          | Typical | Maximum          | Unit | Conditions                                                                                                    |

|------------------|--------------------------------------------------------------------|------------------|---------|------------------|------|---------------------------------------------------------------------------------------------------------------|

| t <sub>F</sub>   | V <sub>CC</sub> slew from 4.75 to 4.25V                            | 300              | -       | -                | μs   |                                                                                                               |

| $t_{FS}$         | $V_{CC}$ slew from 4.25 to $V_{SO}$                                | 10               | -       | -                | μs   |                                                                                                               |

| t <sub>R</sub>   | V <sub>CC</sub> slew from V <sub>SO</sub> to V <sub>PFD(MAX)</sub> | 100              | -       | -                | μs   |                                                                                                               |

| t <sub>PF</sub>  | Interrupt delay from $V_{PFD}$                                     | 6                | -       | 24               | μs   |                                                                                                               |

| twpT             | Write-protect time for external RAM                                | 90               | 100     | 125              | μs   | Delay after $V_{CC}$ slews down past $V_{PFD}$ before SRAM is write-protected and $\overline{RST}$ activated. |

| t <sub>CSR</sub> | $\overline{\text{CS}}$ at $V_{\text{IH}}$ after power-up           | 100              | 200     | 300              | ms   | Internal write-protection period after $V_{CC}$ passes $V_{PFD}$ on power-up.                                 |

| t <sub>RST</sub> | $V_{PFD}$ to $\overline{RST}$ inactive                             | t <sub>CSR</sub> | -       | t <sub>CSR</sub> | ms   | Reset active time-out period                                                                                  |

| tcer             | Chip enable recovery time                                          | tcsr             | -       | t <sub>CSR</sub> | ms   | Time during which external SRAM is write-protected after $V_{CC}$ passes $V_{PFD}$ on power-up.               |

| $t_{CED}$        | Chip enable propagation delay to external SRAM                     | -                | 9       | 12               | ns   | Output load A                                                                                                 |

Caution: Negative undershoots below the absolute maximum rating of -0.3V in battery-backup mode may affect data integrity.

## Power-Down/Power-Up Timing

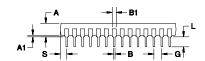

# 28-Pin DIP (P)

## 28-Pin DIP (P)

| Dimension | Minimum | Maximum |

|-----------|---------|---------|

| A         | 0.160   | 0.190   |

| A1        | 0.015   | 0.040   |

| В         | 0.015   | 0.022   |

| B1        | 0.045   | 0.065   |

| C         | 0.008   | 0.013   |

| D         | 1.440   | 1.480   |

| E         | 0.600   | 0.625   |

| E1        | 0.530   | 0.570   |

| e         | 0.600   | 0.670   |

| G         | 0.090   | 0.110   |

| L         | 0.115   | 0.150   |

| S         | 0.070   | 0.090   |

All dimensions are in inches.

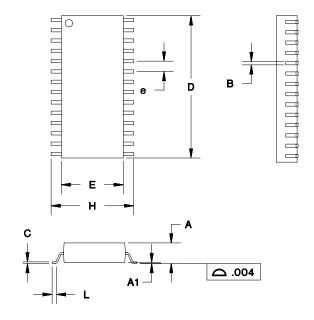

# 28-Pin SOIC (S)

## 28-Pin SOIC (S)

| Dimension | Minimum | Maximum |

|-----------|---------|---------|

| A         | 0.095   | 0.105   |

| A1        | 0.004   | 0.012   |

| В         | 0.013   | 0.020   |

| C         | 0.008   | 0.013   |

| D         | 0.700   | 0.715   |

| E         | 0.290   | 0.305   |

| e         | 0.045   | 0.055   |

| Н         | 0.395   | 0.415   |

| L         | 0.020   | 0.040   |

All dimensions are in inches.

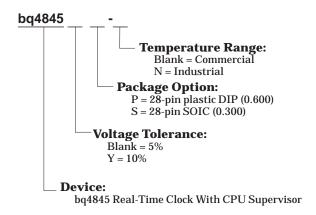

## **Ordering Information**

24-Jan-2013

## **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|--------------------|------|-------------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

| BQ4845P-A4       | ACTIVE | PDIP         | N                  | 28   | 13          | Pb-Free<br>(RoHS)          | A42 SN           | N / A for Pkg Type | 0 to 70      | 4845P<br>-A4      | Samples |

| BQ4845S-A4       | ACTIVE | SOIC         | DW                 | 28   | 20          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | 0 to 70      | 4845S<br>-A4      | Samples |

| BQ4845S-A4G4     | ACTIVE | SOIC         | DW                 | 28   | 20          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | 0 to 70      | 4845S<br>-A4      | Samples |

| BQ4845S-A4N      | ACTIVE | SOIC         | DW                 | 28   | 20          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 4845S-N<br>-A4    | Samples |

| BQ4845S-A4NG4    | ACTIVE | SOIC         | DW                 | 28   | 20          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 4845S-N<br>-A4    | Samples |

| BQ4845S-A4NTR    | ACTIVE | SOIC         | DW                 | 28   | 1000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM |              | 4845S-N<br>-A4    | Samples |

| BQ4845S-A4NTRG4  | ACTIVE | SOIC         | DW                 | 28   | 1000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM |              | 4845S-N<br>-A4    | Samples |

| BQ4845S-A4TR     | ACTIVE | SOIC         | DW                 | 28   | 1000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | 0 to 70      | 4845S<br>-A4      | Samples |

| BQ4845S-A4TRG4   | ACTIVE | SOIC         | DW                 | 28   |             | TBD                        | Call TI          | Call TI            | 0 to 70      |                   | Samples |

| BQ4845YS-A4      | ACTIVE | SOIC         | DW                 | 28   | 20          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | 0 to 70      | 4845YS<br>-A4     | Samples |

| BQ4845YS-A4G4    | ACTIVE | SOIC         | DW                 | 28   | 20          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | 0 to 70      | 4845YS<br>-A4     | Samples |

| BQ4845YS-A4N     | ACTIVE | SOIC         | DW                 | 28   | 20          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 4845YS-N<br>-A4   | Samples |

| BQ4845YS-A4NG4   | ACTIVE | SOIC         | DW                 | 28   |             | TBD                        | Call TI          | Call TI            | -40 to 85    |                   | Samples |

| BQ4845YS-A4NTR   | ACTIVE | SOIC         | DW                 | 28   | 1000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM |              | 4845YS-N<br>-A4   | Samples |

| BQ4845YS-A4NTRG4 | ACTIVE | SOIC         | DW                 | 28   | 1000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM |              | 4845YS-N<br>-A4   | Samples |

| BQ4845YS-A4TR    | ACTIVE | SOIC         | DW                 | 28   | 1000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | 0 to 70      | 4845YS<br>-A4     | Samples |

| BQ4845YS-A4TRG4  | ACTIVE | SOIC         | DW                 | 28   |             | TBD                        | Call TI          | Call TI            | 0 to 70      |                   | Samples |

## PACKAGE OPTION ADDENDUM

24-Jan-2013

(1) The marketing status values are defined as follows:

www.ti.com

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) Only one of markings shown within the brackets will appear on the physical device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

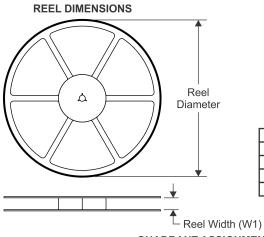

## PACKAGE MATERIALS INFORMATION

www.ti.com 26-Jan-2013

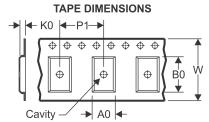

## TAPE AND REEL INFORMATION

| Α0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

|    | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

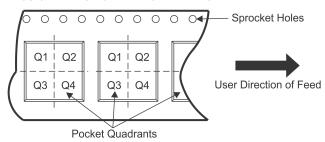

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| All differsions are northinal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-------------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| BQ4845S-A4NTR                 | SOIC            | DW                 | 28 | 1000 | 330.0                    | 32.4                     | 11.35      | 18.67      | 3.1        | 16.0       | 32.0      | Q1               |

| BQ4845S-A4TR                  | SOIC            | DW                 | 28 | 1000 | 330.0                    | 32.4                     | 11.35      | 18.67      | 3.1        | 16.0       | 32.0      | Q1               |

| BQ4845YS-A4NTR                | SOIC            | DW                 | 28 | 1000 | 330.0                    | 32.4                     | 11.35      | 18.67      | 3.1        | 16.0       | 32.0      | Q1               |

| BQ4845YS-A4TR                 | SOIC            | DW                 | 28 | 1000 | 330.0                    | 32.4                     | 11.35      | 18.67      | 3.1        | 16.0       | 32.0      | Q1               |

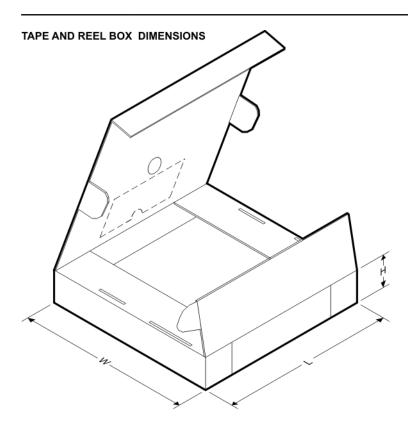

www.ti.com 26-Jan-2013

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| BQ4845S-A4NTR  | SOIC         | DW              | 28   | 1000 | 367.0       | 367.0      | 55.0        |

| BQ4845S-A4TR   | SOIC         | DW              | 28   | 1000 | 367.0       | 367.0      | 55.0        |

| BQ4845YS-A4NTR | SOIC         | DW              | 28   | 1000 | 367.0       | 367.0      | 55.0        |

| BQ4845YS-A4TR  | SOIC         | DW              | 28   | 1000 | 367.0       | 367.0      | 55.0        |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>

# AMEYA360 Components Supply Platform

## **Authorized Distribution Brand:**

## Website:

Welcome to visit www.ameya360.com

## Contact Us:

## > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

## > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

## Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com