**THS788**

## SLOS616D - MARCH 2010 - REVISED MARCH 2015

# THS788 Quad-Channel Time Measurement Unit (TMU)

### **Features**

- Four Event Channels + Sync Channel

- Single-Shot Accuracy: 8 ps, One Sigma

- Precision: 13 ps

- Result Interface Range: 0 s to 7 s

- Event Input Rate: 200 MHz

- Programmable Serial-Result Interface Speed: 75 MHz to 300 MHz

- High-Speed Serial Host-Processor Bus Interface: 50 MHz

- High-Speed LVDS-Compatible Serial-Result Bus per Channel

- Programmable Serial-Result Bus Length

- Temperature Sensor

- Single 3.3-V Supply

- Power: 675 mW per Channel, 18 Bits, 300 MHz, Four Channels

# **Applications**

- Automatic Test Equipment

- Benchtop Time-Measurement Equipment

- Radar and Sonar

- Medical Imaging

- Mass Spectroscopy

- **Nuclear and Particle Physics**

- Laser Distance Measurement

- Ultrasonic Flow Measurement

# 3 Description

The THS788 device is a four-channel timing measurement unit (TMU) that incorporates a time-todigital converter (TDC) architecture for fast and accurate measurements. The TMU can provide 8 ps of single-shot accuracy. The TDC has a 13-ps resolution (LSB), which is derived from an external master clock of 200 MHz. The TDC uses fast LVDScompatible interfaces for all of its event inputs and serial result outputs, which allows for fast and reliable data transfer. Each channel can process timestamps at a maximum speed of 200 MSPS.

The THS788 device has a wide range of programmability that makes it flexible in different applications. The serial-result interface programmable data length, frequency, and data-rate mode (DDR and normal). The event channels can be programmed to take timestamps on rising edges or falling edges. The TMU has a mode for event management, in which the user can program wait times before measurements. This programming is achieved through a 50-MHz LVCMOS interface.

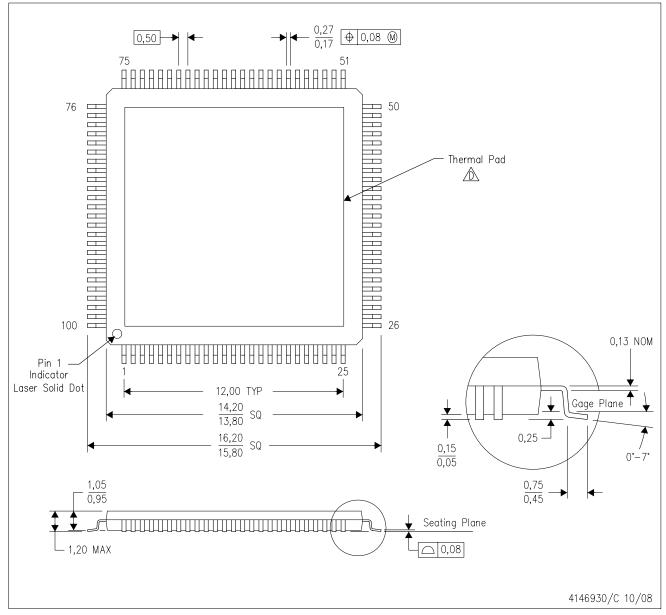

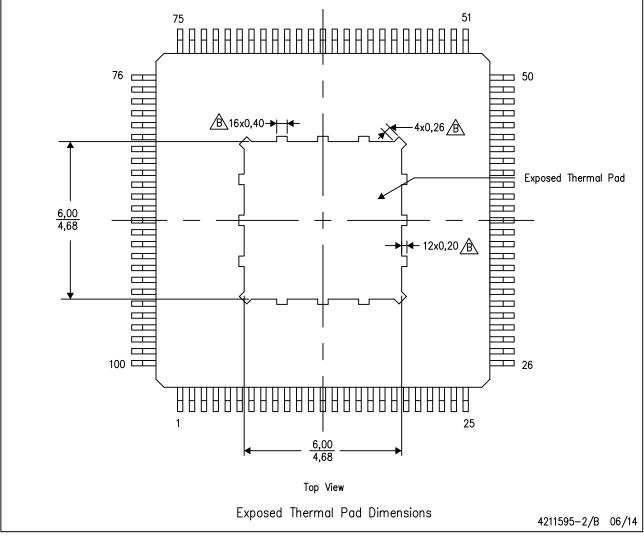

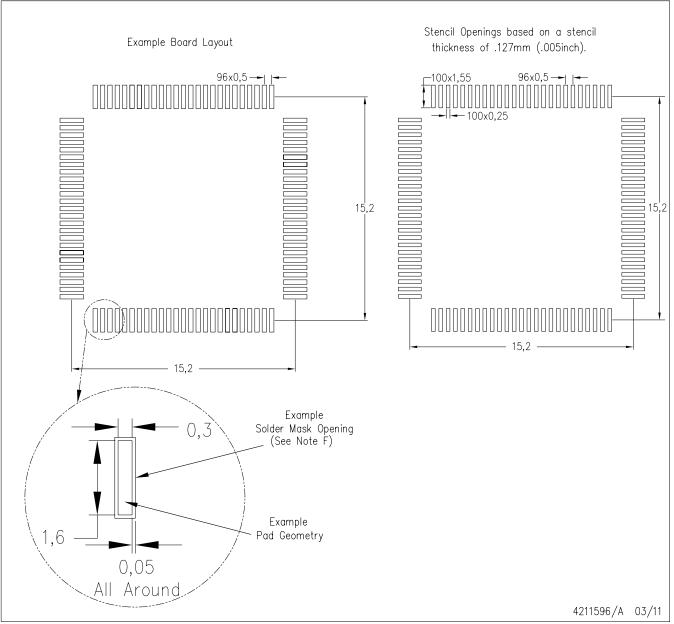

The THS788 device is available in an HTQFP-100 package with a heat slug on top for easy heat-sink access. The device is built using TI's RF SiGe process technology, which allows for maximum timing accuracy with low power.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)     |

|-------------|-------------|---------------------|

| THS788      | HTQFP (100) | 14.00 mm × 14.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

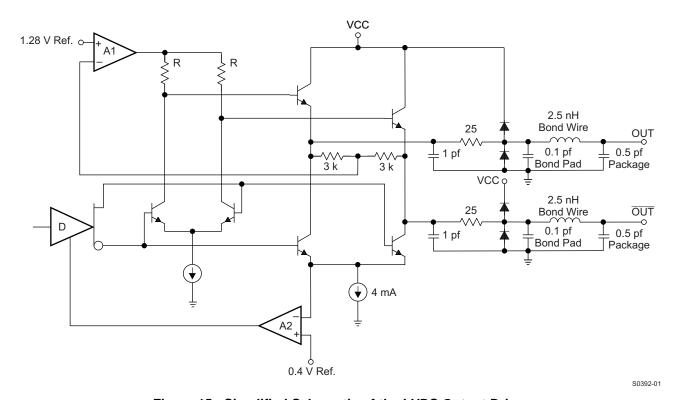

# Simplified Schematic

# **Table of Contents**

| 1 | Features 1                                   |    | 8.2 Functional Block Diagram         | g  |

|---|----------------------------------------------|----|--------------------------------------|----|

| 2 | Applications 1                               |    | 8.3 Feature Description              | 10 |

| 3 | Description 1                                |    | 8.4 Device Functional Modes          | 11 |

| 4 | Simplified Schematic                         |    | 8.5 Programming                      | 17 |

| 5 | Revision History2                            |    | 8.6 Register Maps                    | 22 |

| 6 | Pin Configuration and Functions              | 9  | Application and Implementation       | 29 |

| - | 5                                            |    | 9.1 Application Information          | 29 |

| 7 | Specifications 5                             |    | 9.2 Typical Application              | 30 |

|   | 7.1 Absolute Maximum Ratings 5               | 10 | Power Supply Recommendations         |    |

|   | 7.2 ESD Ratings                              | 11 | Layout                               |    |

|   | 7.3 Recommended Operating Conditions         |    | 11.1 Layout Guidelines               |    |

|   | 7.4 Thermal Information                      |    | 11.2 Layout Example                  |    |

|   | 7.5 Electrical Characteristics               |    | 11.3 Thermal Considerations          |    |

|   | 7.6 Host Serial Interface DC Characteristics | 12 | Device and Documentation Support     |    |

|   | 7.7 Host Serial Interface AC Characteristics |    | 12.1 Trademarks                      |    |

|   | 7.8 Power Consumption                        |    | 12.2 Electrostatic Discharge Caution |    |

| _ | 7.9 Typical Characteristics 8                |    | 12.3 Glossary                        |    |

| 8 | Detailed Description9                        | 13 | Mechanical, Packaging, and Orderable |    |

|   | 8.1 Overview                                 | 13 | Information                          | 40 |

|   |                                              |    |                                      |    |

# **5 Revision History**

| Jpdated Features to remove "800 ps" from single-shot accuracy | ted single-event accuracy, |  |

|---------------------------------------------------------------|----------------------------|--|

|---------------------------------------------------------------|----------------------------|--|

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section

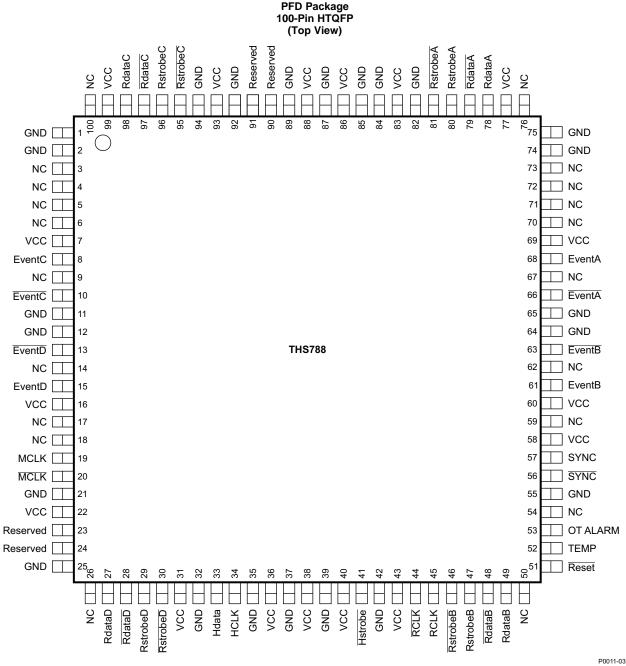

# 6 Pin Configuration and Functions

NOTE: Pin 1 indicator is symbolized with a white dot, and is located near pin 1 corner.

P0011-0

## **Pin Functions**

|          | PIN                                                                                      | Pin Functions            |                                           |

|----------|------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------|

| NAME     | NO.                                                                                      | TYPE                     | DESCRIPTION                               |

| EventA   | 68                                                                                       | LVDS-compatible input    | Positive event input for channel A        |

| EventA   | 66                                                                                       | LVDS-compatible input    | Negative event input for channel A        |

| EventB   | 61                                                                                       | LVDS-compatible input    | Positive event input for channel B        |

| EventB   | 63                                                                                       | LVDS-compatible input    | Negative event input for channel B        |

| EventC   | 8                                                                                        | LVDS-compatible input    | Positive event input for channel C        |

| EventC   | 10                                                                                       | LVDS-compatible input    | Negative event input for channel C        |

| EventD   | 15                                                                                       | LVDS-compatible input    | Positive event input for channel D        |

| EventD   | 13                                                                                       | LVDS-compatible input    | Negative event input for channel D        |

| GND      | 1, 2, 11, 12, 21, 25, 32, 35, 37, 39, 42, 55, 64, 65, 74, 75, 82, 84, 85, 87, 89, 92, 94 | Ground                   | Chip ground                               |

| HCLK     | 34                                                                                       | LVCMOS input             | Host serial-interface clock               |

| Hdata    | 33                                                                                       | LVCMOS I/O               | Host serial-interface data I/O            |

| Hstrobe  | 41                                                                                       | LVCMOS input             | Host serial-interface chip select         |

| MCLK     | 19                                                                                       | LVDS-compatible input    | Positive master-clock input               |

| MCLK     | 20                                                                                       | LVDS-compatible input    | Negative master-clock input               |

| NC       | 3–6, 9, 14, 17, 18, 26, 50, 54, 59, 62, 67, 70–73, 76, 100                               | No connect               | Physically not connected to silicon       |

| OT_ALARM | 53                                                                                       | Open-drain output        | Overtemperature alarm                     |

| RCLK     | 45                                                                                       | LVDS-compatible output   | Positive result-interface clock           |

| RCLK     | 44                                                                                       | LVDS-compatible output   | Negative result-interface clock           |

| RdataA   | 78                                                                                       | LVDS-compatible output   | Positive result-data output for channel A |

| RdataA   | 79                                                                                       | LVDS-compatible output   | Negative result-data output for channel A |

| RdataB   | 49                                                                                       | LVDS-compatible output   | Positive result-data output for channel B |

| RdataB   | 48                                                                                       | LVDS-compatible output   | Negative result-data output for channel B |

| RdataC   | 98                                                                                       | LVDS-compatible output   | Positive result-data output for channel C |

| RdataC   | 97                                                                                       | LVDS-compatible output   | Negative result-data output for channel C |

| RdataD   | 27                                                                                       | LVDS-compatible output   | Positive result-data output for channel D |

| RdataD   | 28                                                                                       | LVDS-compatible output   | Negative result-data output for channel D |

| Reserved | 23, 24, 90, 91                                                                           | Engineering or test pins | Connect to VCC                            |

| Reset    | 51                                                                                       | LVCMOS input             | Chip reset, active-low                    |

| RstrobeA | 80                                                                                       | LVDS-compatible output   | Positive strobe signal for channel A      |

| RstrobeA | 81                                                                                       | LVDS-compatible output   | Negative strobe signal for channel A      |

| RstrobeB | 47                                                                                       | LVDS-compatible output   | Positive strobe signal for channel B      |

| RstrobeB | 46                                                                                       | LVDS-compatible output   | Negative strobe signal for channel B      |

| RstrobeC | 96                                                                                       | LVDS-compatible output   | Positive strobe signal for channel C      |

| RstrobeC | 95                                                                                       | LVDS-compatible output   | Negative strobe signal for channel C      |

| RstrobeD | 29                                                                                       | LVDS-compatible output   | Positive strobe signal for channel D      |

| RstrobeD | 30                                                                                       | LVDS-compatible output   | Negative strobe signal for channel D      |

| SYNC     | 57                                                                                       | LVDS-compatible input    | Positive input for sync channel           |

| SYNC     | 56                                                                                       | LVDS-compatible input    | Negative input for sync channel           |

| TEMP     | 52                                                                                       | Analog output            | Die temperature                           |

| VCC      | 7, 16, 22, 31, 36, 38, 40, 43, 58, 60, 69, 77, 83, 86, 88, 93, 99                        | Power supply             | Positive supply, nominal 3.3 V            |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating junction temperature range (unless otherwise noted)

|                  |                                             | MIN  | MAX            | UNIT |

|------------------|---------------------------------------------|------|----------------|------|

| $V_{CC}$         |                                             |      | 4              | V    |

|                  | Analog I/O to GND <sup>(1)</sup>            | -0.3 | $V_{CC} + 0.3$ | V    |

|                  | Digital I/O to GND                          | -0.3 | $V_{CC} + 0.3$ | V    |

| TJ               | Maximum junction temperature <sup>(2)</sup> |      | 150            | °C   |

| T <sub>stg</sub> | Storage temperature                         |      | 150            | °C   |

<sup>(1)</sup> LVDS outputs are not short-circuit-proof to GND.

# 7.2 ESD Ratings

|                    |                         |                                                                               | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating junction temperature range (unless otherwise noted)

|          |                      | MIN   | NOM | MAX   | UNIT |

|----------|----------------------|-------|-----|-------|------|

| $V_{CC}$ | Supply voltage       | 3.135 |     | 3.465 | V    |

| TJ       | Junction temperature | 0     |     | 105   | °C   |

|          | MCLOCK frequency     |       | 200 |       | MHz  |

## 7.4 Thermal Information

|                       |                                              | THS788                        |      |

|-----------------------|----------------------------------------------|-------------------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PFD (HTQFP)                   | UNIT |

|                       |                                              | 100 PINS                      | _    |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 27.2 (60.2 without heat sink) |      |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 0.6                           |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 6.8                           | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.6                           |      |

| ΨЈВ                   | Junction-to-board characterization parameter | 6.8                           |      |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A                           |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> The THS788 device has an automatic power shutdown at 140°C, typical.

<sup>2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.5 Electrical Characteristics

Typical conditions are at  $T_J = 55$ °C and  $V_{CC} = 3.3$  V.

| PARAMETER                                     | TEST CONDITIONS                  | MIN   | TYP   | MAX   | UNIT   |

|-----------------------------------------------|----------------------------------|-------|-------|-------|--------|

| TDC CHARACTERISTICS                           |                                  |       |       |       |        |

| Time-measurement precision (LSB)              |                                  |       | 13.02 |       | ps     |

| Measurement accuracy after calibration, mean  |                                  | -8    |       | 8     | ps     |

| Single-event accuracy, one sigma              |                                  |       | 8     |       | ps     |

| Time-measurement temperature coefficient      |                                  |       | 0.1   |       | ps/°C  |

| Time-measurement voltage coefficient          |                                  |       | ±30   |       | ps/V   |

| Event input rate                              |                                  |       |       | 200   | MHz    |

| Minimum event pulse duration                  | With preconditioning             | 2.5   |       |       | ns     |

|                                               | Without preconditioning          | 250   |       |       | ps     |

| Minimum event pulse duration                  |                                  | 250   |       |       | ps     |

| Turnon time (ready to take timestamp)         |                                  |       |       | 250   | μs     |

| MASTER CLOCK CHARACTERISTICS                  | +                                |       |       | l     | •      |

| Frequency                                     |                                  |       | 200   |       | MHz    |

| Duty cycle                                    |                                  | 0.4   |       | 0.6   |        |

| Jitter                                        |                                  |       |       | 3     | ps rms |

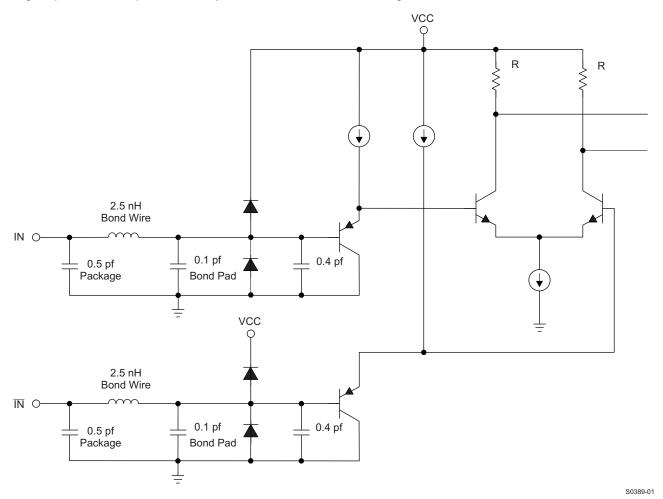

| HIGH-SPEED LVDS INPUTS: MCLK, EVENT, SYNC     |                                  |       |       |       | po imo |

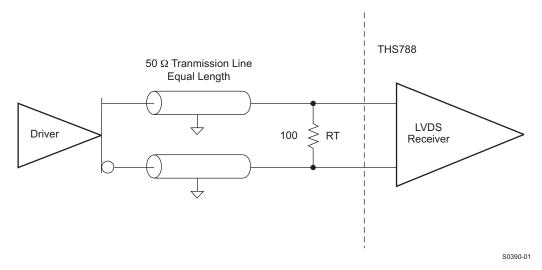

| Differential input voltage                    | 100-Ω termination, line-to-line  | 200   | 350   | 500   | mV     |

| Common-mode voltage                           | 100-12 termination, line-to-line | 200   | 1.25  | 300   | V      |

|                                               |                                  | 0.6   | 1.25  | 1.7   | V      |

| Peak voltage, either input                    |                                  | 0.0   | 1     | 1.7   | -      |

| Input capacitance                             |                                  |       | ı     |       | pF     |

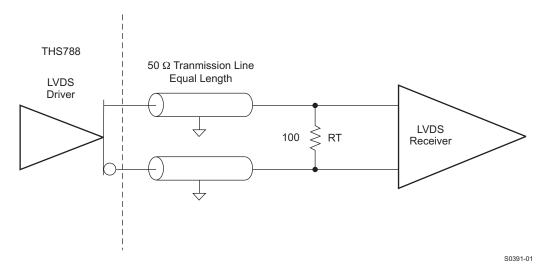

| HIGH-SPEED LVDS OUTPUTS: Rdata, Rstrobe, RCLK |                                  | 050   | 005   | 400   | >/     |

| Differential output voltage                   | 100-Ω termination, line-to-line  | 250   | 325   | 400   | mV     |

| Common-mode voltage                           | 200/1000/                        | 1.125 | 1.28  | 1.375 | V      |

| Rise time/fall time                           | 20%/80%                          |       | 250   |       | ps     |

| Output resistance                             |                                  |       | 40    |       | Ω      |

| TEMPERATURE SENSOR DC CHARACTERISTICS         |                                  |       |       | 1     |        |

| Output voltage                                | T <sub>J</sub> = 65°C            |       | 1.69  |       | V      |

| Output voltage temperature slope              |                                  |       | 5     |       | mV/°C  |

| Max capacitive load                           |                                  | 30    |       |       | pF     |

| Max resistive load                            |                                  |       |       | 10    | kΩ     |

| OVERTEMPERATURE ALARM DC CHARACTERISTIC       | S                                |       |       |       |        |

| Trip point                                    | Active-low pulldown              |       | 141   |       | °C     |

| Leakage current                               | Temperature < trip point         |       | 1     |       | μΑ     |

| Output voltage, low                           | I <sub>sink</sub> = 1 ma         |       |       | 0.2   | V      |

| OUTPUT INTERFACE TIMING                       |                                  |       |       |       |        |

| RCLK duty cycle                               |                                  | 45%   | 50%   | 55%   |        |

|                                               | 300 MHz                          | 1.4   |       |       |        |

| Rdata/Rstrobe to RCLK setup time              | 150 MHz                          | 3.1   |       |       | ns     |

|                                               | 75 MHz                           | 6.4   |       |       |        |

|                                               | 300 MHz                          | 1.5   |       |       |        |

| Rdata/Rstrobe to RCLK hold time               | 150 MHz                          | 3.2   |       |       | ns     |

|                                               | 75 MHz                           | 6.5   |       |       |        |

| OPERATING PARAMETERS                          |                                  |       |       |       |        |

| Coarse counter range                          |                                  | 18    |       | 34    | bit    |

| Coarse counter max time range                 |                                  |       |       | 14.31 | S      |

| Result-interface clock                        |                                  | 75    |       | 300   | MHz    |

Submit Documentation Feedback

Copyright © 2010–2015, Texas Instruments Incorporated

# **Electrical Characteristics (continued)**

Typical conditions are at  $T_J = 55$ °C and  $V_{CC} = 3.3$  V.

| PARAMETER                        | TEST CONDITIONS | MIN    | TYP MAX | UNIT |

|----------------------------------|-----------------|--------|---------|------|

| Result-interface transfer format |                 | 16     | 40      | bit  |

| Result-interface time range      |                 | -7.158 | 7.158   | S    |

### 7.6 Host Serial Interface DC Characteristics

over operating junction temperature range (unless otherwise noted)

|                  | PARAMETER                 | TEST CONDITIONS | MIN                   | TYP MAX               | UNIT |

|------------------|---------------------------|-----------------|-----------------------|-----------------------|------|

| $V_{IH}$         | High-level input voltage  |                 | $0.7 \times V_{CC}$   | V <sub>CC</sub> + 0.5 | V    |

| $V_{IL}$         | Low-level input voltage   |                 | GND - 0.3             | $0.3 \times V_{CC}$   | V    |

| $V_{OH}$         | High-level output voltage |                 | V <sub>CC</sub> - 0.5 | V <sub>CC</sub> + 0.3 | V    |

| $V_{OL}$         | Low-level output voltage  |                 | 0                     | 0.4                   | V    |

| I <sub>lkq</sub> | Leakage current           |                 |                       | 1                     | μA   |

## 7.7 Host Serial Interface AC Characteristics

over operating junction temperature range (unless otherwise noted)

| PARAMETER                                                | TEST CONDITIONS        | MIN  | TYP | MAX | UNIT |

|----------------------------------------------------------|------------------------|------|-----|-----|------|

| HCLK frequency                                           |                        |      |     | 50  | MHz  |

| Rise and fall times                                      |                        |      |     | 3.5 | ns   |

| HCLK duty cycle                                          |                        | 40%  | 50% | 60% |      |

| Hstrobe high period between two consecutive transactions |                        | 40   |     |     | ns   |

| Hstrobe low to HCLK high setup                           |                        | 5    |     |     | ns   |

| HCLK high to Hstrobe high hold time                      |                        | 5    |     |     | ns   |

| Hdata in to HCLK high setup                              |                        | 5    |     |     | ns   |

| Hdata in to HCLK high hold time                          |                        | 5    |     |     | ns   |

| HCLK falling edge to Hdata out (L or H)                  | C <sub>L</sub> = 20 pF | 3.25 |     |     | ns   |

| HCLK falling edge to Hdata out (H or L)                  | C <sub>L</sub> = 20 pF | 3.25 |     |     | ns   |

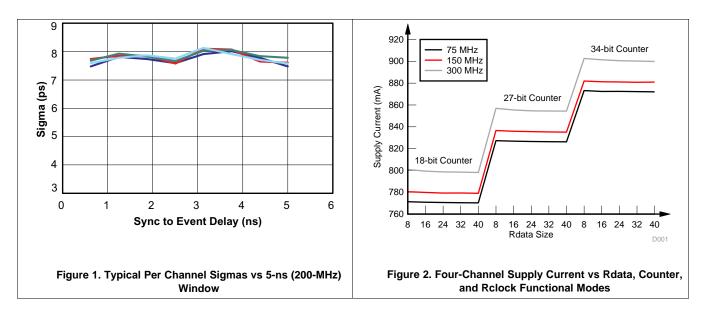

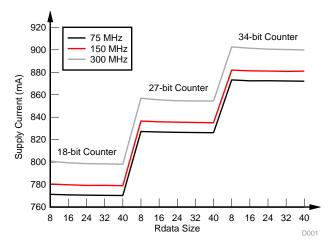

## 7.8 Power Consumption

Typical conditions are at 55°C junction temperature,  $V_{CC} = 3.3 \text{ V}$

|                              |               | CONDITION | CURREN  | IT   |    |  |

|------------------------------|---------------|-----------|---------|------|----|--|

|                              |               | TYP       | MAX     | UNIT |    |  |

| One channel plus sync,       | counter lengt | 420       |         | mA   |    |  |

| As above with an addition    | nal channel   |           | add 125 |      | mA |  |

| Outrout into who are are and | 150 MHz       |           | add 10  |      | A  |  |

| Output interface speed       | 300 MHz       |           | add 25  |      | mA |  |

| O t t                        | 27 bits       |           | add 60  |      | A  |  |

| Counter length               | 34 bits       |           | add 105 |      | mA |  |

|                              | 18 bits       | 75 MHz    | 795     | 1075 |    |  |

|                              |               | 150 MHz   | 805     | 1090 |    |  |

|                              |               | 300 MHz   | 820     | 1101 |    |  |

|                              |               | 75 MHz    | 855     | 1150 |    |  |

| Four-channel current         | 27 bits       | 150 MHz   | 865     | 1165 | mA |  |

|                              |               | 300 MHz   | 880     | 1176 |    |  |

|                              |               | 75 MHz    | 900     | 1210 |    |  |

|                              | 34 bits       | 150 MHz   | 910     | 1225 |    |  |

|                              |               | 300 MHz   | 925     | 1236 |    |  |

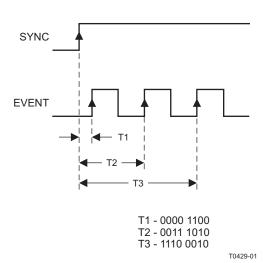

# 7.9 Typical Characteristics

# 8 Detailed Description

### 8.1 Overview

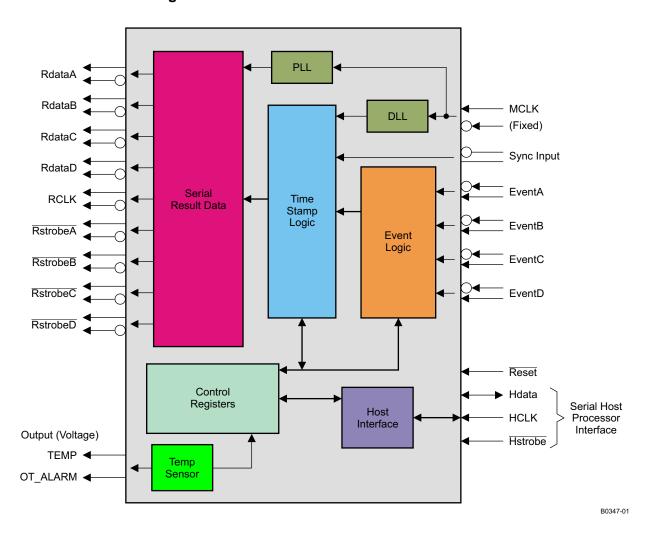

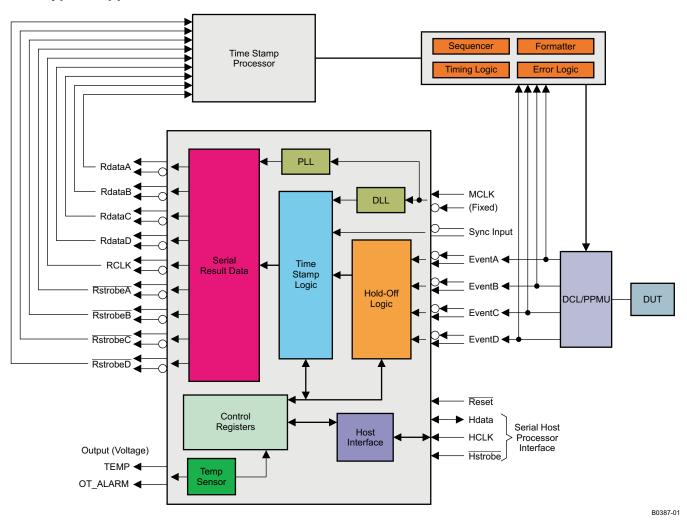

The THS788 TMU includes four measurement channels plus a synchronization channel optimized to make high-accuracy time-interval measurements. The following is a brief description of the various circuit blocks and how they interact to make and process the time measurements.

# 8.2 Functional Block Diagram

Copyright © 2010–2015, Texas Instruments Incorporated

#### 8.3 Feature Description

### 8.3.1 Counter, Latches, Clock Multiplier

The center of the TMU is a master synchronous counter which counts continuously at a rate of 1.2 GHz. This is the master timing generator for the whole TMU and defines the basic timing interval of 833 ps, which is further subdivided with Interpolator circuitry. The output bits of the counter are connected to five sets of latches, which can latch and hold the counter state on command from each of the channels. In this way, when an event occurs, the counter time is recorded in the particular channel's latches. The latch output is converted to CMOS levels and passed to the respective channel's FIFO buffer, which is 15 samples deep. The counter 1.2-GHz clock is derived from the MCLK input to the TMU at 200 MHz. This MCLK input is critical to the accuracy of the TMU, and any error in frequency is reflected as errors in time measurement. Likewise, jitter propagates to the counter and other circuits and adds noise to the measurement accuracy. The 200-MHz clock is the input to a clock multiplier. The clock multiplier uses delay-lock loop (DLL) techniques and combinatorial logic to construct a six-times clock from the reference input. This 1.2-GHz clock is passed to a high-power clock buffer, which drives all the circuitry in the master counter and many other circuits in the TMU.

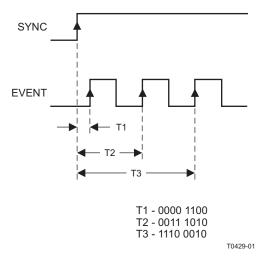

#### 8.3.2 Channels, Interpolator

There are four event channels and one sync channel. The event channels are identical, and the sync channel contains most of the event channel circuitry, but without a FIFO. An input pulse to the sync channel serves as the reference time zero for the TMU. An event input to a channel is compared to the sync time reference, and the time delay is calculated as the time difference modified by a calibration value. An event input follows the following signal path: the event input edge sets a fast latch (hit latch). The output of the latch is current-buffered and applied to the interpolator. The interpolator uses DLL techniques to subdivide the counter interval of 833 ps into 64 time intervals of 13 ps each. A large array of fast latches triggered by the hit latch captures the state of the 64 time intervals and logically determines 6 bits of timing data based on where the event occurred in the 833-ps clock interval. These 6 bits are latched and eventually passed to the FIFO, where they become the LSBs of the time-to-data conversion. A synchronizer circuit is also connected to the 64-latch array and removes the possible timing ambiguity between the 64 latches and the master counter. This takes a few 1.2-GHz clock pulses. When this process is complete, a pulse occurs which captures the master counter bits into the channel latches. A subsequent pulse loads all the bits from the interpolator and the counter into the channel FIFO. While this is happening, the hit latch is being reset, and the channel is prepared to accept another event edge. This process is fast enough to accept and measure event edges as close together as 5 ns.

#### 8.3.3 FIFO

Each event channel contains a 15-deep, 40-bit-wide FIFO, which allows for rapid accepting and measurement of event inputs and a user-defined data-output rate of those measurements.

#### 8.3.4 Calibration, ALU, Tag, Shifter

The output of the FIFO is controlled by the shifter, which is a free-running parallel-to-serial register. The shifter generates a load pulse, which transfers the data in the FIFO output into an arithmetic logic unit, which does the sync time and calibration time subtractions and then parallel-loads the result into the output serial register. An LVDS output buffer outputs the clock, data, and strobe signals to transfer the time-measurement data to the user. A TAG bit is appended to the leading edge of the data word. Currently the TAG feature is not implemented. The bit will always be 0 representing data.

# 8.3.5 Serial Interface, Temperature, Overhead

The TMU functions and options are controlled and read out by a serial interface built in CMOS logic that can operate up to 50 MB/s. There is one central controller which then drives registers, counters, etc., in each channel. A temperature sensor is located central to the chip and outputs a voltage proportional to the chip temperature. If the chip temperature rises above 141°C, the TMU powers down and outputs an overtemperature alarm signal. The TMU does not restart without a command through the serial interface. A bias circuit provides a regulated current bias and voltage reference for the TMU. The serial controller sequences some of the bias circuits to account for some acquisition times, and thereby, turns on the TMU.

#### 8.4 Device Functional Modes

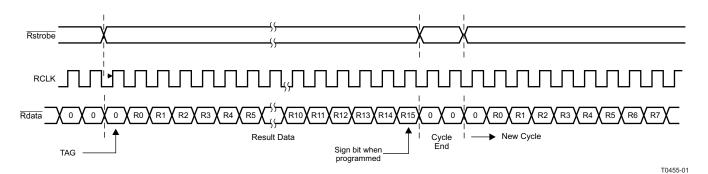

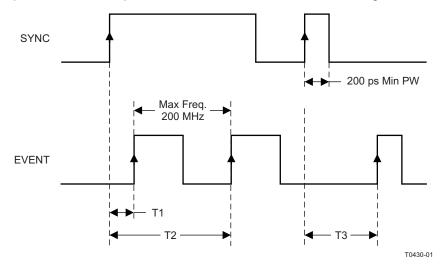

#### 8.4.1 Serial-Results Interface

The TMU captures time-stamp results and sends them to external logic using an LVDS serial-results port. The serial-results port consists of a clock signal (RCLK), four strobe signals (Rstrobex) and four data signals (Rdatax). The Rstrobex signal indicates that a time-stamp data transfer is about to begin for the corresponding channel.

The serial-result interface can be programmed to have a variable data-length format. Three register bits (Rlength0, Rlength1, and Rlength2), are used to program the required data transfer formats.

The default length of the data field is 40 bits, and it is in 2s-complement format. Table 1 defines the various data formats.

**RESULT TRANSFER FORMAT TIME RANGE** Rlenath2 Rlength1 Rlength0 -1.653 ns to 1.667 ns 8 bits 16 bits -426.626 ns to 426.639 ns 0 0 1 24 bits  $-109.22 \mu s$  to  $109.22 \mu s$ 0 1 0 32 bits -27.96 ms to 27.96 ms 0 1 1 40 bits -7.158 s to 7.158 s 0 0

Table 1. Result Transfer Format and Time Range

Table 1 refers to the 2s-complement format. Therefore, the 8-bit result represents a number between -127 and 128.

#### 8.4.2 Result-Interface Clock

The result-interface clock (RCLK) is generated internally and runs at a maximum frequency of 300 MHz. RCLK is programmable and may be programmed using two register bits (RCLK\_sel0 and RCLK\_sel1) according to the following table.

#### 8.4.3 DDR Mode

The result interface may be operated using one-half the clock frequency while keeping the data bit rate unchanged. In this mode, data is clocked out of the device using both edges of RCLK. A register bit (DDR\_EN) is used to enable DDR mode.

**Table 2. Result-Interface Clock**

| RCLK FREQUENCY (MHz)<br>NORMAL MODE | RCLK FREQUENCY (MHz)<br>DDR MODE | RCLK_sel1 | RCLK_sel0 |

|-------------------------------------|----------------------------------|-----------|-----------|

| 75 (default)                        | 37.5                             | 0         | 0         |

| 150                                 | 75                               | 0         | 1         |

| 300                                 | 150                              | 1         | 0         |

#### 8.4.4 Output Interface Throughput

Multiple data-word lengths and bit speeds, combined with a 15-sample-deep FIFO, give exceptional flexibility to output data throughput. The actual throughput is easily calculated, keeping in mind the following: The selected word length includes N-1 data bits and 1 sign bit, which are sent out last as the MSB. Two bit times do not have meaningful data during the Rstrobe high time. The TAG bit is appended to the data bits and is sent first. Example: for a bit rate of 300 MB/s and 16-bit length, the bit time is 3.33 ns, and the total word length is 16+1+2=19 bit times. Therefore, the throughput is 15.8 M samples/s. This is a constant output sample rate. The TMU can take time measurements at up to 200 MS/s. The 15-deep FIFO buffers these two rates until it is filled, in which case samples are lost.

#### 8.4.5 Counter Range

The coarse counter has three supported ranges: 18, 27, and 34 bits. The coarse counter applies to the 1.2-GHz clock.

**Table 3. Counter Range**

| COUNTER RANGE | MAX TIME RANGE | CNT_RNG1 | CNT_RNG0 |

|---------------|----------------|----------|----------|

| Reserved      | X              | 0        | 0        |

| 18 bit        | 218.45 µs      | 0        | 1        |

| 27 bit        | 111.84 ms      | 1        | 0        |

| 34 bit        | 14.31 s        | 1        | 1        |

### 8.4.5.1 Preconditioning Holdoff Delay Time

The preconditioning circuitry controls the ON/OFF state of the event latches. Following a Sync input signal, the TMU checks for a number of conditions before it proceeds with the time-measurement operation. Event input signals are ignored until all arming conditions are met. These conditions are as follows:

The hold-off delay is a programmable delay used to inhibit the creation of the next timestamp until the hold-off delay has expired. A 16-bit register is used for the hold-off delay count register. One holdoff delay register exists for each of the four event input channels.

The generation of a timestamp reloads the value from the holdoff delay register into a down counting counter. Timestamp generation pauses until hold-off delay counter reaches zero. There are seven ranges for the holdoff delay maximum duration. Three register bits are used to specify the required range.

Table 4 defines these ranges.

Table 4. Preconditioning Holdoff Delay Time

| RANGE | HOffRng2_x | HOffRng1_x | HOffRng0_x | FULL RANGE (ms) | LSB (ns) |

|-------|------------|------------|------------|-----------------|----------|

| 1     | 0          | 0          | 0          | 0.655           | 10       |

| 2     | 0          | 0          | 1          | 2.621           | 40       |

| 3     | 0          | 1          | 0          | 10.486          | 160      |

| 4     | 0          | 1          | 1          | 41.943          | 640      |

| 5     | 1          | 0          | 0          | 167.772         | 2560     |

| 6     | 1          | 0          | 1          | 671.089         | 10,240   |

| 7     | 1          | 1          | X          | 2,684           | 40,960   |

In range 1 each count in the holdoff register delays the next possible timestamps by 10 ns (100-MHz clock period). The maximum delay range for this feature is 2.684 s for each channel. To disable this feature, a register bit (HOffTm\_EN\_x) is set to 0.

### 8.4.5.2 Arming Conditions

An additional arming condition for each event channel is based on other channels meeting some preprogrammed conditions before it can become fully armed. These conditions are in addition to the individual channel arming conditions.

- A given channel does not become fully armed until one, two, or all three of the other channels are armed. A

logical AND of one or more channels.

- A given channel does not become fully armed until the holdoff delay expires, the arming counter reaches zero, and the logical OR of one or more channels has been active.

The following tables define this conditional operation.

**Table 5. Channel-A Conditional Arming Definition**

| Arm_sel3A | Arm_sel2A | Arm_sel1A | Arm_sel0A | OUTCOME                                                |

|-----------|-----------|-----------|-----------|--------------------------------------------------------|

| 0         | 0         | 0         | 0         | ChA is armed if ChB is fully armed.                    |

| 0         | 0         | 0         | 1         | ChA is armed if ChC is fully armed.                    |

| 0         | 0         | 1         | 0         | ChA is armed if ChD is fully armed.                    |

| 0         | 0         | 1         | 1         | ChA is armed if ChB AND ChC are fully armed.           |

| 0         | 1         | 0         | 0         | ChA is armed if ChB AND ChD are fully armed.           |

| 0         | 1         | 0         | 1         | ChA is armed if ChC AND ChD are fully armed.           |

| 0         | 1         | 1         | 0         | ChA is armed if ChB AND ChC AND ChD are fully armed.   |

| 0         | 1         | 1         | 1         | ChA will be armed if ChB OR ChC is fully armed.        |

| 1         | 0         | 0         | 0         | ChA will be armed if ChB OR ChD is fully armed.        |

| 1         | 0         | 0         | 1         | ChA will be armed if ChC OR ChD is fully armed.        |

| 1         | 0         | 1         | 0         | ChA will be armed if ChB OR ChC OR ChD is fully armed. |

| 1         | 0         | 1         | 1         | Reserved                                               |

| 1         | 1         | 0         | 0         | Reserved                                               |

| 1         | 1         | 0         | 1         | Reserved                                               |

| 1         | 1         | 1         | 0         | Reserved                                               |

| 1         | 1         | 1         | 1         | Reserved                                               |

**Table 6. Channel-B Conditional Arming Definition**

| Arm_sel3A | Arm_sel2A | Arm_sel1A | Arm_sel0A | OUTCOME                                                |

|-----------|-----------|-----------|-----------|--------------------------------------------------------|

| 0         | 0         | 0         | 0         | ChB is armed if ChA is fully armed.                    |

| 0         | 0         | 0         | 1         | ChB is armed if ChC is fully armed.                    |

| 0         | 0         | 1         | 0         | ChB is armed if ChD is fully armed.                    |

| 0         | 0         | 1         | 1         | ChB is armed if ChA AND ChC are fully armed.           |

| 0         | 1         | 0         | 0         | ChB is armed if ChA AND ChD are fully armed.           |

| 0         | 1         | 0         | 1         | ChB is armed if ChC AND ChD are fully armed.           |

| 0         | 1         | 1         | 0         | ChB is armed if ChA AND ChC AND ChD are fully armed.   |

| 0         | 1         | 1         | 1         | ChB will be armed if ChA OR ChC is fully armed.        |

| 1         | 0         | 0         | 0         | ChB will be armed if ChA OR ChD is fully armed.        |

| 1         | 0         | 0         | 1         | ChB will be armed if ChC OR ChD is fully armed.        |

| 1         | 0         | 1         | 0         | ChB will be armed if ChA OR ChC OR ChD is fully armed. |

| 1         | 0         | 1         | 1         | Reserved                                               |

| 1         | 1         | 0         | 0         | Reserved                                               |

| 1         | 1         | 0         | 1         | Reserved                                               |

| 1         | 1         | 1         | 0         | Reserved                                               |

| 1         | 1         | 1         | 1         | Reserved                                               |

# **Table 7. Channel-C Conditional Arming Definition**

| Arm_sel3A | Arm_sel2A | Arm_sel1A | Arm_sel0A | OUTCOME                                                |

|-----------|-----------|-----------|-----------|--------------------------------------------------------|

| 0         | 0         | 0         | 0         | ChC is armed if ChA is fully armed.                    |

| 0         | 0         | 0         | 1         | ChC is armed if ChB is fully armed.                    |

| 0         | 0         | 1         | 0         | ChC is armed if ChD is fully armed.                    |

| 0         | 0         | 1         | 1         | ChC is armed if ChA AND ChB are fully armed.           |

| 0         | 1         | 0         | 0         | ChC is armed if ChB AND ChD are fully armed.           |

| 0         | 1         | 0         | 1         | ChC is armed if ChA AND ChD are fully armed.           |

| 0         | 1         | 1         | 0         | ChC is armed if ChA AND ChB AND ChD are fully armed.   |

| 0         | 1         | 1         | 1         | ChC will be armed if ChA OR ChB is fully armed.        |

| 1         | 0         | 0         | 0         | ChC will be armed if ChB OR ChD is fully armed.        |

| 1         | 0         | 0         | 1         | ChC will be armed if ChB OR ChD is fully armed.        |

| 1         | 0         | 1         | 0         | ChC will be armed if ChA OR ChB OR ChD is fully armed. |

| 1         | 0         | 1         | 1         | Reserved                                               |

| 1         | 1         | 0         | 0         | Reserved                                               |

| 1         | 1         | 0         | 1         | Reserved                                               |

| 1         | 1         | 1         | 0         | Reserved                                               |

| 1         | 1         | 1         | 1         | Reserved                                               |

# **Table 8. Channel-D Conditional Arming Definition**

| Arm_sel3A | Arm_sel2A | Arm_sel1A | Arm_sel0A | OUTCOME                                                |

|-----------|-----------|-----------|-----------|--------------------------------------------------------|

| 0         | 0         | 0         | 0         | ChD is armed if ChA is fully armed.                    |

| 0         | 0         | 0         | 1         | ChD is armed if ChB is fully armed.                    |

| 0         | 0         | 1         | 0         | ChD is armed if ChC is fully armed.                    |

| 0         | 0         | 1         | 1         | ChD is armed if ChA AND ChB are fully armed.           |

| 0         | 1         | 0         | 0         | ChD is armed if ChA AND ChC are fully armed.           |

| 0         | 1         | 0         | 1         | ChD is armed if ChB AND ChC are fully armed.           |

| 0         | 1         | 1         | 0         | ChD is armed if ChA AND ChB AND ChC are fully armed.   |

| 0         | 1         | 1         | 1         | ChD will be armed if ChA OR ChB is fully armed.        |

| 1         | 0         | 0         | 0         | ChD will be armed if ChB OR ChC is fully armed.        |

| 1         | 0         | 0         | 1         | ChD will be armed if ChB OR ChC is fully armed.        |

| 1         | 0         | 1         | 0         | ChD will be armed if ChA OR ChB OR ChC is fully armed. |

| 1         | 0         | 1         | 1         | Reserved                                               |

| 1         | 1         | 0         | 0         | Reserved                                               |

| 1         | 1         | 0         | 1         | Reserved                                               |

| 1         | 1         | 1         | 0         | Reserved                                               |

| 1         | 1         | 1         | 1         | Reserved                                               |

## **NOTE**

When programming individual-channel arming conditions, it is important to avoid conditions where dependency would cause a lockup situation.

# 8.4.6 Resister Map Descriptions for All Channels and Central Register

# Table 9. Control and Status Register Descriptions For All Channels (X)

| Register | Bit | Name                         | Function                                                  | LogicState | Description          |

|----------|-----|------------------------------|-----------------------------------------------------------|------------|----------------------|

|          | 0   | En ChX                       | Enable or disable channel X by powering down the          | 0          | Channel is disabled  |

|          | U   | EII_CIIX                     | channel. Time to enable a channel is 200 µs.              | 1          | Channel is enabled   |

|          | 1   | ChX IP EN                    | Enables or disables the input of channel X. Events are    | 0          | Input is disabled    |

|          | '   | CIIX_IP_EN                   | prevented from entering a channel.                        | 1          | Input is enabled     |

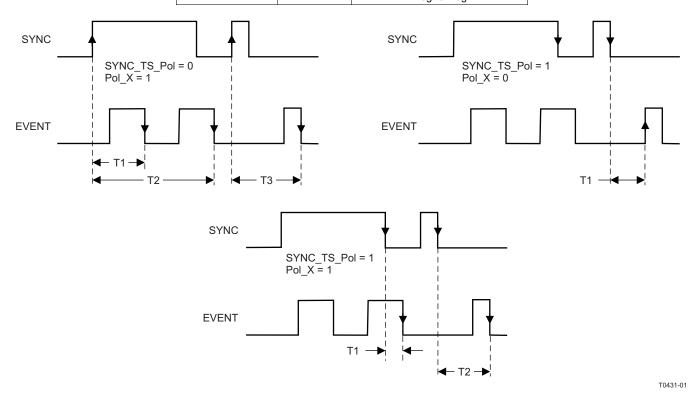

| 00h      | 2   | Pol X                        | Defines the polarity of the event inputX for the upcoming | 0          | Positive edge        |

| 20h      | 2   | FULX                         | timestamp generation.                                     | 1          | Negative edge        |

| 40h      | 7   | LIO#Page V                   | Defines heldeff reason for exert input V                  | 0          | Holdoff range value  |

| 60h      | ,   | HOffRng0_X                   | Defines holdoff range for event input X.                  | 1          | Holdoff range value  |

|          | 0   | 8 HOffRng1_X Defines holdoff | Defines heldeff range for event input V                   | 0          | Holdoff range value  |

|          | 0   |                              | Defines holdoff range for event input X.                  | 1          | Holdoff range value  |

|          | 9   | HOffRng2_X                   | Defines holdoff range for event input X.                  | 0          | Holdoff range value  |

|          | Э   | HOHKIIGZ_X                   | Defines holdon range for event input A.                   | 1          | Hold-off range value |

## Table 10. Control and Status Register Descriptions for All Channels (X)

| Register   | Bit | Name            | Function                                                 | Logic State | Description           |

|------------|-----|-----------------|----------------------------------------------------------|-------------|-----------------------|

|            | 0   | Reserved        | Reserved                                                 | х           |                       |

|            | 1   | Arm colOV       | Define arming conditions for channel V                   | 0           | Arming value          |

|            | _   | Arm_sel0X       | Define arming conditions for channel X.                  | 1           | Arming value          |

|            | 2   | Arm sel1X       | Define arming conditions for channel V                   | 0           | Arming value          |

| 01h        | ۷   | AIII_SerrA      | Define arming conditions for channel X.                  | 1           | Arming value          |

| 21h<br>41h | 3   | Arm sel2X       | Define arming conditions for channel V                   | 0           | Arming value          |

| 61h        | 3   | AIIII_Sei2A     | Define arming conditions for channel X.                  | 1           | Arming value          |

|            | 4   | Arm_sel3X       | Define arming conditions for channel X.                  | 0           | Arming value          |

|            | 4   |                 |                                                          | 1           | Arming value          |

|            | 5   | E Arma Con En V | Enables or disables the arming conditions for channel X. | 0           | Arming cond. disabled |

|            | 5   | Armg_Con_En_X   |                                                          | 1           | Arming cond. enabled  |

|            | 0   | DLL Lock X      |                                                          | 0           | DLL locked            |

|            | U   | DLL_LOCK_X      | Indicates the DLL lock status for channel X.             | 1           | DLL not locked        |

| 04h        | 2   | Reserved        | Reserved                                                 | х           |                       |

| 24h<br>44h | 3   | FIFO Full V     | Indicates that the FIFO is full. Timestamps arriving     | 0           | FIFO not full         |

| 64h        | 3   | 3 FIFO_Full_X   | while FIFO is full are lost.                             | 1           | FIFO full             |

|            | 4   | FIFO Empty V    | Indicates that the FIFO is ampty                         | 0           | FIFO not empty        |

|            | 4   | FIFO_Empty_X    | Indicates that the FIFO is empty.                        | 1           | FIFO empty            |

# **Table 11. Central Control and Status Registers Description**

| Register | Bit | Name          | Function                                                    | Logic State | Description          |

|----------|-----|---------------|-------------------------------------------------------------|-------------|----------------------|

|          |     |               |                                                             | 0           | Disabled             |

|          | 0   | TEST_En       | Enables or disables factory test routines.                  | 1           | Enabled              |

|          |     |               |                                                             | 0           |                      |

|          | 1   | RESET         | Reset the device. Device is fully operational after 250 µs. | 1           | Reset                |

|          |     |               | It enables DDR mode allowing the result interface to        | 0           | Normal mode          |

|          | 2   | DDR_En        | utput data on both edges.                                   | 1           | DDR Mode             |

|          | _   | _             |                                                             | 0           | Inputs not connected |

|          | 3   | Connect_AB    | It connects channels A and B inputs together.               | 1           | Inputs connected     |

|          |     | _             |                                                             | 0           | Inputs not connected |

|          | 4   | Connect_CD    | It connects channels C and D inputs together.               | 1           | Inputs connected     |

|          | _   | DI 11.0       | Define the result data length being used for the            | 0           | Length value         |

|          | 5   | Rlength0      | timestamps.                                                 | 1           | Length value         |

|          | ^   | Diamenth 4    | Define the result data length being used for the            | 0           | Length value         |

|          | 6   | Rlength1      | timestamps.                                                 | 1           | Length value         |

| 0.01     | -   | Diamenth O    | Define the result data length being used for the            | 0           | Length value         |

| 80h      | 7   | Rlength2      | timestamps.                                                 | 1           | Length value         |

|          | _   | DOLK IO       | Define DOLK framework                                       | 0           | Frequency value      |

|          | 8   | RCLK_sel0     | Define RCLK frequency.                                      | 1           | Frequency value      |

|          | ^   | DOLK IA       | Define DOLK for many                                        | 0           | Frequency value      |

|          | 9   | RCLK_sel1     | Define RCLK frequency.                                      | 1           | Frequency value      |

|          | 40  | OT 5-         | Frables or disables the country of the plant since its      | 0           | Disabled             |

|          | 10  | OT_En         | Enables or disables the overtemperature alarm circuits.     | 1           | Enabled              |

|          | 44  | DCT OT ALM    | Decete the temperature clare                                | 0           |                      |

|          | 11  | RST_OT_ALM    | Resets the temperature alarm.                               | 1           | Reset alarm state    |

|          | 12  | CVNC TO Dol   | Defines the polarity of the Sync input for the upcoming     | 0           | Positive edge        |

|          | 12  | SYNC_TS_Pol   | timestamp generation.                                       | 1           | Negative edge        |

|          | 13  | SYNC_IP_ENI   | Enables or disables the sync channel                        | 0           | Sync disabled        |

|          | 13  | STNC_IF_LINI  | Chables of disables the sync charmer                        | 1           | Sync enabled         |

|          | 14  | PWR_DN        | Powers down the device                                      | 0           | Powered up           |

|          | 17  | T WIC_DIV     | 1 owers down the device                                     | 1           | Powered down         |

|          | 1   | CNT_Rng0      | Defines the coarse counter range                            | 0           | Range value          |

|          | •   | OIVI_IXIIgo   | Defines the coarse counter range                            | 1           | Range value          |

| 81h      | 2   | CNT_Rng1      | Defines the coarse counter range                            | 0           | Range value          |

| 0111     | _   | Orti_raigi    | Defined the deares dearlier range                           | 1           | Range value          |

|          | 3   | Quiet_Mod     | It disables the RCLK digital clks internal during timestamp | 0           | Normal mode          |

|          |     | Quict_IVIOu   | process. Allows for only 16 timestamps.                     | 1           | Quiet mode           |

|          | 0   | TMU_Ready     | Indicates that the internal clks, coarse counter and Sync   | 0           | Device is not ready  |

|          | J   | o_rtoddy      | channel are operational.                                    | 1           | Device is ready      |

|          | 1   | OT_ALM        | Over temperature alarm. Indicates that the junction         | 0           | No alarm             |

| 82h      | i   | Ç, (E.)       | temperature is 140°C.                                       | 1           | Alarm is enabled     |

| 0211     | 2   | DLL_Lock_Sync | Indicates the Sync channel DLL lock status.                 | 0           | DLL is locked        |

|          |     |               | maioates the cytic channel DLL lock status.                 | 1           | DLL is not locked    |

|          | 3   | DLL_Lock_1G2  | Indicates the lock status of the 1.2-GHz internal clock.    | 0           | DLL is locked        |

|          |     |               |                                                             | 1           | DLL is not locked    |

Submit Documentation Feedback

Copyright © 2010–2015, Texas Instruments Incorporated

## 8.5 Programming

#### 8.5.1 Host Processor Bus Interface

The THS788 device includes a high-speed serial interface to a host processor. The host interface is used for writing or reading registers that reside in the TMU chip. These registers allow configuration of the device functions. All registers are capable of both read and write operations unless otherwise stated.

#### 8.5.1.1 Serial Interface

The TMU serial interface operates at speeds of up to 50 MHz. Register addresses are 8 bits long. Data words are 16 bits wide, enabling more-efficient interface transactions. The serial bus implementation uses three LVCMOS signals: HCLK, Hstrobe, and Hdata. The HCLK and Hstrobe signals are inputs only, and the Hdata signal is bidirectional. The HCLK signal is not required to run continuously. Thus, the host processor may disable the clock by setting it to a low state after the completion of any required register accesses.

When data is transferred into the device, Hdata is configured as an input bus, and data is latched on a rising edge of HCLK. When data is transferred out of the part, Hdata is configured as an output bus, and data is updated on the falling edge of HCLK. Hstrobe is the control signal that identifies the beginning of a host bus transaction. Hstrobe must remain low for the duration of the transaction, and must go high for at least two clock cycles before another transaction can begin.

#### 8.5.1.2 Read vs Write Cycle

The first Hdata bit latched by HCLK in a transaction identifies the transaction type.

First Hdata bit = 1 for read; data flows out of the chip.

First Hdata bit = 0 for write; data flows into the chip.

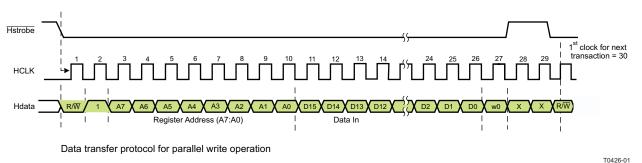

### 8.5.1.3 Parallel (Broadcast) Write

Parallel write is a means of allowing identical data to be transferred to more than one channel in one transaction. The second Hdata bit of a transaction indicates whether a parallel write occurs.

Second Hdata bit = 0: data goes to the selected channel.

Second Hdata bit = 1; data goes to all four channels.

#### 8.5.1.4 Address

After the R/W bit and the parallel write bit, the following 8 bits on the Hdata line contain the source address of the data word for a read cycle or the destination address of the data word for a write cycle. Address bits are shifted in MSB first, LSB last.

Third HCLK - Address Bit 7 (MSB)

Tenth HCLK - Address Bit 0 (LSB)

#### 8.5.1.5 Data

The data stream is 16 bits long, and it is loaded or read back MSB first, LSB last. The timing for read and write cycles is different, as the drivers on Hdata alternate between going into high-impedance and driving the line.

#### 8.5.1.6 Reset

Reset is an external hardware signal that places all internal registers and control lines into their default states. The THS788 device resets after a power-up sequence (POR). Hardware reset is an LVCMOS active-low signal and is required to stay low for approximately 100 ns.

Reset places the TMU in a predetermined idle state at power on, and anytime the system software initializes the system hardware. In the idle state, the TMU ignores state changes on the Event inputs and never creates timestamps. The TMU is capable of switching within 250 µs from the idle state to a state that creates accurate timestamps.

### 8.5.1.7 Chip ID

Address (83h) is a read-only register that identifies the product and the die revision. The 16-bit register is divided into two 8-bit sections. The LSB represents the revision history and the MSB represents the last two digits of THS788 device (i.e., 80). The first revision (1.0) is as follows:

1000 0000 0001.0000

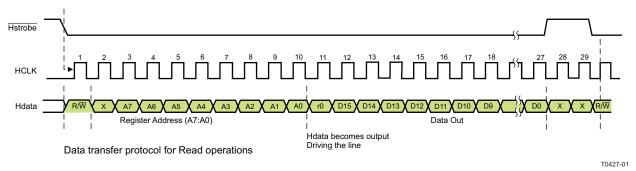

#### 8.5.1.8 Read Operations

Reading the THS788 device registers via the host interface requires the following sequence:

The host controller initiates a read cycle by setting the host strobe signal, Hstrobe, to a low state. The serial Hdata sequence starts with a high R/W bit, followed by (either 1 or 0) for parallel-write bit and 8 bits of address, with most-significant bit (A7) first. The host controller should put the Hdata signal in the high-impedance state beginning at the falling edge of HCLK pulse 10. The THS788 device allows one clock cycle, (r0) for the host to reverse the data-channel direction and begins driving the Hdata line on the falling edge of HCLK pulse 11. The data is read beginning with the most-significant bit (D15) and ending with the least-significant bit (D0).

The host must drive Hstrobe to a high state for a minimum of two HCLK periods beginning at the falling edge of HCLK pulse 27 to indicate the completion of the read cycle. Figure 3 shows the timing diagram of the read operation.

Figure 3. Read Operation

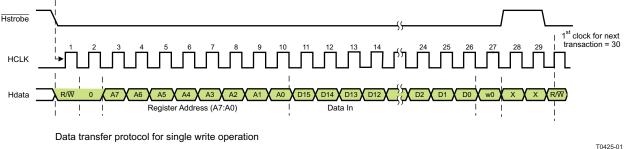

#### 8.5.1.9 Write Operations

Writing into the THS788 device registers via the host interface requires the following sequence:

After the Hstrobe line is pulled low (start condition), the R/W bit is set low, followed by a 0 for the parallel-write bit (single-register write), then the memory address (A7–A0) followed by the data (D15:D0) to be programmed. The next clock cycle (w) is required to allow data to be latched and stored at the destination address (or addresses in the case of a parallel write), followed by at least two dummy clock cycles during which the Hstrobe is high, indicating the completion of the write cycle. Figure 4 and Figure 4 show timing diagrams of write operations.

Figure 4. Write Operation

10425-0

#### 8.5.1.10 Write Operations to Multiple Destinations

This is similar to the single-write operation except the parallel-load bit is set to 1.

Figure 5. Write Operations to Multiple Destinations

#### 8.5.2 Serial-Results Interface and ALU

#### 8.5.2.1 Event Latches

Each event channel and the sync channel include two event latches whose inputs are both connected to the LVDS input-buffer output. One latch is the time-measurement signal path and connects to the interpolator and synchronizer. The other latch connects to the preconditioning circuitry. A selectable rising or falling edge of an event pulse sets the latch. the latch remains set until the interpolator has finished processing the event, at which time the interpolator resets the latch. The latch, however, does not accept another event pulse until the event input returns to its initial state and remains for the initial event-pulse duration. Any event transitions which occur before the interpolator has completed processing the previous event are ignored. For example, assume that rising edge is selected. Two rising edges can occur as quickly as 5 ns apart. The falling edge can occur anywhere from 250 ps after the rising edge to 250 ps before the next rising edge. Any other edges or glitches are ignored. In addition to the rising/falling-edge selection, the event latch includes the gating function whereby the preconditioning logic controls whether the TMU accepts and processes an event input. The second event latch operates similarly to the main signal-path latch with the following exceptions: The latch is followed by and ECL-to-CMOS converter, because all the preconditioning logic is CMOS instead of the fast ECL circuitry in the measurement chain. The preconditioning logic rather than the interpolator resets this latch, and the timing of the reset pulse is slightly faster than the interpolator.

#### 8.5.2.2 FIFO

Timestamps are written to a FIFO at high speed and read for further processing at a lower speed before being sent to the result interface. This FIFO is 15 bits deep and 40 bits wide. There are four FIFOs in THS788 device, one for each channel. There are two status registers (FIFO\_Full\_x and FIFO\_Empty\_x), which are set when a FIFO reaches its full capacity and when it is empty, respectively.

Timestamps are taken and loaded into the FIFO as events occur. Timestamps are mathematically processed by an arithmetic logic unit (ALU) which calculates the difference between the event and the sync timestamps and factors in the appropriate calibration value from the calibration register. The ALU operates on the data as it is read out of the FIFO and sent out through the serial-results interface. The serial-results interface controls the output of the FIFO.

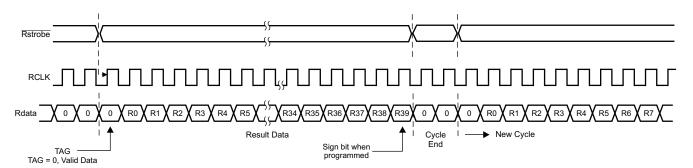

## 8.5.2.3 Result-Interface Operation

The TMU initiates a read cycle by setting the strobe signal, Rstrobe, to a low state, indicating that the data transfer is about to begin. The serial Rdata sequence starts with a TAG bit, followed by the 40-bit data (R0 to R39). R39 (MSB) is the sign bit. Following the last data bit (R39), the strobe signal (Rstrobe) goes high for two clock cycles, indicating the end of the transaction.

The data is clocked out of the TMU on the rising edge of RCLK. The receiving device clocks the data in on the rising edge of RCLK. Figure 6 and Figure 7 show a 40-bit result on the result interface.

T0428-01

Figure 6. Result-Interface Operation A

Figure 7. Result-Interface Operation B

#### NOTE

In the preceding diagrams, only RCLK\_P is drawn to indicate the correct edge with respect to data.

#### 8.5.2.4 Serial Results Latency

The event stored in the FIFO will be transferred to ALU and subsequently to the free running results data shift register when the shift register enters a load pulse. The load pulse is generated once per ALU/shift register processing cycle. The load pulse will trigger the ALU and transfer result to the parallel to serial shift register for output. The cycle time of the load pulse is dependent upon the depth of the result transfer register and data rate. Because the results parallel to serial register are free running, the load pulse will be asynchronous to the actual event. So, the latency will depend upon where in the current cycle the load pulse occurred relative to the event being captured into the FIFO.

The worst case for data to be output from serial bus:

$$T_{\text{event}} + 5(R_{\text{clkcycles}}) + (R_{\text{datalength}} + 3) \times R_{\text{clkcycles}} + (R_{\text{datalength}} + 3) \times R_{\text{clkcycles}}$$

(1)

The best case for data to be output from serial bus:

$$T_{event} + 5(R_{clkcycles}) + (R_{datalength} + 3) \times R_{clkcycles}$$

where

- T<sub>event</sub> = 5 ns (minimum repeat capture time)

- 5(R<sub>clkcycles</sub>) = number cycles for FIFO to ALU to Shift register

- R<sub>clkcycles</sub> is period of R<sub>CLK</sub> data = 300 MHz, SDR = 3.33 ns

- R<sub>datalength</sub> = number of results bits = 40 for THS788 device (2)

In the case where  $R_{CLK} = 300 \text{ MHz}$ , with 40-bit serial result:

Min Latency =

$$5 \text{ ns} + 17 \text{ ns} + (40 + 3) \times 3.33 \text{ ns} = 165 \text{ ns}$$

(3)

Max Latency =  $5 \text{ ns} + 17 \text{ ns} + (40 + 3) \times 3.33 \text{ ns} + (40 + 3) \times 3.33 \text{ ns} = 308 \text{ ns}$  (4)

#### NOTE

The THS788 device was intended for sync-event, event, event, sync-event ... processing. However, some applications desire the use of a sync pulse that is a fixed period. During a sync period, there could be multiple events, or no events. The TMU can be used effectively for this scenario as well.

For applications using the THS788 device in this fashion, it is important to consider the uncertainty that is introduced by the load pulse timing. Because the load pulse is free running and asynchronous to any events, the latency will vary based on this timing. Additionally, the load pulse is the mechanism that will cause the ALU to grab the current sync value for the result calculation.

If an event is in the FIFO, waiting for the load pulse and a new sync occurs, the ALU will use the new sync value for calculating the result. In this case, the event would precede the sync resulting in a negative result. The system could then offset the result by one sync cycle as the result is negative, indicating that is was captured during a prior sync cycle.

#### 8.5.2.5 TMU Calibration

The TMU calibration process is identical to a normal TMU time-stamp measurement. The process involves measuring a known interval and calculating the difference between the measured value and the actual value. The result is then stored into calibration registers inside the TMU. The TMU takes the stored calibration values and corrects the subsequent time-stamp measurements.

There are four calibration registers for each channel. These are identified as follows:

- A calibration register for positive sync edge and positive event edge

- A calibration register for positive sync edge and negative event edge

- A calibration register for negative sync edge and positive event edge

- · A calibration register for negative sync edge and negative event edge

Calibration due to temperature changes following the initial system calibration may be required if temperature variations are significant.

### 8.5.2.6 Temperature Sensor

A temperature sensor has been located centrally in the THS788 device for monitoring the die temperature. There are two monitor outputs for this feature. An analog voltage proportional to the die temperature is presented at the TEMP pin. Also, an overtemperature alarm output is available at the OT\_ALARM pin. The overtemperature alarm (OT\_ALARM) is an open-drain output that is activated when the die temperature reaches 141°C.

The overtemperature alarm sets a register bit (OT\_ALM) in the central register and may be accessed through the serial interface.

The overtemperature alarm initiates an automatic power down to prevent overheating of the device. The digital blocks remain functional when in automatic power down. Following a power down, the user is required to reset OT\_ALM using the serial interface. A register bit (RST\_OT\_ALM) is used for this purpose.

The temperature-monitoring function and its associated overtemperarture alarm circuit may be disabled by the user, using a register bit (OT\_EN). The default for the temperature-monitoring function is enabled.

OT\_EN = 1: Temperature-monitoring function is enabled.

OT\_EN = 0: Temperature-monitoring function is disabled.

Copyright © 2010–2015, Texas Instruments Incorporated

# 8.6 Register Maps

# 8.6.1 Register Address Space

# **Table 12. Channel-A Registers**

| Address (Hex) | Register                                                               |     |

|---------------|------------------------------------------------------------------------|-----|

| 00h–01h       | Control register                                                       | R/W |

| 02h-03h       | Not used                                                               | NA  |

| 04h           | Status registers                                                       | RO  |

| 05h           | Not used                                                               | NA  |

| 06h           | Holdoff delay time register                                            | R/W |

| 07h           | Not used                                                               | R/W |

| 08h           | Not used                                                               | R/W |

| 09h           | Not used                                                               | R/W |

| 0Ah           | Not used                                                               | R/W |

| 0Bh           | Not used                                                               | R/W |

| 0Ch           | Positive edge sync and positive edge hit calibration register, 16 bits | R/W |

| 0Dh           | Positive edge sync and negative edge hit calibration register, 16 bits | R/W |

| 0Eh           | Negative edge sync and positive edge hit calibration register, 16 bits | R/W |

| 0Fh           | Negative edge sync and negative edge hit calibration register, 16 bits | R/W |

| 10h-12h       | Timestamp register, 40 bits                                            | R   |

| 13h-1Fh       | Not used                                                               | NA  |

# Table 13. Channel-B Registers

| Address (Hex) | Register                                                               |     |

|---------------|------------------------------------------------------------------------|-----|

| 20h-21h       | Control register                                                       | R/W |

| 22h-23h       | Not used                                                               | NA  |

| 24h           | Status registers                                                       | RO  |

| 25h           | Not used                                                               | NA  |

| 26h           | Hold_off delay time register                                           | R/W |

| 27h           | Not used                                                               | R/W |

| 28h           | Not used                                                               | R/W |

| 29h           | Not used                                                               | R/W |

| 2Ah           | Not used                                                               | R/W |

| 2Bh           | Not used                                                               | R/W |

| 2Ch           | Positive edge sync and positive edge hit calibration register, 16 bits | R/W |

| 2Dh           | Positive edge sync and negative edge hit calibration register, 16 bits | R/W |

| 2Eh           | Negative edge sync and positive edge hit calibration register, 16 bits | R/W |

| 2Fh           | Negative edge sync and negative edge hit calibration register, 16 bits | R/W |

| 30h-32h       | Timestamp register, 40 bits                                            | R   |

| 33h-3Fh       | Not used                                                               | NA  |

Product Folder Links: THS788

22

# Table 14. Channel-C Registers

| Address (Hex) | Register                                                               |     |

|---------------|------------------------------------------------------------------------|-----|

| 40h–41h       | Control register                                                       | R/W |

| 42h-43h       | Not used                                                               | NA  |

| 44h           | Status registers                                                       | RO  |

| 45h           | Not used                                                               | NA  |

| 46h           | Not used                                                               | R/W |

| 47h           | Not used                                                               | R/W |

| 48h           | Not used                                                               | R/W |

| 49h           | Not used                                                               | R/W |

| 4Ah           | Not used                                                               | R/W |

| 4Bh           | Not used                                                               | R/W |

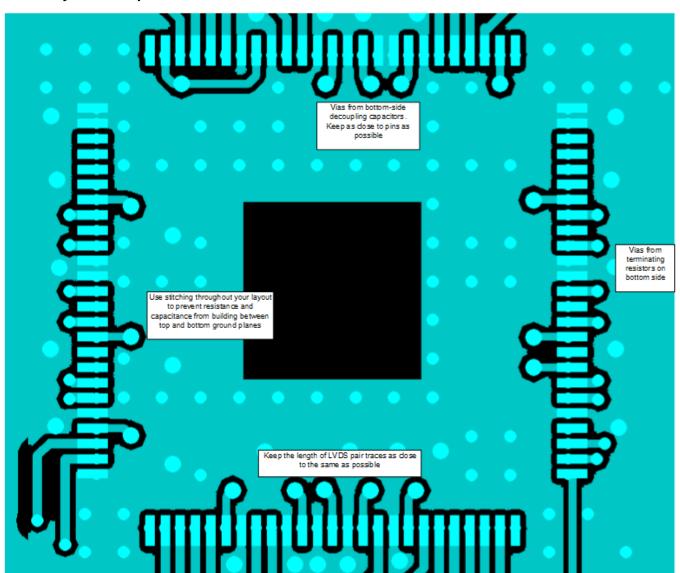

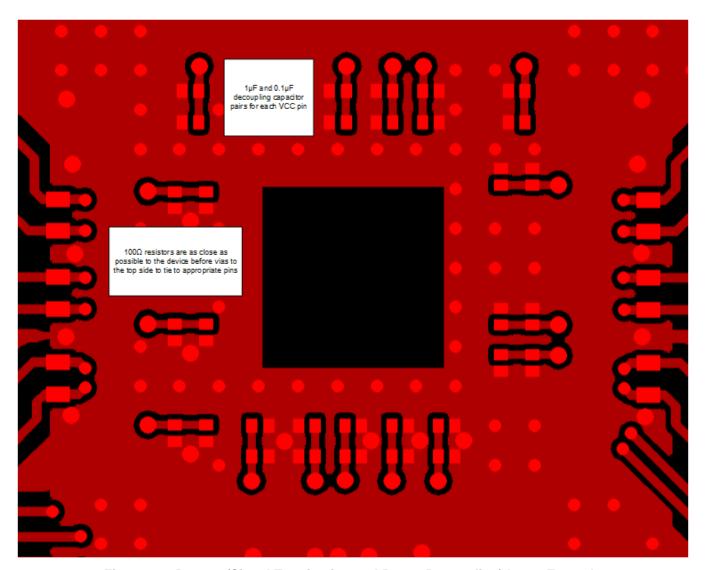

| 4Ch           | Positive edge sync and positive edge hit calibration register, 16 bits | R/W |