Data Sheet September 11, 2007 FN3679.12

#### 400MHz, 4x1 Video Crosspoint Switch

The HA4314B is a very wide bandwidth 4x1 crosspoint switch ideal for professional video switching, HDTV, computer monitor routing, and other high performance applications. The circuit features very low power dissipation (105mW Enabled, 4mW Disabled), excellent differential gain and phase, and very high off isolation. When disabled, the output is switched to a high impedance state, making the HA4314B ideal for routing matrix equipment.

The HA4314B requires no external current source, and features fast switching and symmetric slew rates.

For a 4x1 crosspoint with Tally outputs (channel indicators) or with synchronous control signals, please refer to the HA4404B and HA4344B data sheets, respectively.

For audio channels requiring larger signal swings, please refer to the CD22M3494 (16x8) data sheet.

## **Ordering Information**

| PART<br>NUMBER        | PART<br>MARKING | TEMP.<br>RANGE<br>(°C) | PACKAGE                   | PKG.<br>DWG. # |

|-----------------------|-----------------|------------------------|---------------------------|----------------|

| HA4314BCA             | HA 4314BCA      | 0 to +70               | 16 Ld QSOP                | M16.15A        |

| HA4314BCAZ*<br>(Note) | HA43 14BCAZ     | 0 to +70               | 16 Ld QSOP<br>(Pb-free)   | M16.15A        |

| HA4314BCB*            | HA4314BCB       | 0 to +70               | 14 Ld SOIC                | M14.15         |

| HA4314BCBZ*<br>(Note) | 4314BCBZ        | 0 to +70               | 14 Ld SOIC<br>(Pb-free)   | M14.15         |

| HA4314BCP             | HA4314BCP       | 0 to +70               | 14 Ld PDIP                | E14.3          |

| HA4314BCPZ<br>(Note)  | HA4314BCPZ      | 0 to +70               | 14 Ld PDIP**<br>(Pb-free) | E14.3          |

<sup>\*</sup>Add "96" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate PLUS ANNEAL - e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### **Features**

| Low Power Dissipation                    |

|------------------------------------------|

| • Symmetrical Slew Rates                 |

| • 0.1dB Gain Flatness                    |

| • -3dB Bandwidth                         |

| • Off Isolation (100MHz)                 |

| Crosstalk Rejection (30MHz) 80dB         |

| Differential Gain and Phase 0.01%/0.01 ° |

| • High ESD Rating >2000V                 |

|                                          |

- TTL Compatible Control Inputs

- Improved Replacement for GX4314 and GX4314L

- Pb-Free Available (RoHS Compliant)

#### **Applications**

- · Professional Video Switching and Routing

- HDTV

- · Computer Graphics

- RF Switching and Routing

- · PCM Data Routing

#### Truth Table

| cs | <b>A</b> 1 | Α0 | OUT      |

|----|------------|----|----------|

| 0  | 0          | 0  | IN0      |

| 0  | 0          | 1  | IN1      |

| 0  | 1          | 0  | IN2      |

| 0  | 1          | 1  | IN3      |

| 1  | Х          | Х  | HIGH - Z |

<sup>\*\*</sup>Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications

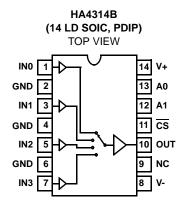

## Pinouts

NOTE: These pins must be left floating or connected to ground

#### **Absolute Maximum Ratings**

| Voltage Between V+ and V 12V                           |

|--------------------------------------------------------|

| Input Voltage                                          |

| Digital Input Current (Note 2)±25mA                    |

| Analog Input Current (Note 2) ±5mA                     |

| Output Current                                         |

| ESD Rating                                             |

| Human Body Model (Per MIL-STD-883 Method 3015.7) 2000V |

#### **Operating Conditions**

| Temperature Range | 0°C to +70°C |

|-------------------|--------------|

|                   |              |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)                                      | $\theta_{JA}  (^{\circ}\text{C/W})$ |

|---------------------------------------------------------------------------|-------------------------------------|

| 14 Ld PDIP Package*                                                       | 95                                  |

| 14 Ld SOIC Package                                                        | 120                                 |

| 16 Ld QSOP Package                                                        | 140                                 |

| Maximum Junction Temperature (Die)                                        | +175°C                              |

| Maximum Junction Temperature (Plastic Package)                            | +150°C                              |

| Maximum Storage Temperature Range65°                                      | C to +150°C                         |

| Pb-free reflow profilese http://www.intersil.com/pbfree/Pb-FreeReflow.asp | e link below                        |

| *Pb-free PDIPs can be used for through hole v                             | vave solder                         |

processing only. They are not intended for use in Reflow solder processing applications.

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 1. θ<sub>JA</sub> is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 2. If an input signal is applied before the supplies are powered up, the input current must be limited to these maximum values.

**Electrical Specifications**  $V_{SUPPLY} = \pm 5V$ ,  $R_L = 10k\Omega$ ,  $V_{\overline{CS}} = 0.8V$ , Unless Otherwise Specified.

| PARAMETER                               | TEST CONDITIONS                                | TEMP. (°C) | MIN<br>(Note 4) | TYP    | MAX<br>(Note 4) | UNITS |

|-----------------------------------------|------------------------------------------------|------------|-----------------|--------|-----------------|-------|

| DC SUPPLY CHARACTERISTICS               | •                                              | II.        | ı.              |        | II.             | Į.    |

| Supply Voltage                          |                                                | Full       | ±4.5            | ±5.0   | ±5.5            | V     |

| Supply Current (V <sub>OUT</sub> = 0V)  | V <del>CS</del> = 0.8V                         | 25, 70     | -               | 10.5   | 13              | mA    |

|                                         | V <del>CS</del> = 0.8V                         | 0          | -               | -      | 15.5            | mA    |

|                                         | V <del>CS</del> = 2.0V                         | 25, 70     | -               | 400    | 450             | μA    |

|                                         | V <del>CS</del> = 2.0V                         | 0          | -               | 400    | 580             | μA    |

| ANALOG DC CHARACTERISTICS               |                                                | 1          | 1               |        | 1               | l     |

| Output Voltage Swing without Clipping   | $V_{OUT} = V_{IN} \pm V_{IO} \pm 20 \text{mV}$ | 25, 70     | ±2.7            | ±2.8   | -               | V     |

|                                         |                                                | 0          | ±2.4            | ±2.5   | -               | V     |

| Output Current                          |                                                | Full       | 15              | 20     | -               | mA    |

| Input Bias Current                      |                                                | Full       | -               | 30     | 50              | μA    |

| Output Offset Voltage                   |                                                | Full       | -10             | -      | 10              | mV    |

| Output Offset Voltage Drift (Note 3)    |                                                | Full       | -               | 25     | 50              | μV/°C |

| SWITCHING CHARACTERISTICS               |                                                | 1          | 1               |        | 1               | I     |

| Turn-On Time                            |                                                | 25         | -               | 160    | -               | ns    |

| Turn-Off Time                           |                                                | 25         | -               | 320    | -               | ns    |

| Output Glitch During Switching          |                                                | 25         | -               | ±10    | -               | mV    |

| DIGITAL DC CHARACTERISTICS              |                                                | 1          | 1               |        | 1               | I     |

| Input Logic High Voltage                |                                                | Full       | 2               | -      | -               | V     |

| Input Logic Low Voltage                 |                                                | Full       | -               | -      | 0.8             | V     |

| Input Current                           | 0V to 4V                                       | Full       | -2              | -      | 2               | μA    |

| AC CHARACTERISTICS                      |                                                | 1          |                 |        | 1               | l .   |

| Insertion Loss                          | 1V <sub>P-P</sub>                              | 25         | -               | 0.055  | 0.063           | dB    |

|                                         |                                                | Full       | -               | 0.07   | 0.08            | dB    |

| Channel-to-Channel Insertion Loss Match |                                                | Full       | -               | ±0.004 | ±0.006          | dB    |

3

**Electrical Specifications**  $V_{SUPPLY} = \pm 5V$ ,  $R_L = 10k\Omega$ ,  $V_{\overline{CS}} = 0.8V$ , Unless Otherwise Specified. (Continued)

| PARAMETER                                 | TEST CONDITIONS                                                    | TEMP. (°C) | MIN<br>(Note 4) | TYP       | MAX<br>(Note 4) | UNITS |

|-------------------------------------------|--------------------------------------------------------------------|------------|-----------------|-----------|-----------------|-------|

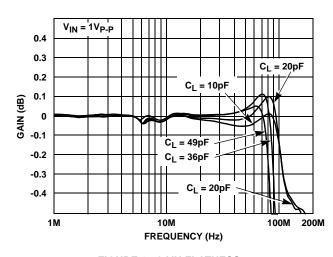

| -3dB Bandwidth                            | $R_S = 50\Omega$ , $C_L = 10pF$                                    | 25         | =               | 400       | =               | MHz   |

|                                           | $R_S = 20\Omega$ , $C_L = 20pF$                                    | 25         | =               | 280       | =               | MHz   |

|                                           | $R_S = 16\Omega$ , $C_L = 36pF$                                    | 25         | -               | 140       | =               | MHz   |

|                                           | $R_S = 13\Omega$ , $C_L = 49pF$                                    | 25         | =               | 110       | =               | MHz   |

| ±0.1dB Flat Bandwidth                     | $R_S = 50\Omega$ , $C_L = 10pF$                                    | 25         | =               | 100       | =               | MHz   |

|                                           | $R_S = 20\Omega$ , $C_L = 20pF$                                    | 25         | -               | 100       | =               | MHz   |

|                                           | $R_S = 16\Omega$ , $C_L = 36pF$                                    | 25         | =               | 85        | =               | MHz   |

|                                           | $R_S = 13\Omega$ , $C_L = 49pF$                                    | 25         | -               | 75        | =               | MHz   |

| Input Resistance                          |                                                                    | Full       | 200             | 400       | =               | kΩ    |

| Input Capacitance                         |                                                                    | Full       | =               | 1.5       | =               | pF    |

| Enabled Output Resistance                 |                                                                    | Full       | -               | 15        | =               | Ω     |

| Disabled Output Capacitance               | V <del>CS</del> = 2.0V                                             | Full       | -               | 2.5       | =               | pF    |

| Differential Gain                         | 4.43MHz, (Note 3)                                                  | 25         | =               | 0.01      | 0.02            | %     |

| Differential Phase                        | 4.43MHz, (Note 3)                                                  | 25         | -               | 0.01      | 0.02            | 0     |

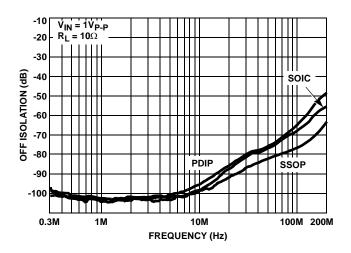

| Off Isolation                             | $1V_{P-P}$ , 100MHz, $V_{\overline{CS}} = 2.0V$ , $R_L = 10\Omega$ | Full       | -               | 70        | -               | dB    |

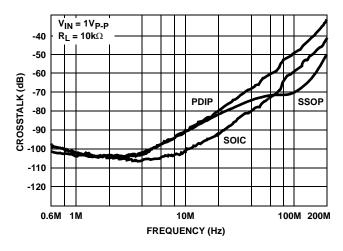

| Crosstalk Rejection                       | 1V <sub>P-P</sub> , 30MHz                                          | Full       | -               | 80        | =               | dB    |

| Slew Rate (1.5V <sub>P-P</sub> , +SR/-SR) | $R_S = 50\Omega$ , $C_L = 10pF$                                    | 25         | -               | 1425/1450 | =               | V/µs  |

|                                           | $R_S = 20\Omega$ , $C_L = 20pF$                                    | 25         | -               | 1010/1010 | =               | V/µs  |

|                                           | $R_S = 16\Omega$ , $C_L = 36pF$                                    | 25         | -               | 725/750   | =               | V/µs  |

|                                           | $R_S = 13\Omega, C_L = 49pF$                                       | 25         | -               | 600/650   | -               | V/µs  |

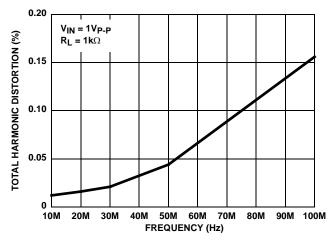

| Total Harmonic Distortion                 | 10MHz, $R_L = 1$ kΩ, (Note 3)                                      | Full       | -               | 0.01      | 0.1             | %     |

| Disabled Output Resistance                | V <del>CS</del> = 2.0V                                             | Full       | -               | 12        | =               | ΜΩ    |

#### NOTES:

- 3. Limits should be considered typical and are not production tested.

- 4. Parts are 100% tested at +25°C. Over-temperature limits established by characterization and are not production tested.

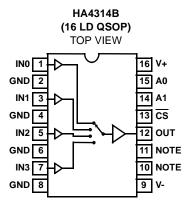

## **AC Test Circuit**

NOTE:  $C_L = C_X + Test Fixture Capacitance$ .

#### PC Board Layout

The frequency response of this circuit depends greatly on the care taken in designing the PC board. The use of low inductance components such as chip resistors and chip capacitors is strongly recommended, while a solid ground plane is a must!

Attention should be given to decoupling the power supplies. A large value ( $10\mu F$ ) tantalum in parallel with a small value ( $0.1\mu F$ ) chip capacitor works well in most cases.

Keep input and output traces as short as possible, because trace inductance and capacitance can easily become the performance limiting items.

## Application Information

#### General

The HA4314B is a 4x1 crosspoint switch that is ideal for the matrix element of high performance switchers and routers. This crosspoint's low input capacitance and high input resistance provide excellent video terminations when used with an external  $75\Omega$  resistor. Nevertheless, if several HA4314B inputs are connected together, the use of an input buffer should be considered (see Figure 1). This crosspoint contains no feedback or gain setting resistors, so the output is a true high impedance load when the IC is disabled  $(\overline{CS} = 1)$ .

#### **Ground Connections**

All GND pins are connected to a common point on the die, so any one of them will suffice as the functional GND connection. For the best isolation and crosstalk rejection, however, all GND pins must connect to the GND plane.

#### Frequency Response

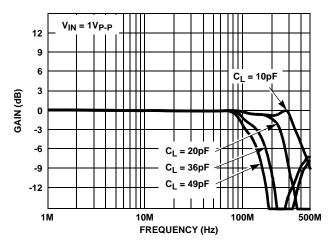

Most applications utilizing the HA4314B require a series output resistor,  $R_{S}$ , to tune the response for the specific load capacitance,  $C_{L}$ , driven. Bandwidth and slew rate degrade as  $C_{L}$  increases (as shown in the "Electrical Specifications" on page 4), so give careful consideration to component placement to minimize trace length. In big matrix configurations where  $C_{L}$  is large, better frequency response is obtained by cascading two levels of crosspoints in the case of multiplexed outputs (see Figure 2), or distributing the load between two drivers if  $C_{L}$  is due to bussing and subsequent stage input capacitance.

#### **Control Signals**

$\overline{\text{CS}}$  - This is a TTL/CMOS compatible, active low Chip Select input. When driven high,  $\overline{\text{CS}}$  forces the output to a true high impedance state and reduces the power dissipation by a factor of 25. The  $\overline{\text{CS}}$  input has no on-chip pull-down resistor, so it must be connected to a logic low (recommend GND) if the enable function isn't utilized.

A0, A1 - These are binary coded, TTL/CMOS compatible address inputs that select which one of the four inputs connect to the crosspoint output.

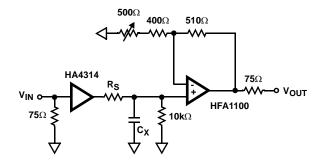

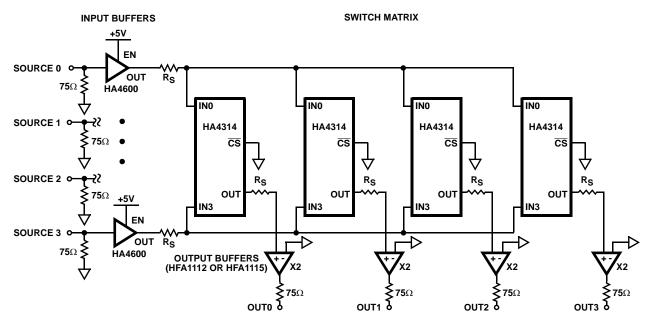

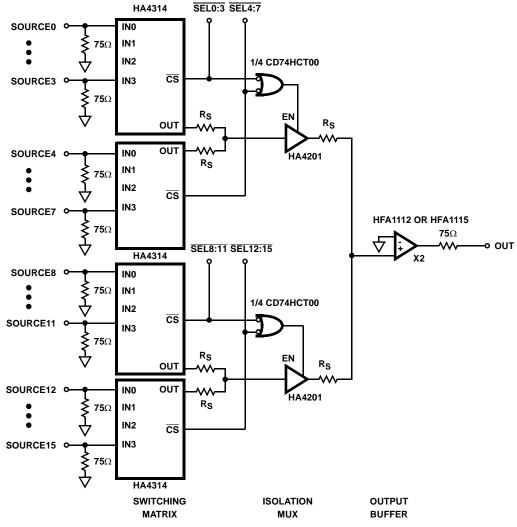

#### Switcher/Router Applications

Figure 1 illustrates one possible implementation of a wideband, low power, 4x4 switcher/router utilizing the HA4314B for the switch matrix. A 4x4 switcher/router allows any of the four outputs to be driven by any one of the four inputs (e.g., each of the four inputs may connect to a different output, or an input may connect to multiple outputs). This application utilizes the HA4600 (video buffer with output disable) for the input buffer, the HA4314B as the switch matrix, and the HFA1112 (programmable gain buffer) as the gain of two output driver. Figure 2 details a 16x1 switcher (basically a 16:1 mux) which uses the HA4201 (1x1 crosspoint) and the HA4314B in a cascaded stage configuration to minimize capacitive loading at each output node, thus increasing system bandwidth.

#### Power-Up Considerations

No signals should be applied to the analog or digital inputs before the power supplies are activated. Latch-up may occur if the inputs are driven at the time of power-up. To prevent latch-up, the input currents during power-up must not exceed the values listed in the "Absolute Maximum Ratings" on page 3.

#### Intersil's Crosspoint Family

Intersil offers a variety of 4x1 and 1x1 crosspoint switches. In addition to the HA4314B, the 4x1 family includes the HA4404 and HA4344. The HA4404 is a 16 Ld device with Tally outputs to indicate the selected channel. The HA4344 is a 16 Ld crosspoint with synchronized control lines (A0, A1,  $\overline{\text{CS}}$ ). With synchronization, the control information for the next channel switch can be loaded into the crosspoint without affecting the current state. On a subsequent clock edge the stored control state effects the desired channel switch.

The 1x1 family is comprised of the HA4201 and HA4600. They are essentially similar devices, but the HA4201 includes a Tally output (enable indicator). The 1x1s are useful as high performance video input buffers, or in a switch matrix requiring very high off isolation.

FN3679.12 September 11, 2007

FIGURE 1. 4x4 SWITCHER/ROUTER APPLICATION

FIGURE 2. 16x1 SWITCHER APPLICATION

## **Typical Performance Curves** $V_{SUPPLY} = \pm 5V$ , $T_A = +25^{\circ}C$ , $R_L = 10k\Omega$ , Unless Otherwise Specified

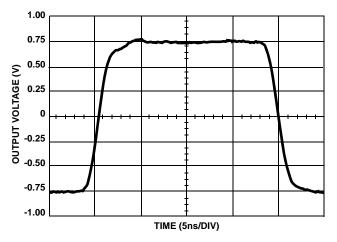

FIGURE 3. LARGE SIGNAL PULSE RESPONSE

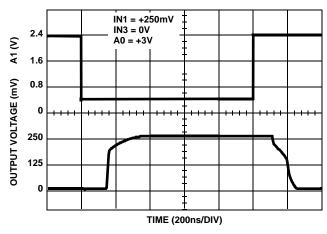

FIGURE 4. CHANNEL-TO-CHANNEL SWITCHING RESPONSE

FIGURE 5. FREQUENCY RESPONSE

FIGURE 6. GAIN FLATNESS

FIGURE 7. ALL HOSTILE CROSSTALK REJECTION

FIGURE 8. ALL HOSTILE OFF ISOLATION

# $\textbf{\textit{Typical Performance Curves}} \quad V_{SUPPLY} = \pm 5 \text{V}, \ T_{A} = +25 ^{\circ}\text{C}, \ R_{L} = 10 \text{k}\Omega, \ \text{Unless Otherwise Specified} \quad \text{\textbf{(Continued)}}$

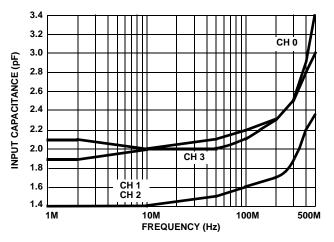

FIGURE 10. INPUT CAPACITANCE vs FREQUENCY

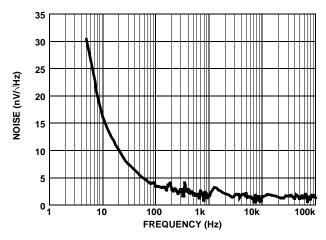

FIGURE 11. NOISE vs FREQUENCY

## Die Characteristics

#### **DIE DIMENSIONS:**

65 milsx118 milsx19 mils  $1640 \mu \text{mx}3000 \mu \text{mx}483 \mu \text{m}$

#### **METALLIZATION:**

Type: Metal 1: AlCu (1%)/TiW Thickness: Metal 1:  $6k\mathring{A} \pm 0.8k\mathring{A}$

Type: Metal 2: AlCu (1%)

Thickness: Metal 2: 16kÅ ±1.1kÅ

#### **PASSIVATION:**

Type: Nitride

Thickness: 4kÅ ±0.5kÅ

#### TRANSISTOR COUNT:

200

#### SUBSTRATE POTENTIAL (POWERED UP):

V-

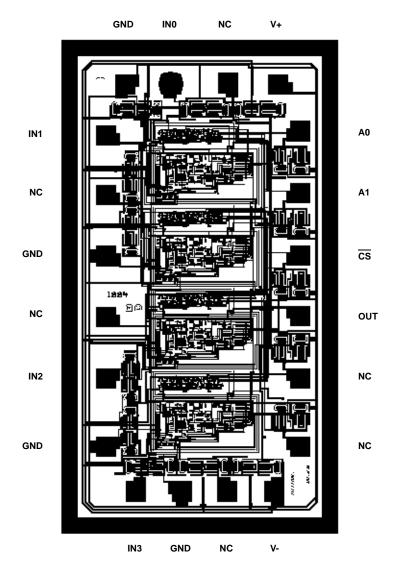

## Metallization Mask Layout

#### HA4314B

<u>intersil</u>

FN3679.12 September 11, 2007

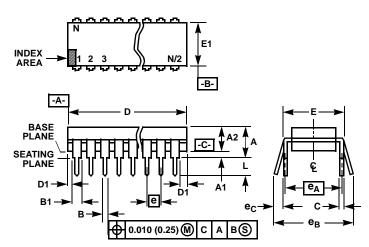

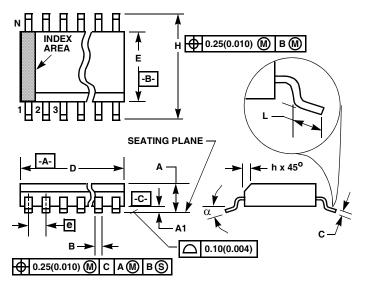

## Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- 1. Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- 6. E and eal are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

E14.3 (JEDEC MS-001-AA ISSUE D)

14 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INC   | HES   | MILLIMETERS |       |       |

|----------------|-------|-------|-------------|-------|-------|

| SYMBOL         | MIN   | MAX   | MIN         | MAX   | NOTES |

| Α              | -     | 0.210 | -           | 5.33  | 4     |

| A1             | 0.015 | -     | 0.39        | -     | 4     |

| A2             | 0.115 | 0.195 | 2.93        | 4.95  | -     |

| В              | 0.014 | 0.022 | 0.356       | 0.558 | -     |

| B1             | 0.045 | 0.070 | 1.15        | 1.77  | 8     |

| С              | 0.008 | 0.014 | 0.204       | 0.355 | -     |

| D              | 0.735 | 0.775 | 18.66       | 19.68 | 5     |

| D1             | 0.005 | -     | 0.13        | -     | 5     |

| Е              | 0.300 | 0.325 | 7.62        | 8.25  | 6     |

| E1             | 0.240 | 0.280 | 6.10        | 7.11  | 5     |

| е              | 0.100 | BSC   | 2.54        | BSC   | -     |

| e <sub>A</sub> | 0.300 | BSC   | 7.62 BSC    |       | 6     |

| e <sub>B</sub> | -     | 0.430 | -           | 10.92 | 7     |

| L              | 0.115 | 0.150 | 2.93        | 3.81  | 4     |

| N              | 1     | 4     | 14          |       | 9     |

Rev. 0 12/93

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 4. Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M14.15 (JEDEC MS-012-AB ISSUE C)

14 LEAD NARROW BODY SMALL OUTLINE PLASTIC

PACKAGE

|        | INC    | INCHES    |      | MILLIMETERS |   |

|--------|--------|-----------|------|-------------|---|

| SYMBOL | MIN    | MAX       | MIN  | MIN MAX     |   |

| Α      | 0.0532 | 0.0688    | 1.35 | 1.75        | - |

| A1     | 0.0040 | 0.0098    | 0.10 | 0.25        | - |

| В      | 0.013  | 0.020     | 0.33 | 0.51        | 9 |

| С      | 0.0075 | 0.0098    | 0.19 | 0.25        | - |

| D      | 0.3367 | 0.3444    | 8.55 | 8.75        | 3 |

| Е      | 0.1497 | 0.1574    | 3.80 | 4.00        | 4 |

| е      | 0.050  | 0.050 BSC |      | BSC         | - |

| Н      | 0.2284 | 0.2440    | 5.80 | 6.20        | - |

| h      | 0.0099 | 0.0196    | 0.25 | 0.50        | 5 |

| L      | 0.016  | 0.050     | 0.40 | 1.27        | 6 |

| N      | 1      | 4         | 14   |             | 7 |

| α      | 0°     | 8º        | 0°   | 8°          | - |

Rev. 0 12/93

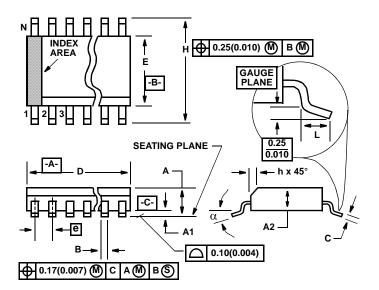

## Shrink Small Outline Plastic Packages (SSOP) Quarter Size Outline Plastic Packages (QSOP)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- Dimension "B" does not include dambar protrusion. Allowable dambar protrusion shall be 0.10mm (0.004 inch) total in excess of "B" dimension at maximum material condition.

- Controlling dimension: INCHES. Converted millimeter dimensions are not necessarily exact.

M16.15A

16 LEAD SHRINK SMALL OUTLINE PLASTIC PACKAGE

(0.150" WIDE BODY)

|        | INC    | HES    | MILLIN |       |       |

|--------|--------|--------|--------|-------|-------|

| SYMBOL | MIN    | MAX    | MIN    | MAX   | NOTES |

| Α      | 0.061  | 0.068  | 1.55   | 1.73  | -     |

| A1     | 0.004  | 0.0098 | 0.102  | 0.249 | -     |

| A2     | 0.055  | 0.061  | 1.40   | 1.55  | -     |

| В      | 0.008  | 0.012  | 0.20   | 0.31  | 9     |

| С      | 0.0075 | 0.0098 | 0.191  | 0.249 | -     |

| D      | 0.189  | 0.196  | 4.80   | 4.98  | 3     |

| Е      | 0.150  | 0.157  | 3.81   | 3.99  | 4     |

| е      | 0.025  | BSC    | 0.635  | BSC   | -     |

| Н      | 0.230  | 0.244  | 5.84   | 6.20  | -     |

| h      | 0.010  | 0.016  | 0.25   | 0.41  | 5     |

| L      | 0.016  | 0.035  | 0.41   | 0.89  | 6     |

| Ν      | 1      | 6      | 16     |       | 7     |

| α      | 0°     | 8°     | 0°     | 8°    | -     |

Rev. 2 6/04

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

# AMEYA360 Components Supply Platform

## **Authorized Distribution Brand:**

## Website:

Welcome to visit www.ameya360.com

## Contact Us:

## > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

## > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

## Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com