# AMIS-492x0 Fieldbus MAU

# Overview

AMIS-492x0 Fieldbus MAU (<u>Media Access Unit</u>) is a transceiver chip for low speed FOUNDATION<sup>®</sup> Fieldbus and Profibus PA devices. The AMIS-49200 was originally designed to be a near pin-for-pin replacement of the Yokogawa  $\mu$ SAA22Q MAU. "Near pin-for-pin" means that associated component values may change, but no board changes are required. A micro-leadframe package option (NQFP) is also available, the AMIS-49250.

### Features

AMIS-492x0 Fieldbus MAU is a transceiver IC for low speed FOUNDATION Fieldbus and Profibus PA devices. It incorporates the following features:

- All Node Power can be Supplied by the Bus, via the AMIS-492x0

- Current Consumption 500 µA (Typ)

- VCC Voltage: 6.2 V to 4.75 V

- VDD Voltage: 5.5 V to 2.7 V

- Compatible to IEC 1158-2 and ISA 50.02

- Shunt Regulator

- Voltage Reference (Internal Only)

- Series Regulator

- Band-pass Filter

- Slew Rate Control

- Segment Current Control

- Low Voltage Detection

- Carrier Detect

- Data Rate: 31.25 kbps Voltage Mode

- Dual Voltage Supply 3-6.2 V

- 44-pin LQFP/NQFP Package

- These Devices are Pb-Free and are RoHS Compliant

### Applications

- Process Automation

- Pressure and Temperature Monitoring

### **Definitions, Acronyms and Abbreviations**

|            | •                                                    |

|------------|------------------------------------------------------|

| IC         | – Integrated Circuit                                 |

| ESD        | – Electrostatic Discharge                            |

| FF         | <ul> <li>FOUNDATION Fieldbus</li> </ul>              |

| LQFP       | <ul> <li>Low Profile Quad Flat Pack</li> </ul>       |

| Manchester | - Communications Encoding Scheme Implemented in      |

|            | FOUNDATION Fieldbus                                  |

| MAU        | – Medium Attachment Unit                             |

| MDS        | <ul> <li>Medium Dependent Sub-layer</li> </ul>       |

| NQFP       | <ul> <li>"Near Chip-scale" Quad Flat Pack</li> </ul> |

| µSAA22Q    | <ul> <li>Name of Yokogawa's MAU IC</li> </ul>        |

# **ON Semiconductor®**

http://onsemi.com

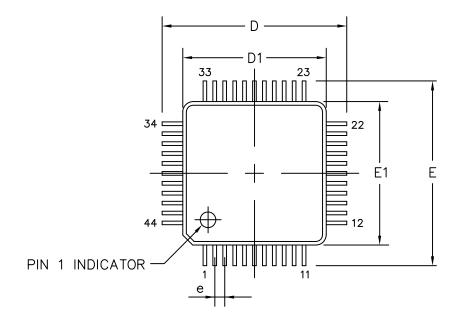

LQFP-44, 10x10 CASE 561AA

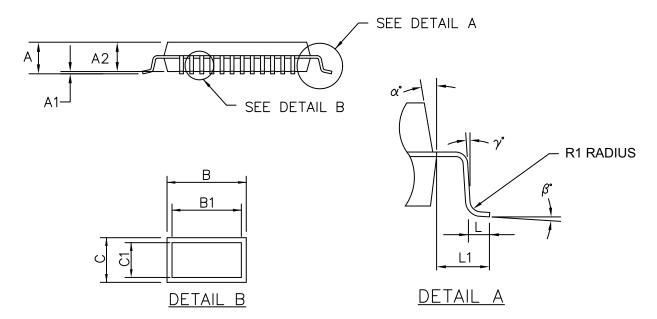

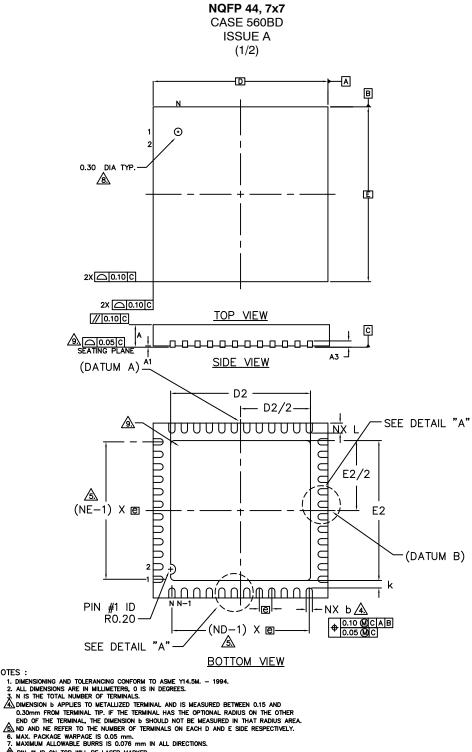

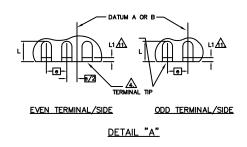

NQFP 44, 7x7 CASE 560BD

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 15 of this data sheet.

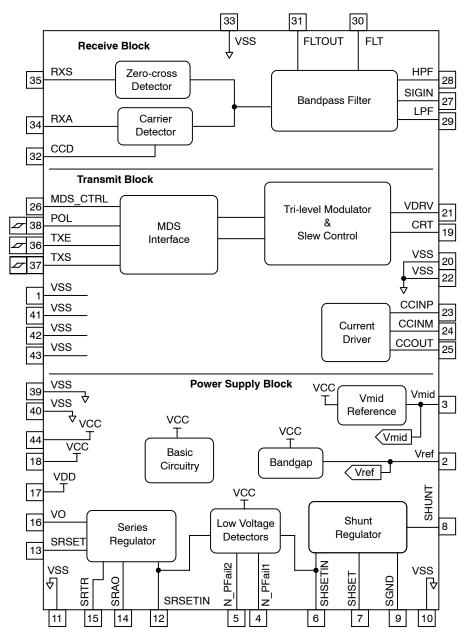

#### **Block Diagram**

#### Table 1. PIN NUMBERS AND SIGNAL DESCRIPTION

| Signal<br>Name | Pin<br>No. | <b>I/O</b><br>(Note 1) | Description                                                                                      |

|----------------|------------|------------------------|--------------------------------------------------------------------------------------------------|

| VSS            | 1          | Ground                 | Connect to Ground.                                                                               |

| VREF           | 2          | AO                     | Internal bandgap voltage (1.18 V).                                                               |

| VMID           | 3          | AO                     | 2 V bias voltage for AC signals.                                                                 |

| N_PFAIL1       | 4          | AI/O                   | Power fail alarm at VCC input. This pin is an open-drain output of negative logic.               |

| N_PFAIL2       | 5          | AI/O                   | Power fail alarm at VDD input. This pin is an open-drain output of negative logic.               |

| SHSETIN        | 6          | AI                     | Feedback (non-inverting) input for the shunt regulator.                                          |

| SHSET          | 7          | AO                     | Divided voltage of VCC input. Feeding this voltage to SHSETIN pin results in 5 V voltage at VCC. |

1. AI = Analog Input, AO = Analog Output, AI/O = Analog Input/Output, DIS = CMOS Digital Input (Schmitt Trigger), DO = CMOS Digital Output.

# AMIS-492x0

| Table 1. PIN NUMBERS AND SIGNAL | <b>DESCRIPTION</b> (continued) |  |

|---------------------------------|--------------------------------|--|

|---------------------------------|--------------------------------|--|

| Signal<br>Name | Pin<br>No. | I/O<br>(Note 1) | Description                                                                                                                                                                                                      |

|----------------|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SHUNT          | 8          | AI              | Control pin of the shunt regulator. Its sink current (25 mA max) is controlled so that the voltage at SHSETIN is equal to $V_{REF}$ (1.18 V).                                                                    |

| VSS/SGND       | 9          | Ground          | The Current absorbed by SHUNT pin (25 mA max) is fed to this pin, which must be connected to the ground level.                                                                                                   |

| VSS            | 10         | Ground          | Ground                                                                                                                                                                                                           |

| VSS            | 11         | Ground          | Ground                                                                                                                                                                                                           |

| SRSETIN        | 12         | AI              | Feedback (inverting) input for the series regulator. The series regulator controls its output (SRAO) to make this input voltage is equal to V <sub>REF</sub> (1.18 V).                                           |

| SRSET          | 13         | AO              | Divided voltage of VO output. Feeding this voltage into SRSETIN pin results in 3 V at VO pin.                                                                                                                    |

| SRAO           | 14         | AO              | Output pin of an operational amplifier for the series regulator.                                                                                                                                                 |

| SRTR           | 15         | AI              | Gate of a PMOS transistor for the series regulator.                                                                                                                                                              |

| VO             | 16         | AO              | Output pin of the series regulator (20 mA max).                                                                                                                                                                  |

| VDD            | 17         | Digital Supply  | Supply voltage input for digital block.                                                                                                                                                                          |

| VCC            | 18         | Analog Supply   | Analog supply voltage.                                                                                                                                                                                           |

| CRT            | 19         | AI/O            | Current integration to limit output slew rate.                                                                                                                                                                   |

| VSS            | 20         | Ground          | Ground                                                                                                                                                                                                           |

| VDRV           | 21         | AO              | Output of an operational amplifier for slew rate control. This signal can be fed to current driver.                                                                                                              |

| VSS            | 22         | Ground          | Ground                                                                                                                                                                                                           |

| CCINP          | 23         | AI              | Non-inverting input of an operational amplifier for transmission current driver.                                                                                                                                 |

| CCINM          | 24         | AI              | Inverting input of an operational amplifier for transmission current driver.                                                                                                                                     |

| CCOUT          | 25         | AO              | Output of an operational amplifier for transmission current driver.                                                                                                                                              |

| MDS_CTRL       | 26         | AI              | For POL = VDD MDS_CTRL should = VSS<br>For POL = VSS MDS_CTRL can be tied to VDD or used as a not reset to control when transmit<br>communications will be enabled.                                              |

| SIGIN          | 27         | AI              | Input pin of the band-pass filter. This pin si connected to VMID bias level with 270 k $\Omega$ resistor.                                                                                                        |

| HPF            | 28         | AI              | Feedback signal of high-pass filter. This pin si connected to the output of an op-amp for high pass filter with 75 k $\Omega$ resistor.                                                                          |

| LPF            | 29         | AI              | Non-inverting input of an operational amplifier for the low-pass filter.                                                                                                                                         |

| FLT            | 30         | AI              | Input pin of low-pass filter for feedback. This pin is connected to the output of the high-pass filter through 20 k $\Omega$ and the non-inverting input of the low-pass filter through 54 k $\Omega$ resisters. |

| FLTOUT         | 31         | AO              | Output of the operational amplifier for the low-pass filter. This signal is internally connected to non-inverting input to form a voltage-follower.                                                              |

| CCD            | 32         | AO              | Current integration (for carrier detect circuit).                                                                                                                                                                |

| VSS            | 33         | Ground          | Ground                                                                                                                                                                                                           |

| RXA            | 34         | DO              | MDS-MAU interface signal for received signal activity. This pin is a push-pull output.                                                                                                                           |

| RXS            | 35         | DO              | MDS-MAU interface signal for received signal. This pin si a push-pull output.                                                                                                                                    |

| TXE            | 36         | DIS             | MDS-MAU interface signal for enable signal transmission (Schmitt Trigger input).                                                                                                                                 |

| TXS            | 37         | DIS             | MDS-MAU interface signal for signal to be transmitted (Schmitt Trigger input).                                                                                                                                   |

| POL            | 38         | DIS             | Selects polarity of TxE input. When this pin is connected to GND, TxE is active high. When this pin is connected to VDD, TxE is active low.                                                                      |

| VSS            | 39         | Ground          | Ground                                                                                                                                                                                                           |

| VSS            | 40         | Ground          | Ground                                                                                                                                                                                                           |

| VSS            | 41         | Ground          | Connect to ground.                                                                                                                                                                                               |

| VSS            | 42         | Ground          | Connect to ground.                                                                                                                                                                                               |

| VSS            | 43         | Ground          | Connect to ground.                                                                                                                                                                                               |

| VCC            | 44         | Analog Supply   | Analog supply voltage.                                                                                                                                                                                           |

1. AI = Analog Input, AO = Analog Output, AI/O = Analog Input/Output, DIS = CMOS Digital Input (Schmitt Trigger), DO = CMOS Digital Output.

# AMIS-492x0

# **ELECTRICAL CHARACTERISTICS**

# **Operating Conditions**

Unless otherwise noted, all block and sub-block specifications apply over the operating temperature (-40 to +85°C).

| Parameter                    | Symbol               | Conditions              | Min  | Max                   | Unit |

|------------------------------|----------------------|-------------------------|------|-----------------------|------|

| Analog Block Supply Voltage  | V <sub>CC</sub>      |                         | -0.3 | 6.5                   | V    |

| Digital Block Supply Voltage | V <sub>DD</sub>      |                         | -0.3 | 6.0                   | V    |

| Digital Input Pin Voltage    | V <sub>IN</sub>      | (TxS, TxE and POL Pins) | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| Digital Output Pin Voltage   | V <sub>OUT</sub>     | (RxS and RxA Pins)      | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| Input Pin Current            | I <sub>IN</sub>      | Not for Shunt Pin       | -    | ±5                    | mA   |

| Output Pin Current           | I <sub>OUT</sub>     | For Shunt, SGND and VO  | -    | 30                    | mA   |

| ESD, Human Body Model        |                      |                         | -    | 2,250                 | V    |

| ESD, Machine Model           |                      |                         | -    | 250                   | V    |

| ESD, Charged Device Model    |                      |                         | -    | 1,000                 | V    |

| Storage Temperature          | T <sub>Storage</sub> |                         | -55  | 125                   | °C   |

# Table 2. ABSOLUTE MAXIMUM RATINGS

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

# Table 3. NORMAL OPERATING CONDITIONS

| Parameter              | Symbol                 | Conditions                                                       | Min  | Тур | Max       | Unit |

|------------------------|------------------------|------------------------------------------------------------------|------|-----|-----------|------|

| Analog Supply Voltage  | VCC                    | Supply voltages are configurable,                                | 4.75 | 5   | 6.2       | V    |

| Digital Supply Voltage | VDD                    | or can be supplied from off-chip.                                | 2.7  | 3   | VCC - 1.1 | V    |

| Storage Temperature    | T <sub>Operating</sub> |                                                                  | -40  | -   | 85        | °C   |

| Current Consumption    | ICC                    | 25°C, SHUNT current = 1 mA,<br>no current from series regulator. | -    | 500 | 800       | μΑ   |

### Table 4. CMOS INPUT SPECIFICATIONS

| Parameter                  | Symbol          | Min                 | Max                 | Unit |

|----------------------------|-----------------|---------------------|---------------------|------|

| Input High Voltage         | VIH             | $0.7 \times V_{DD}$ | V <sub>DD</sub>     | V    |

| Input Low Voltage          | VIL             | 0                   | $0.3 \times V_{DD}$ | V    |

| Input High Current         | I <sub>IH</sub> | -                   | 1                   | μA   |

| Input Low Current          | IIL             | -                   | -1                  | μA   |

| Schmitt Negative Threshold | V <sub>t-</sub> | $0.2 \times V_{DD}$ | -                   | V    |

| Schmitt Positive Threshold | V <sub>t+</sub> | -                   | $0.8 \times V_{DD}$ | V    |

| Schmitt Hysteresis         | V <sub>h</sub>  | 1                   | -                   | V    |

# **Power Supply Blocks**

# **Table 5. REGULATOR SPECIFICATIONS**

| Parameter                         | Parameter Symbol Conditions |                                                                    | Min   | Тур   | Max   | Unit   |

|-----------------------------------|-----------------------------|--------------------------------------------------------------------|-------|-------|-------|--------|

| Shunt Regulator                   | ·                           |                                                                    | •     | •     |       |        |

| Output Voltage                    | V <sub>CC</sub>             | Preset, I <sub>SH</sub> = 1 to 5 mA                                | 4.85  | 5.0   | 5.15  | V      |

|                                   |                             | External Setting                                                   | 4.75  | -     | 6.2   | V      |

| Sink Current                      | I <sub>SH</sub>             | Internal Pass Transistor N-ch and Pad                              | 0.001 | -     | 25    | mA     |

| Load Capacitance                  | C <sub>SH</sub>             |                                                                    | 5     | -     | -     | μF     |

| Load Regulation                   |                             | I <sub>SH</sub> = 1 to 25 mA                                       | 0     | 1.6   | 4     | %      |

| Temperature Coefficient           | TC <sub>Vcc</sub>           | No Load Capacitance                                                | _     | -     | ±200  | ppm/°C |

| Series Regulator                  |                             |                                                                    |       |       |       |        |

| Input Voltage                     | V <sub>CC</sub>             | Internally Tied to V <sub>CC</sub> Pin                             | 4.75  | -     | 6.2   | V      |

| Output Voltage                    | Vo                          | Preset, I <sub>SR</sub> = 0                                        |       | 3.0   | 3.09  | V      |

|                                   |                             | External Setting and N-JFET                                        | 2.85  | -     | 3.5   | V      |

| Output Current                    | I <sub>SR</sub>             | Internal Pass Transistor P-ch and Pad                              | -     | -     | 20    | mA     |

| Load Capacitance                  | C <sub>SR</sub>             | For Stability use CAP w/ESR                                        | 5     | -     | -     | μF     |

| Load Regulation                   |                             | I <sub>SR</sub> = 0 to 20 mA                                       | 0     | 2     | 4     | %      |

| Temperature Coefficient           | TC <sub>Vo</sub>            |                                                                    | _     | ±200  | -     | ppm/°C |

| Low Voltage Detectors (Applies to | N_PFail1 and PFai           | 12)                                                                | •     | •     |       |        |

| Threshold                         | V <sub>TH9</sub>            | SxSETIN > $V_{TH9}$ (Output: L $\rightarrow$ H)                    | 85    | 90    | 95    | % Vref |

| Hysteresis                        | V <sub>HYS5</sub>           | SxSETIN < ( $V_{TH9} - V_{HYS5}$ )<br>(Output: $H \rightarrow L$ ) | 0.012 | 0.025 | 0.038 | V      |

| Output Sink Current               | I <sub>OL</sub>             | V <sub>OL</sub> = 0.4 V (Open Drain)                               | 30    | -     | 135   | μΑ     |

| Output Leakage Current            | ١L                          | V <sub>OH</sub> = 5 V                                              | -     | -     | 1     | μΑ     |

# Table 6. VOLTAGE REFERENCE SPECIFICATIONS

| Parameter                          | Symbol              | Conditions               | Min   | Тур   | Max   | Unit   |

|------------------------------------|---------------------|--------------------------|-------|-------|-------|--------|

| Bandgap Voltage Reference          | •                   | ·                        | -     |       |       |        |

| Output Voltage Tolerance           | V <sub>REF</sub>    | Equates to: ±2%          | 1.157 | 1.185 | 1.205 | V      |

| Temperature Drift                  |                     |                          | -     | 50    | -     | ppm/°C |

| Hysteresis                         | V <sub>REFHYS</sub> | (Note 2)                 | -     | 100   | -     | μV     |

| Supply Voltage                     | V <sub>CCREF</sub>  |                          | 4.75  | 5     | 6.2   | V      |

| Load Current                       | IREFOUT             | No Load During Operation | -     | -     | 0     | μA     |

| V <sub>MID</sub> Voltage Reference |                     |                          |       |       |       |        |

| Output Voltage                     | V <sub>MID</sub>    |                          | 1.95  | 2.0   | 2.05  | V      |

| Output Current                     | I <sub>MID</sub>    |                          | -30   | -     | 100   | μΑ     |

| Load Capacitance                   | C <sub>MID</sub>    | DVC6000F Uses 1 µF       | 0.01  | 0.1   | 1     | μF     |

| Temperature Coefficient            | TC <sub>MID</sub>   |                          | -     | -     | ±200  | ppm/°C |

Iemperature Coefficient

IC<sub>MID</sub>

–

2. Hysteresis is defined as the change in the 25°C reading after 85°C to 25°C cycle and –40°C to 25°C cycle.

# **Transmitter Blocks**

# Table 7. MDS-MAU INTERFACE

| Parameter     | Symbol | Min                             | Тур | Max | Unit |

|---------------|--------|---------------------------------|-----|-----|------|

| POL Input Pin | POL    | See Schmitt Trigger Input Specs |     |     | V    |

| TxE Input Pin | TxE    | See Schmitt Trigger Input Specs |     |     | V    |

| TxS input Pin | TxS    | See Schmitt Trigger Input Specs |     | V   |      |

NOTE: The associated MDS chip must handle the jabber detect function.

#### **Table 8. TRI-LEVEL MODULATOR**

| Parameter                                                | Symbol          | Conditions                       | Min                      | Тур                      | Max                      | Unit |  |  |  |

|----------------------------------------------------------|-----------------|----------------------------------|--------------------------|--------------------------|--------------------------|------|--|--|--|

| Tri-level Modulator and Slew Control (Output is at VDRV) |                 |                                  |                          |                          |                          |      |  |  |  |

| Output Voltage                                           | Vo              |                                  | V <sub>MID</sub>         | -                        | 3.02                     | V    |  |  |  |

| Load Current                                             | Ι <sub>Ο</sub>  | ΔV  10 mV                        | -35                      | -                        | +120                     | μΑ   |  |  |  |

| Output for Silence (Note 3)                              | V <sub>S</sub>  | TXE Disabled                     | V <sub>MID</sub> + 0.485 | V <sub>MID</sub> + 0.500 | V <sub>MID</sub> + 0.515 | V    |  |  |  |

| Output for High Level (Note 3)                           | V <sub>H</sub>  | TXE Active                       | V <sub>S</sub> + 0.380   | V <sub>S</sub> + 0.400   | V <sub>S</sub> + 0.420   | V    |  |  |  |

| Output for Low Level (Note 3)                            | $V_L$           | TXE Active                       | V <sub>S</sub> - 0.420   | V <sub>S</sub> - 0.400   | V <sub>S</sub> - 0.380   | V    |  |  |  |

| Asymmetry of $\rm V_{\rm H}$ and $\rm V_{\rm L}$         | $\Delta V_{HL}$ |                                  | -0.02                    | -                        | 0.02                     | V    |  |  |  |

| Rise and Fall Times (Note 4)                             | tf, tr          | C <sub>RT</sub> = 22 pF (Note 4) | -                        | 4.7                      | -                        | μsec |  |  |  |

Nominal values are: V<sub>S</sub> = 2.5 V, V<sub>H</sub> = 2.9 V and V<sub>L</sub> = 2.1 V.

By adding an external capacitor between the CRT pin and ground, slew rate at VDRV output can be controlled. The controlling equation is tf or tr = 2 μs + (0.123 μs/pF \* C<sub>RT</sub>). C<sub>RT</sub> is nominally 22 pF, yielding tf = tr = 4.7 μs. The constant comes from an internal capacitor. The hot side of the capacitor and the CRT pin should have a guard pattern around them to avoid unnecessary interference.

### **Table 9. CURRENT CONTROL AMPLIFIER**

| Parameter                       | Symbol          | Conditions            | Min    | Тур  | Max                   | Unit |

|---------------------------------|-----------------|-----------------------|--------|------|-----------------------|------|

| Input Common Mode Voltage Range | V <sub>CM</sub> |                       | 0      | -    | V <sub>CC</sub> – 1   | V    |

| Output Voltage Swing            | Vo              |                       | 1      | -    | V <sub>CC</sub> – 0.5 | V    |

| Load Current                    | Ι <sub>Ο</sub>  |                       | -2,300 | -    | 100                   | μΑ   |

| Input Offset Voltage            | V <sub>OS</sub> |                       | -3     | -    | +3                    | mV   |

| Slew Rate                       | SR              | $C_L = 10 \text{ pF}$ | -      | 0.54 | -                     | V/µs |

| Gain Bandwidth Product          | GBW             | $R_L = 200 k\Omega$   | -      | 1.15 | -                     | MHz  |

| Phase Margin                    | PM              |                       | -      | 66   | -                     | Deg  |

# **Receiver Block**

# Table 10. RECEIVER SUB-BLOCKS

| Parameter                 | Symbol                                 | Conditions                   | Min                   | Тур | Max | Unit |

|---------------------------|----------------------------------------|------------------------------|-----------------------|-----|-----|------|

| Band Pass Filter          | ·                                      |                              |                       |     |     |      |

| Input Voltage             | V <sub>BP</sub>                        | SIGIN Pint to GND            | 1                     | -   | 4   | V    |

| Output Voltage Swing      | FLTOUT                                 |                              | 1                     | -   | 4   | V    |

| Output Slew Rate          | SR                                     |                              | _                     | 0.6 | _   | V/μs |

| Input Offset Voltage      | V <sub>OS</sub>                        |                              | _                     | -   | ±5  | mV   |

| Filter Resistors (Note 5) | RF1                                    |                              | 60                    | 75  | 90  | kΩ   |

|                           | RF2                                    |                              | 216                   | 270 | 324 | kΩ   |

|                           | RF3                                    |                              | 16                    | 20  | 24  | kΩ   |

|                           | RF4                                    |                              | 43                    | 54  | 65  | kΩ   |

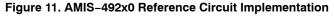

| Carrier Detector          |                                        |                              |                       |     |     |      |

| Threshold Voltage         | V <sub>TH+</sub>                       | Relative to V <sub>MID</sub> | 40                    | 50  | 60  | mV   |

|                           | V <sub>TH-</sub>                       |                              | -60                   | -50 | -40 | mV   |

| Output High Voltage       | V <sub>OH</sub>                        | I <sub>OH</sub> = 0 mA       | V <sub>DD</sub> – 0.6 | -   | -   | V    |

| Output Low Voltage        | V <sub>OL</sub> I <sub>OL</sub> = 0 mA |                              | _                     | -   | 0.3 | V    |

| 1 3 5               | 011             | 011                      | DD |     |     |    |

|---------------------|-----------------|--------------------------|----|-----|-----|----|

| Output Low Voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 0 mA   | _  | -   | 0.3 | V  |

| Output High Current | I <sub>OH</sub> | $V_{DD} - V_O \le 0.6 V$ | 50 | -   | -   | μΑ |

| Output Low Current  | I <sub>OL</sub> | $V_0 \le 0.6 V$          | 50 | -   | -   | μΑ |

| Output Rising Time  | t <sub>R</sub>  | C <sub>L</sub> = 10 pF   | -  | 0.3 | -   | μs |

| Output Leak Current | t <sub>F</sub>  | C <sub>L</sub> = 10 pF   | -  | 0.3 | -   | μs |

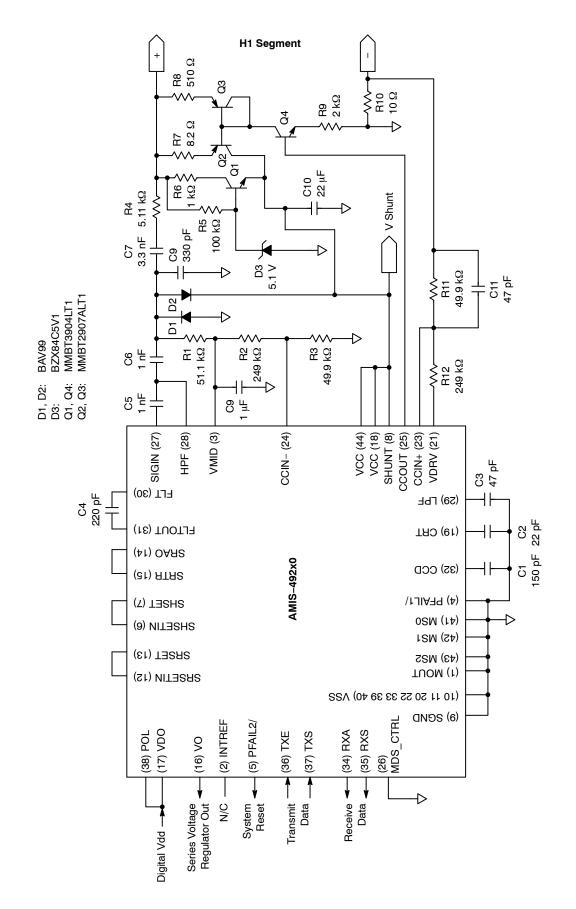

#### Zero-cross Detector

| Threshold Voltage                   | shold Voltage V <sub>TH+</sub> No Carrier                 |                          | V <sub>MID</sub> + 0.025 | V <sub>MID</sub> + 0.040 | V <sub>MID</sub> + 0.058 | V  |

|-------------------------------------|-----------------------------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|----|

|                                     | V <sub>TH-</sub>                                          | Carrier Active           | V <sub>MID</sub>         | V <sub>MID</sub>         | V <sub>MID</sub>         | V  |

| Output High Voltage                 | V <sub>OH</sub>                                           | I <sub>OH</sub> = 0 mA   | V <sub>DD</sub> – 0.6    | -                        | -                        | V  |

| Output Low Voltage                  | lige V <sub>OL</sub> I <sub>OL</sub> = 0 mA               |                          | -                        | -                        | 0.3                      | V  |

| Output High Current                 | I <sub>OH</sub>                                           | $V_{DD} - V_O \le 0.6 V$ | 50                       | -                        | -                        | μA |

| Output Low Current                  | I <sub>OL</sub>                                           | V <sub>O</sub> ≤ 0.6 V   | 50                       | -                        | -                        | μA |

| Output Rising Time t <sub>R</sub> 0 |                                                           | C <sub>L</sub> = 10 pF   | -                        | 0.3                      | -                        | μs |

| Output Leak Current                 | Dutput Leak Current t <sub>F</sub> C <sub>L</sub> = 10 pF |                          | _                        | 0.3                      | -                        | μs |

5. The band pass filter is made up of a two pole high pass filter in series with a two pole low pass filter. The filter consists of four resistors internal to AMIS-492x0, and four external capacitors. The active part of each filter is an amplifier connected in a follower configuration.

### THEORY OF OPERATION

#### Overview

The AMIS-492x0 incorporates two different power supply circuits. Both derive their power from the bus. Using the internal configuration, the shunt regulator is set for 5 V and the series regulator is set for 3 V. Users can modify either power supply by adding external components. The AMIS-492x0 Fieldbus can also monitor these power supply voltages and generate power-fail signals if they fall below a specified value. Please refer to the AMIS-492x0 Fieldbus MAU Reference Design Application Note for ways to adjust the shunt and series voltage regulators.

The AMIS-492x0 Fieldbus MAU transmits a Manchester-encoded signal provided from a standard MDS-MAU interface. The output driver makes it possible to design various signal circuits, which depend on the power requirements of your device. The slew rate of the signal can be controlled to minimize unnecessary radiation as specified in IEC/ISA standards.

The AMIS-492x0 Fieldbus MAU has a built-in band pass filter which makes it easy to design your own receiver. The receive block operates on a Manchester-encoded signal. It decodes the signal and verifies proper amplitude with a zero-cross and carrier detect circuit, respectively. Detected signals are then passed on to a controller with the standard MDS-MAU interface.

#### **Power Supply Block**

The power supply block contains four sub-blocks:

- 1. *A Shunt Regulator* for establishing a supply voltage of V<sub>CC</sub> (typ. = 5 V) used by the analog circuitry.

- 2. A Series Regulator for establishing a supply voltage of V<sub>DD</sub> (typ. = 3 V) used for digital circuitry.

- 3. *Two Low Voltage Detectors* for monitoring the two supply voltages.

- 4. A Bandgap Voltage Reference which is used internally for generating a bias level for AC signals.

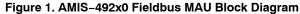

#### Shunt Regulator

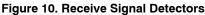

The shunt regulator controls its sink current to the SHUNT pin so that the voltage applied to the SHSETIN pin is equal to  $V_{REF}$ . The  $V_{CC}$  input is divided by an internal network to provide a voltage equal to Vref at the SHSET pin. If SHSET and SHSETIN pins are tied together, and  $V_{CC}$  and SHUNT pins are connected to a power source of high impedance (e.g., current mirror circuit of signal driver), the shunt regulator provides 5 V power to itself and external circuits. A capacitor of 5  $\mu$ F or larger capacity is necessary to stabilize this regulator. Figure 11 shows C10 (22  $\mu$ F) connected to Pin 8 to accomplish stabilization.

It is possible to increase the  $V_{CC}$  voltage up to 6.2 V by dividing  $V_{CC}$  with an external network to supply the appropriate voltage to SHSETIN pin. In this case, SHSET pin must be kept open. The output voltage is determined by the following equation:

$$V_{CC} = V_{REF} \times \left(1 + \frac{R_1}{R_2}\right)$$

(eq. 1)

Figure 2. Shunt Regulator

9 SGND

4

6

SHSETIN

The SHUNT pin is normally connected to  $V_{CC}$ . It is possible to insert a resister between  $V_{CC}$  and SHUNT to measure the shunt current. Its value should be small enough to keep  $V_{DS}$  (voltage between SHUNT pin and SGND pin) larger than 2.5 V (i.e., resistor must be less than 100  $\Omega$ ).

Since the internal transistor can sink as much as 25 mA, no additional circuit is necessary in most cases. Note that the drain current must not exceed 25 mA because no protection is implemented for the internal transistor. If you do not need the shunt regulator, you should connect SHUNT and SHSETIN pins to GND and open SHSET pin. Then  $V_{CC}$  must be supplied from another source.

7 SHSET

N/C

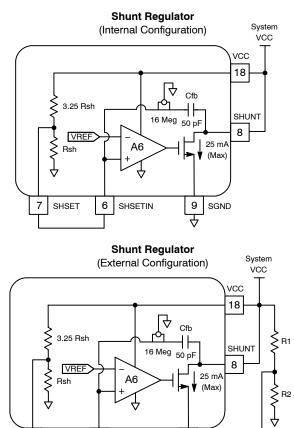

#### Series Regulator

The series regulator produces a regulated voltage at the  $V_O$  pin from  $V_{CC}$ . If you connect SRAO and SRTR pins together, the internal amplifier will regulate the input voltage at SRSETIN pin to equal  $V_{REF}$ . An internal feedback signal is generated to produce a voltage equal to  $V_{REF}$  at pin SRSET. If you connect SRSET and SRSETIN pins, the series regulator supplies 3 V at pin  $V_O$ . A capacitor ( $C_D$  in Figure 3) of 5  $\mu$ F or larger capacity is necessary to stabilize this regulator. The capacitor is expected to have an ESR resistor for the circuit to be stable. If the capacitor is low, a series resistor with the cap load will help stabilize the circuit).

Figure 3. Series Regulator

The supply current must not exceed 20 mA because no current limiting is applied to the internal transistor. You can increase  $V_O$  voltage up to 3.5 V by dividing  $V_O$  with an external network to supply the appropriate voltage to pin SRSETIN. In this case, pin SRSET must be kept open. The drain-source voltage of the internal transistor must be larger or equal to 2 V. If this condition is not satisfied, you may need an external P-channel JFET to create the desired low voltage-drop regulator. The output voltage is determined by the following equation:

$$V_{O} = V_{REF} \times \left(1 + \frac{R_{4}}{R_{5}}\right) \qquad (eq. 2)$$

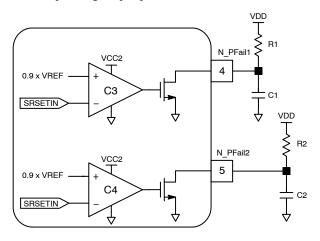

#### Low Voltage Detectors

Low voltage detectors are included to monitor supply voltages and generate "power fail" signals. The low voltage alarms are detected by sensing the voltage on pins SHSETIN and SRSETIN. These pins also provide feedback for the shunt and series regulators. If the voltage on the SHSETIN pin is lower than the threshold, VTH9 (90 percent VREF), N\_PFAIL1 goes low. Typically SHSETIN monitors the analog rail voltage VCC. If the voltage on the SRSETIN pin is lower than the threshold, VTH9, N\_PFAIL2 goes low. Typically SRSETIN monitors the digital rail voltage VDD.

Both outputs are open drain, so a resistor will be required. If you do not use one of these pins, it should be connected to GND. You can also add capacitors to delay these signals. In this case, sink current must not exceed the maximum value.

If you do not wish to use one of the low voltage detectors its corresponding output pin should be connected to GND.

If you do not use one of the regulators, the corresponding alarm signal can potentially be used to monitor another signal. For example, if the series regulator is not used, SRAO should be left open, SRTR tied to VCC, VO grounded and SRSET left open. Then SRSETIN can be the input for monitoring another voltage signal with N\_PFAIL2.

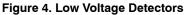

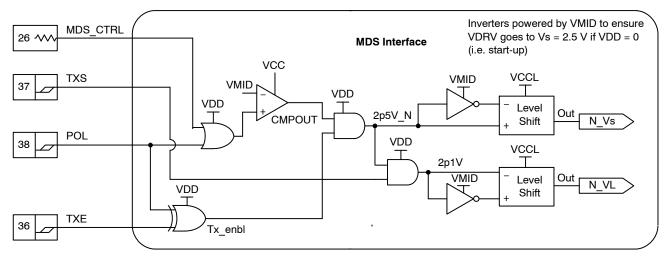

#### Voltage Reference

The voltage reference circuitry generates two voltage signals, VREF and VMID. VREF comes from a bandgap circuit and is used as the reference voltage for all circuits in the AMIS-492x0 Fieldbus MAU. The typical value for VREF is 1.185 V. See Figure 5.

An operational amplifier is regulating VMID to provide a bias (common) level for the AC signals. Its typical voltage is 2 V. A capacitor larger than 0.01  $\mu$ F is necessary on VMID to remove high-frequency ripple.

trace or star connection to system ground.

#### Figure 5. Bandgap and VMID Voltage Reference

### **Transmit Block**

The transmit block contains four sub-blocks:

- 1. *MDS-interface* decodes input signals to generate internal control signals.

- 2. *Tri-level Modulator* generates current signals used as inputs to the slew-rate controller.

- 3. *Slew Rate Controller* converts current to three distinct VDRV voltage levels (V<sub>S</sub>, V<sub>H</sub>, V<sub>L</sub>).

- 4. *Current Drive Amplifier* op amp designed to drive current drivers for 31.25 kbps voltage-mode medium.

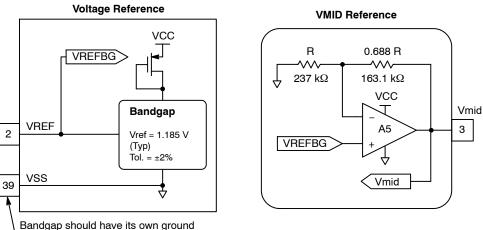

### MDS-interface

The MDS-interface decodes input signals to generate internal control signals. The POL pin is used to select the polarity of TxE (transmit enable). The TxE and TxS (transmit signal) are the MDS–MAU interface signals. These three signals are CMOS logic signals powered by the  $V_{DD}$  supply voltage. When POL is connected to GND, TxE is assumed to be active high (positive logic). Likewise, if

POL is connected to  $V_{DD}$ , TxE is assumed to be active low (negative logic). See Table 1 on page 2, Table 11, and Figure 6 to see how MDS\_CTRL Pin 26 can be used to control MDS interface operation. Table 11 shows the resulting VDRV output for the various combinations of interface signals.

### Table 11. MDS-INTERFACE LOGIC

| POL       | TxE   | TxS  | VDRV           |

|-----------|-------|------|----------------|

|           | Low   | Low  | V              |

| Laur      | Low   | High | VS             |

| Low       | Llinh | Low  | V <sub>H</sub> |

|           | High  | High | VL             |

|           | 1     | Low  | V <sub>H</sub> |

| l li e le | Low   | High | VL             |

| High      | Llinh | Low  | N/             |

|           | High  | High | VS             |

Figure 6. MDS Interface

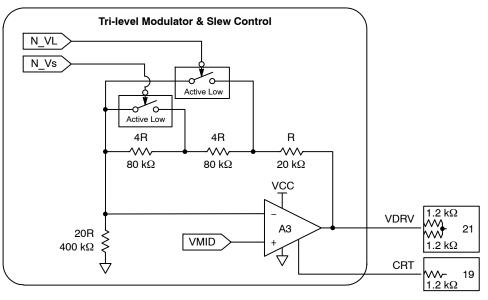

### Tri-level Modulator

The tri-level modulator switches current signals into a summing node. The slew rate controller converts the current to a voltage signal, VDRV. The DC level of silence  $(V_S)$  is

nominally 2.5 V. Transmission high ( $V_H$ ) is nominally 2.9 V and transmission low ( $V_L$ ) is nominally 2.1 V, yielding an amplitude of 0.8 V.

Figure 7. Tri-level Modulator

### Slew Rate Controller

Amplifier (A3), shown in the above figure, controls the slew rate. The amplifier converts the current signals from the tri-level modulator to a voltage signal, VDRV. It controls its slew rate with a capacitor ( $C_{RT}$ ) connected to the CRT pin. The waveform at the VDRV pin is symmetric and the fall/rise times are determined by the following equation:

$$t_{F'} t_{R} = 2.0[\mu s] + 0.12[\mu s/pF] \times C_{RT}$$

(eq. 3)

The constant part comes from the internal capacitor (not shown). It is recommended to make a guard pattern on your circuit board around the CRT pin and the hot side of  $C_{RT}$  to avoid unnecessary interference.

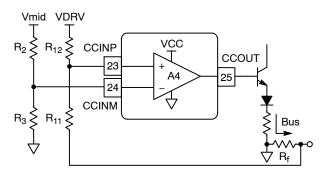

#### Current Drive Amplifier

The drive amplifier is an operational amplifier optimized to drive current drivers for 31.25 kbps voltage-mode medium. Its input and output signals are exposed to allow flexible design of the external driver. Note that this amplifier cannot directly sink the necessary current from the medium. In the following drive circuit the current ( $I_{BUS}$ ) through the current-detect resister ( $R_F$ ) is determined by the following equation.

$$I_{bus} = \frac{\left[R_{3}V_{mid}\left(R_{12} + R_{11}\right)\right] - \left[V_{DRV}\left(R_{2}R_{11} + R_{3}R_{11}\right)\right]}{-\left[R_{F}\left(R_{2}R_{12} + R_{3}R_{12}\right)\right]} (eq. 4)$$

A diode and/or a resistor connected to the emitter are necessary to shift the DC level of CCOUT and to suppress the loop gain. The resistance value depends on your design (overall gain and emitter current).

Figure 8. Current Control Circuit

#### **Receive Block**

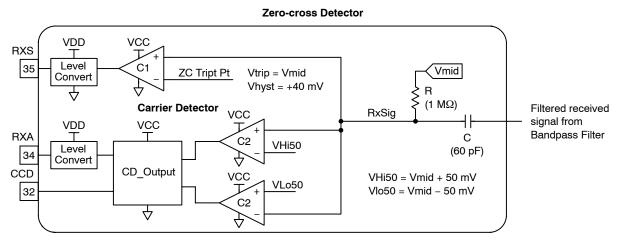

The receive block contains three sub-blocks, which are internally connected:

- 1. *A Band Pass Filter* to filter the desired incoming communication signal.

- 2. *Carrier Detector* generates the RxA signal by detecting the signal amplitude.

- 3. *Zero-cross Detector* generates the RxS signal by detecting the high/low transitions of the Manchester code.

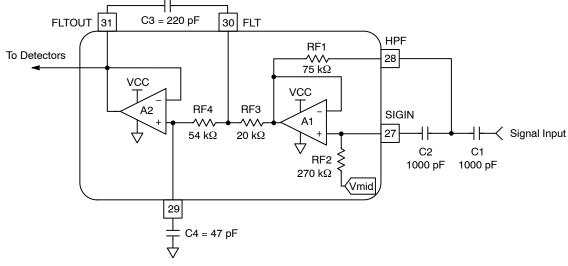

#### Band Pass Filter

The band pass filter is a series connection of a high-pass and a low-pass filters each having two poles. Each filter is comprised of a voltage follower and on chip resisters, so only four external capacitors are necessary. The following figure shows an internal circuit and the connection of external capacitors. Cut-off frequency,  $f_L$ , of the high-pass filter is determined by  $C_1$  and  $C_2$  while cut-off frequency,  $f_H$ , of the low-pass filter is determined by  $C_3$  and  $C_4$ .

$$\begin{split} f_{L} &= \frac{1}{2\pi} \sqrt{\frac{1}{R_{F1} \times R_{F2} \times C_{1} \times C_{2}}} \\ Q_{L} &= \frac{1}{2} \sqrt{\frac{R_{F2}}{R_{F1}}} = 0.95 \end{split} \tag{eq. 5}$$

$$f_{H} = \frac{1}{2\pi} \sqrt{\frac{1}{R_{F3} \times R_{F4} \times C_{3} \times C_{4}}}$$

$$Q_{L} = 0.44 \times \sqrt{\frac{C_{3}}{C_{4}}} = 0.95$$

(eq. 6)

The possible ranges of  $f_L$  and  $f_H$  are 1 kHz ~ 10 kHz and 10 kHz ~ 100 kHz, respectively. The values in the following figure are recommended to obtain 1 kHz and 47.6 kHz cut-off frequencies.

#### **Receive Signal Detection**

The carrier detector generates the receive activity (RxA) signal by detecting the input signal amplitude. Minimum amplitude is 100 mVp-p (TYP). A delay, determined by the capacitor connected between the CCD pin and GND, is added to avoid detection of transient noise. The recommended value of  $C_{CD}$  is 100 pF. The output can drive a CMOS input of  $V_{DD}$  supply voltage.

The zero-cross detector generates the receive signal (RxS) with minimum phase error (jitter) by detecting the transition between high and low levels of the incoming Manchester code. Hysteresis of +40 mV (TYP) is applied to avoid unnecessary switching by noise. Once the carrier-detect goes active the hysteresis is removed and the switching point threshold is set to Vmid. The output can drive a CMOS input of  $V_{DD}$  supply voltage.

# AMIS-49200 AS REPLACEMENT FOR YOKOGAWA µSAA22Q

The AMIS-49200 is a near pin-for-pin compatible replacement for the Yokogawa µSAA22Q Fieldbus MAU. There are some differences between the two chips both in the internal operation, the required external connections and the value (or existence) of some of the external components. These differences are small and those who used the µSAA22Q would most likely be able to use the AMIS-49200 in designs with only some component value changes.

#### Functional Differences between the µSAA22Q and the AMIS-492x0

#### Jabber Inhibit

The AMIS-492x0 does not implement the Jabber Inhibit function in the µSAA22Q. Typically the AMIS-492x0 will be connected with a link controller chip such as the UFC100-F1 from Aniotek/Softing. This link controller has a Jabber Inhibit function so the absence of this function in the AMIS-492x0 should not be a problem.

As can be seen in Table 12, MDS CTRL is only connected to ground if POL is connected to VDD. See Table 1 for a detailed description of the interaction between MDS CTRL and POL.

In Table 12, the µSAA22Q recommends that the JAB/ signal (Pin 39) be connected to ground if the signal is not used. On AMIS-492x0, Pin 39 must be connected to ground.

#### Low Power Mode

The low power mode on the µSAA22Q allows the user to have a quiescent current draw of less than 10 mA yet still communicate at the proper IEC 61158–2 signal levels. Very few, if any, Fieldbus devices are capable of operating at such a low current level so this capability was not included in the AMIS-492x0.

The pins affected by this are 41, 42 and 43. If the low power mode is not being used on the µSAA22Q, these three pins are grounded. On the AMIS-492x0 it is required that these pins be grounded.

#### Pin Differences between the µSAA22Q and the AMIS-492x0

Pin differences are shown in Table 12.

#### Table 12. PIN CONNECTION DIFFERENCES BETWEEN THE μSAA22Q AND THE AMIS-492x0

|         | μSA         | A22Q                      | AMIS-492x0  |                     |  |  |

|---------|-------------|---------------------------|-------------|---------------------|--|--|

| Pin No. | Signal Name | Recommended<br>Connection | Signal Name | Required Connection |  |  |

| 1       | NC          | Ground                    | VSS         | Ground              |  |  |

| 11      | NC          | Ground                    | VSS         | Ground              |  |  |

| 22      | NC          | Ground                    | VSS         | Ground              |  |  |

| 26      | NC          | Ground                    | MDS_CTRL    | Ground*             |  |  |

| 33      | NC          | Ground                    | VSS         | Ground              |  |  |

| 39      | JAB/        | Ground if Not Used        | VSS         | Ground              |  |  |

| 41      | CJB         | 1 μF cap                  | VSS         | Ground              |  |  |

| 42      | VTX         | Ground                    | VSS         | Ground              |  |  |

| 43      | VSL         | Ground                    | VSS         | Ground              |  |  |

\* MDS\_CTRL is only connected to ground if POL is connected to VDD. See Table 1 for a detailed description of the interaction between MDS CTRL and POL.

#### **External Circuitry**

Figure 11 shows the external circuitry required to connect the AMIS-492x0 to an IEC 61158-2 conformant network. This schematic is the circuit that was used to pass the FOUNDATION Fieldbus Physical Layer Conformance test as specified in FOUNDATION Fieldbus specification FF830, Rev 1.5. This circuit is similar but not identical to the circuit recommended by Yokogawa for the µSAA22Q.

Table 13 lists the four external component values that need to be changed with using the AMIS-492x0 in a circuit that previously used the µSAA22Q.

#### Table 13. PASSIVE EXTERNAL COMPONENT VALUE DIFFERENCES BETWEEN THE µSAA22Q AND THE AMIS-492x0

| Component | μSAA22Q Value | AMIS-492x0 Value |

|-----------|---------------|------------------|

| C1        | 100 pF        | 150 pF           |

| C3        | 100 pF        | 47 pF            |

| C4        | 470 pF        | 220 pF           |

| C8        | 10 nF         | 1 μF             |

C1 connects to signal CCD (Pin 32) and controls the carrier detect assert and drop-out timing. Particular implementations may require that the value of C1 be changed to accommodate received signal level changes introduced by the addition of intrinsic safety components added to the external circuitry. C3 and C4 are part of the receive filter and determine the band pass characteristics of the receive filter. It is unlikely that these would need to be changed. C8 is a noise filter for VMID. It is important that VMID have as little noise as possible as it is used as a reference for many sub-circuits in the AMIS–492x0. C8 must be a large capacitor with maximum of 100 nF. C8 recommended value is 1 µF.

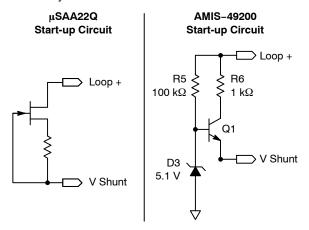

There is one other minor difference in the recommended external circuitry between the  $\mu$ SAA22Q and the AMIS-492x0. Figure 12 shows the start-up circuits recommended for the  $\mu$ SAA22Q and the AMIS-492x0. The circuit shown for the AMIS-492x0 is different from that shown for the  $\mu$ SAA22Q but either one will work. Both are current sources that turn on when power is applied to the H1 segment terminals so that the AMIS-492x0 can turn on without any turn-on transients on the network.

Figure 12. Recommended Start-up Circuits

#### **Active Components**

Transistors Q1–Q4 are ordinary small signal transistors. Diodes D1 and D2 are similarly ordinary small signal diodes. Users desiring to replace a  $\mu$ SAA22Q with the AMIS–49200 in an existing design should be able to use whatever transistors and diodes were used with the  $\mu$ SAA22Q. For new designs, the specified transistors can be used or other devices may be chosen.

#### **Alternative Designs**

Some users of the Yokogawa µSAA22Q did not use the exact recommended external circuit for the media interface circuit (see Figure 11). Using the AMIS-492x0 without the Yokogawa recommended external circuit may result in some compatibility problems. There are many alternative designs and it is beyond the scope of this document to identify all possible configurations and their associated design implications. Please refer to the AMIS-492x0 Fieldbus MAU Reference Design Application Note for a recommended, FOUNDATION Fieldbus certifiable board design.

#### Verification

All designs using the AMIS-492x0 should re-run the entire physical layer conformance test as defined in FOUNDATION Fieldbus document FF-830, FOUNDATION<sup>®</sup> Specification 31.25 kbit/s Physical Layer Conformance Test. Board layout can alter the behavior of all circuit implementations, even designs that follow the recommended implementation.

| Table 44  |          |             |

|-----------|----------|-------------|

| Table 14. | ORDERING | INFORMATION |

| Part Number    | Package                                        | Temperature Range | Shipping <sup>†</sup> |

|----------------|------------------------------------------------|-------------------|-----------------------|

| AMIS-49200-XTD | 44 LQFP 10 × 10 mm<br>(Pb-Free/RoHS Compliant) | –40°C to 85°C     | 160 / Tray            |

| AMIS-49200-XTP | 44 LQFP 10 × 10 mm<br>(Pb-Free/RoHS Compliant) | –40°C to 85°C     | 1,500 / Tape & Reel   |

| AMIS-49250-XTD | 44 NQFP 7 × 7 mm<br>(Pb-Free/RoHS Compliant)   | –40°C to 85°C     | 160 / Tray            |

| AMIS-49250-XTP | 44 NQFP 7 × 7 mm<br>(Pb–Free/RoHS Compliant)   | –40°C to 85°C     | 1,500 / Tape & Reel   |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

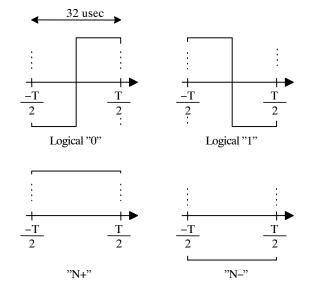

# **APPENDIX – MANCHESTER ENCODING**

All Fieldbus devices transmit the data onto the media as a Manchester-encoded baseband signal. With Manchester encoding, zeros and ones are represented by transitions that occur in the middle of the bit period (see below). For FOUNDATION Fieldbus H1 and Profibus PA, the nominal bit time is 32  $\mu$ sec, with the transition occurring at 16  $\mu$ sec. The Manchester encoding rules have been extended to include two additional symbols, non-data plus (N+) and non-data minus (N-). The symbol encoding rules are shown in Figure 13.

Figure 13. Manchester Encoding

# PACKAGE DIMENSIONS

LQFP-44, 10x10 CASE 561AA ISSUE O

| SYMBOL | MIN  | NOM   | MAX  |

|--------|------|-------|------|

| A      | —    | —     | 1.60 |

| A1     | 0.05 | -     | 0.15 |

| A2     | 1.35 | 1.40  | 1.45 |

| В      | 0.30 | 0.37  | 0.45 |

| B1     | 0.30 | 0.35  | 0.40 |

| С      | 0.09 | -     | 0.20 |

| C1     | 0.09 | 1     | 0.16 |

| D      | 12   | .00 B | SC   |

| D1     | 10   | .00 B | SC   |

| E      | 12   | .00 B | SC   |

| E1     | 10   | .00 B | SC   |

| e      | 0.   | 80 BS | C.   |

| L      | 0.45 | 0.60  | 0.75 |

| L1     | 1.0  | 00 RE | F    |

| R1     | 0.08 | -     | 0.20 |

| α      | 11   | -     | 13   |

| β°     | 0    | —     | 7    |

| γ      | 0    | —     | _    |

NOTES :

- A PIN #1 ID ON TOP WILL BE LASER MARKED.

- $\underline{\&}$  bilateral coplanarity zone applies to the exposed heat sink slug as well as the

- TERMINALS. 10. THIS DRAWING CONFORMES TO JEDEC REGISTERED OUTLINE MO-220

- A DEPENDING ON THE WITHOUT OF GLED TERMINATION AT THE EDGE OF THE PACKAGE, PULLBACK (L1) MAYBE PRESENT ▲ PULLBACK DESIGN OPTIONS IS FOR 0.50mm NOMINAL LANDLENGTH ONLY

# PACKAGE DIMENSIONS

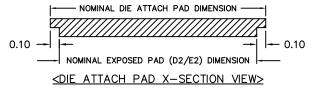

# NQFP 44, 7x7

CASE 560BD ISSUE A (2/2)

| -      |        |           |       |                               |  |  |  |

|--------|--------|-----------|-------|-------------------------------|--|--|--|

| s      | 0.80mi | n LEAD    | PITCH |                               |  |  |  |

| s,,∎®o | VA     | RIATION   | A*    | <sup>N</sup> º <sub>T</sub> _ |  |  |  |

| Ľ      | MIN.   | NOM.      | MAX.  | -                             |  |  |  |

| е      |        | 0.80 BSC. |       |                               |  |  |  |

| Ν      |        | 28        |       |                               |  |  |  |

| ND     |        | 7         |       | ∕∆                            |  |  |  |

| NE     |        | 7         |       | ∕∆                            |  |  |  |

| L      | 0.55   | 0.60      | 0.65  | 公                             |  |  |  |

| b      | 0.25   | 0.30      | 0.35  |                               |  |  |  |

| D2     | 5.00   | 5.10      | 5.20  |                               |  |  |  |

| E2     | 5.00   | 5.10      | 5.20  |                               |  |  |  |

| s | ,  | 0.65mr | n LEAD      | PITCH | N <sub>O,</sub> |  |  |  |  |  |

|---|----|--------|-------------|-------|-----------------|--|--|--|--|--|

| 1 | N  | VA     | VARIATION A |       |                 |  |  |  |  |  |

|   | Ľ  | MIN.   | NOM.        | MAX.  | -               |  |  |  |  |  |

|   | e  |        | 0.65 BSC.   |       |                 |  |  |  |  |  |

|   | N  |        | 32          |       | 3               |  |  |  |  |  |

| N | ٩D |        | 8           |       |                 |  |  |  |  |  |

| N | ١E |        | 8           |       |                 |  |  |  |  |  |

|   | L  | 0.45   | 0.50        | 0.55  | ₽               |  |  |  |  |  |

|   | b  | 0.25   | 0.30        | 0.35  | A               |  |  |  |  |  |

| D | )2 | 5.00   | 5.10        | 5.20  |                 |  |  |  |  |  |

| E | 2  | 5.00   | 5.10        | 5.20  |                 |  |  |  |  |  |

| s  | 0.50mm LEAD PITCH |          |      |      |          |      |      |          |      |      |          |      |                 |

|----|-------------------|----------|------|------|----------|------|------|----------|------|------|----------|------|-----------------|

| B  | VA                | RIATION  | А    | VA   | RIATION  | В    | VA   | RIATION  | С    | VA   | RIATION  | D    | <sup>™</sup> т_ |

| Ľ  | MIN.              | NOM.     | MAX. | MIN. | NOM.     | MAX. | MIN. | NOM.     | MAX. | MIN. | NOM.     | MAX. |                 |

| e  |                   | 0.50 BSC |      |      | 0.50 BSC |      |      | 0.50 BSC |      |      | 0.50 BSC |      |                 |

| N  |                   | 44       |      |      | 44       |      |      | 44       |      |      | 44       |      | 3               |

| ND |                   | 11       |      |      | 11       |      |      | 11       |      |      | 11       |      |                 |

| NE |                   | 11       |      |      | 11       |      |      | 11       |      |      | 11       |      |                 |

| L  | 0.45              | 0.50     | 0.55 | 0.55 | 0.60     | 0.65 | 0.55 | 0.60     | 0.65 | 0.55 | 0.60     | 0.65 |                 |

| b  | 0.18              | 0.25     | 0.30 | 0.18 | 0.25     | 0.30 | 0.18 | 0.25     | 0.30 | 0.18 | 0.25     | 0.30 |                 |

| D2 | 4.60              | 4.70     | 4.80 | 3.20 | 3.30     | 3.40 | 4.60 | 4.70     | 4.80 | 5.00 | 5.10     | 5.20 |                 |

| E2 | 4.60              | 4.70     | 4.80 | 3.20 | 3.30     | 3.40 | 4.60 | 4.70     | 4.80 | 5.00 | 5.10     | 5.20 |                 |

| _  |                   |          |      |             |          |      |             |          |      |             |          |      |                             |

|----|-------------------|----------|------|-------------|----------|------|-------------|----------|------|-------------|----------|------|-----------------------------|

| s  | 0.50mm LEAD PITCH |          |      |             |          |      |             |          |      |             |          |      |                             |

| Ň  | VARIATION E       |          |      | VARIATION F |          |      | VARIATION G |          |      | VARIATION H |          |      | <sup>№</sup> т <sub>Е</sub> |

| Ľ  | MIN.              | NOM.     | MAX. | MIN.        | NOM.     | MAX. | MIN.        | NOM.     | MAX. | MIN.        | NOM.     | MAX. | -                           |

| е  |                   | 0.50 BSC | •    |             | 0.50 BSC |      |             | 0.50 BSC |      |             | 0.50 BSC |      |                             |

| N  |                   | 48       |      |             | 48       |      |             | 48       |      |             | 48       |      | 3                           |

| ND | 12                |          | 12   |             | 12       |      | 12          |          |      |             |          |      |                             |

| NE | 12                |          | 12   |             | 12       |      | 12          |          |      | ⚠           |          |      |                             |

| L  | 0.35              | 0.40     | 0.45 | 0.35        | 0.40     | 0.45 | 0.45        | 0.50     | 0.55 | 0.45        | 0.50     | 0.55 | ⚠                           |

| b  | 0.18              | 0.25     | 0.30 | 0.18        | 0.25     | 0.30 | 0.18        | 0.25     | 0.30 | 0.18        | 0.25     | 0.30 | ▲                           |

| D2 | 5.50              | 5.60     | 5.70 | 5.00        | 5.10     | 5.20 | 5.30        | 5.40     | 5.50 | 5.00        | 5.10     | 5.20 |                             |

| E2 | 5.50              | 5.60     | 5.70 | 5.00        | 5.10     | 5.20 | 5.30        | 5.40     | 5.50 | 5.00        | 5.10     | 5.20 |                             |

| S<br>Y<br>M⊟ | COMMON DIMENSIONS |      |      |                   |  |  |

|--------------|-------------------|------|------|-------------------|--|--|

| ٦.           | MIN.              | NOM. | MAX. | No <sub>t</sub> e |  |  |

| A            | 0.80              | 0.85 | 0.90 |                   |  |  |

| A1           | 0.00              | 0.02 | 0.05 |                   |  |  |

| A3           | 0.20 REF.         |      |      |                   |  |  |

| θ            | 0                 |      | 12   | 2                 |  |  |

| K            | 0.20 MIN.         |      |      |                   |  |  |

| D            | 7.0 BSC           |      |      |                   |  |  |

| Ε            | 7.0 BSC           |      |      |                   |  |  |

| L1           | 0.15 mm MAX       |      |      |                   |  |  |

| s×≊®0 | COMMON DIMENSIONS  |           |      |                   |  |  |  |

|-------|--------------------|-----------|------|-------------------|--|--|--|

| B     | COMMON DIVIENSIONS |           |      |                   |  |  |  |

| °L    | MIN.               | NOM.      | MAX. | No <sub>T</sub> E |  |  |  |

| Α     | 0.70               | 0.75      | 0.80 |                   |  |  |  |

| A1    | 0.00               | 0.02      | 0.05 |                   |  |  |  |

| Α3    |                    | 0.20 REF. |      |                   |  |  |  |

| θ     | 0                  |           | 12   | 2                 |  |  |  |

| Κ     | 0.20 MIN.          |           |      |                   |  |  |  |

| D     | 7.0 BSC            |           |      |                   |  |  |  |

| Е     | 7.0 BSC            |           |      |                   |  |  |  |

| L1    | 0.15 mm MAX        |           |      |                   |  |  |  |

|       |                    |           |      |                   |  |  |  |

GENERAL ; NOMINAL EXPOSED PAD DIMENSION = NOMINAL DIE ATTACH PAD DIMENSION-0.20

1. ALL DIMENSIONS ARE IN MILLIMETERS.

# AMIS-492x0

#### REFERENCES

- Fieldbus Medium Attachment Unit (MAU) Chip, μSAA22Q, Yokogawa Electric Corporation, June 12, 1998, Document No.: SS-96-01 (Rev.3).

- [2] Fieldbus Standard for Use in Industrial Control Systems Part 2: Physical Layer Specification and Service Definition, Amendment to Clause 22 ISA/SP50 – 1996–544B, dS50.02, Part 2, Draft Standard.

- [3] Profibus PA specifications EN 50170 (formerly DIN 19245) covers all of Profibus and includes PA (31.25 kbps Intrinsically Safe Physical Layer), references IEC 61158–2.

#### FOUNDATION is a registered trademark of Semiconductor Components Industries, LLC (SCILLC).

**ON Semiconductor** and **W** are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemic.om/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights of others. SCILLC products are not designed, intended, or authorized for use as components intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly, any claim of personal injury or death massociated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and ex

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# Authorized Distribution Brand :

# Website :

Welcome to visit www.ameya360.com

# Contact Us :

➤ Address :

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

- > Sales :

- Direct +86 (21) 6401-6692

- Email amall@ameya360.com

- QQ 800077892

- Skype ameyasales1 ameyasales2

# > Customer Service :

Email service@ameya360.com

# > Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com