## **CMOS 4-BIT SINGLE CHIP MICROCONTROLLER**

# S1C6F016 Technical Manual

#### Evaluation board/kit and Development tool important notice

- 1. This evaluation board/kit or development tool is designed for use for engineering evaluation, demonstration, or development purposes only. Do not use it for other purpose. It is not intended to meet the requirement of design for finished product.

- 2. This evaluation board/kit or development tool is intended for use by an electronics engineer, and it is not the product for consumer. The user should use this goods properly and safely. Seiko Epson dose not assume any responsibility and liability of any kind of damage and/or fire coursed by usage of it. User should cease to use it when any abnormal issue occurs even during proper and safe use.

- 3. The part used for this evaluation board/kit or development tool is changed without any notice.

#### Notice

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

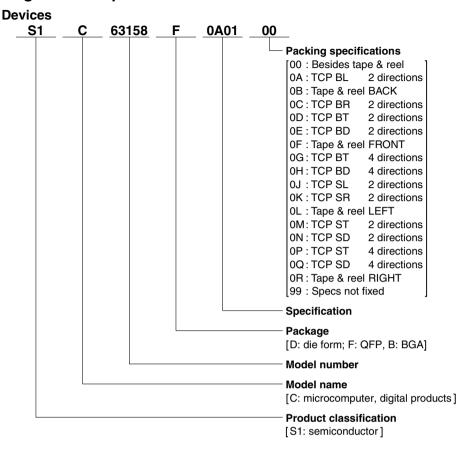

## Configuration of product number

## - Contents -

| 1 | Outline                                            | 1-1 |

|---|----------------------------------------------------|-----|

|   | 1.1 Features                                       | 1-1 |

|   | 1.2 Block Diagram                                  | 1-2 |

|   | 1.3 Mask Option                                    | 1-3 |

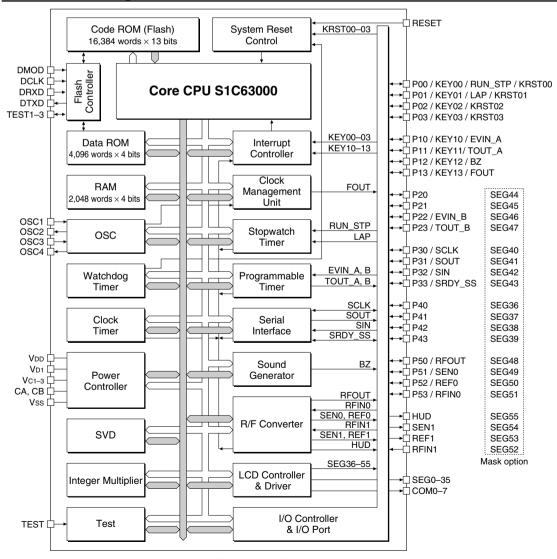

| 2 | Pins and Package                                   | 2-1 |

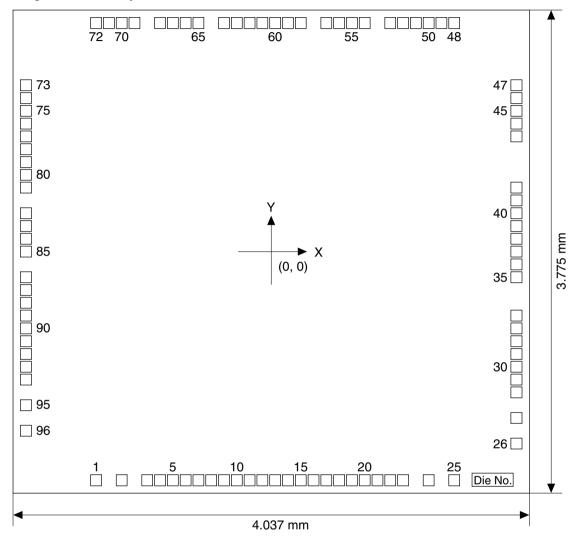

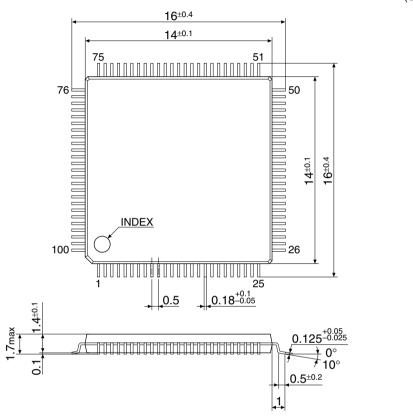

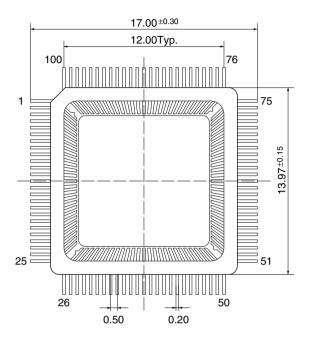

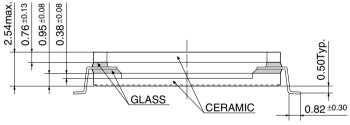

| _ | 2.1 Pin Layout Diagram                             |     |

|   | 2.1.1 QFP15-100pin                                 |     |

|   | 2.1.2 Chip                                         |     |

|   | 2.2 Pin Description                                |     |

|   | 2.3 Package                                        |     |

|   | 2.3.1 Plastic Package                              |     |

|   | 2.3.2 Ceramic Package for Test Samples             |     |

| 3 | CPU and Memory                                     | 3-1 |

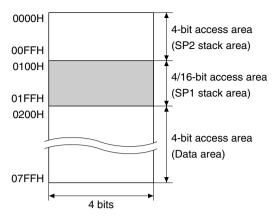

| J | 3.1 CPU                                            |     |

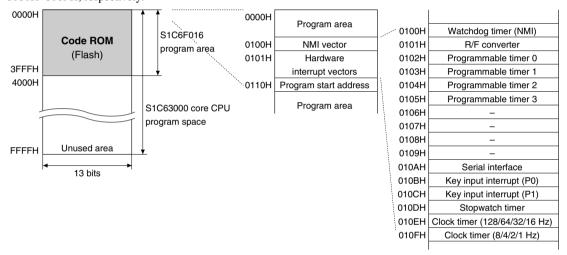

|   | 3.2 Code Memory Area                               |     |

|   | 3.2.1 Code ROM                                     |     |

|   | 3.2.2 Flash EEPROM Specifications                  |     |

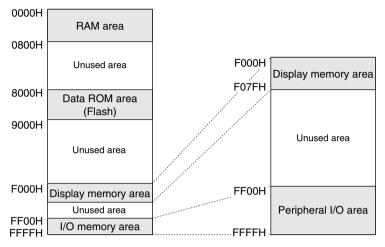

|   | 3.3 Data Memory Area                               |     |

|   | 3.3.1 RAM                                          |     |

|   | 3.3.2 Data ROM                                     | 3-3 |

|   | 3.3.3 Display Memory                               |     |

|   | 3.3.4 I/O Memory                                   | 3-3 |

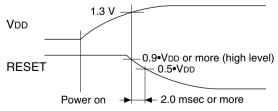

| 4 | Initial Reset                                      | 4-1 |

|   | 4.1 Initial Reset Circuit                          | 4-1 |

|   | 4.2 Reset Terminal (RESET)                         | 4-1 |

|   | 4.3 Simultaneous High Input to P0x Ports (P00–P03) |     |

|   | 4.4 Internal Register at Initial Resetting         |     |

|   | 4.5 Terminal Settings at Initial Resetting         |     |

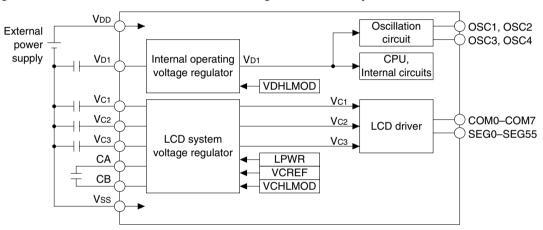

| 5 | Power Supply                                       | 5-1 |

| Ū | 5.1 Operating Voltage                              |     |

|   | 5.2 Internal Power Supply Circuit                  |     |

|   | 5.3 Controlling LCD Power Supply                   |     |

|   | 5.4 Heavy Load Protection Function                 |     |

|   | 5.5 I/O Memory for Power Supply Circuit            |     |

|   | 5.6 Precautions                                    |     |

| _ |                                                    |     |

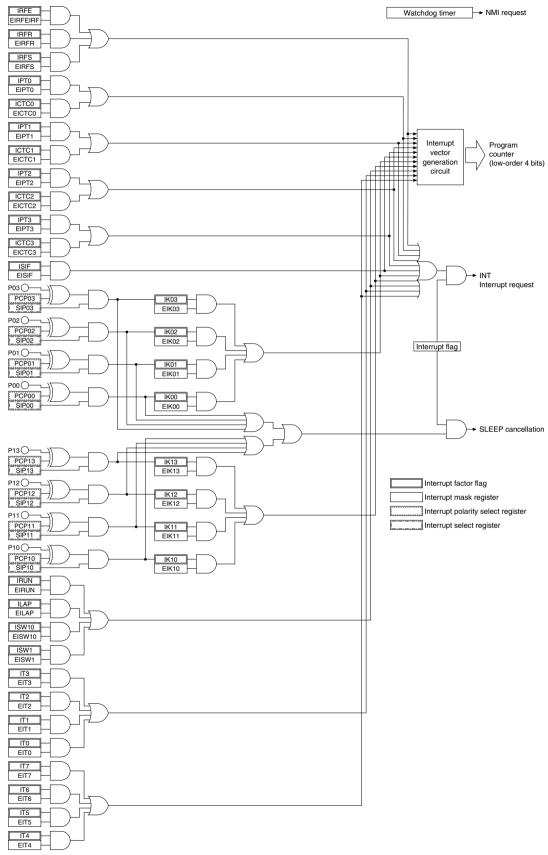

| 6 | Interrupt Controller                               |     |

|   | 6.1 Configuration of Interrupt Controller          |     |

|   | 6.2 Interrupt Factors                              |     |

|   | 6.3 Interrupt Mask                                 |     |

|   | 6.4 Interrupt Vector                               |     |

|   | 6.5 I/O Memory of Interrupt Controller             |     |

|   | 6.6 Precautions                                    | 6-8 |

| 7 | Oscillation Circuit and Clock Control              | 7-1 |

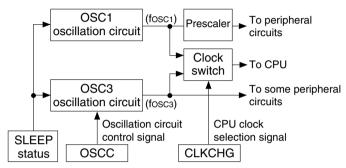

|   | 7.1 Oscillation Circuit                            | 7-1 |

|   | 7.1.1 Configuration of Oscillation Circuit         | 7-1 |

|    | 7.1.2 Mask Option                                           |      |

|----|-------------------------------------------------------------|------|

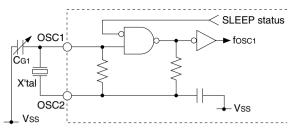

|    | 7.1.3 OSC1 Oscillation Circuit                              |      |

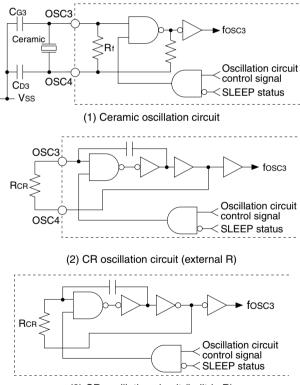

|    | 7.1.4 OSC3 Oscillation Circuit                              |      |

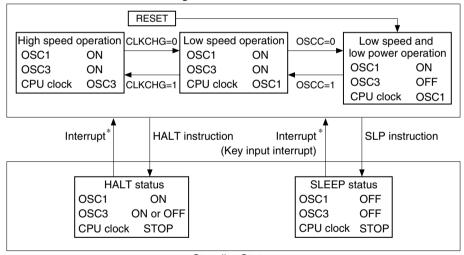

|    | 7.2 Switching the CPU Clock                                 |      |

|    | 7.3 HALT and SLEEP                                          |      |

|    | 7.4 Control of Peripheral Circuit Clocks                    |      |

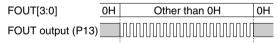

|    | 7.5 Clock Output (FOUT)                                     |      |

|    | 7.6 I/O Memory for Oscillation Circuit/Clock Output Control |      |

|    | 7.7 Precautions                                             | 7-6  |

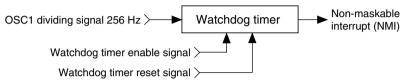

| 8  | Watchdog Timer                                              | 8-1  |

|    | 8.1 Configuration of Watchdog Timer                         | 8-1  |

|    | 8.2 Interrupt Function                                      | 8-1  |

|    | 8.3 I/O Memory of Watchdog Timer                            | 8-1  |

|    | 8.4 Precautions                                             | 8-2  |

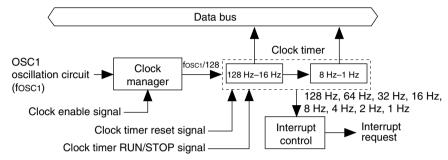

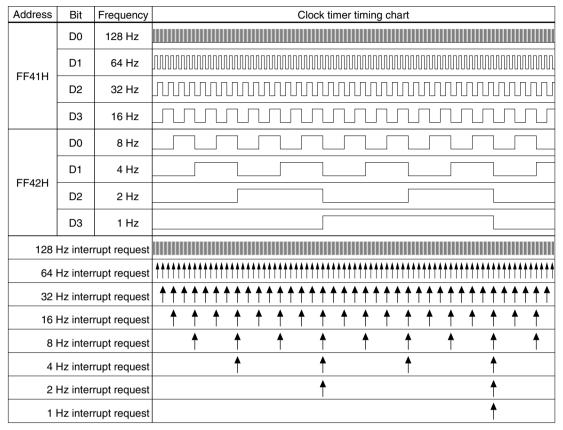

| 9  | Clock Timer                                                 | 9-1  |

| -  | 9.1 Configuration of Clock Timer                            |      |

|    | 9.2 Controlling Operating Clock                             |      |

|    | 9.3 Data Read and Hold Function                             |      |

|    | 9.4 Interrupt Function                                      |      |

|    | 9.5 I/O Memory of Clock Timer                               |      |

|    | 9.6 Precautions                                             |      |

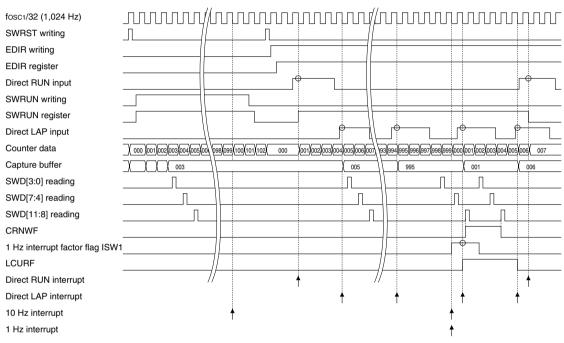

| 11 | 0 Stopwatch Timer                                           |      |

|    | 10.1 Configuration of Stopwatch Timer                       |      |

|    | 10.2 Controlling Operating Clock                            |      |

|    | 10.3 Counter and Prescaler                                  |      |

|    | 10.4 Capture Buffer and Hold Function                       |      |

|    | 10.5 Stopwatch Timer RUN/STOP and Reset                     |      |

|    | 10.6 Direct Input Function and Key Mask                     |      |

|    | 10.7 Interrupt Function                                     |      |

|    | 10.8 I/O Memory of Stopwatch Timer                          |      |

|    | 10.9 Precautions                                            |      |

|    |                                                             |      |

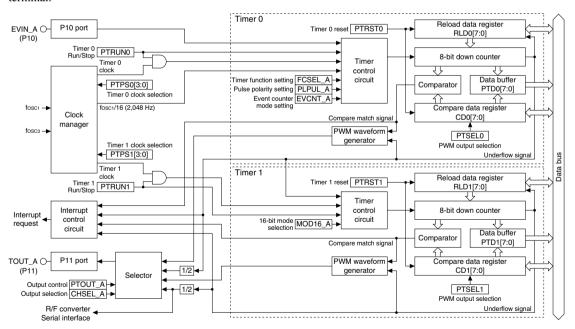

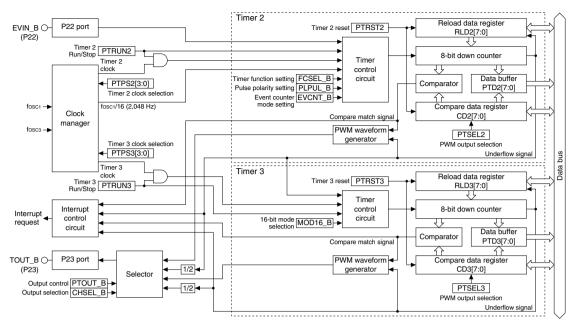

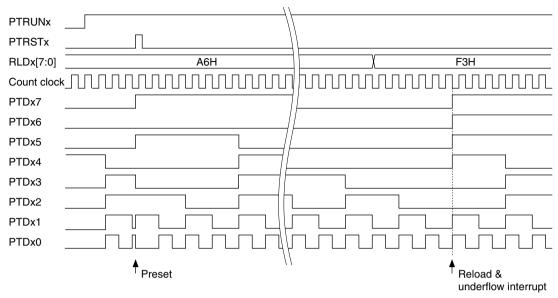

| 11 | 1 Programmable Timer                                        |      |

|    | 11.1 Configuration of Programmable Timer                    |      |

|    | 11.2 Controlling Operating Clock                            |      |

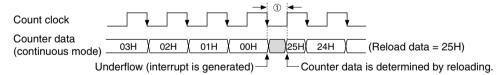

|    | 11.3 Basic Counter Operation                                |      |

|    | 11.4 Event Counter Mode (Timers 0 and 2)                    |      |

|    | 11.5 PWM mode (Timers 0–3)                                  |      |

|    | 11.6 16-bit timer mode (Timer 0 + 1, Timer 2 + 3)           |      |

|    | 11.7 Interrupt Function                                     |      |

|    | 11.8 TOUT Output Control                                    |      |

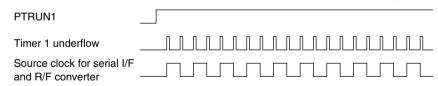

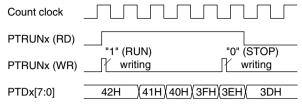

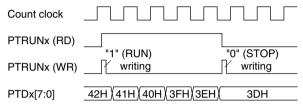

|    | 11.9 Clock Output to Serial Interface and R/F Converter     |      |

|    | 11.10 I/O Memory of Programmable Timer                      |      |

|    | 11.11 Precautions                                           |      |

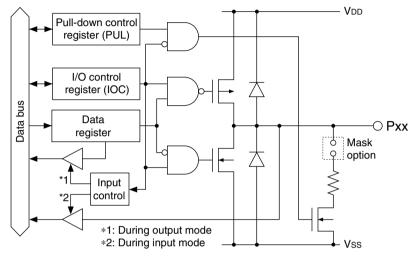

| 12 | 2 I/O Ports                                                 |      |

|    | 12.1 Configuration of I/O Ports                             |      |

|    | 12.2 Mask Option                                            | 12-2 |

## CONTENTS

|    | 12.3   | I/O Control Registers and Input/Output Mode       | 12-3  |

|----|--------|---------------------------------------------------|-------|

|    | 12.4   | Input Interface Level                             | 12-3  |

|    | 12.5   | Pull-down During Input Mode                       | 12-3  |

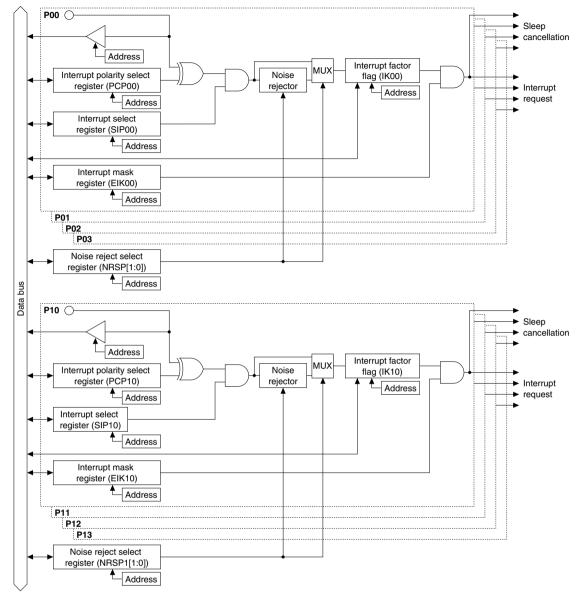

|    | 12.6   | Key Input Interrupt Function                      | 12-3  |

|    | 12.7   | I/O memory of I/O ports                           | 12-5  |

|    | 12.8   | Precautions                                       | 12-10 |

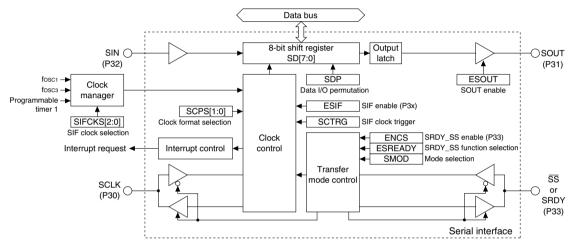

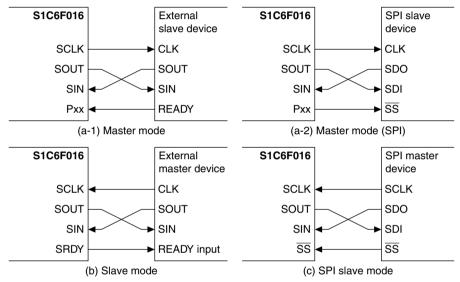

| 13 | Serial | Interface                                         | 13-1  |

|    |        | Configuration of Serial Interface                 |       |

|    |        | Serial Interface Terminals                        |       |

|    |        | Mask Option                                       |       |

|    |        | Operating Mode of Serial Interface                |       |

|    |        | Setting Synchronous Clock                         |       |

|    |        | 13.5.1 Selecting Source Clock                     |       |

|    |        | 13.5.2 Selecting Synchronous Clock Format         |       |

|    | 13.6   | Data Input/Output and Interrupt Function          |       |

|    |        | 13.6.1 Serial Data Output Procedure and Interrupt | 13-5  |

|    |        | 13.6.2 Serial Data Input Procedure and Interrupt  | 13-5  |

|    |        | 13.6.3 Serial Data Input/Output Permutation       |       |

|    |        | 13.6.4 SRDY Signal                                |       |

|    |        | 13.6.5 Timing Chart                               |       |

|    |        | Data Transfer in SPI Mode                         |       |

|    |        | I/O Memory of Serial Interface                    |       |

|    | 13.9   | Precautions                                       | 13-12 |

| 14 | LCD D  | river                                             | 14-1  |

|    | 14.1   | Configuration of LCD Driver                       | 14-1  |

|    | 14.2   | Mask Option                                       | 14-1  |

|    |        | 14.2.1 SEG/GPIO/RFC Terminal Configuration        |       |

|    |        | 14.2.2 Power Source for LCD Driving               |       |

|    |        | 14.2.3 Segment Option                             |       |

|    | 14.3   | LCD Display Control                               |       |

|    |        | 14.3.1 Selecting Display Mode                     |       |

|    |        | 14.3.2 Switching Drive Duty                       |       |

|    |        | 14.3.3 Switching Frame Frequency                  |       |

|    |        | 14.3.5 Static Drive                               |       |

|    |        | 14.3.6 LCD Contrast Adjustment                    |       |

|    | 14.4   | Display Memory                                    |       |

|    |        | I/O Memory of LCD Driver                          |       |

|    |        | Precautions                                       |       |

| 15 | Sound  | Generator                                         | 15-1  |

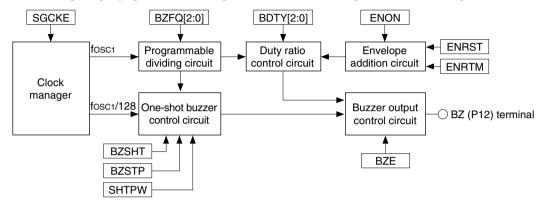

|    |        | Configuration of Sound Generator                  |       |

|    |        | Controlling Operating Clock                       |       |

|    |        | Buzzer Output Control                             |       |

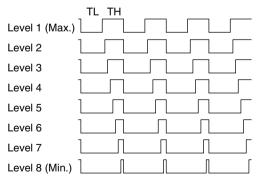

|    |        | Buzzer Frequency and Sound Level Settings         |       |

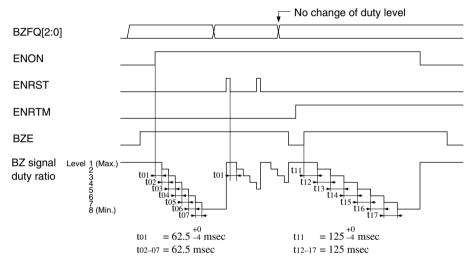

|    |        | Digital Envelope                                  |       |

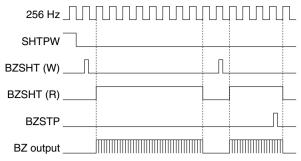

|    |        | One-shot output                                   |       |

|    |        | I/O Memory of Sound Generator                     |       |

|    |        | Precautions                                       |       |

|    | 10.6   | 1 166auti0113                                     | 10-0  |

| 16 | Intege  | r Multiplier        |                                      | 16-1   |

|----|---------|---------------------|--------------------------------------|--------|

|    | 16.1    | Configuration of In | teger Multiplier                     | 16-1   |

|    | 16.2    | Controlling Clock I | Manager                              | 16-1   |

|    | 16.3    | Multiplication Mod  | -<br>∋                               | 16-1   |

|    |         | •                   |                                      |        |

|    |         |                     |                                      |        |

|    |         | •                   | ger Multiplier                       |        |

|    |         |                     | g                                    |        |

| 17 |         |                     |                                      |        |

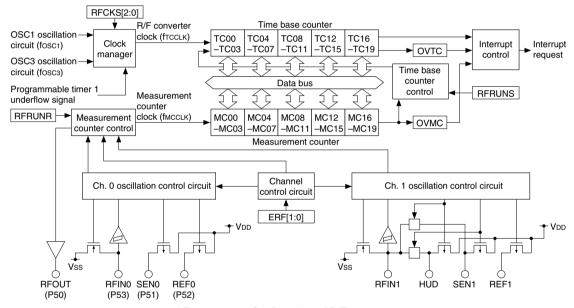

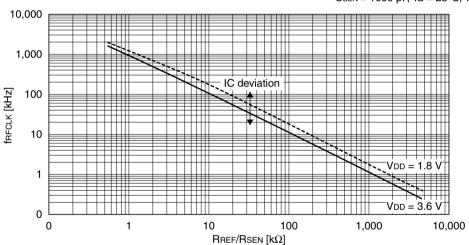

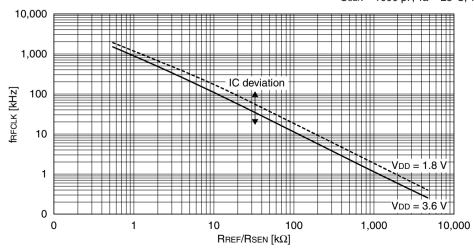

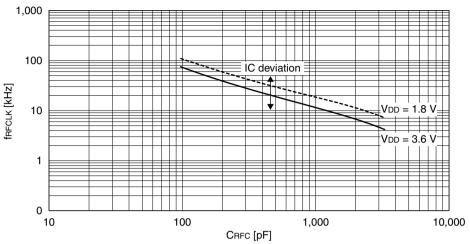

| ., |         |                     | /F Converter                         |        |

|    |         | · ·                 | ing Clock                            |        |

|    |         | - ·                 | _                                    |        |

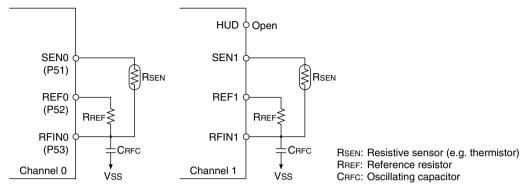

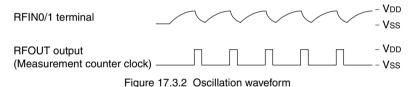

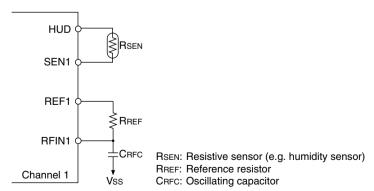

|    |         |                     | als and CR Oscillation Circuit       |        |

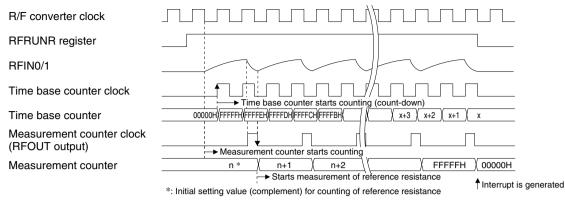

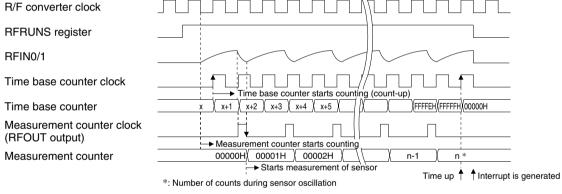

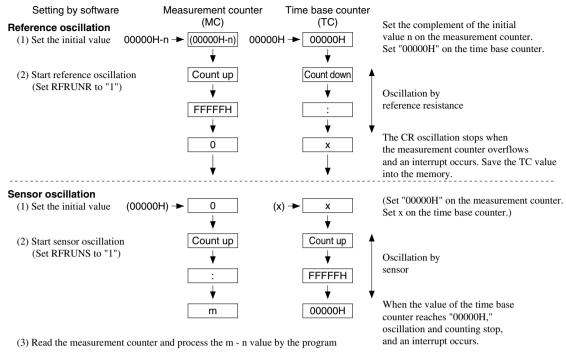

|    |         | •                   | Conversion                           |        |

|    |         | •                   |                                      |        |

|    |         |                     | tion Function                        |        |

|    |         |                     | Converter                            |        |

|    | 17.8    | Precautions         |                                      | 17-11  |

| 18 | SVD (S  | Supply Voltage D    | etection) Circuit                    | 18-1   |

|    | 18.1    | Configuration of S  | VD Circuit                           | 18-1   |

|    | 18.2    | SVD Operation       |                                      | 18-1   |

|    | 18.3    | I/O Memory of SV    | O Circuit                            | 18-2   |

|    | 18.4    | Precautions         |                                      | 18-2   |

| 19 | Electri | cal Characterist    | cs                                   | 19-1   |

|    |         |                     | n Rating                             |        |

|    |         |                     | perating Conditions                  |        |

|    |         |                     | ;                                    |        |

|    |         |                     | racteristics and Current Consumption |        |

|    | 13.4    |                     | er                                   |        |

|    |         |                     | uit                                  |        |

|    |         |                     | erter Circuit                        |        |

|    |         | 19.4.4 Current C    | onsumption                           | 19-4   |

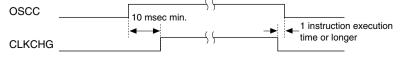

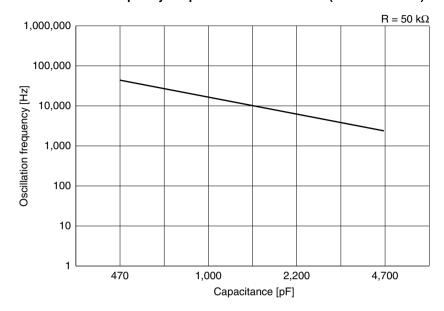

|    | 19.5    | Oscillation Charac  | teristics                            | 19-4   |

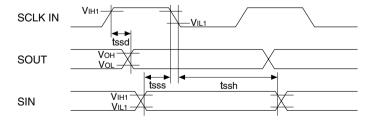

|    | 19.6    | Serial Interface AC | Characteristics                      | 19-5   |

|    | 19.7    | Timing Chart        |                                      | 19-5   |

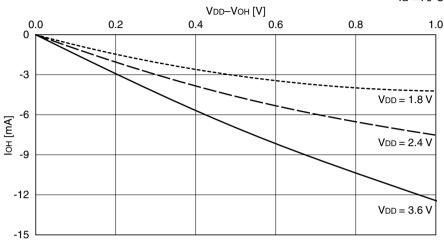

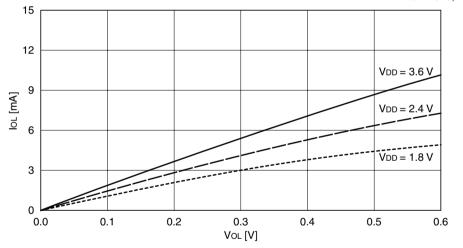

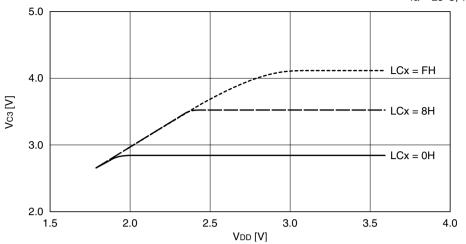

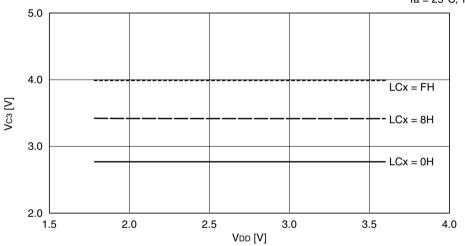

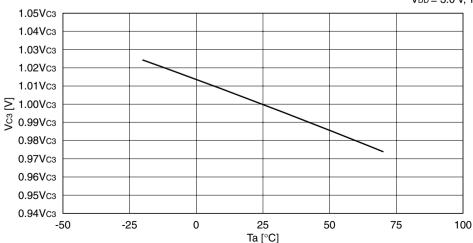

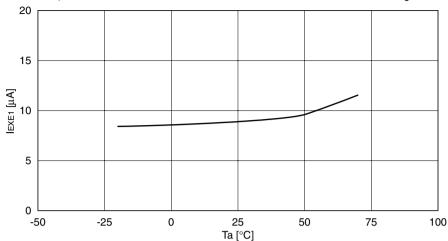

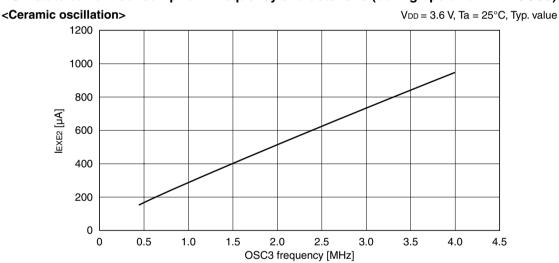

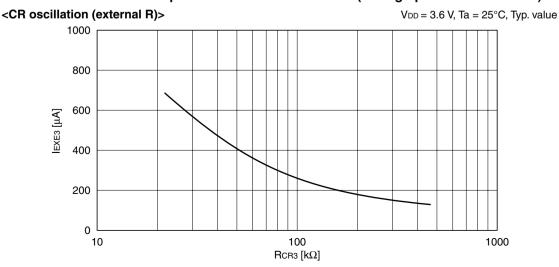

|    | 19.8    | Characteristics Cu  | rves (reference value)               | 19-6   |

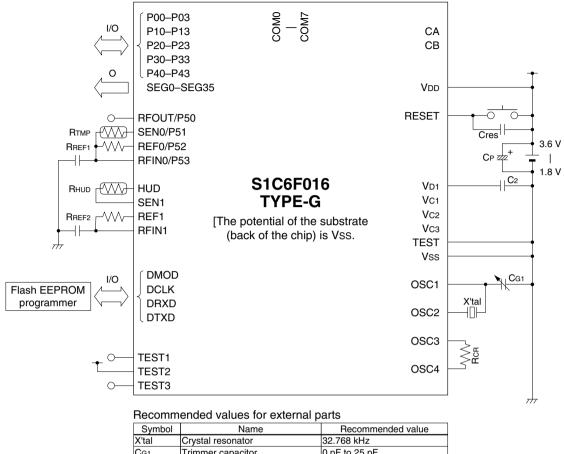

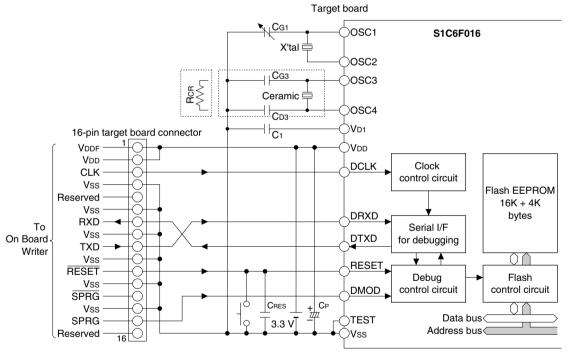

| 20 | Basic I | External Wiring     | Diagram                              | 20-1   |

|    |         | _                   | gisters                              |        |

| ΑÞ | pendix  | FF00H               | Oscillation Circuit                  |        |

|    |         | FF01H               | Watchdog Timer                       |        |

|    |         | FF02H-FF03H         | Power Supply Circuit                 |        |

|    |         | FF04H-FF05H         | SVD Circuit                          |        |

|    |         | FF10H-FF1BH         | Clock Manager                        | AP-A-1 |

|    |         | FF20H-FF3FH         | I/O Ports                            | AP-A-2 |

|    |         | FF40H-FF42H         | Clock Timer                          |        |

|    |         | FF44H–FF47H         | Sound Generator                      |        |

|    |         | FF48H–FF4DH         | Stopwatch Timer                      |        |

|    |         | FF50H-FF52H         | LCD Driver                           |        |

#### **CONTENTS**

|      | FF60H-FF6BH               | R/F Converter                                                   | AP-A-5  |

|------|---------------------------|-----------------------------------------------------------------|---------|

|      | FF70H-FF76H               | Integer Multiplier                                              | AP-A-6  |

|      | FF80H-FF9FH               | Programmable Timer                                              | AP-A-7  |

|      | FFE1H-FFFFH               | Interrupt Controller                                            | AP-A-9  |

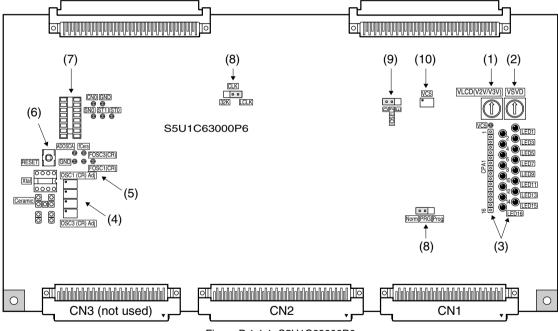

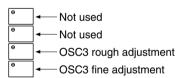

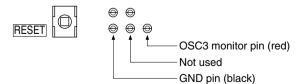

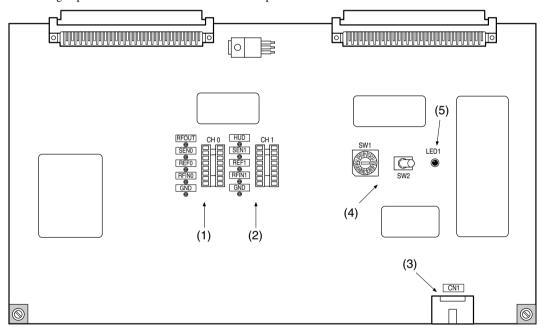

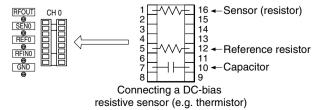

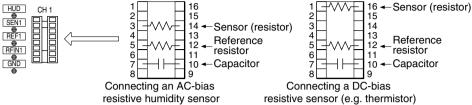

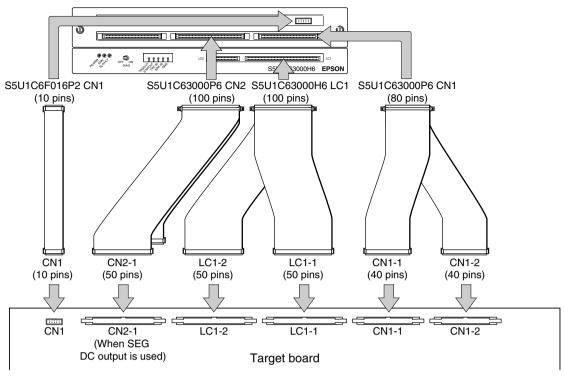

| Anne | endix B. Perinheral Ci    | rcuit Boards for S1C6F016                                       | ΔP-R-1  |

| Дррс |                           | ons of Each Part                                                |         |

|      |                           | 000P6                                                           |         |

|      |                           | 016P2                                                           |         |

|      |                           |                                                                 |         |

|      |                           | arget System                                                    |         |

|      | •                         | U1C63000P6                                                      |         |

|      | •                         |                                                                 |         |

|      | -                         | al precautions                                                  |         |

|      | B.4.2 Difference          | s with the actual IC                                            | AP-B-9  |

|      | B.5 Product Specification | ons                                                             | AP-B-12 |

|      | B.5.1 Specificat          | ions of S5U1C63000P6                                            | AP-B-12 |

|      | B.5.2 Specificat          | ons of S5U1C6F016P2                                             | AP-B-12 |

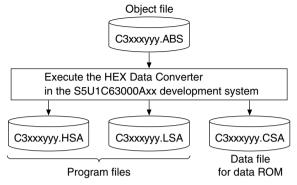

| Anne | endix C. Flash FFPRC      | OM Programming                                                  | ΔP-C-1  |

| ДРРС |                           | ools                                                            |         |

|      | · ·                       | g                                                               |         |

|      |                           |                                                                 |         |

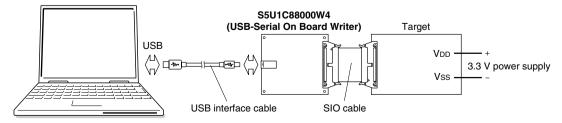

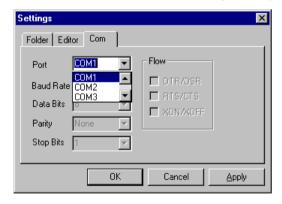

|      |                           | gramming Environment                                            |         |

|      |                           | onnection for Serial Programming                                |         |

|      |                           | gramming Procedure                                              |         |

|      |                           | n Diagram for Serial Programming                                |         |

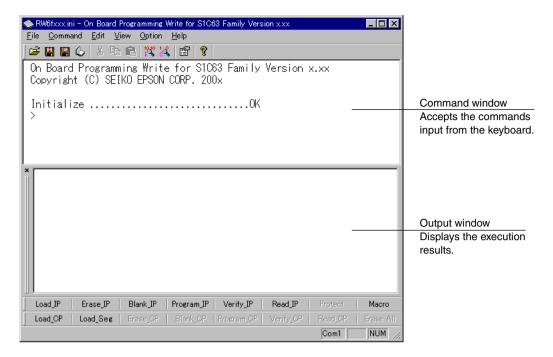

|      |                           | ontrol Software                                                 |         |

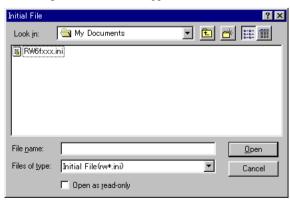

|      |                           | p                                                               |         |

|      |                           |                                                                 |         |

|      |                           | Details                                                         |         |

|      |                           | D PROGRAM (HSA file, LSA file)                                  |         |

|      |                           | D DATA (CSA file)                                               |         |

|      |                           | D SEGMENT (SSA file)                                            |         |

|      |                           | SE PROGRAM, DATA, SEGMENT                                       |         |

|      |                           | NK CHECK PROGRAM, DATA, SEGMENT<br>DGRAM PROGRAM, DATA, SEGMENT |         |

|      |                           | IIFY PROGRAM, DATA, SEGMENT                                     |         |

|      |                           | ND PROGRAM, DATA, SEGMENT                                       |         |

|      |                           | CROCRO                                                          |         |

|      |                           | IMP MEMORY                                                      |         |

|      |                           | PEN LOG FILE                                                    |         |

|      |                           | VE PROGRAM                                                      |         |

|      |                           | VE DATA                                                         |         |

|      |                           | mmands                                                          |         |

|      |                           | or Messages                                                     |         |

|      |                           | ogramming Notes                                                 |         |

| A    |                           |                                                                 |         |

| Appe |                           | <b>)</b>                                                        |         |

|      |                           | lock Control                                                    |         |

|      | D.2 Power Saving by P     | ower Supply Control                                             | AP-D-3  |

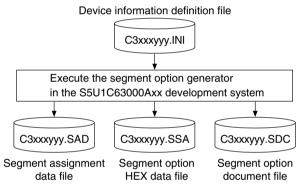

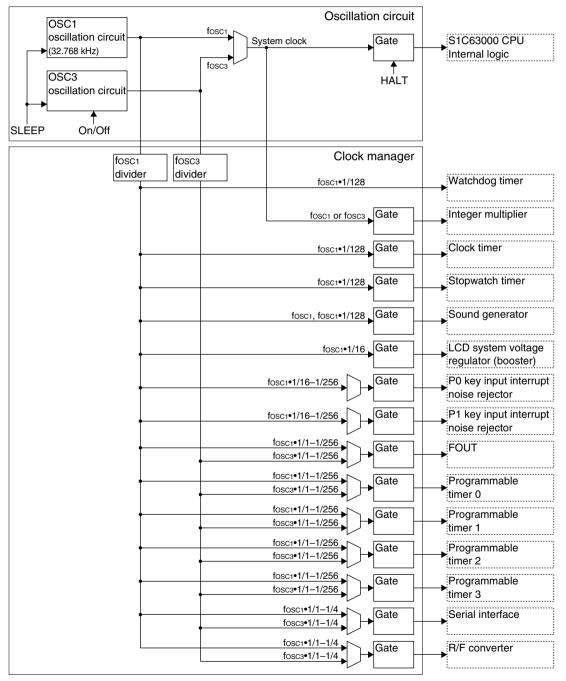

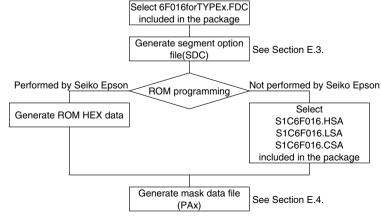

| Appe | endix E S1C6F016 Ma       | ask Data Generation Procedure                                   | AP-E-1  |

| -    |                           | tion Flowchart                                                  |         |

|      |                           | e Generation Procedure                                          |         |

|      | •                         | le Generation Procedure                                         |         |

|      |                           | neration Procedure                                              |         |

|      | INGSN 1/010 I NE CIE      |                                                                 |         |

#### **CONTENTS**

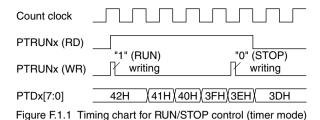

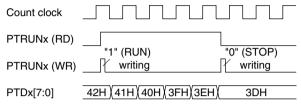

| Appendix F Summary of Notes      | AP-F-1 |

|----------------------------------|--------|

| F.1 Summary of Notes by Function | AP-F-1 |

| F.2 Precautions on Mounting      | AP-F-5 |

| Revision History                 |        |

## 1 Outline

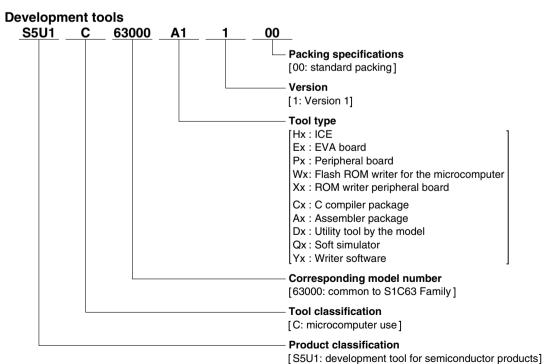

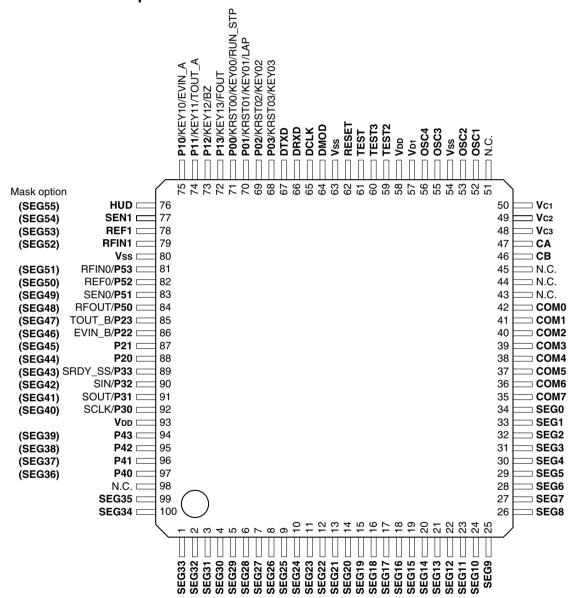

The S1C6F016 is a 4-bit microcontroller that features low voltage operations and low current consumption. It consists of a 4-bit core CPU S1C63000 as the core CPU, Flash EEPROM (16,384 words  $\times$  13 bits), RAM (2,048 words  $\times$  4 bits), supply voltage detection (SVD) circuit, multiply-divide circuit, serial interface, timers, and sound generator. It also incorporates a segment LCD controller/driver that can drive a maximum 56-segment  $\times$  8-common LCD panel, and an R/F converter that can measure temperature and humidity using sensors such as a thermistor.

The S1C6F016 is suitable for battery driven clocks and watches with temperature and humidity measurement functions. The S1C6F016 allows choice from eight different models by mask-option selections and shipment form selections as shown in Table 1.1.

|   | Mask option type *          | Shipment form |  |  |  |  |

|---|-----------------------------|---------------|--|--|--|--|

| 1 | Standard mask option Type B | QFP15-100pin  |  |  |  |  |

| 2 |                             | Die form      |  |  |  |  |

| 3 | Standard mask option Type E | QFP15-100pin  |  |  |  |  |

| 4 |                             | Die form      |  |  |  |  |

| 5 | Standard mask option Type G | QFP15-100pin  |  |  |  |  |

| 6 |                             | Die form      |  |  |  |  |

| 7 | Custom mask option          | QFP15-100pin  |  |  |  |  |

| 8 |                             | Die form      |  |  |  |  |

<sup>\*</sup> See Section 1.3, "Mask Option."

## 1.1 Features

| Core                                                                                 | 4-bit core CPU S1C63000                                                          |  |  |  |  |  |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| OSC1 oscillation circuit                                                             | n circuit                                                                        |  |  |  |  |  |

| OSC3 oscillation circuit                                                             | 4.2 MHz (Max.) ceramic oscillation circuit,                                      |  |  |  |  |  |

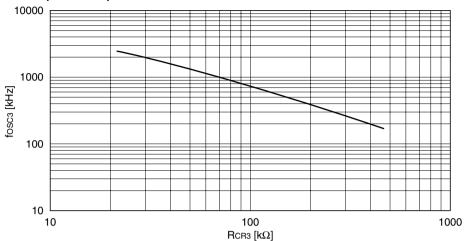

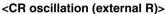

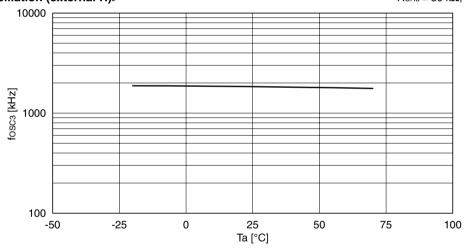

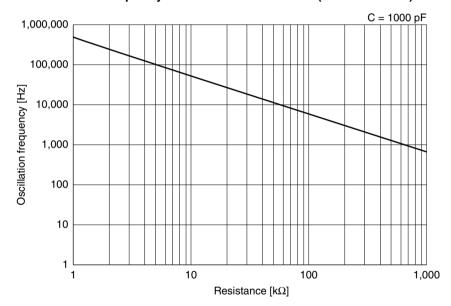

|                                                                                      | 1.8 MHz (Typ.) CR oscillation circuit (external R), or                           |  |  |  |  |  |

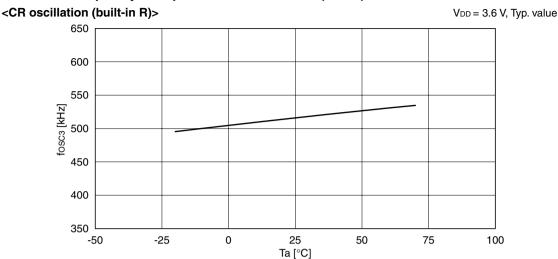

|                                                                                      | 500 kHz (Typ.) CR oscillation circuit (built-in R) (*1)                          |  |  |  |  |  |

| Instruction set                                                                      | Basic instruction: 47 types (411 instructions with all)                          |  |  |  |  |  |

|                                                                                      | Addressing mode: 8 types                                                         |  |  |  |  |  |

| Instruction execution time                                                           | During operation at 32.768 kHz: 61 µsec 122 µsec 183 µsec                        |  |  |  |  |  |

|                                                                                      | During operation at 4 MHz: 0.5 µsec 1 µsec 1.5 µsec                              |  |  |  |  |  |

| Flash EEPROM capacity                                                                | Code ROM: 16,384 words × 13 bits                                                 |  |  |  |  |  |

|                                                                                      | Data ROM: $4,096 \text{ words} \times 4 \text{ bits}$                            |  |  |  |  |  |

| RAM capacity                                                                         | Data memory: $2,048 \text{ words} \times 4 \text{ bits}$                         |  |  |  |  |  |

|                                                                                      | Display memory: 448 bits                                                         |  |  |  |  |  |

| I/O port                                                                             | 24 bits Pull-down resistors can be incorporated. (*1)                            |  |  |  |  |  |

|                                                                                      | The pins can be switched for peripheral circuit inputs/outputs. (*2)             |  |  |  |  |  |

| Serial interface                                                                     | al interface                                                                     |  |  |  |  |  |

| LCD driver                                                                           | 56 segments (Max.) $\times$ 8, 7, 6, 5, 4, or 3 commons (*2)                     |  |  |  |  |  |

| Time base counters                                                                   |                                                                                  |  |  |  |  |  |

| 1/1000-second stopwatch timer with direct key input function                         |                                                                                  |  |  |  |  |  |

| Programmable timer                                                                   | 16-bit timer × 2 channels                                                        |  |  |  |  |  |

|                                                                                      | Each 16-bit timer is configurable to two 8-bit timer channels (*2)               |  |  |  |  |  |

| Watchdog timer                                                                       | Built-in                                                                         |  |  |  |  |  |

| Sound generator                                                                      | With envelope and 1-shot output functions                                        |  |  |  |  |  |

| R/F converter                                                                        | :                                                                                |  |  |  |  |  |

|                                                                                      | Supports resistive humidity sensors.                                             |  |  |  |  |  |

| Multiply-divide circuit                                                              | 8-bit accumulator × 1 channel                                                    |  |  |  |  |  |

|                                                                                      | Multiplication: 8 bits $\times$ 8 bits $\rightarrow$ 16-bit product              |  |  |  |  |  |

|                                                                                      | Division: 16 bits $\div$ 8 bits $\rightarrow$ 8-bit quotient and 8-bit remainder |  |  |  |  |  |

| Supply voltage detection (SVD) circuit Programmable 16 detection voltage levels (*2) |                                                                                  |  |  |  |  |  |

<sup>\*</sup> This product uses SuperFlash® technology licensed from Silicon Storage Technology, Inc.

| External interrupt          | . Key input interrupt:              | 8 systems                                |

|-----------------------------|-------------------------------------|------------------------------------------|

| Internal interrupt          | . Watchdog timer interrupt (NMI)    | : 1 system                               |

|                             | Clock timer interrupt:              | 8 systems                                |

|                             | Stopwatch timer interrupt:          | 4 systems                                |

|                             | Programmable timer interrupt:       | 8 systems                                |

|                             | Serial interface interrupt:         | 1 system                                 |

|                             | R/F converter interrupt:            | 3 systems                                |

| Power supply voltage        | . 1.8 to 3.6 V (for normal operatio | n)                                       |

|                             | 2.7 to 3.6 V (for Flash programm    | ning)                                    |

| Operating temperature range | 20 to 70°C                          |                                          |

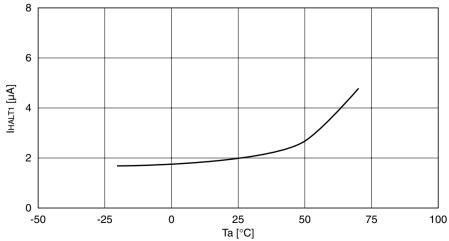

| Current consumption (Typ.)  | . During SLEEP (32 kHz) 0.7 µ       | ıА                                       |

|                             | During HALT (32 kHz) 2 μA           | Δ                                        |

|                             | During running (32 kHz) 9 μA        | Δ                                        |

|                             | During running (4 MHz) 950          | μA                                       |

| Shipment form               | . QFP15-100pin or die form          |                                          |

|                             | *1: Can be selected with mask op    | tion. *2: Can be selected with software. |

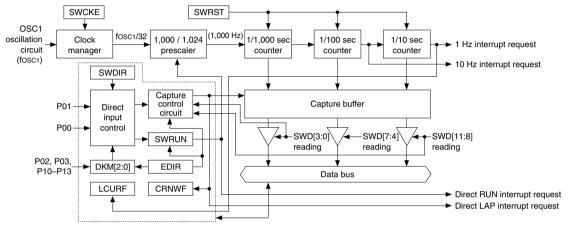

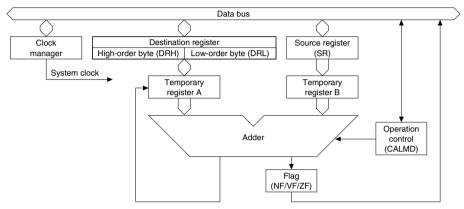

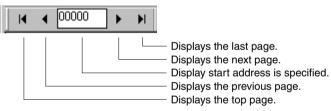

1.2 Block Diagram

Figure 1.2.1 Block diagram

Seiko Epson Corporation

## 1.3 Mask Option

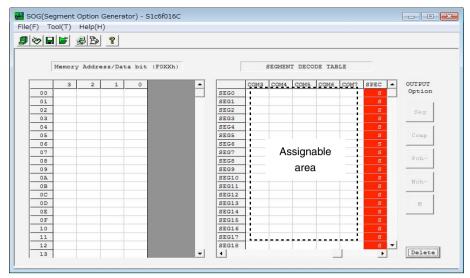

S1C6F016 provides three standard mask option models (Type B, Type E, and Type G) and a custom mask option model that allows selection of each optional specification. (See Table 1.1 and Tables 1.3.1–1.3.5.) In the custom option model, several hardware specifications are prepared in each optional item, and one of them can be selected according to the application. Use the function option generator "winfog" and segment option generator "winsog" provided as development tools of S1C6F016 for this selection. Mask pattern of the IC is finally generated based on the data created by winfog and winsog. (The mask pattern for the segment option will be generated using only the segment output specification (S) in the custom mask option data created by winsog. The segment allocation data must be programmed.)

Refer to the "S5U1C63000A Manual" for winfog and winsog.

## <Outline of the mask option>

#### (1) OSC1 oscillation circuit

The OSC1 oscillator type is fixed at crystal oscillation. Refer to "OSC1 Oscillation Circuit" in the "Oscillation Circuit and Clock Control" chapter for details.

#### (2) OSC3 oscillation circuit

The custom mask option model provides an option to select the OSC3 oscillator type from ceramic oscillation, CR oscillation (external R) and CR oscillation (built-in R). The standard mask option Type B model is configured with a ceramic oscillation circuit. The Type E and Type G models are configured with a CR oscillation circuit (external R). Refer to "OSC3 Oscillation Circuit" in the "Oscillation Circuit and Clock Control" chapter for details.

#### (3) RESET terminal pull-down resistor

The custom mask option model provides an option to select whether an internal pull-down resistor is incorporated into the RESET input port. The standard mask option models have a built-in pull-down resistor. Refer to "Reset Terminal (RESET)" in the "Initial Reset" chapter for details.

#### (4) SEG/GPIO/RFC selector

The I/O port (P20–P23, P30–P33, P40–P43) and R/F converter input/output pins are shared with the SEG36–SEG55 terminals. The custom mask option model allows selection of whether each of these pins are used for the I/O port or R/F converter or used for the SEG output. The standard mask option Type B and Type G models are configured for the I/O port or R/F converter pins. The standard mask option Type E model is configured for the SEG output pins. Refer to "Mask Option" in the "LCD Driver" chapter for details.

#### (5) I/O port pull-down resistor

The custom mask option model provides an option to select whether an internal pull-down resistor that will be enabled in input mode is incorporated into each I/O port (P00–P03, P10–P13, P20–P23, P30–P33, P40–P43, P50–P53). The standard mask option Type B and Type E models have built-in pull-down resistors for all I/O ports. The standard mask option Type G model has no built-in pull-down resistors for P10 and P11 and all other I/O ports include a pull-down resistor. Refer to "Mask Option" in the "I/O Ports" chapter for details.

#### (6) Output specification of the I/O port

The custom mask option model provides an option to select either complementary output or P-channel open drain output as the output cell type of each I/O port (P00–P03, P10–P13, P20–P23, P30–P33, P40–P43, P50–P53). The standard mask option models are configured with complementary output for all I/O ports. Refer to "Mask Option" in the "I/O Ports" chapter for details.

Do not configure the P50-P53 ports to P-channel open drain output if the R/F converter (channel 0) is used.

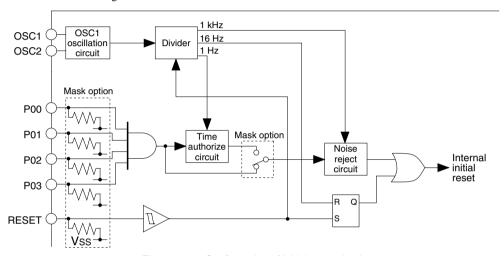

#### (7) Multiple key entry reset function (by simultaneous high input to the P0x ports)

The custom mask option model provides an option to select whether the function to reset the IC by pressing multiple keys simultaneously is implemented or not. A combination of the P0x ports (P00–P03) to be used for this function can also be selected. The standard mask option models do not have this function. Refer to "Simultaneous High Input to P0x Ports (P00–P03)" in the "Initial Reset" chapter for details.

#### (8) Time authorize circuit for the multiple key entry reset function

When the multiple key entry reset option (option (7)) is selected in the custom mask option model, the time authorize circuit can also be incorporated. The time authorize circuit measures the high pulse width of the simultaneous input signals and asserts the reset signal if it is longer than the predetermined time.

This option is not available when the multiple key entry reset option is not selected. Refer to "Simultaneous High Input to P0x Ports (P00–P03)" in the "Initial Reset" chapter for details.

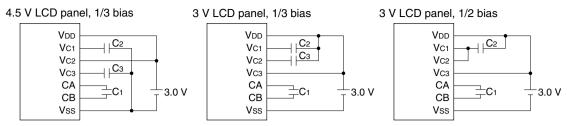

#### (9) LCD drive power supply

The custom mask option model allows use of an external power supply as the LCD drive power source. The standard mask option models support internal power supply only. Refer to "Mask Option" in the "LCD Driver" chapter for details.

#### (10) LCD segment specification

The LCD segment specification of the custom mask option model and standard mask option Type B and Type E models is fixed at LCD segment output (S). The LCD segment specification of the standard mask option Type G model is fixed at DC complementary output (C). Refer to "Mask Option" in the "LCD Driver" chapter for details.

Table 1.3.1 Option list

| Optional it              | om       | Standard Type B           | Standard Type E                                 | Standard Type G           | Custom                                    |

|--------------------------|----------|---------------------------|-------------------------------------------------|---------------------------|-------------------------------------------|

|                          |          |                           |                                                 |                           | ■ 1. Crystal (32.768 kHz)                 |

| OSC3 oscillation circuit |          | ■ 1. Crystai (32.768 KHZ) | ■ 1. Crystal (32.768 KHZ)                       | ■ 1. Crystai (32.766 KHZ) | ☐ 1. Crystar (32.766 kHz)                 |

| OSC3 oscillation circuit |          |                           | ■ 0 CD (outernal D)                             | ■ 2. CR (external R)      | □ 1. CR (built-in R) □ 2. CR (external R) |

|                          |          | = 0 Caramia (4 0 MHz)     | ■ 2. CR (external R)                            | ■ 2. CR (external R)      |                                           |

| DECET to meeting         | .1       | ■ 3. Ceramic (4.2 MHz)    | <b>=</b> 4 11                                   | <b>=</b> 4 11             | 3. Ceramic (4.2 MHz)                      |

| RESET termina            | ai puii- | ■ 1. Use                  | ■ 1. Use                                        | ■ 1. Use                  | □ 1. Use                                  |

| down resistor            | Inna     | /6                        |                                                 |                           | 2. Not Use                                |

| SEG/GPIO/                | P20      | ■ 1. I/O                  |                                                 | ■ 1. I/O                  | □ 1. I/O                                  |

| RFC selector             |          |                           | ■ 2. SEG                                        |                           | □ 2. SEG                                  |

|                          | P21      | ■ 1. I/O                  |                                                 | ■ 1. I/O                  | □ 1. I/O                                  |

|                          |          |                           | ■ 2. SEG                                        |                           | □ 2. SEG                                  |

|                          | P22      | ■ 1. I/O                  |                                                 | ■ 1. I/O                  | □ 1. I/O                                  |

|                          |          |                           | ■ 2. SEG                                        |                           | □ 2. SEG                                  |

|                          | P23      | ■ 1. I/O                  |                                                 | ■ 1. I/O                  | □ 1. I/O                                  |

|                          |          |                           | ■ 2. SEG                                        |                           | □ 2. SEG                                  |

|                          | P30      | ■ 1. I/O                  |                                                 | ■ 1. I/O                  | □ 1. I/O                                  |

|                          |          |                           | ■ 2. SEG                                        |                           | □ 2. SEG                                  |

|                          | P31      | ■ 1. I/O                  |                                                 | ■ 1. I/O                  | □ 1. I/O                                  |

|                          |          |                           | ■ 2. SEG                                        |                           | □ 2. SEG                                  |

|                          | P32      | ■ 1. I/O                  |                                                 | ■ 1. I/O                  | □ 1. I/O                                  |

|                          |          |                           | ■ 2. SEG                                        |                           | □ 2. SEG                                  |

|                          | P33      | ■ 1. I/O                  |                                                 | ■ 1. I/O                  | □ 1. I/O                                  |

|                          |          |                           | ■ 2. SEG                                        |                           | □ 2. SEG                                  |

|                          | P40      | ■ 1. I/O                  |                                                 | ■ 1. I/O                  | □ 1. I/O                                  |

|                          |          |                           | ■ 2. SEG                                        |                           | □ 2. SEG                                  |

|                          | P41      | ■ 1. I/O                  |                                                 | ■ 1. I/O                  | □ 1. I/O                                  |

|                          | ' ' '    | , 0                       | ■ 2. SEG                                        | , 0                       | □ 2. SEG                                  |

|                          | P42      | ■ 1. I/O                  |                                                 | ■ 1. I/O                  | □ 1. I/O                                  |

|                          | '-       | ,0                        | ■ 2. SEG                                        | , 0                       | □ 2. SEG                                  |

|                          | P43      | ■ 1. I/O                  | <u>= 2: 02                                 </u> | ■ 1. I/O                  | □ 1. I/O                                  |

|                          | 1 40     | _ 1.1/0                   | ■ 2. SEG                                        | <b>-</b> 1.1/0            | □ 2. SEG                                  |

|                          | P50      | ■ 1. I/O                  | <b>2</b> 2. 324                                 | ■ 1. I/O                  | □ 1. I/O                                  |

|                          | 1 30     | <b>-</b> 1.1/O            | ■ 2. SEG                                        | <b>1</b> 1.1/0            | □ 2. SEG                                  |

|                          | P51      | ■ 1. I/O                  | <b>■</b> 2. 3LG                                 | ■ 1. I/O                  | □ 1. I/O                                  |

|                          | [5]      | <b>=</b> 1. 1/O           | ■ 2. SEG                                        | <b>=</b> 1.1/O            | □ 1. 1/O                                  |

|                          | P52      | <b>=</b> 1 1/O            | <b>■</b> 2. 3EU                                 | ■ 1. I/O                  |                                           |

|                          | P32      | ■ 1. I/O                  | <b>=</b> 0.050                                  | <b>■</b> 1.1/U            | □ 1. I/O                                  |

|                          | DEO      | <b>=</b> 4 1/0            | ■ 2. SEG                                        | <b>=</b> 4 1/0            | □ 2. SEG                                  |

|                          | P53      | ■ 1. I/O                  | <b>-</b> 0 050                                  | ■ 1. I/O                  | □ 1. I/O                                  |

|                          | DEINI    | <b>=</b> 4 DEO            | ■ 2. SEG                                        | <b>=</b> 4 DEO            | □ 2. SEG                                  |

|                          | RFIN1    | ■ 1. RFC                  |                                                 | ■ 1. RFC                  | □ 1. RFC                                  |

|                          |          |                           | ■ 2. SEG                                        |                           | □ 2. SEG                                  |

|                          | REF1     | ■ 1. RFC                  |                                                 | ■ 1. RFC                  | □ 1. RFC                                  |

|                          |          |                           | ■ 2. SEG                                        |                           | □ 2. SEG                                  |

|                          | SEN1     | ■ 1. RFC                  |                                                 | ■ 1. RFC                  | □ 1. RFC                                  |

|                          |          |                           | ■ 2. SEG                                        |                           | □ 2. SEG                                  |

|                          | HUD      | ■ 1. RFC                  |                                                 | ■ 1. RFC                  | □ 1. RFC                                  |

|                          |          |                           | ■ 2. SEG                                        |                           | □ 2. SEG                                  |

| Optional it                   | em   | Standard Type B    | Standard Type E    | Standard Type G    | Custom                                                           |

|-------------------------------|------|--------------------|--------------------|--------------------|------------------------------------------------------------------|

| I/O port pull-                | P00  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | □ 1. Use                                                         |

| down resistor                 | P01  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 2. Not Use ☐ 1. Use                                            |

|                               | Doo  | <b>=</b> 4 11      | <b>=</b> 4 11      | <b>=</b> 4 11      | ☐ 2. Not Use                                                     |

|                               | P02  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 1. Use<br>☐ 2. Not Use                                         |

|                               | P03  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | □ 1. Use                                                         |

|                               | P10  | ■ 1. Use           | ■ 1. Use           | +                  | ☐ 2. Not Use ☐ 1. Use                                            |

|                               |      |                    |                    | ■ 2. Not Use       | □ 2. Not Use                                                     |

|                               | P11  | ■ 1. Use           | ■ 1. Use           | ■ 2. Not Use       | ☐ 1. Use<br>☐ 2. Not Use                                         |

|                               | P12  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | □ 1. Use                                                         |

|                               | P13  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 2. Not Use ☐ 1. Use                                            |

|                               | P20  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 2. Not Use ☐ 1. Use                                            |

|                               | 1 20 |                    | <b>1</b> 1.030     | 1.030              | □ 2. Not Use                                                     |

|                               | P21  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 1. Use<br>☐ 2. Not Use                                         |

|                               | P22  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | □ 1. Use                                                         |

|                               | P23  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 2. Not Use ☐ 1. Use                                            |

|                               |      |                    |                    |                    | ☐ 2. Not Use                                                     |

|                               | P30  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 1. Use<br>☐ 2. Not Use                                         |

|                               | P31  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | □ 1. Use                                                         |

|                               | P32  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 2. Not Use ☐ 1. Use                                            |

|                               | Doo  |                    |                    |                    | □ 2. Not Use                                                     |

|                               | P33  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | □ 1. Use<br>□ 2. Not Use                                         |

|                               | P40  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 1. Use<br>☐ 2. Not Use                                         |

|                               | P41  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | □ 1. Use                                                         |

|                               | P42  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 2. Not Use ☐ 1. Use                                            |

|                               | P43  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 2. Not Use ☐ 1. Use                                            |

|                               | P50  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 2. Not Use ☐ 1. Use                                            |

|                               |      |                    |                    |                    | □ 2. Not Use                                                     |

|                               | P51  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 1. Use<br>☐ 2. Not Use                                         |

|                               | P52  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | □ 1. Use                                                         |

|                               | P53  | ■ 1. Use           | ■ 1. Use           | ■ 1. Use           | ☐ 2. Not Use ☐ 1. Use                                            |

|                               |      |                    |                    |                    | ☐ 2. Not Use                                                     |

| I/O port output specification | P00  | ■ 1. Complementary | ■ 1. Complementary | ■ 1. Complementary | <ul><li>□ 1. Complementary</li><li>□ 2. Pch Open Drain</li></ul> |

| -                             | P01  | ■ 1. Complementary | ■ 1. Complementary | ■ 1. Complementary | ☐ 1. Complementary ☐ 2. Pch Open Drain                           |

|                               | P02  | ■ 1. Complementary | ■ 1. Complementary | ■ 1. Complementary | ☐ 1. Complementary                                               |

|                               | P03  | ■ 1. Complementary | ■ 1. Complementary | ■ 1. Complementary | ☐ 2. Pch Open Drain ☐ 1. Complementary                           |

|                               | P10  | ■ 1. Complementary | ■ 1. Complementary | ■ 1. Complementary | ☐ 2. Pch Open Drain ☐ 1. Complementary                           |

|                               |      | <u>'</u>           |                    | . ,                | ☐ 2. Pch Open Drain                                              |

|                               | P11  | ■ 1. Complementary | ■ 1. Complementary | ■ 1. Complementary | <ul><li>□ 1. Complementary</li><li>□ 2. Pch Open Drain</li></ul> |

|                               | P12  | ■ 1. Complementary | ■ 1. Complementary | ■ 1. Complementary | ☐ 1. Complementary                                               |

|                               | P13  | ■ 1. Complementary | ■ 1. Complementary | ■ 1. Complementary | ☐ 2. Pch Open Drain ☐ 1. Complementary                           |

|                               | P20  | ■ 1. Complementary | ■ 1. Complementary | ■ 1. Complementary | ☐ 2. Pch Open Drain ☐ 1. Complementary                           |

|                               |      |                    | · · ·              |                    | ☐ 2. Pch Open Drain                                              |

|                               | P21  | ■ 1. Complementary | ■ 1. Complementary | ■ 1. Complementary | <ul><li>□ 1. Complementary</li><li>□ 2. Pch Open Drain</li></ul> |

|                               | P22  | ■ 1. Complementary | ■ 1. Complementary | ■ 1. Complementary | ☐ 1. Complementary                                               |

|                               |      |                    |                    |                    | ☐ 2. Pch Open Drain                                              |

#### 1 OUTLINE

| Optional it                                 | em   | Standard Type B        | Standard Type E        | Standard Type G        | Custom                                                                                                                                                                |

|---------------------------------------------|------|------------------------|------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O port output specification               | P23  | ■ 1. Complementary     | ■ 1. Complementary     | ■ 1. Complementary     | <ul><li>□ 1. Complementary</li><li>□ 2. Pch Open Drain</li></ul>                                                                                                      |

| Specification                               | P30  | ■ 1. Complementary     | ■ 1. Complementary     | ■ 1. Complementary     | ☐ 1. Complementary                                                                                                                                                    |

|                                             | P31  | ■ 1. Complementary     | ■ 1. Complementary     | ■ 1. Complementary     | ☐ 2. Pch Open Drain ☐ 1. Complementary                                                                                                                                |

|                                             | P32  | ■ 1. Complementary     | ■ 1. Complementary     | ■ 1. Complementary     | ☐ 2. Pch Open Drain ☐ 1. Complementary                                                                                                                                |

|                                             | 1 32 | 1. Complementary       | 1. Complementary       | 1. Complementary       | ☐ 2. Pch Open Drain                                                                                                                                                   |

|                                             | P33  | ■ 1. Complementary     | ■ 1. Complementary     | ■ 1. Complementary     | ☐ 1. Complementary ☐ 2. Pch Open Drain                                                                                                                                |

|                                             | P40  | ■ 1. Complementary     | ■ 1. Complementary     | ■ 1. Complementary     | ☐ 1. Complementary ☐ 2. Pch Open Drain                                                                                                                                |

|                                             | P41  | ■ 1. Complementary     | ■ 1. Complementary     | ■ 1. Complementary     | ☐ 1. Complementary ☐ 2. Pch Open Drain                                                                                                                                |

|                                             | P42  | ■ 1. Complementary     | ■ 1. Complementary     | ■ 1. Complementary     | ☐ 1. Complementary ☐ 2. Pch Open Drain                                                                                                                                |

|                                             | P43  | ■ 1. Complementary     | ■ 1. Complementary     | ■ 1. Complementary     | ☐ 1. Complementary ☐ 2. Pch Open Drain                                                                                                                                |

|                                             | P50  | ■ 1. Complementary     | ■ 1. Complementary     | ■ 1. Complementary     | <ul><li>□ 1. Complementary</li><li>□ 2. Pch Open Drain *</li></ul>                                                                                                    |

|                                             | P51  | ■ 1. Complementary     | ■ 1. Complementary     | ■ 1. Complementary     | <ul><li>□ 1. Complementary</li><li>□ 2. Pch Open Drain *</li></ul>                                                                                                    |

|                                             | P52  | ■ 1. Complementary     | ■ 1. Complementary     | ■ 1. Complementary     | ☐ 1. Complementary ☐ 2. Pch Open Drain *                                                                                                                              |

|                                             | P53  | ■ 1. Complementary     | ■ 1. Complementary     | ■ 1. Complementary     | ☐ 1. Complementary ☐ 2. Pch Open Drain *                                                                                                                              |

| P0x port multiple entry reset com           | ,    | ■ 1. Not Use           | ■ 1. Not Use           | ■ 1. Not Use           | ☐ 1. Not Use ☐ 2. Use <p00, p01=""> ☐ 3. Use <p00, p01,="" p02=""> ☐ 4. Use <p00, p01,="" p02,="" p03=""></p00,></p00,></p00,>                                        |

| P0x port multiple entry reset time rization | ,    | ■ 1. Not Use           | ■ 1. Not Use           | ■ 1. Not Use           | ☐ 1. Not Use<br>☐ 2. Use                                                                                                                                              |

| LCD drive powersupply                       | er   | ■ 1. Internal 1/3 bias | ■ 1. Internal 1/3 bias | ■ 1. Internal 1/3 bias | ☐ 1. Internal 1/3 bias ☐ 2. Ext. 1/3 bias, VDD = VC2 (4.5 V panel) ☐ 3. Ext. 1/3 bias, VDD = VC3 (3.0 V panel) ☐ 4. Ext. 1/2 bias, VDD = VC3, VC1 = VC2 (3.0 V panel) |

☐ Selectable ■ Fixed

<sup>\*</sup> Do not select "Pch Open Drain" as the P50–P53 port output specification if the R/F converter (channel 0) is used.

Address (F0xxH) Pin COM4 COM0 COM1 COM2 СОМЗ COM5 COM6 COM7 Output specification name H L D H L D H L D SEG0 ■ S SEG1 **■**S  $\square$  N □N SFG2  $\blacksquare$ S SEG3 ■ S  $\square$  N □С  $\square$  N SEG4 ■ S SEG5 ■ S  $\Box$  C  $\square$  N □N SFG6  $\blacksquare$ S SEG7 ■ S  $\square$  N □С  $\square$  N SEG8 ■ S **■**S SEG9  $\Box$  C  $\square$  N □ N SEG10 ■ S ■ S SEG11 SEG12 ■ S □С  $\square$  N  $\square$  N SEG13 **■**S  $\Box$  C SEG14 ■ S ٦N SEG15 ■ S SEG16 ■ S  $\square$  N  $\square$  N SEG17 ■ S SEG18 ■ S  $\square$  N SEG19 ■ S  $\square$  N SEG20 ■ S  $\square$  N □N SEG21 ■ S SEG22 ■ S  $\square$  N  $\square N$ SEG23 ■ S SEG24 ■ S  $\square$  N □ N SEG25 ■ S □ C SEG26 ■ S  $\square$  N SEG27 ■ S SEG28 III S  $\square$  N SEG29 ■ S ٦N □N C SEG30 **■**S SEG31 **■**S  $\square$  N  $\square$  N SEG32  $\blacksquare$ S SEG33 **■**S  $\square$  N  $\square$  N SEG34 **■**S SEG35 ■ S  $\Box$  C  $\square$  N □N S SEG36 SEG37 ■ S  $\square$  N  $\square$  N SEG38 S SEG39 ■ S  $\square$  N □ N SEG40 ■ S ■ S SEG41 SEG42 ■ S  $\square$  N SEG43 ■ S  $\square$  N SEG44 ■ S \_ N N SEG45 S

Table 1.3.2 Segment option (standard mask option Type B)

#### Notes for using the segment option generator "winsog" (standard mask option Type B)

- 1. Any display memory address can be allocated to SEG0 to SEG35.

- 2. Always select "LCD segment output (S)" as the output specification of SEG0 to SEG35, as it is fixed at segment

<Output specification>

- 3. Configurations for nonexistent SEG pins (SEG36 to SEG55)

- Always select "LCD segment output (S)" as the output specification of SEG36 to SEG55.

- · Leave the address cells for SEG36 to SEG55 blank. (Unused addresses will be allocated.)

<address> H: RAM data high-order address (0-7)

D: Data bit (0-3)

L: RAM data low-order address (0-F)

SEG46

SEG47

SEG48

SEG49

SEG50

SEG51

SEG52

SEG53

SEG54

SFG55

$\square$  N  $\square$  N

] N □N

$\square$  N  $\square$  N

] N

$\square$  N

$\square$  N

$\square$  N

■ S

S

■ S

**S**

■ S

S

■ S

■ S

■ S

■ S

S: Segment output

C: Complementary output

N: Nch open drain output

Table 1.3.3 Segment option (standard mask option Type E)

| name SEG0 SEG1 SEG2 SEG3 SEG4 SEG5 SEG6 SEG7 SEG8 SEG9 SEG10 SEG11 SEG12 SEG13 SEG14 SEG15 SEG16 SEG16 SEG16                                                                                                                                                                                                                                                                  | H    | L    | 0<br>D   | H    | L        | D D      | H                                                | L           | D D   | H        | L | D<br>D | Н    | L     | 4<br>D | Н        | L        | D<br>D | Н   | L    | 6<br>D   | Н           | MO:<br>L | D        | Outp  S ■ S | ut specifi | □ N         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|----------|----------|--------------------------------------------------|-------------|-------|----------|---|--------|------|-------|--------|----------|----------|--------|-----|------|----------|-------------|----------|----------|-------------|------------|-------------|

| SEG0<br>SEG1<br>SEG2<br>SEG3<br>SEG4<br>SEG5<br>SEG6<br>SEG7<br>SEG8<br>SEG9<br>SEG10<br>SEG11<br>SEG12<br>SEG12<br>SEG13<br>SEG14<br>SEG14                                                                                                                                                                                                                                   | H    |      |          | H    |          |          | H                                                | L           |       | H        |   | D      | H    | L     | D      | H        | _        | D      | Н   | L    | D        | Н           | L        |          |             |            |             |

| SEG1<br>SEG2<br>SEG3<br>SEG4<br>SEG5<br>SEG6<br>SEG7<br>SEG8<br>SEG9<br>SEG10<br>SEG11<br>SEG12<br>SEG12<br>SEG13<br>SEG14<br>SEG14                                                                                                                                                                                                                                           |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          |             |            |             |

| SEG2<br>SEG3<br>SEG4<br>SEG5<br>SEG6<br>SEG7<br>SEG8<br>SEG9<br>SEG10<br>SEG11<br>SEG12<br>SEG12<br>SEG13<br>SEG14<br>SEG15                                                                                                                                                                                                                                                   |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          |             | 110        | IIN         |

| SEG3 SEG4 SEG5 SEG6 SEG7 SEG8 SEG9 SEG10 SEG11 SEG12 SEG13 SEG14 SEG15                                                                                                                                                                                                                                                                                                        |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       | -      |          |          |        |     |      |          |             |          | -        |             |            |             |

| SEG4 SEG5 SEG6 SEG7 SEG8 SEG9 SEG10 SEG11 SEG12 SEG13 SEG14 SEG15                                                                                                                                                                                                                                                                                                             |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          | ■ S         | □С         | □N          |

| SEG5<br>SEG6<br>SEG7<br>SEG8<br>SEG9<br>SEG10<br>SEG11<br>SEG12<br>SEG13<br>SEG14<br>SEG15                                                                                                                                                                                                                                                                                    |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          | ■ S         | □С         |             |

| SEG6<br>SEG7<br>SEG8<br>SEG9<br>SEG10<br>SEG11<br>SEG12<br>SEG13<br>SEG14<br>SEG15                                                                                                                                                                                                                                                                                            |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          | ■ S         | □C         | $\square$ N |

| SEG7<br>SEG8<br>SEG9<br>SEG10<br>SEG11<br>SEG12<br>SEG13<br>SEG14<br>SEG15                                                                                                                                                                                                                                                                                                    |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          | ■ S         | □С         | $\square$ N |

| SEG8<br>SEG9<br>SEG10<br>SEG11<br>SEG12<br>SEG13<br>SEG14<br>SEG15                                                                                                                                                                                                                                                                                                            |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          | ■ S         | □C         | $\square$ N |

| SEG9<br>SEG10<br>SEG11<br>SEG12<br>SEG13<br>SEG14<br>SEG15                                                                                                                                                                                                                                                                                                                    |      |      |          |      |          |          | _                                                |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          | ■ S         | □ C        | $\square$ N |

| SEG10<br>SEG11<br>SEG12<br>SEG13<br>SEG14<br>SEG15                                                                                                                                                                                                                                                                                                                            |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          | ■S          | $\Box$ C   | $\square$ N |

| SEG11<br>SEG12<br>SEG13<br>SEG14<br>SEG15                                                                                                                                                                                                                                                                                                                                     |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          | ■ S         | $\Box$ C   | $\square$ N |

| SEG12<br>SEG13<br>SEG14<br>SEG15                                                                                                                                                                                                                                                                                                                                              |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          | ■ S         | □C         | $\square$ N |

| SEG13<br>SEG14<br>SEG15                                                                                                                                                                                                                                                                                                                                                       |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          | ■ S         | □С         | $\square$ N |

| SEG14<br>SEG15                                                                                                                                                                                                                                                                                                                                                                |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          | ■ S         | □С         | □N          |

| SEG14<br>SEG15                                                                                                                                                                                                                                                                                                                                                                |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          | ■ S         | □С         | $\square$ N |

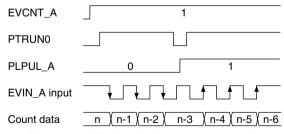

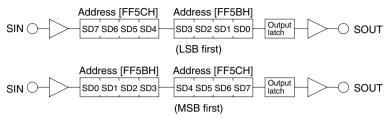

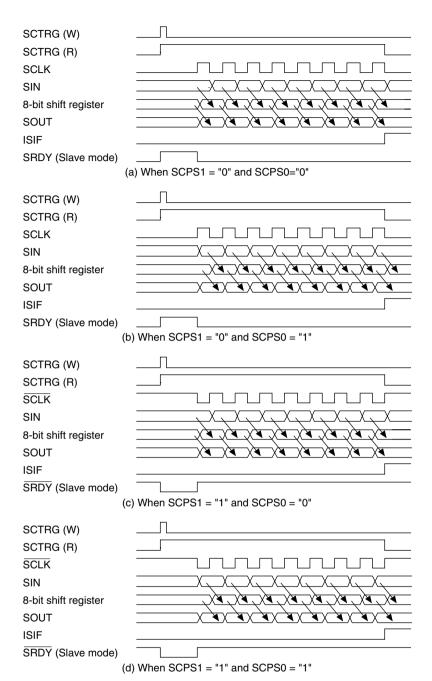

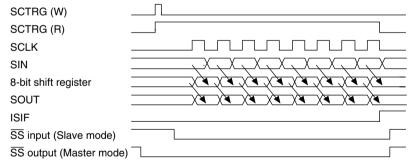

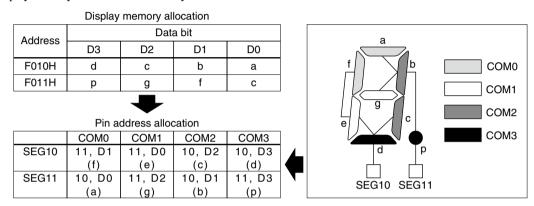

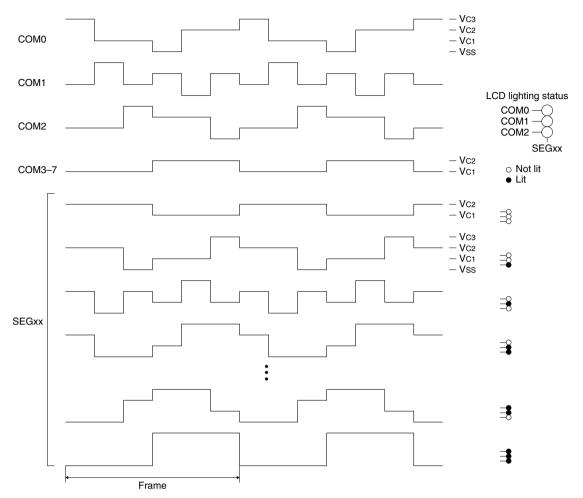

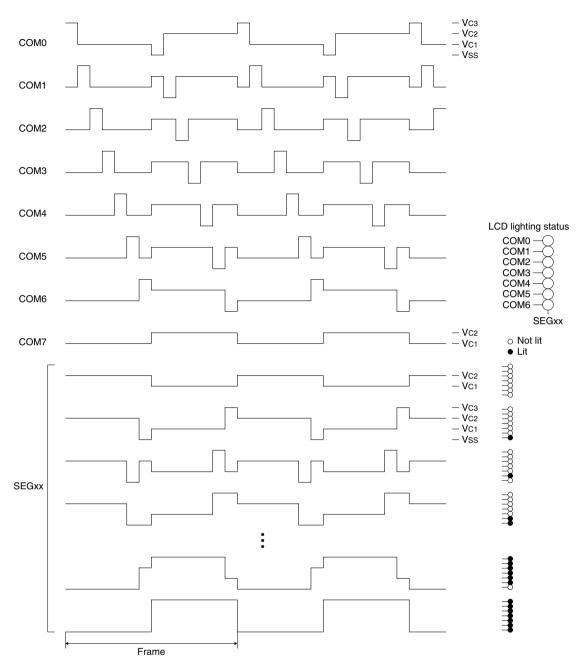

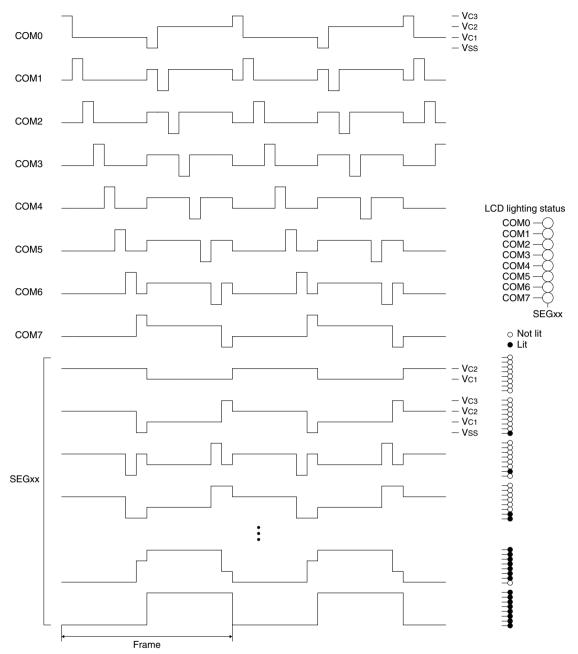

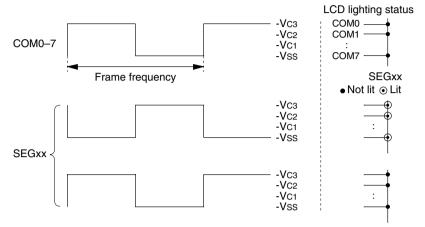

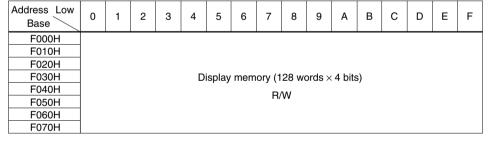

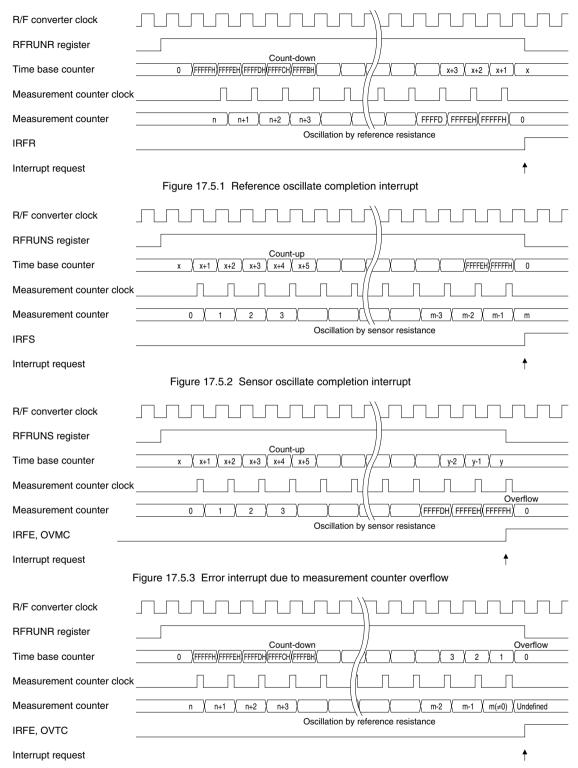

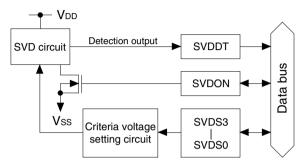

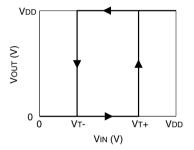

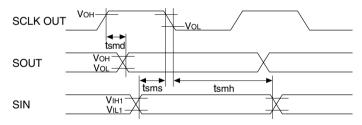

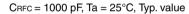

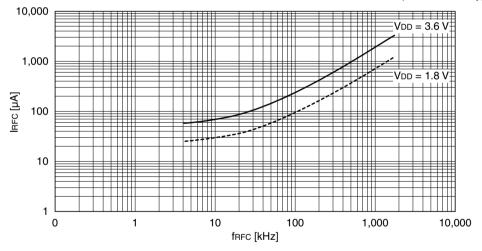

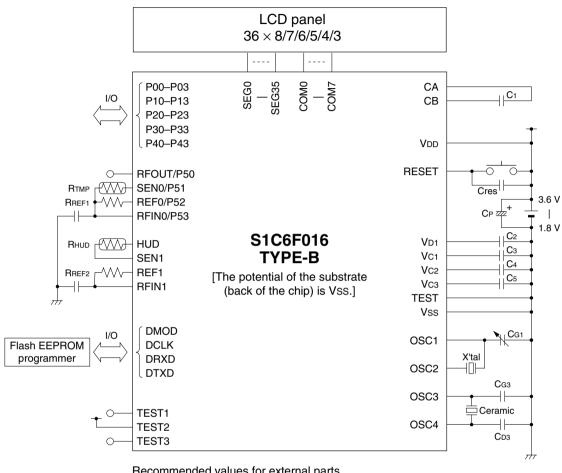

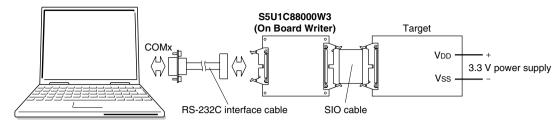

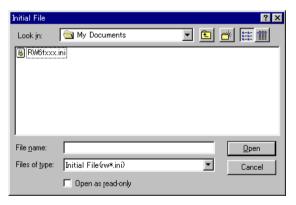

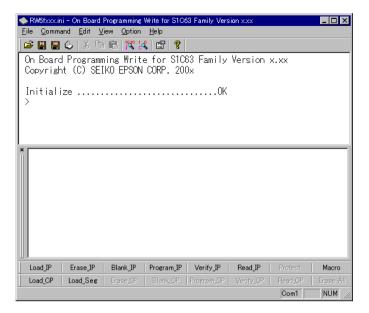

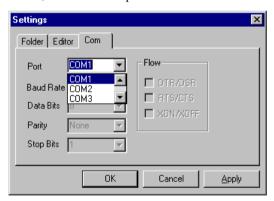

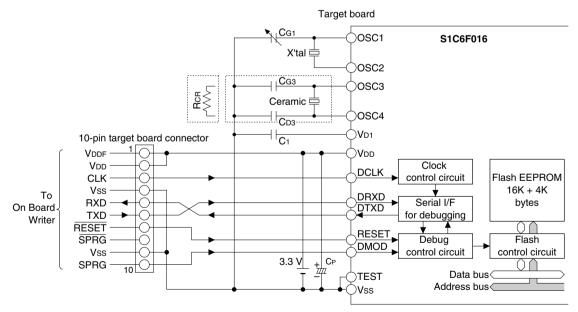

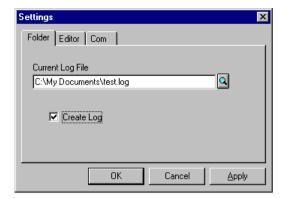

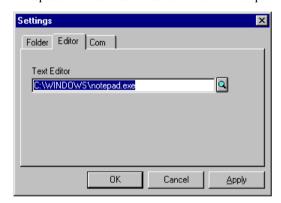

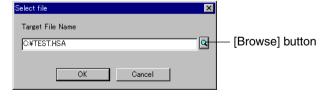

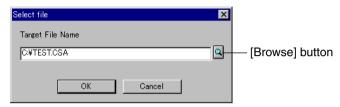

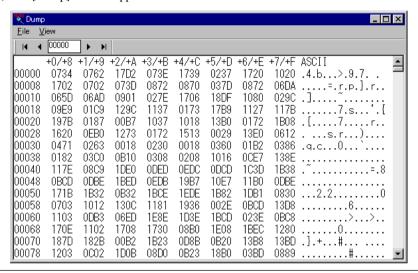

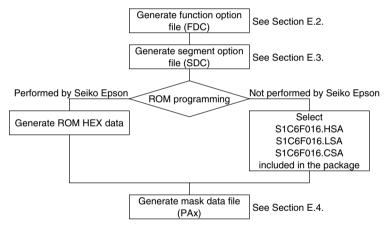

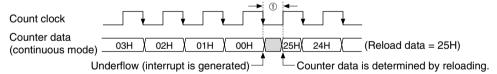

| SEG15                                                                                                                                                                                                                                                                                                                                                                         |      |      |          |      |          |          |                                                  |             |       |          |   |        |      |       |        |          |          |        |     |      |          |             |          |          | ■ S         | □С         | □N          |