#### General Description

The ADC0820 is a high speed, microprocessor compatible, 8 bit analog-to-digital converter which uses a half-flash technique to achieve a conversion time of 1.4 µs. The converter has a 0V to +5V analog input range and uses a single +5V supply.

A built-in track-and-hold function is included, eliminating the need for an external track-and-hold for input slew rates up to  $100 \text{mV}/\mu\text{s}$ .

The A/D easily interfaces with microprocessors by appearing as a memory location or I/O port without the need for external interfacing logic. Data outputs use latched, three-state buffer circuitry to allow direct connection to a microprocessor data bus or system I/O port. An over-flow output is also provided for cascading devices to achieve higher resolution.

Maxim's ADC0820 is pin-compatible with National Semiconductor's ADC0820 and provides improved specifications. It is packaged in 20-pin Small Outline, DIP and CERDIP packages.

### **Applications**

Digital Signal Processing High Speed Data Acquisition **Telecommunications** High Speed Servo Loops Audio Systems

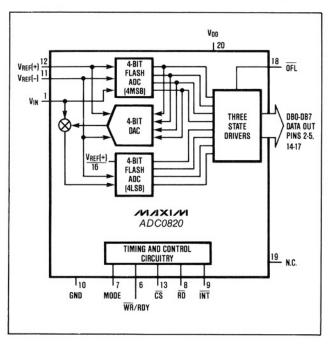

# Functional Block Diagram

#### Features

- Fast Conversion Time: 1.4 µs Max.

- **Built-in Track-and-Hold Function**

- No Missing Codes

- No User Adjustments Required

- Single +5V Supply

- No External Clock

- **Easy Interface To Microprocessors**

### Ordering Information

| PART        | TEMP. RANGE       | PIN-PACKAGE    | INL<br>(LSB) |

|-------------|-------------------|----------------|--------------|

| ADC0820BCN  | 0° C to +70° C    | 20 Plastic DIP | ±1/2         |

| ADC0820CCN  | 0° C to +70° C    | 20 Plastic DIP | ±1           |

| ADC0820CC/D | 0° C to +70° C    | Dice*          | ±1           |

| ADC0820BCM  | 0° C to +70° C    | 20 SO          | ±1/2         |

| ADC0820CCM  | 0° C to +70° C    | 20 SO          | ±1/2         |

| ADC0820BCJ  | -40° C to +85° C  | 20 CERDIP      | ±1/2         |

| ADC0820CCJ  | -40° C to +85° C  | 20 CERDIP      | ±1           |

| ADC0820BJ   | -55° C to +125° C | 20 CERDIP**    | ±1/2         |

| ADC0820CJ   | -55° C to +125° C | 20 CERDIP**    | ±1           |

<sup>\*</sup>Dice are specified at  $T_A = +25$ °C.

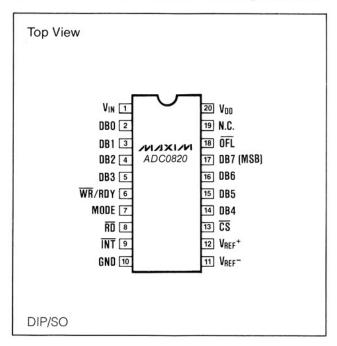

# Pin Configuration

MIXIM

Maxim Integrated Products 1

<sup>\*\*</sup>Contact factory

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>DD</sub> to GND              | Operating Temperature Ranges              |

|-----------------------------------------------------|-------------------------------------------|

| Voltage at any other pins                           | ADC0820BC_/CC0°C to +70°C                 |

| (Pins 1–9, 11–19) GND – 0.3V, V <sub>DD</sub> +0.3V | ADC0820BCJ/CCJ40°C to +85°C               |

| Output current (Pin 19)                             | ADC08020BJ/CJ55°C to +125°C               |

| Power Dissipation (Any Package) to +75°C 450mW      | Storage Temperature Range65°C to +160°C   |

| Derate Above +25°C by 6mW/°C                        | Lead Temperature (soldering, 10sec)+300°C |

| 04                                                  | , , , , , , , , , , , , , , , , , , , ,   |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect the device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +5V, V_{REF}^+ = +5V, V_{REF}^- = GND, RD-MODE, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted})$

| PARAMETER                                         | SYMBOL            | CONDITI                                                                         | ONS                                                             | MIN.               | TYP. | MAX.                  | UNITS |

|---------------------------------------------------|-------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------|------|-----------------------|-------|

| ACCURACY                                          |                   |                                                                                 |                                                                 |                    |      |                       |       |

| Resolution                                        |                   |                                                                                 |                                                                 | 8                  |      |                       | bits  |

| Total Unadjusted Error (Note 1)                   |                   | ADC0820B<br>ADC0820C                                                            |                                                                 |                    |      | ±1/2<br>±1            | LSB   |

| No Missing Codes Resolution                       |                   |                                                                                 |                                                                 | 8                  |      |                       | bits  |

| REFERENCE INPUT                                   |                   | -                                                                               |                                                                 |                    |      |                       |       |

| Reference Resistance                              |                   | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub> |                                                                 | 1.4<br>1.25        | 2.2  | 4.0<br>4.0            | kΩ    |

| V <sub>REF</sub> <sup>+</sup> Input Voltage Range |                   |                                                                                 |                                                                 | V <sub>REF</sub> - |      | V <sub>DD</sub> + 0.1 | V     |

| V <sub>REF</sub> - Input Voltage Range            |                   |                                                                                 |                                                                 | GND - 0.1          |      | V <sub>REF</sub> +    | V     |

| ANALOG INPUT                                      | •                 |                                                                                 |                                                                 |                    |      |                       |       |

| Analog Input Voltage Range                        | V <sub>INR</sub>  |                                                                                 |                                                                 | GND - 0.1          |      | V <sub>DD</sub> + 0.1 | V     |

| Analog Input Capacitance                          | C <sub>VIN</sub>  |                                                                                 |                                                                 |                    | 45   |                       | pF    |

| Analog Input Current                              | I <sub>VIN</sub>  | V <sub>IN</sub> = 0V to +5V                                                     | T <sub>A</sub> = +25°C,<br>T <sub>MIN</sub> to T <sub>MAX</sub> |                    |      | ±0.3<br>±3            | μΑ    |

| Slew Rate, Tracking (Note 2)                      | SR                |                                                                                 |                                                                 |                    | 0.2  | 0.1                   | V/μs  |

| LOGIC INPUTS                                      |                   |                                                                                 |                                                                 |                    |      |                       |       |

| Input HIGH Voltage                                | V <sub>INH</sub>  | CS, WR, RD<br>MODE                                                              |                                                                 | 2.0<br>3.5         |      |                       | ٧     |

| Input LOW Voltage                                 | V <sub>INL</sub>  | CS, WR, RD<br>MODE                                                              |                                                                 |                    |      | 0.8<br>1.5            | ٧     |

| 3                                                 |                   | CS, RD;                                                                         | T <sub>A</sub> = +25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub>  |                    |      | 0.1<br>1              |       |

| Input High Current                                | I <sub>INH</sub>  | WR;                                                                             | T <sub>A</sub> = +25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub>  |                    |      | 0.3<br>3              | μΑ    |

|                                                   |                   | MODE;                                                                           | T <sub>A</sub> = +25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub>  |                    | 50   | 150<br>200            |       |

| Input Low Current                                 | I <sub>INL</sub>  | CS, RD, WR, MODE                                                                | T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub>   |                    |      | -0.3<br>-1            | μΑ    |

| Input Capacitance (Note 3)                        | C <sub>IN</sub>   | CS, RD, WR, MODE                                                                |                                                                 |                    | 5    | 8                     | pF    |

| LOGIC OUTPUTS                                     |                   |                                                                                 |                                                                 |                    |      |                       |       |

| Output HIGH Voltage                               | V <sub>OH</sub>   | DB0-DB7, OFL, INT<br>V <sub>DD</sub> = +4.75V I<br>V <sub>DD</sub> = +4.75V I   | <sub>OUT</sub> = -360μΑ<br><sub>OUT</sub> = -10μΑ               | 4.0<br>4.5         |      |                       | ٧     |

| Output LOW Voltage                                | V <sub>OL</sub>   | DB0-DB7, OFL, INT, F<br>V <sub>DD</sub> = +4.75V                                | RDY<br>OUT = 1.6mA                                              |                    |      | 0.4                   | ٧     |

| Three-state Output Current                        |                   | DB0-DB7, RDY                                                                    | T <sub>A</sub> = +25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub>  | -0.3<br>-3         |      | +0.3<br>+3            | μΑ    |

| Output Capacitance (Note 3)                       | C <sub>OUT</sub>  | DB0-DB7, OFL, INT, F                                                            | RDY                                                             |                    | 5    | 8                     | pF    |

| Output Source Current                             | I <sub>SRC</sub>  | DB0-DB7, OFL, INT; V                                                            | / <sub>OUT</sub> = 0                                            |                    | -25  | -10                   | mA    |

| Output Sink Current                               | I <sub>SINK</sub> | DB0-DB7, OFL, INT, P                                                            | RDY; VOUT = VDD                                                 |                    | 40   | 15                    | mA    |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +5V, V_{REF}^+ = +5V, V_{REF}^- = GND, RD-MODE, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted})$

| PARAMETER                | SYMBOL          | CONDITIONS                                                                                                                                         | MIN. | TYP.  | MAX.     | UNITS |

|--------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------|-------|

| POWER SUPPLY             |                 |                                                                                                                                                    |      |       |          |       |

| Supply Voltage           | V <sub>DD</sub> | ±5% for Specified Performance                                                                                                                      | T    | 5     |          | V     |

| Supply Current           | I <sub>DD</sub> | $\overline{\text{CS}} = \overline{\text{WR}} = \overline{\text{RD}} = 0$ $T_{\text{A}} = +25^{\circ}\text{C}$ $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |      | 5     | 10<br>15 | mA    |

| Power Dissipation        |                 | CS=WR=RD=0                                                                                                                                         |      | 25    |          | mW    |

| Power Supply Sensitivity | PSS             | V <sub>DD</sub> = ±5%                                                                                                                              |      | ±1/16 | ±1/4     | LSB   |

#### **TIMING CHARACTERISTICS**

$(V_{DD} = +5V, V_{REF}^{+} = +5V, V_{REF}^{-} = GND, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise specified. See Note 2, 4.)}$

| PARAMETER                                          | SYMBOL              | CONDITIONS                                        | T <sub>A</sub> = +25°C |                          | ADC0820BCX<br>ADC0820CCX |      | ADC0820BJ<br>ADC0820CJ   |      | UNITS                 |    |

|----------------------------------------------------|---------------------|---------------------------------------------------|------------------------|--------------------------|--------------------------|------|--------------------------|------|-----------------------|----|

|                                                    |                     |                                                   | MIN.                   | TYP.                     | MAX.                     | MIN. | MAX.                     | MIN. | MAX.                  |    |

| CS to RD, WR Setup Time                            | t <sub>CSS</sub>    |                                                   | 0                      |                          |                          | 0    |                          | 0    |                       | ns |

| CS to RD, WR Hold Time                             | t <sub>CSH</sub>    |                                                   | 0                      |                          |                          | 0    |                          | 0    |                       | ns |

| CS to RDY Delay                                    | t <sub>RDY</sub>    | $C_L = 50pF, R = 3k\Omega$                        |                        | 35                       | 70                       |      | 90                       |      | 100                   | ns |

| Conversion Time (RD Mode)                          | t <sub>CRD</sub>    | (Note 7)                                          |                        | 1.2                      | 1.6                      |      | 2.0                      |      | 2.5                   | μs |

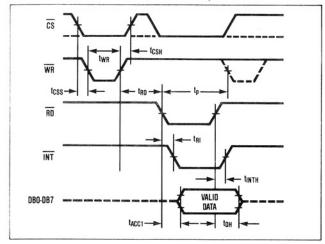

| Data Access Time (RD Mode)<br>(See Figure 1)       | t <sub>ACC0</sub>   | (Note 5)                                          |                        | t <sub>CRD</sub><br>+ 10 | t <sub>CRD</sub><br>+ 35 |      | t <sub>CRD</sub><br>+ 50 |      | t <sub>CRD</sub> + 70 | ns |

| RD to INT Delay (RD Mode)                          | t <sub>INTH</sub>   | C <sub>L</sub> = 50pF                             |                        | 60                       | 125                      |      | 175                      |      | 225                   | ns |

| Data Hold Time                                     | t <sub>DH</sub>     | (Note 6)                                          |                        | 40                       | 90                       |      | 120                      |      | 150                   | ns |

| Delay Time<br>Between Conversions                  | tp                  |                                                   | 500                    |                          |                          | 600  |                          | 600  |                       | ns |

| Write Pulse Width                                  | t <sub>WR</sub>     |                                                   | 600                    |                          | 50,000                   | 600  | 50,000                   | 600  | 50,000                | ns |

| Conversion Time<br>(WR-RD Mode)                    | t <sub>CWR-RD</sub> |                                                   | 1.4                    |                          |                          | 1.56 |                          | 1.62 |                       | μS |

| Delay between WR and RD Pulses                     | t <sub>RD</sub>     |                                                   | 600                    |                          |                          | 700  |                          | 700  |                       | ns |

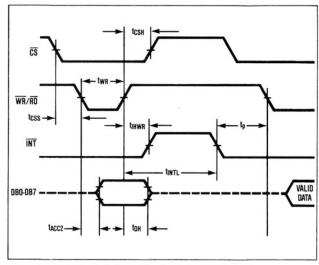

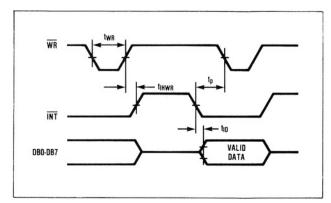

| Data Access Time<br>(WR-RD Mode)<br>(See Figure 3) | t <sub>ACC1</sub>   | t <sub>RD</sub> < t <sub>INTL</sub>               |                        | 110                      | 220                      |      | 280                      |      | 350                   | ns |

| RD to INT Delay                                    | t <sub>RI</sub>     |                                                   |                        | 100                      | 200                      |      | 260                      |      | 320                   | ns |

| WR to INT Delay                                    | t <sub>INTL</sub>   |                                                   |                        | 600                      | 1000                     |      | 1400                     |      | 1700                  | ns |

| Data Access Time<br>(WR-RD Mode)<br>(See Figure 2) | t <sub>ACC2</sub>   | t <sub>RD</sub> > t <sub>INTL</sub> ,<br>(Note 6) |                        | 60                       | 100                      |      | 130                      |      | 160                   | ns |

| WR to INT Delay<br>(Stand-Alone)                   | t <sub>IHWR</sub>   | C <sub>L</sub> = 50pF                             |                        | 70                       | 100                      |      | 130                      |      | 150                   | ns |

| Data Access Time After INT                         | t <sub>ID</sub>     |                                                   |                        | 10                       | 50                       |      | 65                       |      | 75                    | ns |

Note 1: Total unadjusted error includes offset, full-scale and linearity errors.

Note 2: Sample tested at +25°C by Quality Assurance to ensure compliance.

Note 3: Guaranteed by design.

Note 4: All input control signals are specified with t<sub>R</sub> = t<sub>F</sub> = 20ns (10% to 90% of +5V) and timed from a voltage level of 1.6V.

Note 5: Defined as the time required for an output to cross 0.8V or 2.4 V.

Note 6: Defined as the time required for the data lines to change 0.5V.

Note 7: For faster conversions use WR-RD Mode.

### **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                               |

|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>IN</sub> | Analog input; range = GND < V <sub>IN</sub> < V <sub>DD</sub> .                                                                        |

| 2   | DB0             | Three-state data output, bit 0 (LSB).                                                                                                  |

| 3   | DB1             | Three-state data output, bit 1.                                                                                                        |

| 4   | DB2             | Three-state data output, bit 2.                                                                                                        |

| 5   | DB3             | Three-state data output, bit 3.                                                                                                        |

| 6   | WR/RDY          | WRITE control input/READY status output. See Digital Interface section.                                                                |

| 7   | MODE            | Mode selection input. This input is internally pulled low with a 50µA current source.  RD Mode: MODE low/open.  WR-RD Mode: MODE high. |

| 8   | RD              | READ input. RD must be low to access data. See Digital Interface section.                                                              |

| 9   | ĪNT             | INTERRUPT output. INT going low indicates the completion of a conversion. See Digital Interface section.                               |

| 10  | GND             | Ground.                                                                                                                                |

# **Digital Interface**

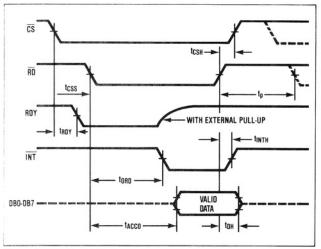

#### RD Mode (Pin 7 Low)

A conversion is started by taking  $\overline{\text{RD}}$  low and keeping it low until output data appears (Figure 1). Pin 6 (WR/RDY) is configured as a status output (RDY) in this mode, and is used with microprocessors which can be forced into a WAIT state. The processor starts a conversion, waits, and then reads data with a single READ instruction. RDY, an open collector output, goes low after the falling edge of  $\overline{\text{CS}}$  and goes high impedance at the end of the conversion. INT goes low at the end of the conversion and returns high on the rising edge of  $\overline{\text{CS}}$  or  $\overline{\text{RD}}$ .

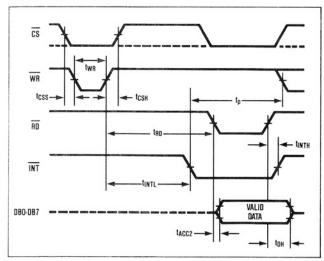

#### WR-RD Mode (Pin 7 High)

In the WR-RD mode, pin 6  $(\overline{WR}/RDY)$  is the WRITE input for the converter. With  $\overline{CS}$  low, a conversion starts on the falling edge of  $\overline{WR}$ . There are several options for reading data:

#### Using the Internal Delay

The processor waits for  $\overline{\text{INT}}$  to go low before reading data (Figure 2).  $\overline{\text{INT}}$  typically goes low 600ns after the rising edge of  $\overline{\text{WR}}$ , indicating that the conversion is complete. With CS low, DB0-DB7 are read by pulling  $\overline{\text{RD}}$  low.  $\overline{\text{INT}}$  is then reset on the rising edge of  $\overline{\text{CS}}$  or  $\overline{\text{RD}}$ .

#### Reading Before Delay

The conversion time is externally controlled with  $\overline{\text{RD}}$  (Figure 3). The status of  $\overline{\text{INT}}$  is ignored and  $\overline{\text{RD}}$  is taken low as soon as 600ns after the rising edge of

| V <sub>REF</sub> <sup>+</sup> CS DB4 | Lower limit of reference span. Sets the zero code voltage. Range: GND to V <sub>REF</sub> <sup>+</sup> .  Upper limit of reference span. Sets the Full Scale input voltage. Range: V <sub>REF</sub> <sup>-</sup> to V <sub>DD</sub> .  CHIP-SELECT input. CS must be low for the device to recognize WR or RD inputs  Three-state data output, bit 4. |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS<br>DB4                            | Scale input voltage. Range: V <sub>REF</sub> <sup>-</sup> to V <sub>DD</sub> .  CHIP-SELECT input. CS must be low for the device to recognize WR or RD inputs                                                                                                                                                                                         |

| DB4                                  | device to recognize WR or RD inputs                                                                                                                                                                                                                                                                                                                   |

|                                      | Three-state data output, bit 4.                                                                                                                                                                                                                                                                                                                       |

| 1 (125) LONGO                        |                                                                                                                                                                                                                                                                                                                                                       |

| DB5                                  | Three-state data output, bit 5.                                                                                                                                                                                                                                                                                                                       |

| DB6                                  | Three-state data output, bit 6.                                                                                                                                                                                                                                                                                                                       |

| DB7                                  | Three-state data output, bit 7 (MSB).                                                                                                                                                                                                                                                                                                                 |

| OFL                                  | Overflow Output. If the analog input is greater than V <sub>REF</sub> <sup>+</sup> , OFL will be high at the end of the conversion. It can be used to cascade two or more devices to increase resolution.                                                                                                                                             |

| N.C.                                 | Test Pin. Do not connect.                                                                                                                                                                                                                                                                                                                             |

| V <sub>DD</sub>                      | Power supply voltage, +5V.                                                                                                                                                                                                                                                                                                                            |

|                                      | DB7<br>OFL                                                                                                                                                                                                                                                                                                                                            |

WR. This <u>completes</u> the conversion and enables DB0-DB7. INT goes low after the <u>falling edge</u> of RD and is reset on the rising edge of RD or CS.

#### **Pipelined Operation**

"Pipelined" operation is achieved by tying WR and RD together (Figure 4). With CS low, taking WR and RD low starts a new conversion and, at the same time, reads the result of the previous conversion.

#### Stand-Alone Operation

In stand-alone operation,  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  are  $\underline{\text{tied}}$  low and a conversion is initiated by pulling  $\overline{\text{WR}}$  low (Figure 5). Output data is valid approximately 600ns after the rising edge of  $\overline{\text{WR}}$ .

#### **Analog Considerations**

#### Reference Input

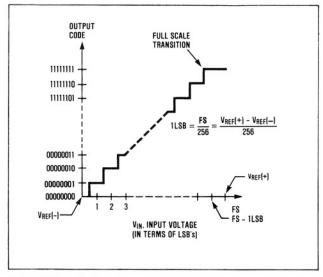

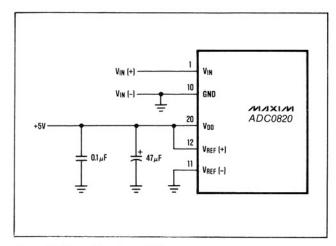

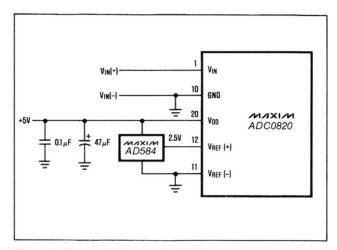

The  $V_{REF}(+)$  and  $V_{REF}(-)$  inputs of the converter set the full-scale and zero input voltages. The voltage at  $V_{REF}(-)$  defines the input level which produces an output code of all zeroes, and the voltage at  $V_{REF}(+)$  defines the input which produces an output code of all ones (see Figure 6). Figure 7 shows some reference configurations.

#### Bypassing

A  $47\mu F$  electrolytic and  $0.1\mu F$  ceramic capacitor should be used to bypass the  $V_{DD}$  pin to GND. The lead length of these capacitors should be as short as possible. If the reference inputs (pins 11, 12) are driven by long lines, they also should be bypassed to GND with  $0.1~\mu F$  capacitors at the reference input pins.

Figure 1. RD Mode Timing

Figure 2. WR-RD Mode Timing  $(t_{RD} > t_{INTL})$

Figure 3. WR-RD Mode Timing  $(t_{RD} < t_{INTL})$

Figure 4. WR-RD Mode Pipe-Lined Timing,  $\overline{WR} = \overline{RD}$

Figure 5. WR-RD Mode Stand-Alone Timing,  $\overline{CS} = \overline{RD} = 0$

Figure 6. Transfer Function

Figure 7a. Power Supply as Reference

#### Input Current

The ADC0820 analog input behaves somewhat differently from conventional A/D converters. The ADC0820 takes varying amounts of current from the input depending on the operating cycle of the A/D.

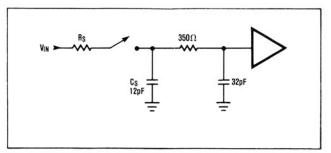

During the input sampling phase  $(\overline{WR} = LOW)$  in the (WR-RD) Mode) input capacitors must be charged to the input voltage through the resistance of internal analog switches (about  $2k\Omega$  to  $5k\Omega$ ). In addition, about 12pF of stray capacitance  $(C_S)$  must be charged. An equivalent RC model of the input is shown in Figure 8. The 45pF input capacitance allows source resistances  $(R_S)$  of up to  $1k\Omega$  to be used without increased settling time. For larger resistances, the width of the  $\overline{WR}$  pulse must be increased from 600ns. In the RD mode, where the sample time is fixed,  $R_S$  greater than  $1k\Omega$  may cause settling errors. In this case, use the WR-RD mode and greater than 600ns  $\overline{RD}$  time, or use a buffer to drive the analog input.

#### Input Filtering

The ADC0820's sampled data comparators generate input transients at  $V_{IN}$ . This does not degrade performance since the A/D only "looks" at the input after these transients occur. It is not necessary to filter these transients with an external capacitor at the  $V_{IN}$  terminal.

#### Inherent Track-and-Hold

The ADC0820 can measure a variety of high speed input signals without the help of an external sample-and-hold. The input is tracked from the time  $\overline{WR}$  goes low (in the WR-RD mode) to approximately 100ns after it returns high. Input signals with slew rates typically up to  $200\text{mV}/\mu\text{s}$  can be converted without error.

Figure 7b. External Reference 2.5V Full Scale

Figure 8. Equivalent Input Model

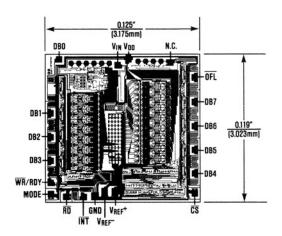

### Chip Topography

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

# AMEYA360 Components Supply Platform

# **Authorized Distribution Brand:**

# Website:

Welcome to visit www.ameya360.com

# Contact Us:

# > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

# > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

# Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com