#### **General Description**

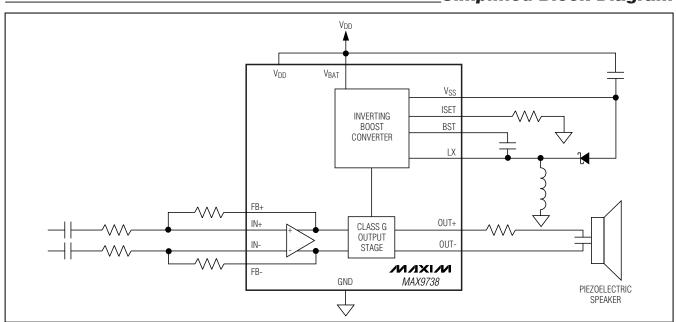

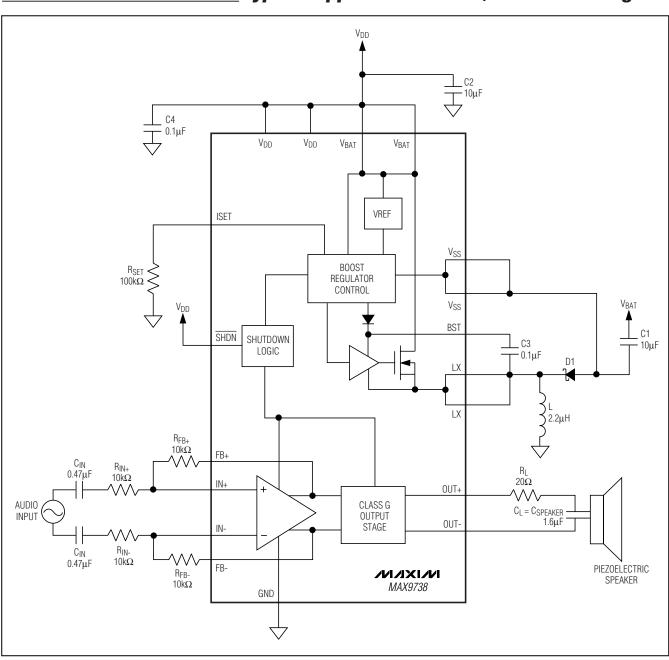

The MAX9738 features a mono Class G power amplifier with an integrated inverting boost converter. The Class G amplifier is specifically designed to drive the high capacitance of a ceramic/piezoelectric loudspeaker. The inverting boost converter can typically supply up to 400mA of peak output current, allowing for a constant output of 16VP-P over the 2.7V to 5.5V supply voltage range.

The MAX9738 maximizes battery life by offering high-performance efficiency. Maxim's proprietary output stage provides efficiency levels greater than Class AB devices without the EMI penalties commonly associated with Class D amplifiers.

The MAX9738 is ideally suited to deliver the high output voltage swing required to drive ceramic/piezoelectric speakers.

The device utilizes fully differential inputs and outputs, comprehensive click-and-pop suppression, shutdown control, and soft-start circuitry. The MAX9738 is fully specified over the -40°C to +85°C extended temperature range and is available in an ultra-small, lead-free 5x4 WLP (2.5mm x 2mm) package.

Typical Application Circuit/Functional Diagram and Pin Configuration appear at end of data sheet.

#### \_\_\_\_\_Features

- ♦ Integrated Inverting Boost Converter

- ♦ 2.7V to 5.5V Single-Supply Operation

- ♦ 16Vp-p Output Voltage Swing, Ideal for Driving a Ceramic Speaker

- Maintains Output Voltage Swing as the Battery Decays

- ♦ Clickless/Popless Operation

- ♦ Small, Thermally Efficient 5x4 WLP Package (2.5mm x 2mm)

#### **Applications**

Cellular Phones Smartphones MP3 Players Personal Media Players Handheld Gaming Consoles

Notebook Computers

#### **Ordering Information**

| PART            | TEMP RANGE     | PIN-<br>PACKAGE |

|-----------------|----------------|-----------------|

| MAX9738EWP+TG45 | -40°C to +85°C | 5x4 WLP         |

+Denotes a lead-free package.

T = Tape and reel.

G45 indicates protective die coating.

#### Simplified Block Diagram

Maxim Integrated Products

#### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages with respect to GND.)     |                                         |

|-------------------------------------|-----------------------------------------|

| VDD, VBAT                           | 0.3V to +6V                             |

| V <sub>DD</sub> to V <sub>BAT</sub> | 0.1V to +0.1V                           |

| Vss                                 | Capacitor Connection Only,              |

|                                     | (V <sub>BAT</sub> - 10V) to +0.3V       |

| OUT+, OUT                           | 6V to (V <sub>DD</sub> + 0.3V)          |

| (OUT+ to OUT-)                      | 8.7V to +8.7V                           |

| ÎN+, IN-, FB+, FB-, ISET            | 0.3V to (V <sub>DD</sub> + 0.3V)        |

| LX                                  | $(V_{DD} - 11.5V)$ to $(V_{DD} + 0.3V)$ |

| BST                                 | (LX - 0.3V) to (LX + 6V)                |

| SHDN                                | 0.3V to +6V                             |

|                                     |                                         |

| Continuous Current into/out of                                 |                 |

|----------------------------------------------------------------|-----------------|

| OUT+, OUT-, VBAT, VSS, VDD                                     | 400mA           |

| Any Other Pin                                                  | 20mA            |

| Duration of OUT+, OUT- Short Circuit to                        |                 |

| V <sub>DD</sub> , GND, V <sub>SS</sub> (V <sub>SS</sub> > -6V) | Continuous      |

| RMS Current per Bump                                           |                 |

| V <sub>BAT</sub> , LX                                          | 800mA           |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )          |                 |

| 20-Bump UCSP (derate 10mW/°C above +70                         |                 |

| Operating Temperature Range                                    | 40°C to +85°C   |

| Junction Temperature                                           | +150°C          |

| Storage Temperature Range                                      | -65°C to +150°C |

| Bump Temperature (soldering) Reflow                            |                 |

| = -                                                            |                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD}=V_{BAT}=\overline{SHDN}=3.6V, GND=0V, V_{DD}-V_{SS}=9V, R_{ISET}=100k\Omega, R_{IN+}=R_{IN-}=10k\Omega, R_{FB+}=R_{FB-}=10k\Omega, C_{L}=open, R_{L}=\infty, C_{L}=10\mu F, C_{L}=10\mu$

| PARAMETER                          | SYMBOL          | CONDITIONS                                                                | MIN    | TYP  | MAX  | UNITS |

|------------------------------------|-----------------|---------------------------------------------------------------------------|--------|------|------|-------|

| PARAMETER                          | STWIDOL         | CONDITIONS                                                                | IVIIIN | 117  | WAA  | UNITS |

| GENERAL                            |                 |                                                                           |        |      |      |       |

| Supply Voltage Range               | $V_{DD}$        | Inferred from PSRR test                                                   | 2.7    |      | 5.5  | V     |

| Total Quiescent Current            | IDD_TOT         | I <sub>VDD</sub> + I <sub>VBAT</sub> (boost converter disabled)           |        | 7    | 12.5 | mA    |

| Maximum Total Quiescent<br>Current | IDD_TOT_MAX     | Typical application circuit (Note 2)                                      |        | 16.5 |      | mA    |

| Shutdown Supply Current            | ISHDN           | SHDN = GND                                                                |        | 0.6  | 2    | μΑ    |

| Turn-On Time                       | t <sub>ON</sub> | Time from shutdown or power-on to full operation ( $C_{IN} = 0.1 \mu F$ ) |        | 10   |      | ms    |

| ISET Bias Voltage                  | VISET           |                                                                           | 0.9    | 1.0  | 1.1  | V     |

| Thermal Shutdown Threshold         |                 |                                                                           |        | 150  | •    | °C    |

| Thermal Shutdown Hysteresis        |                 |                                                                           |        | 15   |      | °C    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=V_{BAT}=\overline{SHDN}=3.6V, GND=0V, V_{DD}-V_{SS}=9V, R_{ISET}=100k\Omega, R_{IN+}=R_{IN-}=10k\Omega, R_{FB+}=R_{FB-}=10k\Omega, C_L=open, R_L=\infty, C_1=10\mu F, C_2=10\mu F, C_3=0.1\mu F, C_4=0.1\mu F, T_A=T_{MIN}\ to\ T_{MAX}, unless otherwise noted. Typical values are at T_A=+25°C.) (Note 1)$

| PARAMETER                      | SYMBOL                            | CONDITIONS                                                                                                       |                                            | MIN  | TYP  | MAX  | UNITS              |  |

|--------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------|------|------|--------------------|--|

| SPEAKER AMPLIFIER              |                                   | <u> </u>                                                                                                         |                                            |      |      |      |                    |  |

| Output Offset Voltage          | Voc                               | \/ 0.7\/ or F. F\/                                                                                               | T <sub>A</sub> = +25°C                     |      | ±3.7 | ±15  | m\/                |  |

| Output Offset Voltage          | Vos                               | $V_{DD} = 2.7V \text{ or } 5.5V$                                                                                 | $T_{MIN} \le T_A \le T_{MAX}$              |      |      | ±30  | mV                 |  |

| Input DC Bias Voltage          | V <sub>BIAS</sub>                 | (Note 3)                                                                                                         |                                            | 1.0  | 1.23 | 1.5  | V                  |  |

| Common-Mode Output Level       | V <sub>CM</sub>                   | $V_{DD} = 2.7V$                                                                                                  |                                            | 0.75 | 1.17 | 1.60 | V                  |  |

| Common-wode Output Level       | V CM                              | $V_{DD} = 5.5V$                                                                                                  | 2.40 3 3.4                                 |      | 3.45 | v    |                    |  |

| Click-and-Pop Level            | K <sub>CP</sub>                   | Peak voltage into/out of shutdown,<br>A-weighted, 32 samples per second<br>(Note 4)                              |                                            |      | -60  |      | dBV                |  |

| Voltage Gain                   | Av                                | V <sub>DD</sub> = 2.7V (Note 5)                                                                                  |                                            | 11.5 | 12   | 12.5 | dB                 |  |

| Continuous Output Power        | Pout                              | $V_{BAT} = V_{DD} = 2.7V \text{ or } 5$<br>THD+N = 1%                                                            | $1.5$ V, $R_{LOAD} = 8\Omega$ ,            |      | 0.25 |      | W                  |  |

| Output Voltage                 |                                   | THD+N < 1%, $C_{IN}$ = 0.1 $\mu$ F, $C_L$ = 1.6 $\mu$ F, $R_L$ = 20 $\Omega$ , $T_A$ = +25 $^{\circ}$ C (Note 6) | $V_{BAT} = V_{DD} =$ 2.7V, f = 1kHz        |      | 5.5  |      | - V <sub>RMS</sub> |  |

|                                | Vout                              |                                                                                                                  | $V_{BAT} = V_{DD} =$ 2.7V, f = 10kHz       |      | 5.0  |      |                    |  |

|                                |                                   |                                                                                                                  | $V_{BAT} = V_{DD} =$ 3.6V, f = 1kHz        | 5.65 | 6.3  |      |                    |  |

|                                |                                   |                                                                                                                  | $V_{BAT} = V_{DD} =$ 3.6V, f = 10kHz       | 5.37 | 6.0  |      |                    |  |

| Common-Mode Rejection<br>Ratio | CMRR                              | f <sub>IN</sub> = 1kHz (Note 7)                                                                                  |                                            |      | 60   |      | dB                 |  |

|                                |                                   | $V_{DD} = 2.7V \text{ to } 5.5V$                                                                                 |                                            | 54   | 60   |      |                    |  |

| Davies Commission Daties       | DODD                              | f = 217Hz, 100mV <sub>P-P</sub> ripple                                                                           |                                            |      | 80   |      | j<br>-ID           |  |

| Power-Supply Rejection Ratio   | PSRR                              | f = 1kHz, 100mV <sub>P-P</sub> ripple                                                                            |                                            |      | 70   |      | dB                 |  |

|                                |                                   | $f = 20kHz$ , $100mV_{P-P}$ rip                                                                                  | ople                                       |      | 60   |      |                    |  |

| Total Harmonic Distortion Plus | TUD. N                            | $ f = 1 \text{kHz}, V_{OUT} = 16 V_{P-P}, C_L = 1.6 \mu F, \\ R_L = 20 \Omega $                                  |                                            |      | 0.2  | 0.5  | 0/                 |  |

| Noise                          | THD+N                             | $f = 10kHz, V_{OUT} = 15.2$<br>$R_L = 20\Omega$                                                                  | V <sub>P-P</sub> , C <sub>L</sub> = 1.6μF, | 0.4  |      | - %  |                    |  |

| Peak Load Current              |                                   |                                                                                                                  |                                            |      | 355  |      | mA                 |  |

| Signal-to-Noise Ratio          | SNR                               | V <sub>OUT</sub> = 5V <sub>RMS</sub> , A-weighted (Note 6)                                                       |                                            |      | 95   |      | dB                 |  |

| Dynamic Range                  | DR                                | A-weighted (Note 8)                                                                                              |                                            |      | 110  |      | dB                 |  |

| SHDN Input Threshold           | VIH                               |                                                                                                                  |                                            | 1.4  |      |      | V                  |  |

| טוטוא ווויףענ דוויפאווטוע      | V <sub>IL</sub>                   | _ 0                                                                                                              |                                            | 0.4  | v    |      |                    |  |

| SHDN Input Leakage Current     | I <sub>IH</sub> , I <sub>IL</sub> |                                                                                                                  |                                            | -3   |      | +3   | μΑ                 |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=V_{BAT}=\overline{SHDN}=3.6V,\ GND=0V,\ V_{DD}-V_{SS}=9V,\ R_{ISET}=100k\Omega,\ R_{IN+}=R_{IN-}=10k\Omega,\ R_{FB+}=R_{FB-}=10k\Omega,\ C_L=open,\ R_L=\infty,\ C_1=10\mu F,\ C_2=10\mu F,\ C_3=0.1\mu F,\ C_4=0.1\mu F,\ T_A=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.\ Typical\ values\ are\ at\ T_A=+25^{\circ}C.)\ (Note\ 1)$

| PARAMETER                         | SYMBOL                                 | CONDITIONS                                                           | MIN    | TYP  | MAX  | UNITS             |

|-----------------------------------|----------------------------------------|----------------------------------------------------------------------|--------|------|------|-------------------|

|                                   | 1                                      |                                                                      | IVIIIN | ITP  | WAX  | UNITS             |

| INVERTING BOOST CONVER            | TER (V <sub>DD</sub> - V <sub>SS</sub> | = -8.75V)                                                            |        |      |      | 1                 |

| Switching Frequency               |                                        |                                                                      |        |      | 1.5  | MHz               |

| FET On-Time                       | tFON                                   |                                                                      | 550    | 750  | 950  | ns                |

| Minimum FET Off-Time              |                                        |                                                                      | 100    | 220  | 350  | ns                |

| Peak Output Current               |                                        | V <sub>DD</sub> > 3V, typical application circuit (Note 9)           |        | 400  |      | mA                |

| FET Current Limit (DC)            |                                        | $T_A = +25^{\circ}C \text{ (Note 10)}$                               | 0.77   | 1.1  | 1.35 | А                 |

| FET Current Limit (Transient)     |                                        | Typical application circuit, inductor I <sub>SAT</sub> rating > 1.7A |        | 1.6  |      | А                 |

| FET On-Resistance                 | R <sub>DSON</sub>                      | $I_{LX} = 100 \text{mA}, T_A = +25 ^{\circ}\text{C}$                 |        | 0.2  | 0.26 | Ω                 |

| Regulated Output Voltage          |                                        | V <sub>BAT</sub> - V <sub>SS</sub>                                   | 8.15   | 8.9  | 9.60 | V                 |

| Transient Load Regulation         |                                        | 0 to 400mA load step, typical application circuit                    |        | 300  |      | mV                |

| Maximum Output Ripple             |                                        | I <sub>LOAD</sub> = 20mA, typical application circuit                |        | 200  |      | mV <sub>P-P</sub> |

| BST Shutdown Leakage              |                                        | SHDN = 0V, LX = 0V, BST = 5V                                         |        | 0.01 | 1    | μΑ                |

| V <sub>BAT</sub> Shutdown Current |                                        | $V_{BAT} = V_{DD}$ , $\overline{SHDN} = 0V$ , $LX = 0V$ , $BST = 5V$ |        | 0.01 | 3    | μA                |

| LX Shutdown Leakage               |                                        | $LX = 0V, \overline{SHDN} = 0V, BST = 5V$                            |        | 0.01 | 3    | μΑ                |

- **Note 1:** All devices are 100% production tested at  $T_A = +25^{\circ}C$ . Specifications over temperature limits are guaranteed by design.

- **Note 2:** Total quiescent current depends on overall efficiency and varies with the LX inductor value and ESR, diode turn-on voltage, and the parasitic losses in all external components.

- **Note 3:** Input DC bias voltage determines the maximum voltage swing of the input signal. An input signal with an amplitude greater than the input DC bias voltage results in clipping.

- Note 4: Amplifier inputs AC-coupled to GND.

- Note 5: Voltage gain is defined as [VouT+ VouT-]/[VIN+ VIN-].

- **Note 6:** VouT is defined as [VouT+ VouT-].

- Note 7: Matching of external AC-coupling input capacitors and gain resistors is critical to achieving good CMRR.

- **Note 8:** Dynamic range calculated by measuring the RMS voltage difference between a -60dBFS output signal and the noise floor, then adding 60dB. Full scale is defined as the output signal needed to achieve 1% THD+N.

- Note 9: Peak output current depends on external power-supply components and the signal frequency.

- **Note 10:** Boost converter current limit is tested with a DC sweep. Actual current-limit values under transient conditions may be higher. At high input supply, V<sub>BAT</sub>, and low inductance, L, transient current limit might be higher than 1.7A.

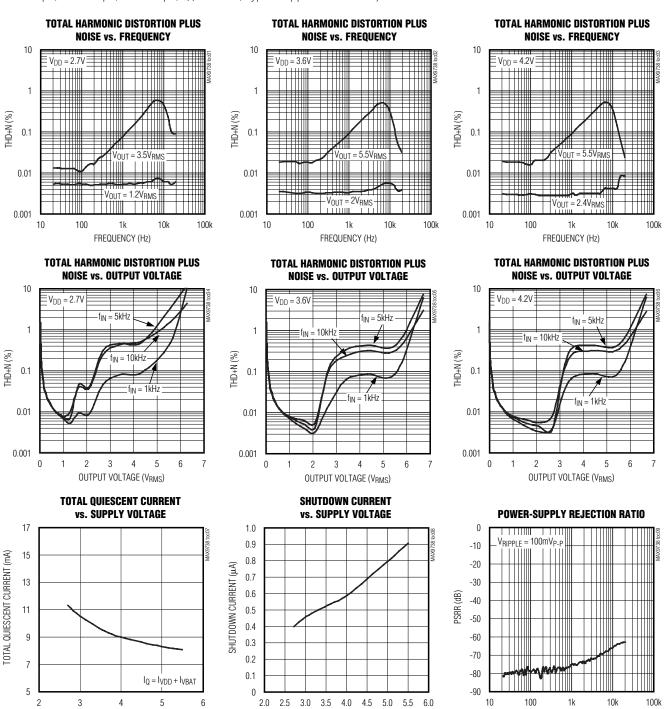

#### **Typical Operating Characteristics**

$(V_{DD} = V_{BAT} = \overline{SHDN} = +3.6V, \ GND = 0V, \ R_{ISET} = 100k\Omega, \ R_{IN+} = R_{IN-} = 10k\Omega, \ R_{FB+} = R_{FB-} = 10k\Omega, \ C_L = 1.6\mu F, \ R_L = 20\Omega, \ C_1 = 10\mu F, \ C_2 = 10\mu F, \ C_3 = 0.1\mu F, \ C_4 = 0.1\mu F, \ T_A = +25^{\circ}C, \ Typical \ Application \ Circuit.)$

SUPPLY VOLTAGE (V)

SUPPLY VOLTAGE (V)

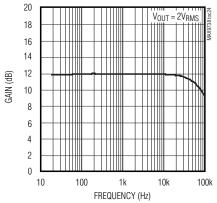

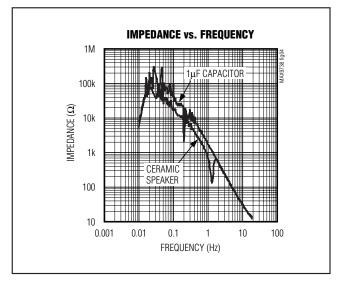

FREQUENCY (Hz)

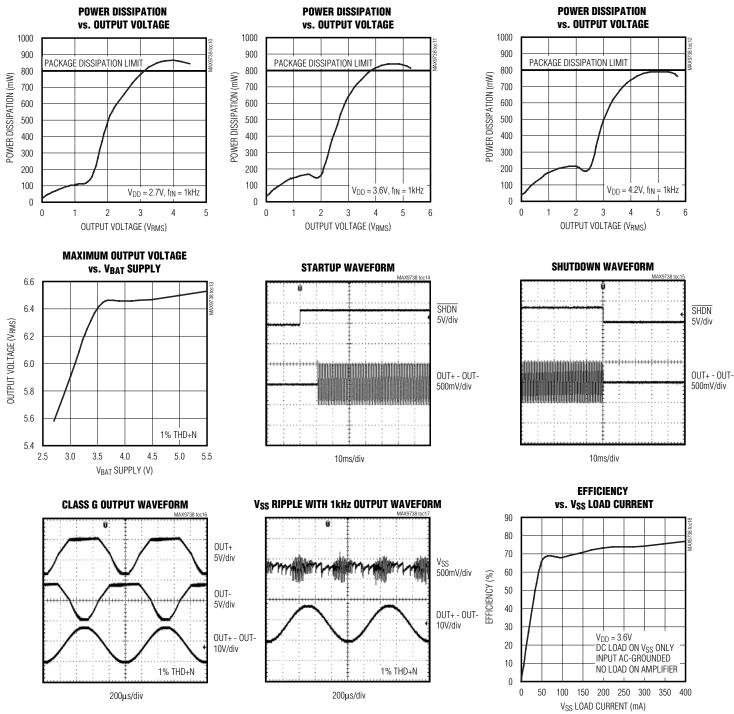

#### Typical Operating Characteristics (continued)

$(V_{DD} = V_{BAT} = \overline{SHDN} = +3.6V, \ GND = 0V, \ R_{ISET} = 100k\Omega, \ R_{IN+} = R_{IN-} = 10k\Omega, \ R_{FB+} = R_{FB-} = 10k\Omega, \ C_L = 1.6\mu F, \ R_L = 20\Omega, \ C_1 = 10\mu F, \ C_2 = 10\mu F, \ C_3 = 0.1\mu F, \ C_4 = 0.1\mu F, \ T_A = +25^{\circ}C, \ Typical \ Application \ Circuit.)$

#### Typical Operating Characteristics (continued)

$(V_{DD} = V_{BAT} = \overline{SHDN} = +3.6V, GND = 0V, R_{ISET} = 100k\Omega, R_{IN+} = R_{IN-} = 10k\Omega, R_{FB+} = R_{FB-} = 10k\Omega, C_L = 1.6\mu F, R_L = 20\Omega, C1 = 10\mu F, C2 = 10\mu F, C3 = 0.1\mu F, C4 = 0.1\mu F, T_A = +25^{\circ}C, \textit{Typical Application Circuit.})$

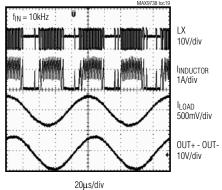

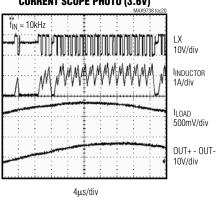

#### BOOST CONVERTER-INDUCTOR CURRENT SCOPE PHOTO (3.6V)

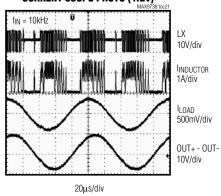

#### BOOST CONVERTER-INDUCTOR CURRENT SCOPE PHOTO (3.6V)

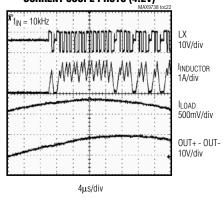

#### BOOST CONVERTER-INDUCTOR CURRENT SCOPE PHOTO (4.2V)

BOOST CONVERTER-INDUCTOR CURRENT SCOPE PHOTO (4.2V)

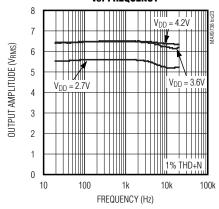

## OUTPUT AMPLITUDE vs. FREQUENCY

#### FREQUENCY RESPONSE

#### **Pin Description**

| PIN    | NAME             | FUNCTION                                                                                                                                                   |

|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2 | V <sub>BAT</sub> | Battery Connection. Bypass to GND with a 10µF ceramic capacitor.                                                                                           |

| A3     | SHDN             | Active-Low Shutdown. Connect to VDD for normal operation.                                                                                                  |

| A4     | FB-              | Negative Polarity Amplifier Feedback                                                                                                                       |

| A5     | IN-              | Negative Polarity Amplifier Input                                                                                                                          |

| B1, B2 | LX               | Inverting-Boost Inductor Connection. Connect a 1.5µH to 2.2µH inductor between LX and GND.                                                                 |

| B4     | FB+              | Positive Polarity Amplifier Feedback                                                                                                                       |

| B5     | IN+              | Positive Polarity Amplifier Input                                                                                                                          |

| C1     | BST              | Boost Flying Capacitor Connection. Connect a 0.1µF capacitor between BST and LX.                                                                           |

| C2, C4 | V <sub>SS</sub>  | Class G Amplifier Negative Power-Supply Input. Connect to inverting boost converter output node. Bypass $V_{\rm BAT}$ with a 10 $\mu$ F ceramic capacitor. |

| C5     | ISET             | Boost Current Set. Connect a 100kΩ resistor from ISET to GND.                                                                                              |

| D1, D5 | V <sub>DD</sub>  | Power-Supply Input. Connect to V <sub>BAT</sub> .                                                                                                          |

| D2     | OUT-             | Negative Polarity Amplifier Output                                                                                                                         |

| D3     | GND              | Ground                                                                                                                                                     |

| D4     | OUT+             | Positive Polarity Amplifier Output                                                                                                                         |

#### **Detailed Description**

The MAX9738 Class G power amplifier with inverting boost converter is the latest in linear amplifier technology. The Class G output stage offers improved performance over a Class AB amplifier while increasing efficiency to extend battery life. The integrated inverting boost converter generates a negative supply capable of delivering up to 400mA. The negative supply is only used when the output signal requires a larger supply voltage differential. As the battery voltage drops, the boost converter output becomes more negative to maintain amplifier output swing all the way down to  $V_{\rm BAT} = 2.7V$ .

The Class G output stage and the inverting boost converter allow the MAX9738 to deliver a 16V<sub>P-P</sub> voltage swing, up to four times greater than a Class AB amplifier.

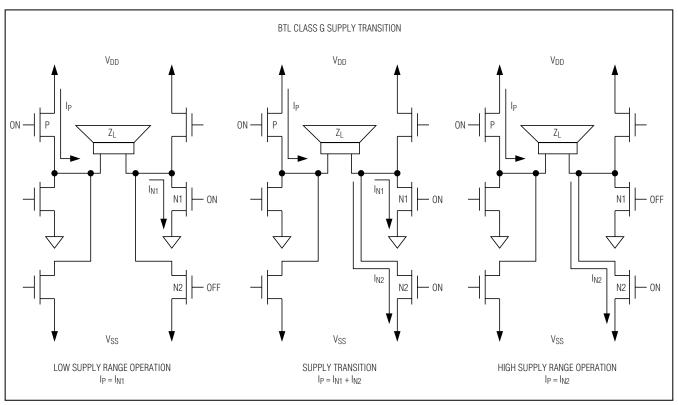

#### Class G Operation

The MAX9738 Class G amplifier is a linear amplifier that operates within a low (V<sub>DD</sub> to GND) and high (V<sub>DD</sub> to V<sub>SS</sub>) supply range. Figure 1 illustrates the transition from the low to high supply range. For small signals, the device operates within the lower (V<sub>DD</sub> to GND) supply range. In this range, the operation of the device is identical to a traditional single-supply Class AB amplifier where:

ILOAD = IN1

As the output signal increases so a wider supply is needed, the device begins its transition to the higher supply range (VDD to VSS) for the large signals. To ensure a seamless transition between the low and high supply ranges, both of the lower transistors are on so that:

$$I_{1} OAD = I_{N1} + I_{N2}$$

As the output signal continues to increase, the transition to the high supply is complete. The device then operates from the higher supply range, where the operation of the device is identical to a traditional dual-supply Class AB amplifier where:

$$I_{LOAD} = I_{N2}$$

During operation, the output common-mode voltage of the MAX9738 adjusts dynamically as the device transitions between supply ranges.

Utilizing a Class G output stage with an inverting boost converter allows the MAX9738 to realize a 17.5Vp-p output swing with a 5V supply. A traditional Class AB amplifier would need to be powered with a ±5V supply to generate the same output swing at half the efficiency of the Class G.

8 \_\_\_\_\_\_ /V|X|/M

Figure 1. Class G Supply Transition

#### **Inverting Boost Converter**

The MAX9738 features an integrated inverting boost converter with an on-chip n-channel MOSFET to provide an inverted supply rail that can supply up to 400mA over the +2.7V to +5.5V positive supply range. The boost converter generates the negative supply rail (VSS) needed to create the higher supply range that allows the output of the device to operate over a greater dynamic range as the battery supply collapses over time. The converter uses a constant on-time, pulse-frequency modulation (PFM) architecture. The integrated MOSFET and the built-in soft-start function reduce the number of external components required while controlling inrush currents. The inverting boost regulator achieves soft-start by decreasing both peak inductor current limit and the constant on-time until Vss voltage reaches 90% of its regulation level.

#### PFM Controller Block

An error amplifier compares the output voltage to an internal target voltage. Once the output voltage is smaller than the regulation level, the controller sets a flip-flop, turning on the n-channel MOSFET and applying the battery voltage across the inductor. The current through the inductor ramps up linearly, storing energy in its magnetic field. Once the on-time timer expires, or the inductor current reaches the current limit, the controller resets the flip-flop and turns off the MOSFET. Since the inductor current is continuous, a transverse potential develops across the inductor that turns on the diode (D1). This discharge condition forces the current through the inductor to ramp back down, transferring the energy stored in the magnetic field to the output capacitor and the load. The MOSFET remains off until the minimum off-time is expired or the output voltage is above the regulation level.

#### **Shutdown Mode**

The MAX9738 has a shutdown mode that reduces power consumption and extends battery life. Driving SHDN low places the MAX9738 in a low-power (0.6µA) shutdown mode. Connect SHDN to VDD for normal operation.

#### Click-and-Pop Suppression

The MAX9738 Class G amplifier features Maxim's comprehensive, industry-leading click-and-pop suppression. During startup, the click-and-pop suppression circuitry eliminates any audible transient sources internal to the device.

#### Applications Information

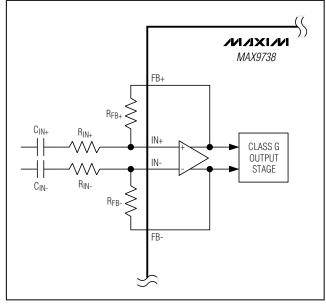

#### **Differential Input Amplifier**

The MAX9738 features a differential input configuration, making the device compatible with many CODECs, and offering improved noise immunity over a single-ended input amplifier. In devices such as PCs, noisy digital signals can be picked up by the amplifier's input traces. The signals appear at the amplifiers' inputs as common-mode noise. A differential input amplifier amplifies the difference of the two inputs, and signals common to both inputs are canceled out. When configured for differential inputs, the voltage gain of the MAX9738 is set by:

$$A_V = 20\log[4 \times (\frac{R_{FB}}{R_{IN}})] (dB)$$

where A<sub>V</sub> is the desired voltage gain in dB.  $R_{IN+}$  should be equal to  $R_{IN-}$ , and  $R_{FB+}$  should be equal to  $R_{FB-}$ . The Class G output stage has a fixed gain of 4V/V (12dB). Any gain or attenuation set by the external input stage resistors add to or subtract from this fixed gain. See Figure 2.

In differential input configurations, the common-mode rejection ratio (CMRR) is primarily limited by the external resistor and capacitor matching. Ideally, to achieve the highest possible CMRR the following external components should be selected where:

$$\frac{R_{FB+}}{R_{IN+}} = \frac{R_{FB-}}{R_{IN-}}$$

and

$$C_{\mathsf{IN+}} = C_{\mathsf{IN-}}$$

Figure 2. Gain Setting

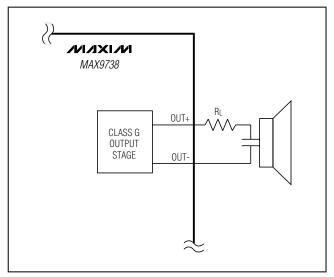

#### **Driving a Ceramic Speaker**

Applications that require a thin profile, such as today's mobile phones, demand that components have a small form factor. Dynamic loudspeakers that use a cone and voice coil typically cannot conform to the height requirements. The option for these applications is to use a ceramic/piezoelectric loudspeaker.

Ceramic speakers are much more capacitive than a conventional loudspeaker. Typical capacitance values for such a speaker can be greater than 1 $\mu$ F. High peakto-peak voltage drive is required to achieve acceptable sound pressure levels. The high output voltage requirement coupled with the capacitive nature of the speaker demand that the amplifier supply much more current at high frequencies than at lower frequencies. Above 5kHz the typical speaker impedance can be less than 20 $\Omega$ .

The MAX9738 is ideal for driving a capacitive ceramic speaker. The high boost converter current limit allows for a flat frequency response out to 20kHz while maintaining high output voltage swings. Figure 3 shows a typical circuit for driving a ceramic speaker.

A  $20\Omega$  series resistance is required between the amplifier output and the ceramic speaker load to ensure the output of the amplifier sees some fixed resistance at high frequencies when the speaker is essentially an electrical short.

Figure 3. Driving a Ceramic Speaker

#### **Component Selection**

#### Input Coupling Capacitors (CIN\_)

The AC-coupling capacitors ( $C_{IN}$ ) and input resistors ( $R_{IN}$ ) form highpass filters that remove any DC bias from an input signal (see the *Typical Application Circuit/Functional Diagram*).  $C_{IN}$  blocks the input signal source from appearing at the amplifier outputs. The -3dB point of the highpass filter, assuming zero source impedance due to the input signal source, is given by:

$$f_{-3dB} = \frac{1}{2\pi \times R_{IN} \times C_{IN}} (Hz)$$

Ceramic speakers generally perform best at frequencies greater than 1kHz. To reduce low-frequency distortion that may be added by the ceramic speakers low-frequency response, select a C<sub>IN</sub> such that the f-3dB closely matches the low-frequency response of the ceramic speaker. Use capacitors with low-voltage coefficient dielectrics. Aluminum electrolytic, tantalum, or film dielectric capacitors are good choices for AC-coupling capacitors. Capacitors with high-voltage coefficients, such as ceramics (non-COG dielectrics), can result in increased distortion at low frequencies.

#### Boost Converter Output Capacitor Selection (C1)

The total output voltage ripple has two components: the capacitive ripple caused by the charging and

discharging of the output capacitance, and the voltage drop across the capacitor's ESR caused by the current into and out of the capacitor. The worst-case voltage ripple is:

$$\begin{split} &V_{VSS\_RIPPLE} = V_{VSS\_RIPPLE(C)} + V_{VSS\_RIPPLE(ESR)} \\ &V_{VSS\_RIPPLE(C)} = \frac{I_{L\_RIPPLE^2} \times L1}{2 \times C1 \times V_{SS}} \times t_{FON} \text{ and} \\ &V_{VSS\_RIPPLE(ESR)} = I_{L\_RIPPLE(ESR)} \times R_{ESR} \text{ where} \\ &I_{L\_RIPPLE} = \frac{V_{BAT}}{1.1} \times t_{FON} \end{split}$$

where IL\_RIPPLE is the inductor ripple current. For ceramic capacitors, the output voltage ripple is typically dominated by Vvss\_RIPPLE(C). The voltage rating and temperature characteristics of the output capacitor must also be considered. Note that all ceramic capacitors typically have large temperature coefficients and bias voltage coefficients. The actual capacitor value in the circuit is typically significantly less than the stated value.

#### Input Filter Capacitor (C2)

The input capacitor reduces the current peaks drawn from the input supply and reduces noise injection into the IC. A 10µF ceramic capacitor is recommended for the *Typical Applications Circuit/Functional Diagram* because of the high-source impedance seen in typical lab setups. Actual applications usually have much lower source impedance since the step-up regulator often runs directly from a battery. Typically, the input capacitance can be reduced below 10µF.

#### **Boost Flying Capacitor (C3)**

A bootstrap circuit that uses an external flying capacitor between LX and BST provides the supply voltage for the internal n-channel MOSFET driver. A 0.1µF or larger ceramic capacitor provides sufficient current for the internal MOSFET driver supply.

#### **Inductor Selection**

The MAX9738 operates with a standard 2.2µH inductor for the entire range of supply voltages and load currents. The inductor must have a saturation (incremental) current (ISAT) rating greater than the peak switching current. Choose an inductor that has a higher ISAT rating than the given FET Current Limit (Transient) specification in the *Electrical Characteristics* table. Temperature characteristics of the inductor's saturation current must also be considered.

#### Rectifier Diode Selection

The MAX9738's high-switching frequency demands a high-speed rectifier. Schottky diodes are recommended for most applications because of their fast recovery time and low forward voltage. In general, a 1A to 2A Schottky diode complements the internal MOSFET.

#### Ceramic Speaker Impedance Characteristics

A  $1\mu F$  capacitor is a good model for the ceramic speaker as it best approximates the impedance of a ceramic speaker over the audio band. When selecting a capacitor to simulate a ceramic speaker, the capacitor's voltage rating must be equal to or higher than the expected amplifier output voltage swing.

#### **Series Load Resistor**

The capacitive nature of the ceramic speaker results in very low impedances at high frequencies. To prevent the ceramic speaker from shorting the amplifier output at high frequencies, a series load resistor must be used. The output load resistor and the ceramic speaker create a lowpass filter. To set the rolloff frequency of the output filter, the approximate capacitance of the speaker must be known. This information can be obtained from bench testing or from the ceramic speaker manufacturer. Set the lowpass filter cutoff frequency with the following equation:

$$f_{LP} = \frac{1}{2\pi \times R_{L} \times C_{SPEAKER}} (Hz)$$

Increasing the value of R<sub>L</sub> decreases the amount of high-frequency audio content sent to the speaker, but improves the MAX9738's power dissipation. Lowering

Figure 4. Ceramic Speaker and Capacitor Impedance

the value of R<sub>L</sub> burdens the amplifier output stage with more power dissipation. An R<sub>L</sub> of  $20\Omega$  is a good compromise between power dissipation and frequency response when coupled with a typical ceramic speaker.

#### \_WLP Applications Information

For the latest application details on WLP construction, dimensions, tape carrier information, PCB techniques, bump-pad layout, and recommended reflow temperature profile, as well as the latest information on reliability testing results, go to the Maxim website at www.maximic.com/ucsp for Application Note 1891: *UCSP—A Wafer-Level Chip-Scale Package*.

#### Typical Application Circuit/Functional Diagram

#### **Pin Configuration** TOP VIEW (BUMP SIDE DOWN) MIXIM MAX9738 3 SHDN $V_{\text{BAT}}$ $V_{\mathsf{BAT}}$ В IN+ ISET OUT+ $V_{\text{DD}}$ OUT-GND $V_{DD}$ **20-BUMP WLP**

Chip Information

PROCESS: BICMOS

#### Package Information

For the latest package outline information, go to **www.maxim-ic.com/packages**.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 5x4 WLP      | W202A2+1     | <u>21-0059</u> |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

# AMEYA360 Components Supply Platform

#### **Authorized Distribution Brand:**

#### Website:

Welcome to visit www.ameya360.com

#### Contact Us:

#### > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

#### > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

#### Customer Service :

Email service@ameya360.com

### Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com