# LMR14203 SIMPLE SWITCHER® 42Vin, 0.3A Step-Down Voltage Regulator in SOT-23

Check for Samples: LMR14203

#### **FEATURES**

- Input Voltage Range of 4.5V to 42V

- Output Voltage Range of 0.765V to 34V

- Output Current up to 0.3A

- 1.25 MHz Switching Frequency

- Low Shutdown Iq, 16 μA Typical

- Short Circuit Protected

- Internally Compensated

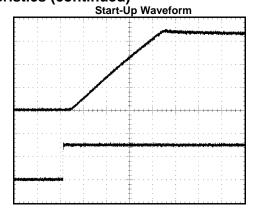

- Soft-Start Function

- Thin SOT-23-6 Package (2.97 x 1.65 x 1mm)

- Fully Enabled for WEBENCH® Power Designer

## **PERFORMANCE BENEFITS**

- Tight Accuracy for Powering Digital ICs

- Extremely Easy to Use

- Tiny Overall Solution Reduces System Cost

#### **APPLICATIONS**

- Point-of-Load Conversions from 5V, 12V, and 24V Rails

- Space Constrained Applications

- Battery Powered Equipment

- Industrial Distributed Power Applications

- Power Meters

- Portable Hand-Held Instruments

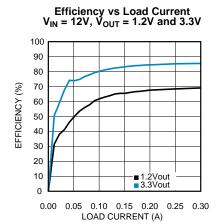

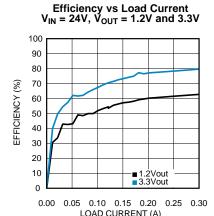

#### **System Performance**

#### **DESCRIPTION**

The LMR14203 is a PWM DC/DC buck (step-down) regulator. With a wide input range from 4.5V-42V, it is suitable for a wide range of applications such as power conditioning from unregulated sources. They feature a low  $R_{\rm DSON}$  (0.9 $\Omega$  typical) internal switch for maximum efficiency (85% typical). Operating frequency is fixed at 1.25 MHz allowing the use of small external components while still being able to have low output voltage ripple. Soft-start can be implemented using the shutdown pin with an external RC circuit allowing the user to tailor the soft-start time to a specific application.

The LMR14203 is optimized for up to 300 mA load current.

Additional features include: thermal shutdown,  $V_{\text{IN}}$  under-voltage lockout, and gate drive under-voltage lockout. The LMR14203 is available in a low profile SOT-6L package.

Te

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

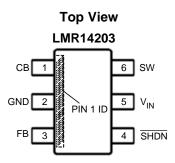

# **Connection Diagram**

Figure 1. 6 Lead SOT Package See Package Number DDC0006A

## **Pin Descriptions**

| Pin | Name            | Function                                                                                                                                                             |

|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | СВ              | SW FET gate bias voltage. Connect C <sub>BOOT</sub> cap between CB and SW.                                                                                           |

| 2   | GND             | Ground connection.                                                                                                                                                   |

| 3   | FB              | Feedback pin: Set feedback voltage divider ratio with $V_{OUT} = V_{FB}$ (1+(R1/R2)). Resistors should be in the 100-10K range to avoid input bias errors.           |

| 4   | SHDN            | Logic level shutdown input. Pull to GND to disable the device and pull high to enable the device. If this function is not used tie to $V_{\text{IN}}$ or leave open. |

| 5   | V <sub>IN</sub> | Power input voltage pin: 4.5V to 42V normal operating range.                                                                                                         |

| 6   | SW              | Power FET output: Connect to inductor, diode, and C <sub>BOOT</sub> cap.                                                                                             |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings(1)(2)

| V <sub>IN</sub>                                            | -0.3V to +45V                         |

|------------------------------------------------------------|---------------------------------------|

| SHDN                                                       | -0.3V to (V <sub>IN</sub> +0.3V) <45V |

| SW Voltage                                                 | -0.3V to +45V                         |

| CB Voltage above SW Voltage                                | 7V                                    |

| FB Voltage                                                 | -0.3V to +5V                          |

| Maximum Junction Temperature                               | 150°C                                 |

| Power Dissipation (3)                                      | Internally Limited                    |

| For soldering specifications:http://www.ti.com/lit/SNOA549 | ·                                     |

| ESD Susceptibility <sup>(4)</sup>                          | 4.51//                                |

| Human Body Model                                           | 1.5 kV                                |

- (1) Absolute maximum ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions for which the device is intended to be functional, but device parameter specifications may not be ensured. For ensured specifications and test conditions, see the Electrical Characteristics.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperature is calculated using: P<sub>D</sub> (MAX) = (T<sub>J</sub>(MAX) T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub>=175°C (typ.) and disengages at T<sub>J</sub>=155°C (typ).

- (4) Human Body Model, applicable std. JESD22-A114-C.

#### **Operating Conditions**

| Operating Junction Temperature Range <sup>(1)</sup> | -40°C to +125°C |

|-----------------------------------------------------|-----------------|

| Storage Temperature                                 | -65°C to +150°C |

| Input Voltage V <sub>IN</sub>                       | 4.5V to 42V     |

| SW Voltage                                          | Up to 42V       |

(1) All limits specified at room temperature (standard typeface) and at temperature extremes (bold typeface). All room temperature limits are 100% production tested. All limits at temperature extremes are ensured via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

Product Folder Links: LMR14203

#### **Electrical Characteristics**

Specifications in standard type face are for  $T_J = 25^{\circ}\text{C}$  and those with **boldface type** apply over the full **Operating Temperature Range** ( $T_J = -40^{\circ}\text{C}$  to +125°C). Minimum and Maximum limits are ensured through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = +25^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 12V$ .

|                   | Parameter                                                 | Test Conditions                    | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units |  |

|-------------------|-----------------------------------------------------------|------------------------------------|--------------------|--------------------|--------------------|-------|--|

| IQ                | Quiescent current                                         | SHDN = 0V                          |                    | 16                 | 40                 | μA    |  |

|                   |                                                           | Device On, Not Switching           |                    | 1.30               | 1.75               | ^     |  |

|                   |                                                           | Device On, No Load                 |                    | 1.35               | 1.85               | mA    |  |

| R <sub>DSON</sub> | Switch ON resistance                                      | See (3)                            |                    | 0.9                | 1.6                | Ω     |  |

| I <sub>LSW</sub>  | Switch leakage current                                    | V <sub>IN</sub> = 42V              |                    | 0.0                | 0.5                | μA    |  |

| I <sub>CL</sub>   | Switch current limit                                      | See (4)                            |                    | 525                |                    | mA    |  |

| I <sub>FB</sub>   | Feedback pin bias current                                 | See (5)                            |                    | 0.1                | 1.0                | μA    |  |

| V <sub>FB</sub>   | FB Pin reference voltage                                  |                                    | 0.747              | 0.765              | 0.782              | V     |  |

| t <sub>MIN</sub>  | Minimum ON time                                           |                                    |                    | 100                |                    | ns    |  |

| $f_{SW}$          | Outliebing for many                                       | V <sub>FB</sub> = 0.5V             | 0.95               | 1.25               | 1.50               | MIL   |  |

|                   | Switching frequency                                       | V <sub>FB</sub> = 0V               |                    | 0.35               |                    | MHz   |  |

| D <sub>MAX</sub>  | Maximum duty cycle                                        |                                    | 81                 | 87                 |                    | %     |  |

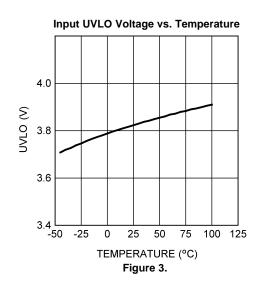

| V <sub>UVP</sub>  | Undervoltage lockout thresholds                           | On threshold                       | 4.4                | 3.7                |                    |       |  |

|                   |                                                           | Off threshold                      |                    | 3.5                | 3.25               | V     |  |

| V <sub>SHDN</sub> | Shutdown threshold                                        | Device on                          | 2.3                | 1.0                |                    | .,    |  |

|                   |                                                           | Device off                         |                    | 0.9                | 0.3                | V     |  |

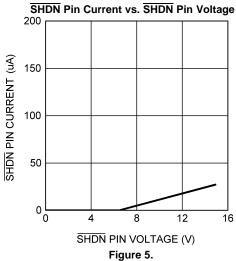

| I <sub>SHDN</sub> | Shutdown pin input bias current                           | $V_{\overline{SHDN}} = 2.3V^{(5)}$ |                    | 0.05               | 1.5                |       |  |

|                   |                                                           | V <sub>SHDN</sub> = 0V             |                    | 0.02               | 1.5                | μA    |  |

| THERMAL           | SPECIFICATIONS                                            |                                    |                    |                    |                    | •     |  |

| $R_{\theta JA}$   | Junction-to-Ambient Thermal<br>Resistance, SOT-6L Package | See (6)                            |                    | 121                |                    | °C/W  |  |

<sup>(1)</sup> All limits specified at room temperature (standard typeface) and at temperature extremes (bold typeface). All room temperature limits are 100% production tested. All limits at temperature extremes are ensured via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

<sup>(2)</sup> Typical numbers are at 25°C and represent the most likely norm.

<sup>(3)</sup> Includes the bond wires, R<sub>DSON</sub> from V<sub>IN</sub> pin to SW pin.

<sup>(4)</sup> Current limit at 0% duty cycle.

<sup>(5)</sup> Bias currents flow into pin.

<sup>(6)</sup> All numbers apply for packages soldered directly onto a 3" x 3" PC board with 2 oz. copper on 4 layers in still air in accordance to JEDEC standards. Thermal resistance varies greatly with layout, copper thickness, number of layers in PCB, power distribution, number of thermal vias, board size, ambient temperature, and air flow.

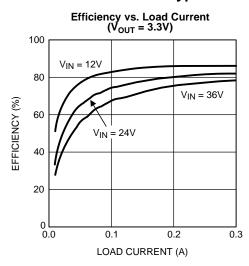

## **Typical Performance Characteristics**

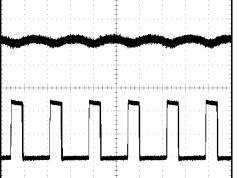

Figure 2.

**Switching Node and Output Voltage Waveforms**

$V_{IN}$  = 12V,  $V_{OUT}$  = 3.3V,  $I_{OUT}$  = 200 mA Top trace: V<sub>OUT</sub>, 10 mV/div, AC Coupled Bottom trace: SW, 5V/div, DC Coupled

$T = 1 \mu s/div$

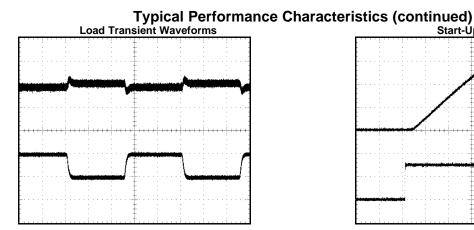

Figure 6.

$V_{\rm IN}$  = 12V,  $V_{\rm OUT}$  = 3.3V,  $I_{\rm OUT}$  = 300 mA to 200 mA to 300 mA Top trace:  $V_{\rm OUT},$  20 mV/div, AC Coupled Bottom trace: I<sub>OUT</sub>, 100 mA/div, DC Coupled  $T = 200 \mu s/div$

Figure 7.

$V_{IN}$  = 12V,  $V_{OUT}$  = 3.3V,  $I_{OUT}$  = 50 mA Top trace:  $V_{OUT}$ , 1V/div, DC Coupled Bottom trace: SHDN, 2V/div, DC Coupled  $T = 40 \mu s/div$

Figure 8.

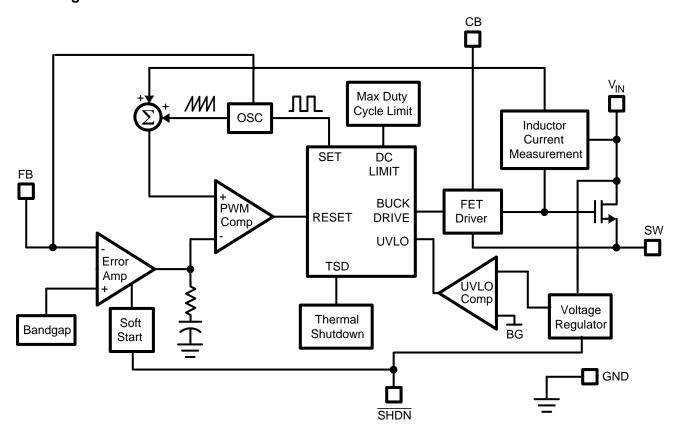

# **Block Diagram**

#### **APPLICATION INFORMATION**

#### **Protection**

The LMR14203 has dedicated protection circuitry running during normal operation to protect the IC. The thermal shutdown circuitry turns off the power device when the die temperature reaches excessive levels. The UVLO comparator protects the power device during supply power startup and shutdown to prevent operation at voltages less than the minimum input voltage. A gate drive (CB) under-voltage lockout is included to ensure that there is enough gate drive voltage to drive the MOSFET before the device tries to start switching. The LMR14203 also features a shutdown mode decreasing the supply current to approximately  $16 \, \mu A$ .

#### **Continuous Conduction Mode**

The LMR14203 contains a current-mode, PWM buck regulator. A buck regulator steps the input voltage down to a lower output voltage. In continuous conduction mode (when the inductor current never reaches zero at steady state), the buck regulator operates in two cycles. The power switch is connected between  $V_{IN}$  and SW. In the first cycle of operation the transistor is closed and the diode is reverse biased. Energy is collected in the inductor and the load current is supplied by  $C_{OUT}$  and the rising current through the inductor. During the second cycle the transistor is open and the diode is forward biased due to the fact that the inductor current cannot instantaneously change direction. The energy stored in the inductor is transferred to the load and output capacitor. The ratio of these two cycles determines the output voltage. The output voltage is defined approximately as:

$$D=V_{OUT}/V_{IN}$$

and  $D'=(1-D)$

where

D and D' will be required for design calculations.

## **Design Procedure**

This section presents guidelines for selecting external components.

#### **Setting the Output Voltage**

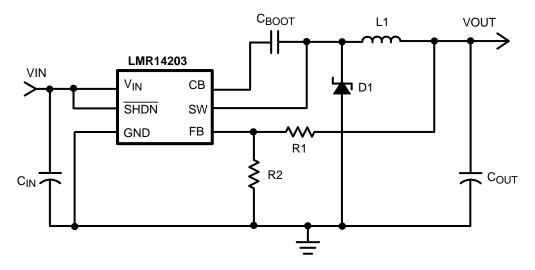

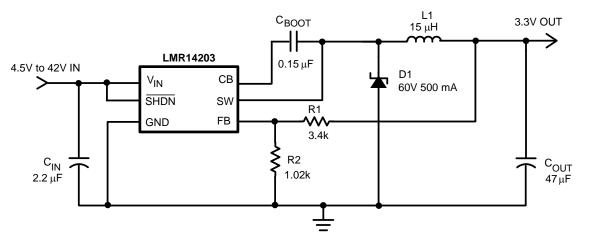

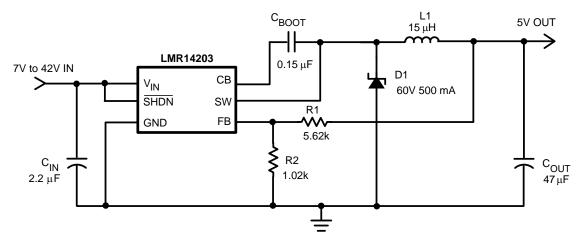

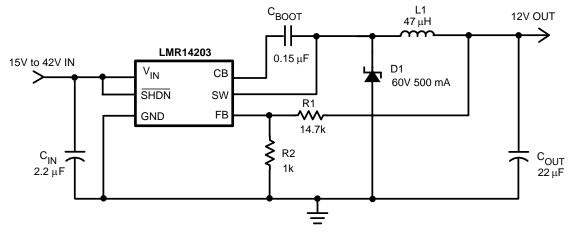

The output voltage is set using the feedback pin and a resistor divider connected to the output as shown on the front page schematic. The feedback pin voltage is 0.765V, so the ratio of the feedback resistors sets the output voltage according to the following equation:

$$V_{OUT} = 0.765V(1 + (R1/R2))$$

(2)

Typically R2 will be given as  $100\Omega$ -10 k $\Omega$  for a starting value. To solve for R1 given R2 and V<sub>OUT</sub> use R1=R2((V<sub>OUT</sub>/0.765V)-1).

#### **Input Capacitor**

A low ESR ceramic capacitor ( $C_{IN}$ ) is needed between the  $V_{IN}$  pin and GND pin. This capacitor prevents large voltage transients from appearing at the input. Use a 2.2  $\mu$ F-10  $\mu$ F value with X5R or X7R dielectric. Depending on construction, a ceramic capacitor's value can decrease up to 50% of its nominal value when rated voltage is applied. Consult with the capacitor manufacturer's data sheet for information on capacitor derating over voltage and temperature.

#### Inductor Selection

The most critical parameters for the inductor are the inductance, peak current, and the DC resistance. The inductance is related to the peak-to-peak inductor ripple current, the input and the output voltages.

$$L = \frac{(V_{IN} - V_{OUT})V_{OUT}}{V_{IN} \times I_{RIPPLE} \times f_{SW}}$$

(3)

A higher value of ripple current reduces inductance, but increases the conductance loss, core loss, and current stress for the inductor and switch devices. It also requires a bigger output capacitor for the same output voltage ripple requirement. A reasonable value is setting the ripple current to be 30% of the DC output current. Since the ripple current increases with the input voltage, the maximum input voltage is always used to determine the inductance. The DC resistance of the inductor is a key parameter for the efficiency. Lower DC resistance is

available with a bigger winding area. A good tradeoff between the efficiency and the core size is letting the inductor copper loss equal 2% of the output power. See AN-1197 SNVA038 for more information on selecting inductors. A good starting point for most applications is a 10  $\mu$ H to 22  $\mu$ H with a 0.7A or greater current rating for the LMR14203. Using such a rating will enable the LMR14203 to current limit without saturating the inductor. This is preferable to the device going into thermal shutdown mode and the possibility of damaging the inductor if the output is shorted to ground or other longterm overload.

#### **Output Capacitor**

The selection of  $C_{OUT}$  is driven by the maximum allowable output voltage ripple. The output ripple in the constant frequency, PWM mode is approximated by:

$$V_{RIPPLE} = I_{RIPPLE}(ESR + (1/(8f_{SW}C_{OUT})))$$

(4)

The ESR term usually plays the dominant role in determining the voltage ripple. Low ESR ceramic capacitors are recommended. Capacitors in the range of 22  $\mu$ F-100  $\mu$ F are a good starting point with an ESR of 0.1 $\Omega$  or less.

#### **Bootstrap Capacitor**

A 0.15  $\mu$ F ceramic capacitor or larger is recommended for the bootstrap capacitor ( $C_{BOOT}$ ). For applications where the input voltage is less than twice the output voltage a larger capacitor is recommended, generally 0.15  $\mu$ F to 1  $\mu$ F to ensure plenty of gate drive for the internal switches and a consistently low  $R_{DSON}$ .

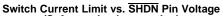

# **Soft-Start Components**

The LMR14203 has circuitry that is used in conjunction with the SHDN pin to limit the inrush current on start-up of the DC/DC switching regulator. The SHDN pin in conjunction with a RC filter is used to tailor the soft-start for a specific application. When a voltage applied to the SHDN pin is between 0V and up to 2.3V it will cause the cycle by cycle current limit in the power stage to be modulated for minimum current limit at 0V up to the rated current limit at 2.3V. Thus controlling the output rise time and inrush current at startup. The resistor value should be selected so the current sourced into the SHDN pin will be greater then the leakage current of the SHDN pin (1.5 µA) when the voltage at SHDN is equal or greater then 2.3V.

#### **Shutdown Operation**

The  $\overline{SHDN}$  pin of the LMR14203 is designed so that it may be controlled using 2.3V or higher logic signals. If the shutdown function is not to be used the  $\overline{SHDN}$  pin may be tied to  $V_{IN}$ . The maximum voltage to the  $\overline{SHDN}$  pin should not exceed 42V. If the use of a higher voltage is desired due to system or other constraints it may be used, however a 100 k $\Omega$  or larger resistor is recommended between the applied voltage and the  $\overline{SHDN}$  pin to protect the device.

#### **SCHOTTKY Diode**

The breakdown voltage rating of the diode (D1) is preferred to be 25% higher than the maximum input voltage. The current rating for the diode should be equal to the maximum output current for best reliability in most applications. In cases where the duty cycle is greater than 50%, the average diode current is lower. In this case it is possible to use a diode with a lower average current rating, approximately (1-D)I<sub>OUT</sub>, however the peak current rating should be higher than the maximum load current. A 0.5A to 1A rated diode is a good starting point.

#### **Layout Considerations**

To reduce problems with conducted noise pick up, the ground side of the feedback network should be connected directly to the GND pin with its own connection. The feedback network, resistors R1 and R2, should be kept close to the FB pin, and away from the inductor to minimize coupling noise into the feedback pin. The input bypass capacitor  $C_{\text{IN}}$  must be placed close to the  $V_{\text{IN}}$  pin. This will reduce copper trace resistance which effects input voltage ripple of the IC. The inductor L1 should be placed close to the SW pin to reduce EMI and capacitive coupling. The output capacitor,  $C_{\text{OUT}}$  should be placed close to the junction of L1 and the diode D1. The L1, D1, and  $C_{\text{OUT}}$  trace should be as short as possible to reduce conducted and radiated noise and increase overall efficiency. The ground connection for the diode,  $C_{\text{IN}}$ , and  $C_{\text{OUT}}$  should be as small as possible and tied to the system ground plane in only one spot (preferably at the  $C_{\text{OUT}}$  ground point) to minimize conducted noise in the system ground plane. For more detail on switching power supply layout considerations see Application Note AN-1149: Layout Guidelines for Switching Power Supplies SNVA021.

Product Folder Links: LMR14203

Copyright © 2011-2013, Texas Instruments Incorporated

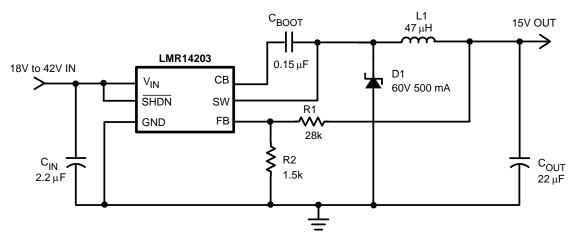

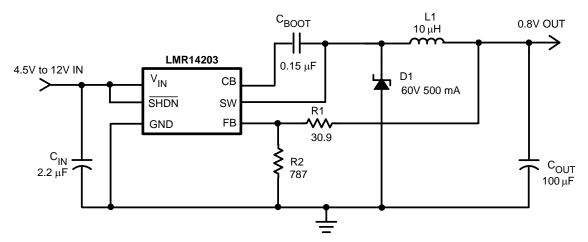

## **Typical Applications**

Figure 9. Application Circuit, 3.3V Output

Figure 10. Application Circuit, 5V Output

Figure 11. Application Circuit, 12V Output

Copyright © 2011–2013, Texas Instruments Incorporated

Figure 12. Application Circuit, 15V Output

Figure 13. Application Circuit, 0.8V Output

# **REVISION HISTORY**

| Cł | Changes from Revision B (April 2013) to Revision C |      |  |  |  |  |  |

|----|----------------------------------------------------|------|--|--|--|--|--|

| •  | Changed layout of National Data Sheet to TI format | . 10 |  |  |  |  |  |

Product Folder Links: *LMR14203*

# PACKAGE OPTION ADDENDUM

11-Apr-2013

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device  | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Top-Side Markings | Samples |

|-------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

| LMR14203XMK/NOPB  | ACTIVE | SOT          | DDC                | 6    | 1000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | SJ3B              | Samples |

| LMR14203XMKE/NOPB | ACTIVE | SOT          | DDC                | 6    | 250            | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | SJ3B              | Samples |

| LMR14203XMKX/NOPB | ACTIVE | SOT          | DDC                | 6    | 3000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | SJ3B              | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

PACKAGE MATERIALS INFORMATION

www.ti.com 8-Apr-2013

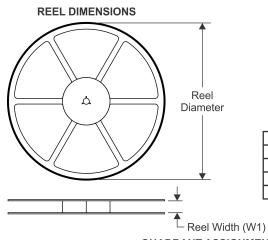

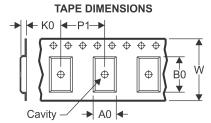

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

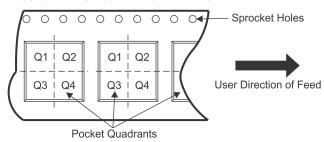

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device            | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMR14203XMK/NOPB  | SOT             | DDC                | 6 | 1000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMR14203XMKE/NOPB | SOT             | DDC                | 6 | 250  | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMR14203XMKX/NOPB | SOT             | DDC                | 6 | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

www.ti.com 8-Apr-2013

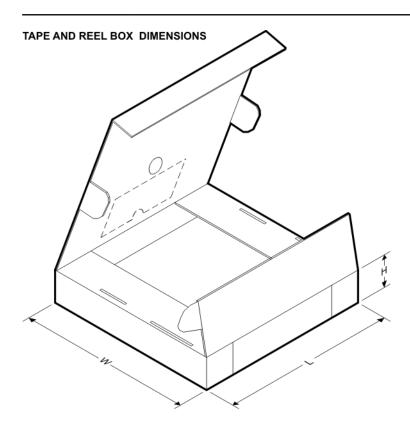

\*All dimensions are nominal

| 7 till dillitoriolorio di o mominidi |              |                 |      |      |             |            |             |

|--------------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                               | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| LMR14203XMK/NOPB                     | SOT          | DDC             | 6    | 1000 | 210.0       | 185.0      | 35.0        |

| LMR14203XMKE/NOPB                    | SOT          | DDC             | 6    | 250  | 210.0       | 185.0      | 35.0        |

| LMR14203XMKX/NOPB                    | SOT          | DDC             | 6    | 3000 | 210.0       | 185.0      | 35.0        |

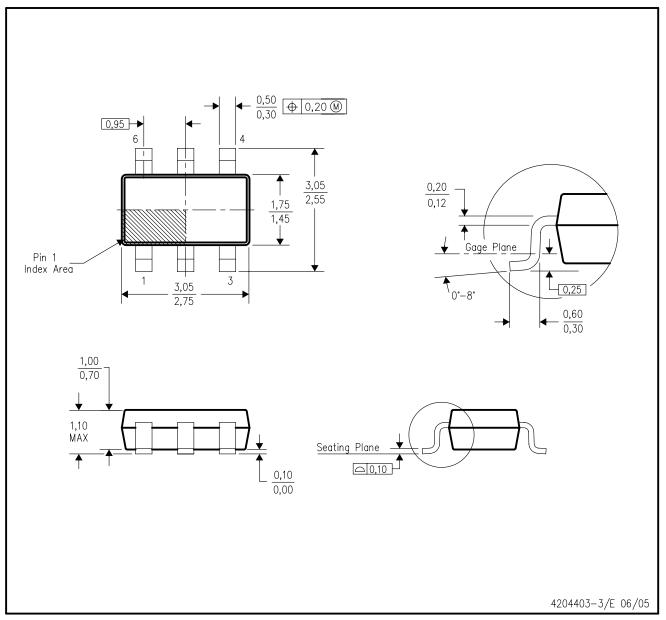

# DDC (R-PDSO-G6)

# PLASTIC SMALL-OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. Falls within JEDEC MO-193 variation AA (6 pin).

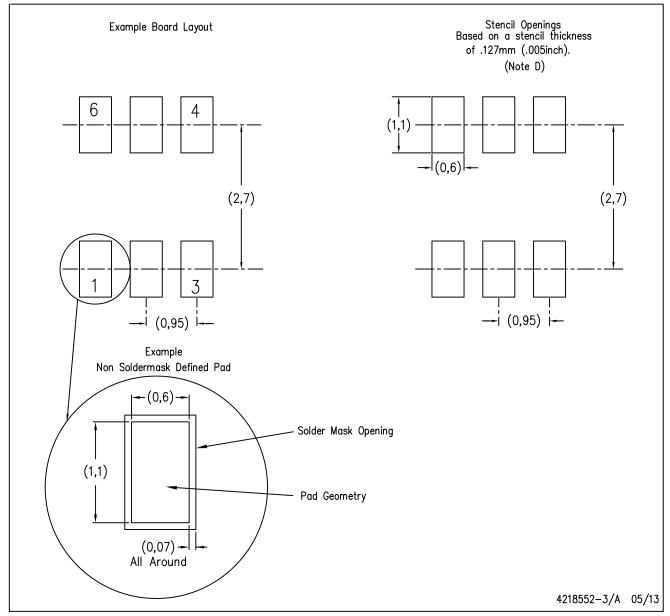

# DDC (R-PDSO-G6)

# PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>

# AMEYA360 Components Supply Platform

# **Authorized Distribution Brand:**

# Website:

Welcome to visit www.ameya360.com

# Contact Us:

# > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

# > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

# Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com