# Octal half-bridge driver with SPI control for automotive application

#### **Features**

- 8 half bridges

- R<sub>ON</sub> = typ. 0.9 Ω (HS), 0.64 Ω (LS) @  $T_i$  = 25 °C

- Current limit of each output at min. 0.8 A

- Intrinsic DC/DC step up converter driving an external MOSFET

- PWM mode option for all half bridges for hold current

- Internal PWM generation

- Two current monitor outputs

- SPI interface for data communication

- Temperature warning

- All outputs overtemperature protected

- All outputs short circuit protected

- V<sub>CC</sub> supply voltage 3.0 to 5.3 V

- Very low current consumption in standby mode typ. 5 µA

- V<sub>S</sub> operating range compliant: 6 V 18 V

### **Applications**

- Stepper motor driver and / or DC

- Intended to drive HVAC flaps

### **Description**

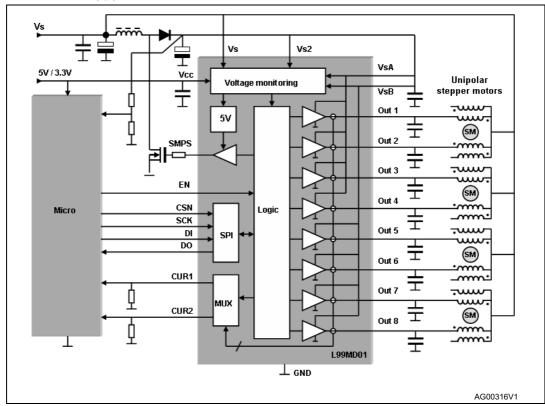

The L99MD01 is an octal half-bridge driver for automotive applications.

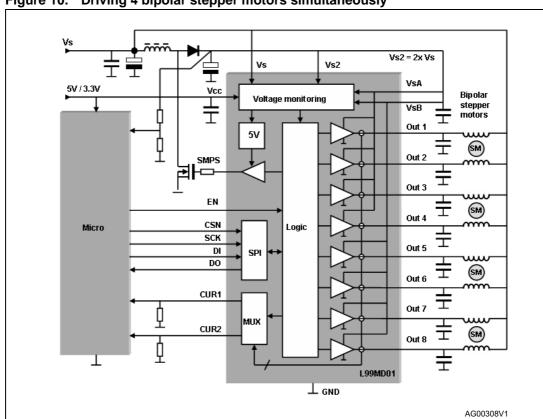

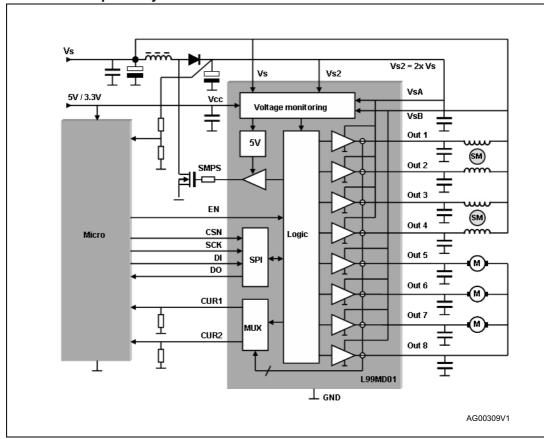

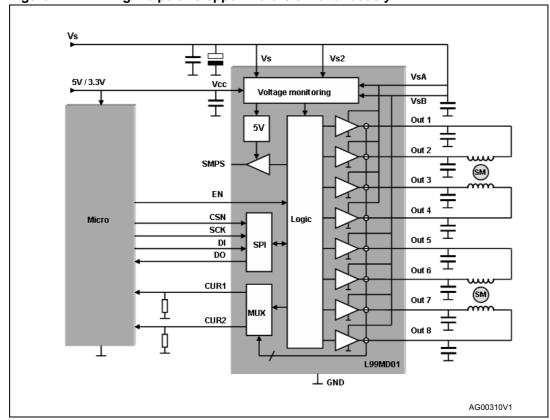

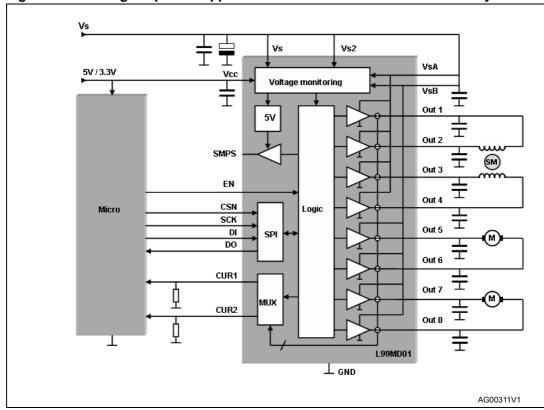

The device is intended to drive DC and/or stepper motors. Using the boost converter it's possible to drive 4 stepper motors simultaneously. Without boost converter the system is able to run 3 stepper motors in sequential mode or 2 stepper motors simultaneously. The octal half bridge configuration allows also to drive 4 DC-motors simultaneously and 7 DC-motors sequentially.

The integrated 24 bit standard Serial Peripheral Interface (SPI) controls all outputs and provides diagnostic information: normal operation, openload in on-state, overcurrent, temperature warning and overtemperature.

Table 1. Device summary

| Package     | Order codes |               |  |

|-------------|-------------|---------------|--|

| rackage     | Tube        | Tape and reel |  |

| PowerSSO-36 | L99MD01XP   | L99MD01XPTR   |  |

Contents L99MD01

### **Contents**

| 1 | Bloc  | k diagra   | am6                                                         | 6 |

|---|-------|------------|-------------------------------------------------------------|---|

| 2 | Detai | iled des   | scription                                                   | 7 |

|   | 2.1   | Power      | supply: V <sub>CC</sub>                                     | 7 |

|   | 2.2   | Power      | supply: V <sub>SA</sub> , V <sub>SB</sub>                   | 7 |

|   | 2.3   | Standb     | y mode                                                      | 7 |

|   | 2.4   | PWM r      | mode                                                        | 7 |

|   | 2.5   | SMPS       | Switched Mode Power Supply 8                                | 8 |

|   | 2.6   | Curren     | t monitor 8                                                 | 8 |

|   | 2.7   | Inducti    | ve loads                                                    | 8 |

|   | 2.8   | Diagno     | ostic functions                                             | 8 |

|   | 2.9   | Tempe      | rature warning and thermal shutdown                         | 9 |

|   | 2.10  | $V_S, V_S$ | <sub>2</sub> , V <sub>SA</sub> , V <sub>SB</sub> monitoring | 9 |

|   | 2.11  | Open-l     | oad detection                                               | 9 |

|   | 2.12  | Overlo     | ad detection                                                | 0 |

|   | 2.13  | Cross-     | current protection                                          | 0 |

| 3 | Pin c | lefinitio  | ns and functions                                            | 1 |

| 4 | Elect | trical sp  | pecifications                                               | 3 |

|   | 4.1   | Absolu     | te maximum ratings                                          | 3 |

|   | 4.2   |            | rotection                                                   |   |

|   | 4.3   | Therma     | al data                                                     | 4 |

|   | 4.4   | Electric   | cal characteristics                                         | 4 |

|   |       | 4.4.1      | SPI electrical characteristics                              | 9 |

|   |       | 4.4.2      | SPI timing parameter definition2                            | 1 |

| 5 | Fund  | tional c   | description of the SPI22                                    | 2 |

|   | 5.1   | Signal     | description                                                 | 2 |

|   |       | 5.1.1      | Serial clock (SCK)                                          | 2 |

|   |       | 5.1.2      | Serial data input (SDI)                                     | 2 |

|   | 5.2   | SPI co     | mmunication flow                                            | 4 |

L99MD01 Contents

|    |      | 5.2.1 General description       | 4 |

|----|------|---------------------------------|---|

|    |      | 5.2.2 Command byte              | 4 |

|    | 5.3  | Write operation                 | 7 |

|    | 5.4  | Read operation                  | 7 |

|    | 5.5  | Read and clear status operation | 7 |

|    | 5.6  | Read device information         | 8 |

| 6  | SPI  | ontrol and status register2     | 9 |

|    | 6.1  | Control status register 3       | 0 |

| 7  | App  | cation examples                 | 9 |

| 8  | Pack | age and PCB thermal data4       | 8 |

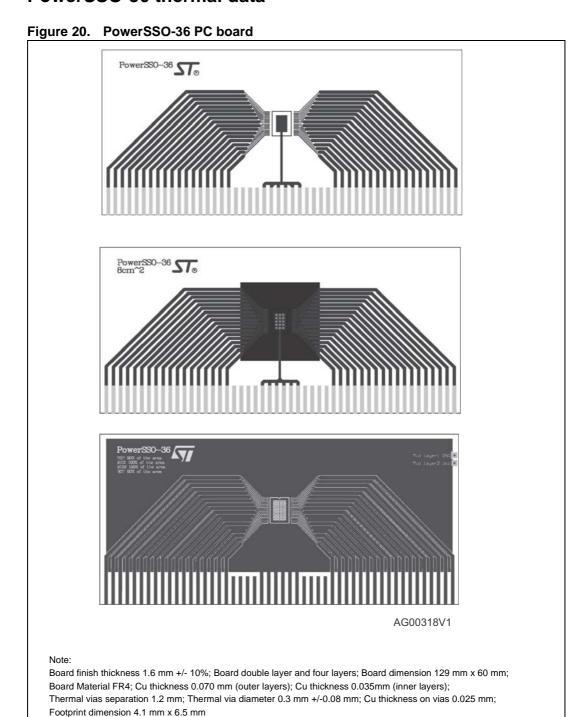

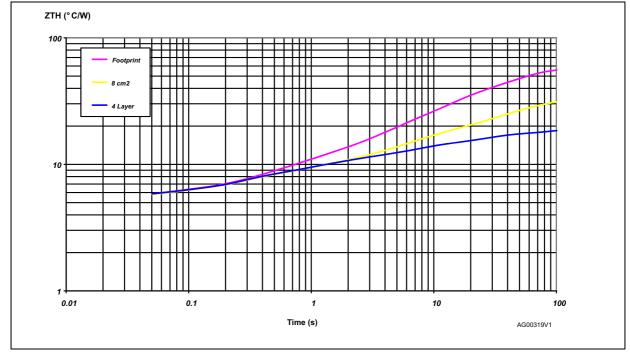

|    | 8.1  | PowerSSO-36 thermal data        | 8 |

| 9  | Pack | age information                 | 0 |

|    | 9.1  | ECOPACK® package 5              | 0 |

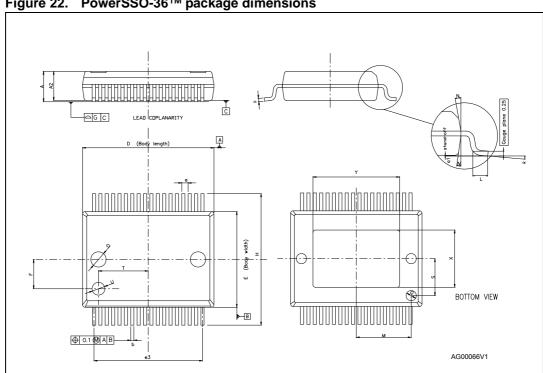

|    | 9.2  | PowerSSO-36™ mechanical data 5  | 0 |

|    | 9.3  | Packing information             | 2 |

| 10 | Revi | sion history                    | 3 |

List of tables L99MD01

### List of tables

| l able 1. | Device summary                                                                  |      |

|-----------|---------------------------------------------------------------------------------|------|

| Table 2.  | V <sub>S</sub> , V <sub>S2</sub> , V <sub>SA</sub> , V <sub>SB</sub> monitoring | 9    |

| Table 3.  | Pin description                                                                 | . 11 |

| Table 4.  | Absolute maximum ratings                                                        | . 13 |

| Table 5.  | ESD protection                                                                  |      |

| Table 6.  | Operating junction temperature                                                  | . 14 |

| Table 7.  | Temperature warning and thermal shutdown                                        | . 14 |

| Table 8.  | Supply                                                                          | . 14 |

| Table 9.  | Overvoltage and undervoltage detection                                          | . 15 |

| Table 10. | Switches                                                                        | . 16 |

| Table 11. | Current monitor output                                                          | . 17 |

| Table 12. | Current monitor dynamic characteristics                                         |      |

| Table 13. | SMPS switched mode power supply gate driver output                              | . 18 |

| Table 14. | Oscillator                                                                      |      |

| Table 15. | DC characteristics                                                              |      |

| Table 16. | AC characteristics                                                              |      |

| Table 17. | Dynamic characteristics                                                         |      |

| Table 18. | Command byte (8 bit)                                                            |      |

| Table 19. | Data byte                                                                       |      |

| Table 20. | Operating code definition                                                       |      |

| Table 21. | Global status byte                                                              |      |

| Table 22. | Reset                                                                           |      |

| Table 23. | RAM memory map                                                                  |      |

| Table 24. | ROM memory map (access with OC0 and OC1 set to '1')                             |      |

| Table 25. | Control status register                                                         |      |

| Table 26. | Control register 1                                                              |      |

| Table 27. | Control register 2                                                              |      |

| Table 28. | Control register 3                                                              |      |

| Table 29. | Wobble                                                                          |      |

| Table 30. | Frequency deviation                                                             |      |

| Table 31. | Control register 4                                                              |      |

| Table 32. | Ratio for CURR2                                                                 |      |

| Table 33. | Ratio for CURR1                                                                 |      |

| Table 34. | Control register 5                                                              |      |

| Table 35. | Control register 6                                                              |      |

| Table 36. | Status register 0                                                               |      |

| Table 37. | Status register 1                                                               |      |

| Table 38. | Status register 2                                                               |      |

| Table 39. | PowerSSO-36 mechanical data                                                     |      |

| Table 40. | Document revision history                                                       | . 53 |

L99MD01 List of figures

# **List of figures**

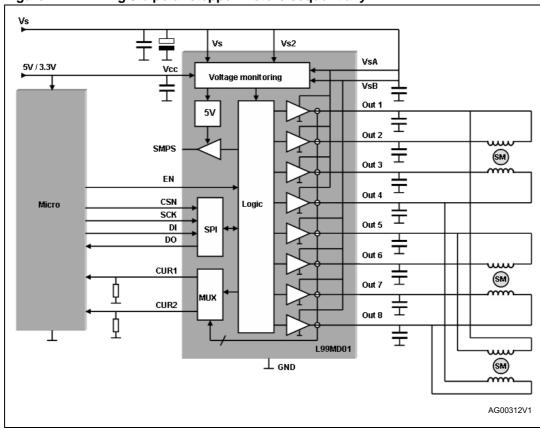

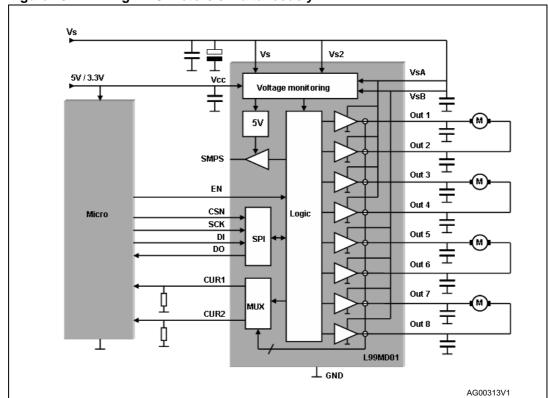

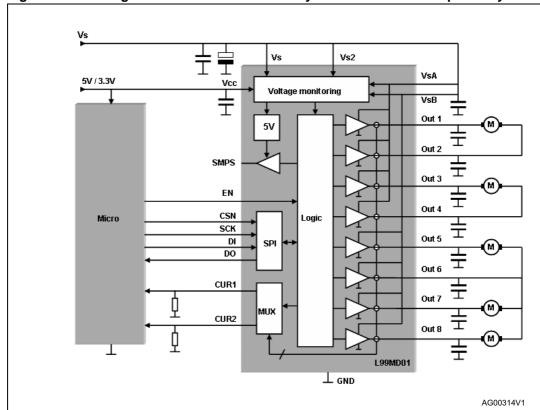

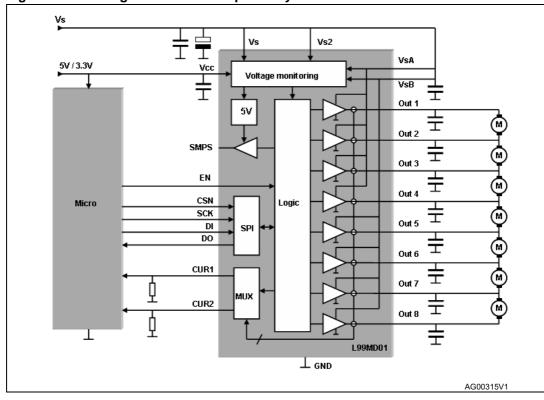

| Figure 1.  | Detailed block diagram                                                       | 6  |

|------------|------------------------------------------------------------------------------|----|

| Figure 2.  | Power on reset                                                               | 7  |

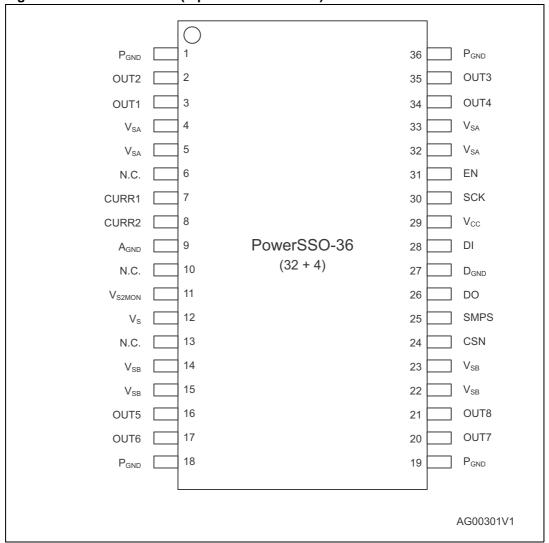

| Figure 3.  | Pin connection (top view- not in scale)                                      | 12 |

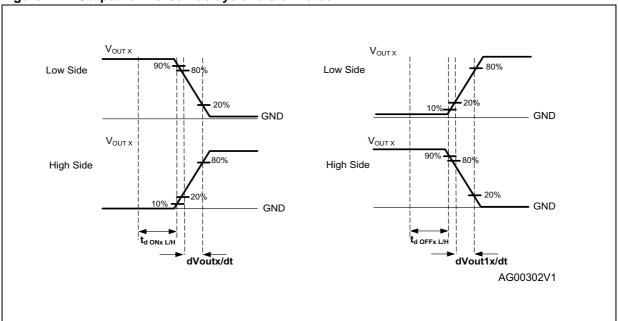

| Figure 4.  | Output turn-on/off delays and slew rates                                     | 17 |

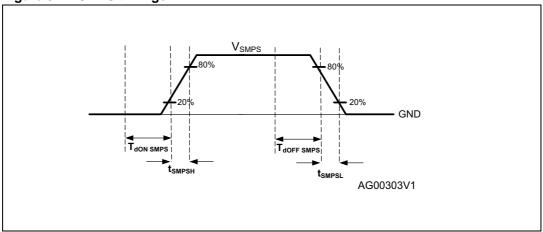

| Figure 5.  | SMPS timings                                                                 | 19 |

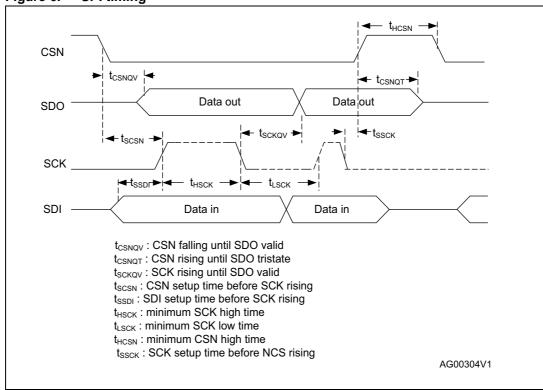

| Figure 6.  | SPI timing                                                                   | 21 |

| Figure 7.  | Clock polarity and clock phase                                               | 22 |

| Figure 8.  | SPI frame structure                                                          | 23 |

| Figure 9.  | Indication of the global error flag on SDO when CSN is low and SCK is stable | 26 |

| Figure 10. | Driving 4 bipolar stepper motors simultaneously                              | 39 |

| Figure 11. | Driving 2 bipolar stepper motors simultaneously and 3 DC-motors sequentially | 40 |

| Figure 12. | Driving 2 bipolar stepper motors simultaneously                              | 41 |

| Figure 13. | Driving 1 bipolar stepper motor and 2 DC-motors simultaneously               | 42 |

| Figure 14. | Driving 3 bipolar stepper motors sequentially                                | 43 |

| Figure 15. | Driving 4 DC-motors simultaneously                                           | 44 |

| Figure 16. | Driving 3 DC-motors simultaneously and 2 DC-motors sequentially              | 45 |

| Figure 17. | Driving 7 DC-motors sequentially                                             | 45 |

| Figure 18. | Driving simultaneously 4 unipolar winded stepper motors in bipolar mode      | 46 |

| Figure 19. | Cost saving impact using L99MD01 as stepper motor driver inside HVAC systems | 47 |

| Figure 20. | PowerSSO-36 PC board                                                         |    |

| Figure 21. | PowerSSO-36 thermal impedance junction ambient                               |    |

| Figure 22. | PowerSSO-36™ package dimensions                                              | 50 |

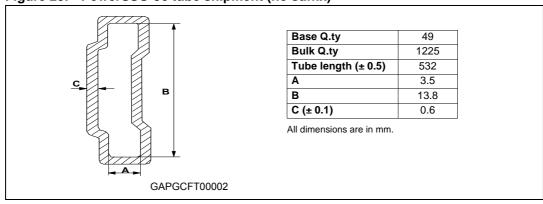

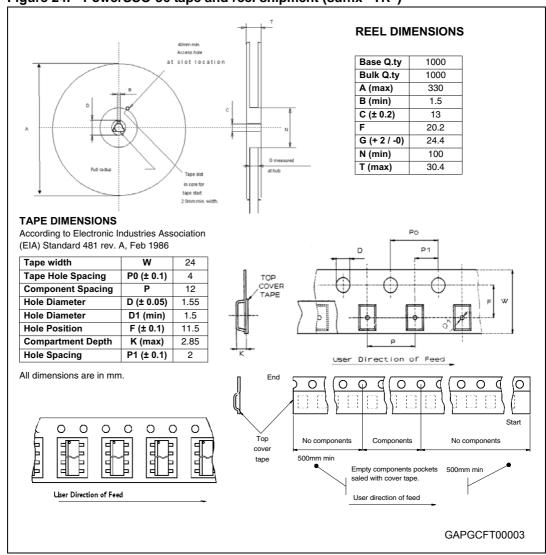

| Figure 23. | PowerSSO-36 tube shipment (no suffix)                                        | 52 |

| Figure 24. | PowerSSO-36 tape and reel shipment (suffix "TR")                             | 52 |

L99MD01 **Block diagram**

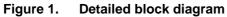

#### **Block diagram** 1

L99MD01 Detailed description

### 2 Detailed description

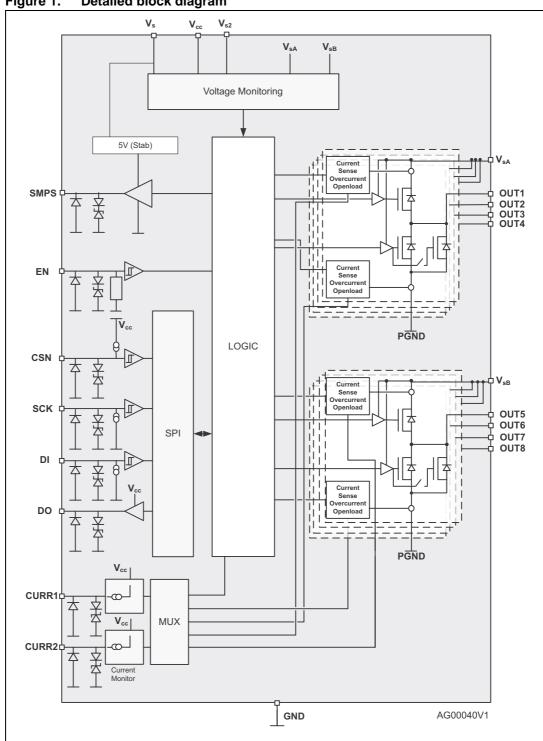

### 2.1 Power supply: V<sub>CC</sub>

The supply voltage  $V_{CC}$  (3.3 V / 5 V) supplies the whole device. In case of power-on ( $V_{CC}$  increases from undervoltage to  $V_{POR\ OFF}$  = 2.75 V, typical) the circuit is initialized by an internally generated power-on-reset (POR). If the voltage  $V_{CC}$  decreases under the minimum threshold ( $V_{POR\ ON}$  = 2.55 V, typical), the outputs are switched off in 3-state (high impedance). The status registers are cleared and the control registers are reset to their default.

Figure 2. Power on reset

### 2.2 Power supply: V<sub>SA</sub>, V<sub>SB</sub>

Each V<sub>SA</sub> and V<sub>SB</sub> supplies 4 half bridges independently.

$V_{SA} \rightarrow Out 1 to Out 4$

$V_{SB} \rightarrow Out 5 to Out 8$

### 2.3 Standby mode

The standby mode of the L99MD01 is activated by EN pin to low. The inputs and outputs are switched off. The status registers are cleared and the control registers are reset to their default values.

In the standby mode the current consumption is typ. 5  $\mu$ A.

### 2.4 PWM mode

The PWM Mode is intended to generate a hold current for stepper motors.

PWM frequency typ. 100 Hz.

Duty cycle (SPI 2bit): 15 %, 30 %, 45 % and 60 %.

Each half-bridge is independently addressable (SPI 8bit).

Detailed description L99MD01

### 2.5 SMPS Switched Mode Power Supply

External MOSFET

Spread spectrum technique:

- Wobble oscillator, programmable by SPI (1.95 K / 3.9 K / 7.8 K / 15.6 KHz).

- Frequency modulation programmable by SPI (0 / 5 / 10 / 20%).

V<sub>S2</sub> level concept:

- Microcontroller measuring pulse of SMPS frequency (dependent on internal oscillator frequency).

- Due to the Oscillator frequency of L99MD01 the  $\mu C$  can calculate the on/off counts to program the SMPS frequency and duty cycle.

- Microcontroller sending by SPI SMPS 6-bit on counter value, microcontroller sending by SPI SMPS 6-bit off counter value.

- Basing on the on and off counter value the duty cycle and the SMPS frequency can be programmed.

The V<sub>S2</sub> voltage is strongly related to the duty cycle of SMPS.

#### 2.6 Current monitor

The current monitor output sources a current image at the current monitor output which has a programmable ratio (1/250, 1/500, 1/750, 1/1000) of the instantaneous current of the selected half bridge (high-side or low-side). Via SPI it can be programmed which of the outputs are multiplexed to the current monitor output.

The current monitor output allows a more precise analysis of the actual state of the load rather than the detection of an open or overload condition. For example this can be used to detect the motor state (starting, free-running, stalled).

### 2.7 Inductive loads

Each half bridge is built by an internally connected high-side and a low-side power DMOS transistor. Due to the built-in reverse diodes of the output transistors, inductive loads can be driven at the outputs.

### 2.8 Diagnostic functions

All diagnostic functions (over/open-load, temperature warning and thermal shutdown, over/undervoltage) are internally filtered and the condition has to be valid for at least 32  $\mu s$  (open-load: typ. 2 ms, respectively) before the corresponding status bit in the status registers is set. The filters are used to improve the noise immunity of the device. Open-load and temperature warning function are intended for information purpose and not changes the state of the output drivers. On contrary, the overload and thermal shutdown condition disables the corresponding driver (overload) or all drivers (thermal shutdown), respectively. The microcontroller has to clear the overcurrent status bit to reactivate the corresponding driver.

L99MD01 Detailed description

### 2.9 Temperature warning and thermal shutdown

If the junction temperature rises above  $T_{j \ TW \ ON}$  a temperature warning flag is set and is detectable via the SPI. If the junction temperature increases above the second threshold  $T_{j \ SD \ ON}$ , the thermal shutdown bit is set and power DMOS transistors of all output stages are switched off to protect the device. Temperature warning flag and thermal shutdown bits are latched. In order to reactivate the output stages, the junction temperature must decrease below  $T_{j \ SD \ ON}$  and the thermal shutdown bit has to be cleared by the microcontroller.

### 2.10 V<sub>S</sub>, V<sub>S2</sub>, V<sub>SA</sub>, V<sub>SB</sub> monitoring

V<sub>S</sub> undervoltage: Status bit is set. All outputs and SMPS are switched off.

The microcontroller needs to clear the status bits to reactivate the

drivers and SMPS.

V<sub>S</sub> overvoltage: Status bit is set. All outputs are switched off (default).

The microcontroller needs to clear the status bits to reactivate the

drivers Can be deactivated via SPI.

V<sub>SA</sub> undervoltage: Status bit is set. Out 1 to Out 8 are switched off.

The microcontroller needs to clear the status bits to reactivate the

drivers.

V<sub>SB</sub> undervoltage: Status bit is set. Out 1 to Out 8 are switched off.

The microcontroller needs to clear the status bits to reactivate the

drivers.

V<sub>S2</sub> undervoltage: Status bit is set. Only if SPMS is active.

The microcontroller needs to clear the status bits to reactivate SMPS

V<sub>S2</sub> overvoltage: Status bit is set. SMPS is switched off (default).

The microcontroller needs to clear the status bits to reactivate SMPS. If the VS2 recovery bit is set, and the VS2 voltage falls below the threshold, the SMPS goes in active mode and the status bit is

cleared.

Table 2. V<sub>S</sub>, V<sub>S2</sub>, V<sub>SA</sub>, V<sub>SB</sub> monitoring

|                              | 'typ                  | SMPS                              | Out x                  |

|------------------------------|-----------------------|-----------------------------------|------------------------|

| V <sub>S</sub> undervoltage  | 5.7 V                 | Status + off                      | Status + off           |

| V <sub>S</sub> overvoltage   | 22.0 V                | X                                 | Status + (off or mask) |

| V <sub>SA</sub> undervoltage | 5.7 V                 | Х                                 | Status + off           |

| V <sub>SB</sub> undervoltage | 5.7 V                 | X                                 | Status + off           |

| V <sub>S2</sub> undervoltage | V <sub>S</sub> + 1.5V | Status                            | X                      |

| V <sub>S2</sub> overvoltage  | 35.0 V                | Status + (off or (off+ recovery)) |                        |

Detailed description L99MD01

### 2.11 Open-load detection

The open-load detection monitors the load current in each activated output stage. If the load current is below the open-load detection threshold for at least 2 ms ( $t_{dOL}$ ) the corresponding open load bit is set in the status register. Due to mechanical/electrical inertia of typical loads a short activation of the outputs (e.g. 3 ms) can be used to test the open-load status without changing the mechanical/electrical state of the loads.

### 2.12 Overload detection

In case of an overcurrent condition, a flag is set in the corresponding status register. If the overcurrent signal is valid for at least  $t_{\rm ISC}$  = 32  $\mu$ s, the overcurrent flag is set and the corresponding switch is switched off to reduce the power dissipation and to protect the integrated circuit. The microcontroller has to clear the status bit to reactivate the corresponding driver.

### 2.13 Cross-current protection

The device is cross-current protected by an internal delay time. If one driver (LS or HS) is turned-off the activation of the other driver of the same half bridge are automatically delayed by the cross-current protection time. After the cross-current protection time is expired the slew-rate limited switch-off phase of the driver is changed to a fast turn-off phase and the opposite driver is turned-on with slew-rate limitation. Due to this behavior it is always guaranteed that the previously activated driver is totally turned-off before the opposite driver starts to conduct. If wrong SPI commands try to turn-on both driver (LS and HS) simultaneously, the high-side and the low-side are (or stay) deactivated (3-state).

## 3 Pin definitions and functions

Table 3. Pin description

| Pin                             | Symbol                   | Function                                                                                                                                                                                                                                                                                         |

|---------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 18, 19, 36                   | $P_{GND}$                | Power ground: reference potential                                                                                                                                                                                                                                                                |

| 9                               | A <sub>GND</sub>         | Analog ground: reference potential                                                                                                                                                                                                                                                               |

| 27                              | D <sub>GND</sub>         | Digital ground: reference potential                                                                                                                                                                                                                                                              |

| 6, 10, 13                       | N.C.                     | Not connected                                                                                                                                                                                                                                                                                    |

|                                 |                          | Exposed pad: reference potential connected to PGND                                                                                                                                                                                                                                               |

| 2, 3, 16, 17,<br>20, 21, 34, 35 |                          |                                                                                                                                                                                                                                                                                                  |

| 29                              | V <sub>CC</sub>          | Logic voltage supply 3.3 V / 5 V For this input a ceramic capacitor as close as possible to AGND is recommended                                                                                                                                                                                  |

| 4, 5, 32, 33                    | V <sub>SA</sub>          | Power supply voltage for OUT 1 to 4 (external reverse protection required): For this input a ceramic capacitor as close as possible to PGND is recommended. Important: for the capability of driving the full current at the outputs all pins of V <sub>SA</sub> must be externally connected!   |

| 14, 15, 22, 23                  | $V_{SB}$                 | Power supply voltage for OUT 5 to 8 (external reverse protection required):  For this input a ceramic capacitor as close as possible to PGND is recommended.  Important: for the capability of driving the full current at the outputs all pins of V <sub>SA</sub> must be externally connected! |

| 11                              | V <sub>S2MON</sub>       | V <sub>S2</sub> monitoring                                                                                                                                                                                                                                                                       |

| 12                              | Vs                       | V <sub>S</sub> supply and monitoring                                                                                                                                                                                                                                                             |

| 25                              | SMPS                     | SMPS gate driver. For overcurrent and overvoltage protection a external resistor is recommended                                                                                                                                                                                                  |

| 7, 8                            | CURR1/2                  | Current monitor 1 / 2                                                                                                                                                                                                                                                                            |

| 31                              | 31 EN Enable the L99MD01 |                                                                                                                                                                                                                                                                                                  |

| 28                              | DI                       | SPI data in: the input requires CMOS logic levels and receives serial data from the microcontroller. The data is a 24 bit control word and the most significant bit (MSB) is transferred first.                                                                                                  |

| 26                              | DO                       | SPI data out: the diagnosis data is available via the SPI and this 3-state output. The output remains in 3-state, if the chip is not selected by the input CSN (CSN = high)                                                                                                                      |

Table 3. Pin description (continued)

| Pin                                                                                                    | Symbol | Function                                                                                                                                                                                          |  |

|--------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                        |        | SPI CSN chip select: this input is active low and requires CMOS logic levels. The serial data transfer between the L99MD01 and micro controller is enabled by pulling the input CSN to low level. |  |

| SCK SPI serial clock input: this input controls the internal s the SPI and requires CMOS logic levels. |        | SPI serial clock input: this input controls the internal shift register of the SPI and requires CMOS logic levels.                                                                                |  |

Figure 3. Pin connection (top view- not in scale)

# 4 Electrical specifications

### 4.1 Absolute maximum ratings

Table 4. Absolute maximum ratings

| Symbol                             | Parameter                                                                                             | Value                         | Unit |

|------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------|------|

| \/                                 | DC supply voltage                                                                                     | -0,328                        | V    |

| V <sub>S</sub>                     | Single pulse t <sub>max</sub> < 400 ms                                                                | 40                            | V    |

| V <sub>S2</sub>                    | DC supply voltage                                                                                     | -0,338                        | V    |

| V <sub>SA</sub><br>V <sub>SB</sub> | Single pulse t <sub>max</sub> < 400 ms                                                                | 40                            | V    |

| V <sub>CC</sub>                    | Stabilized supply voltage, logic supply                                                               | -0.3 to 5.5                   | V    |

| EN<br>DI<br>DO<br>SCK<br>CSN       | Digital input / output voltage                                                                        | -0.3 to V <sub>CC</sub> + 0.3 | V    |

| CURR1/2                            | Current monitor output                                                                                | -0.3 to V <sub>CC</sub> + 0.3 |      |

| OUT 1-8                            | Output current capability                                                                             | ±2                            | Α    |

| SMPS                               | SMPS is not overcurrent protected, external resistor can be used for protection and EMC optimizations |                               |      |

Note:

All maximum ratings are absolute ratings. Leaving the limitation of any of these values may cause an irreversible damage of the integrated circuit!

### 4.2 ESD protection

Table 5. ESD protection

| Parameter                                                                                     | Value             | Unit |

|-----------------------------------------------------------------------------------------------|-------------------|------|

| All pins                                                                                      | ±2 <sup>(1)</sup> | kV   |

| Output Pins: OUT1 – 8, V <sub>S</sub> , V <sub>SA</sub> , V <sub>SB</sub> , V <sub>S2</sub> , | ±4 <sup>(2)</sup> | kV   |

<sup>1.</sup> HBM according to EIA/JESD22-A114-E.

<sup>2.</sup> HBM with all unzapped pins grounded.

### 4.3 Thermal data

Table 6. Operating junction temperature

| Symbol         | Parameter                      | Value      | Unit |

|----------------|--------------------------------|------------|------|

| T <sub>j</sub> | operating junction temperature | -40 to 150 | °C   |

Table 7. Temperature warning and thermal shutdown

| Symbol              | Parameter                                          |                           | Min. | Тур. | Max. | Unit |

|---------------------|----------------------------------------------------|---------------------------|------|------|------|------|

| T <sub>jTW ON</sub> | temperature warning threshold junction temperature | T <sub>j</sub> increasing | -    | 1    | 150  | °C   |

| T <sub>jSD ON</sub> | thermal shutdown threshold junction temperature    | T <sub>j</sub> increasing | -    | -    | 170  | °C   |

### 4.4 Electrical characteristics

$V_S$  = 6 to 18 V,  $V_{CC}$  = 3.0 to 5.3 V,  $T_j$  = -40 to 150 °C, unless otherwise specified.

The voltages are referred to GND and currents are assumed positive, when the current flows into the pin.

Table 8. Supply

| Symbol                            | Parameter                                                                      | Test condition                                                                                             | Min. | Тур. | Max. | Unit |

|-----------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>SA</sub> / V <sub>SB</sub> | operating supply voltage range                                                 |                                                                                                            | 6    |      | 38   | V    |

| I <sub>S</sub>                    | V <sub>SA</sub> / V <sub>SB</sub> DC supply current                            | $V_{Sx} = 13 \text{ V}, V_{CC} = 5.0 \text{ V}$<br>EN = high<br>Outputs floating                           |      | 0.5  | 2    | mA   |

|                                   |                                                                                | $V_S = 13 \text{ V}, V_{CC} = 5 \text{ V}$<br>EN = high<br>SMPS output off                                 |      | 1.5  | 4    | mA   |

| I <sub>VS</sub>                   | I <sub>VS</sub> V <sub>S</sub> supply current                                  | $V_S$ = 13 V, $V_{CC}$ = 5 V<br>EN = high<br>SMPS load = 2 nF, 200 kHz,<br>duty 50 %                       |      | 4.2  | 7    | mA   |

| I <sub>VS2</sub>                  | V <sub>S2</sub> DC current                                                     | V <sub>S2</sub> =26 V, V <sub>CC</sub> = 5.0 V<br>EN = high                                                |      | 300  | 600  | μΑ   |

| I <sub>VSX</sub>                  | $V_{Sx}$ ( $V_{S}$ , $V_{SA}$ , $V_{SB}$ , $V_{S2}$ ) quiescent supply current | $V_{Sx} = 13 \text{ V}, V_{CC} = 5 \text{ V}$<br>EN = low<br>$T_j = -40, 25 ^{\circ}C$<br>Outputs floating |      | 3    | 10   | μА   |

|                                   |                                                                                | T <sub>j</sub> = 130 °C; TBV                                                                               |      | 6    | 20   | μΑ   |

| V <sub>CC</sub>                   | operating supply voltage range                                                 |                                                                                                            | 3,0  |      | 5,3  | V    |

Table 8. Supply (continued)

| Symbol          | Parameter                                | Test condition                                                                          | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------|-----------------------------------------------------------------------------------------|------|------|------|------|

|                 | I Voc DC Supply current                  | $V_{Sx} = 13 \text{ V}, V_{CC} = 5.0 \text{ V}$<br>EN = high                            |      | 1    | 3    | mA   |

| I <sub>CC</sub> | V <sub>CC</sub> quiescent supply current | $V_S = 13 \text{ V}, V_{CC} = 5.0 \text{ V}$ $CSN = V_{CC}$ $EN = low$ Outputs floating |      | 5    | 20   | μA   |

Table 9. Overvoltage and undervoltage detection

| Symbol                 | Parameter                            | Test condition                               | Min.              | Тур. | Max.              | Unit |

|------------------------|--------------------------------------|----------------------------------------------|-------------------|------|-------------------|------|

| V <sub>POR OFF</sub>   | power-on-reset threshold             | V <sub>CC</sub> increasing                   |                   |      | 3.0               | V    |

| V <sub>POR ON</sub>    | power-on-reset threshold             | V <sub>CC</sub> decreasing                   | 2.3               |      |                   | V    |

| V <sub>POR hyst</sub>  | power-on-reset hysteresis            | V <sub>POR OFF</sub> - V <sub>POR ON</sub>   |                   | 0.2  |                   | V    |

| V <sub>SUV OFF</sub>   | V <sub>S</sub> UV-threshold voltage  | V <sub>S</sub> increasing                    | 6.0               |      | 6.7               | V    |

| V <sub>SUV ON</sub>    | V <sub>S</sub> UV-threshold voltage  | V <sub>S</sub> decreasing                    | 5.4               |      | 6                 | V    |

| V <sub>SUV hyst</sub>  | V <sub>S</sub> UV-hysteresis         | V <sub>SUV OFF</sub> - V <sub>SUV ON</sub>   | 0.35              | 0.5  |                   | V    |

| V <sub>SAUV OFF</sub>  | V <sub>SA</sub> UV-threshold voltage | V <sub>SA</sub> increasing                   | 5.95              |      | 6.7               | V    |

| V <sub>SAUV ON</sub>   | V <sub>SA</sub> UV-threshold voltage | V <sub>SA</sub> decreasing                   | 5.4               |      | 6                 | V    |

| V <sub>SAUV hyst</sub> | V <sub>SA</sub> UV-hysteresis        | V <sub>SAUV OFF</sub> - V <sub>SAUV ON</sub> | 0.35              | 0.5  |                   | V    |

| V <sub>SBUV OFF</sub>  | V <sub>SB</sub> UV-threshold voltage | V <sub>SB</sub> increasing                   | 5.95              |      | 6.7               | V    |

| V <sub>SBUV ON</sub>   | V <sub>SB</sub> UV-threshold voltage | V <sub>SB</sub> decreasing                   | 5.4               |      | 6                 | V    |

| V <sub>SBUV hyst</sub> | V <sub>SB</sub> UV-hysteresis        | V <sub>SBUV OFF</sub> - V <sub>SBUV ON</sub> | 0.35              | 0.5  |                   | V    |

| V <sub>SOV ON</sub>    | V <sub>S</sub> OV-threshold voltage  | V <sub>S</sub> increasing                    |                   |      | 24                | V    |

| V <sub>SOV OFF</sub>   | V <sub>S</sub> OV-threshold voltage  | V <sub>S</sub> decreasing                    | 18                |      |                   | V    |

| V <sub>SOV hyst</sub>  | V <sub>S</sub> OV-hysteresis         | V <sub>SOV ON -</sub> V <sub>SOV OFF</sub>   | 0.75              | 1    |                   | V    |

| V <sub>S2UV OFF</sub>  | V <sub>S2</sub> UV-threshold voltage | V <sub>S2</sub> increasing                   |                   |      | V <sub>S</sub> +5 | V    |

| V <sub>S2UV ON</sub>   | V <sub>S2</sub> UV-threshold voltage | V <sub>S2</sub> decreasing                   | V <sub>S</sub> +1 |      |                   | V    |

| V <sub>S2UV hyst</sub> | V <sub>S2</sub> UV-hysteresis        | V <sub>S2UV OFF</sub> - V <sub>S2UV ON</sub> | 0.55              | 0.8  | 1.15              | V    |

| V <sub>S2OV ON</sub>   | V <sub>S2</sub> OV-threshold voltage | V <sub>S</sub> increasing                    |                   |      | 38                | V    |

| V <sub>S2OV OFF</sub>  | V <sub>S2</sub> OV-threshold voltage | V <sub>S</sub> decreasing                    | 32                |      |                   | V    |

| V <sub>S2OV hyst</sub> | V <sub>S2</sub> OV-hysteresis        | V <sub>S2OV ON -</sub> V <sub>S2OV OFF</sub> | 0.75              | 1    |                   | V    |

Table 10. Switches

| Symbol                               | Parameter                                                     | Test condition                                                 | Min. | Тур. | Max. | Unit |

|--------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------|------|------|------|------|

| _                                    | On resistance V <sub>SA</sub> / V <sub>SB</sub> to            | T <sub>j</sub> = 25 °C,<br>I <sub>OUT1-8</sub> = -0.25 A       |      | 900  | 1200 | mΩ   |

| r <sub>ON HS 1-8</sub>               | OUT 1-8                                                       | T <sub>j</sub> = 125 °C,<br>I <sub>OUT1-8</sub> = -0.25 A      |      | 1300 | 1800 | mΩ   |

| _                                    | On resistance OUT 1-8 to GND                                  | T <sub>j</sub> = 25 °C, HC=1<br>I <sub>OUT1-8</sub> = 0.25 A   |      | 700  | 1000 | mΩ   |

| ONLSHC 1-8                           | in HC mode                                                    | T <sub>j</sub> = 125 °C, HC=1<br>I <sub>OUT1-8</sub> = 0.25 A  |      | 1000 | 1500 | mΩ   |

| r                                    | On resistance OUT 1-8 to GND                                  | T <sub>j</sub> = 25 °C, HC=0<br>I <sub>OUT1-8</sub> = 0.125 A  |      | 1200 | 1800 | mΩ   |

| r <sub>ONLSLC 1-8</sub>              | in LC mode                                                    | T <sub>j</sub> = 125 °C, HC=0<br>I <sub>OUT1-8</sub> = 0.125 A |      | 2000 | 2800 | mΩ   |

| I <sub>SCHS1-8</sub>                 | HS overcurrent protection                                     | V <sub>S</sub> = 13.5 V                                        | 0.8  |      | 1.4  | Α    |

| I <sub>SCLSHC1-8</sub>               | LS overcurrent protection in HC mode                          | V <sub>S</sub> = 13.5 V, HC = 1                                | 0.8  |      | 1.4  | А    |

| I <sub>SCLSLC1-8</sub>               | LS overcurrent protection in LC mode                          | V <sub>S</sub> = 13.5 V, HC = 0                                | 0.4  |      | 0.7  | А    |

| t <sub>d ON1-8</sub> H               | Output delay time, HS switch on                               | $V_{S} = 13.5 \text{ V}, R_{load} = 52 \Omega$                 | 10   | 25   | 80   | μs   |

| t <sub>d OFF1-8</sub> H              | Output delay time, HS switch off                              | $V_S = 13.5 \text{ V}, R_{load} = 52 \Omega$                   | 50   | 100  | 300  | μs   |

| t <sub>d ON1-8</sub> L               | Output delay time, LS switch on                               | $V_S = 13.5 \text{ V}, R_{load} = 52 \Omega$                   | 5    | 15   | 80   | μs   |

| t <sub>d OFF1-8 L</sub>              | Output delay time, LS switch off                              | $V_S = 13.5 \text{ V}, R_{load} = 52 \Omega$                   | 50   | 100  | 300  | μs   |

| t <sub>D LH</sub> /t <sub>D HL</sub> | Cross current protection time                                 |                                                                | 20   | 200  | 400  | μs   |

| I <sub>QLH</sub>                     | Switched-off output current HS OUT 1-8                        | V <sub>OUT1-8</sub> = 0 V                                      | -2   |      |      | μΑ   |

| I <sub>QLL</sub>                     | Switched-off output current LS OUT 1-8                        | $V_{OUT1-8} = V_{S}$                                           |      |      | 2    | μΑ   |

| 1                                    | Open-load detection current HS                                | T <sub>j</sub> = -40 °C                                        | 8    | 30   | 60   | mA   |

| I <sub>OLDHS1-8</sub>                | OUT 1-8                                                       | T <sub>j</sub> = 25 °C to 125 °C                               | 10   | 30   | 60   | mA   |

|                                      | Open lead detection surrent I C                               | HC bit set to 1; T <sub>j</sub> = -40 °C                       | 4.5  | 30   | 65   | mA   |

| I <sub>OLDLSHC1-8</sub>              | Open-load detection current LS<br>OUT 1-8 in HC mode          | HC bit set to 1;<br>T <sub>j</sub> = 25 °C to 125 °C           | 8    | 30   | 60   | mA   |

|                                      | Open load detection surrent I C                               | HC bit set to 0; T <sub>j</sub> = -40 °C                       | 1.8  | 15   | 35   | mA   |

| I <sub>OLDLSLC1-8</sub>              | Open-load detection current LS<br>OUT 1-8 in LC mode          | HC bit set to 0;<br>T <sub>j</sub> = 25 °C to 125 °C           | 4    | 15   | 30   | mA   |

| t <sub>dOL</sub>                     | Minimum duration of open-load condition to set the status bit |                                                                | 500  | 2000 | 3000 | μs   |

Table 10. Switches (continued)

| Symbol                   | Parameter                                                          | Test condition                               | Min. | Тур. | Max. | Unit |

|--------------------------|--------------------------------------------------------------------|----------------------------------------------|------|------|------|------|

| t <sub>ISC</sub>         | Minimum duration of overcurrent condition to switch off the driver |                                              | 10   | 32   | 100  | μs   |

| dV <sub>OUT1-8</sub> /dt | Slew rate of OUT 1-8                                               | $V_S = 13.5 \text{ V}, R_{load} = 52 \Omega$ | 0.1  | 0.25 | 0.5  | V/µs |

Figure 4. Output turn-on/off delays and slew rates

Table 11. Current monitor output

| Symbol                    | Parameter                                                                               | Test condition                                                                                                                                                                                                               | Min. | Тур.   | Max.                | Unit |

|---------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|---------------------|------|

| V <sub>CURR1/2</sub>      | Functional voltage range                                                                | V <sub>CC</sub> = 5 V                                                                                                                                                                                                        | 0    |        | V <sub>CC</sub> - 1 | ٧    |

| I <sub>CURRHSLS250</sub>  | HS/LS current monitor output ratio: I <sub>CURR1/2</sub> / I <sub>OUT 1-8</sub>         | $ 0 \text{ V} \leq \text{V}_{\text{CURR1/2}} \leq \text{V}_{\text{CC}} - 1 \text{ V}, $ $ \text{V}_{\text{CC}} = 5 \text{ V}; \text{ prog. via SPI, } $ $ \text{I}_{\text{max}} = 800 \text{ mA, HC} = 1 $                   |      | 1/250  |                     | 1    |

| I <sub>CURRHSLS500</sub>  | HS/LS current monitor output ratio: I <sub>CURR1/2</sub> / I <sub>OUT 1-8</sub>         | $ 0 \text{ V} \leq \text{V}_{\text{CURR1/2}} \leq \text{V}_{\text{CC}} - 1 \text{ V}, $ $ \text{V}_{\text{CC}} = 5 \text{ V}; \text{ prog. via SPI,} $ $ \text{I}_{\text{max}} = 800 \text{ mA, HC} = 1 $                    |      | 1/500  |                     | -    |

| I <sub>CURRHSLS750</sub>  | HS/LS current monitor output ratio: I <sub>CURR1/2</sub> / I <sub>OUT 1-8</sub>         | $ \begin{array}{l} 0 \text{ V} \leq \text{V}_{\text{CURR1/2}} \leq \text{V}_{\text{CC}} \text{ - 1 V,} \\ \text{V}_{\text{CC}} = 5 \text{ V; prog. via SPI,} \\ \text{I}_{\text{max}} = 800 \text{ mA, HC} = 1 \end{array} $ |      | 1/750  |                     | 1    |

| I <sub>CURRHSLS1000</sub> | HS/LS current monitor output ratio: I <sub>CURR1/2</sub> / I <sub>OUT 1-8</sub>         | $ 0 \text{ V} \leq \text{V}_{\text{CURR1/2}} \leq \text{V}_{\text{CC}} - 1 \text{ V}, $ $ \text{V}_{\text{CC}} = 5 \text{ V}; \text{ prog. via SPI,} $ $ \text{I}_{\text{max}} = 800 \text{ mA, HC} = 1 $                    |      | 1/1000 |                     | -    |

| I <sub>CURRLSLC125</sub>  | LS current monitor output ratio in LC mode: I <sub>CURR1/2</sub> / I <sub>OUT 1-8</sub> | $ \begin{array}{l} 0 \text{ V} \leq \text{V}_{CURR1/2} \leq \text{V}_{CC} \text{ - 1 V}, \\ \text{V}_{CC} = 5 \text{ V}; \text{ prog. via SPI}, \\ \text{HC} = 0; \text{I}_{max} = 400 \text{ mA} \end{array} $              |      | 1/125  |                     | 1    |

**577**

Table 11. Current monitor output (continued)

| Symbol                       | Parameter                                                                               | Test condition                                                                                                                                                                                                                                                                                                 | Min. | Тур.         | Max.          | Unit |

|------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|---------------|------|

| I <sub>CURRLSLC250</sub>     | LS current monitor output ratio in LC mode:  CURRLSLC1/2 / OUT 1-8                      | $ \begin{array}{l} 0 \text{ V} \leq \text{V}_{\text{CURR1/2}} \leq \text{V}_{\text{CC}} \text{ - 1 V}, \\ \text{V}_{\text{CC}} = 5 \text{ V}; \text{ prog. via SPI}, \\ \text{HC} = 0; \text{I}_{\text{max}} = 400 \text{ mA} \end{array} $                                                                    |      | 1/250        |               | -    |

| I <sub>CURRLSLC375</sub>     | LS current monitor output ratio in LC mode: I <sub>CURR1/2</sub> / I <sub>OUT 1-8</sub> | $ \begin{array}{l} 0 \text{ V} \leq \text{V}_{\text{CURR1/2}} \leq \text{V}_{\text{CC}} \text{ - 1 V}, \\ \text{V}_{\text{CC}} = 5 \text{ V}; \text{ prog. via SPI}, \\ \text{HC} = 0; \text{I}_{\text{max}} = 400 \text{ mA} \end{array} $                                                                    |      | 1/375        |               | -    |

| I <sub>CURRLSLC500</sub>     | LS current monitor output ratio in LC mode: I <sub>CURR1/2</sub> / I <sub>OUT 1-8</sub> | $ \begin{array}{l} 0 \text{ V} \leq \text{V}_{\text{CURR1/2}} \leq \text{V}_{\text{CC}} \text{ - 1 V}, \\ \text{V}_{\text{CC}} = 5 \text{ V}; \text{ prog. via SPI}, \\ \text{HC} = 0; \text{I}_{\text{max}} = 400 \text{ mA} \end{array} $                                                                    |      | 1/500        |               | 1    |

|                              | HS current monitor accuracy                                                             | 0 V $\leq$ V <sub>CURR1/2</sub> $\leq$ V <sub>CC</sub> - 1 V,<br>V <sub>CC</sub> = 5 V; I <sub>OUT 1-8 max</sub> = 0.8 A<br>(FS = full scale=<br>800 mA*current ratio); T <sub>j</sub> = -<br>40 °C                                                                                                            |      | 4% +<br>1%FS | 10% +<br>3%FS | 1    |

| ICURRHS1/2 acc               |                                                                                         | $ \begin{array}{l} 0 \text{ V} \leq \text{V}_{\text{CURR1/2}} \leq \text{V}_{\text{CC}} \text{ - 1 V,} \\ \text{V}_{\text{CC}} = 5 \text{ V; I}_{\text{OUT 1-8 max}} = 0.8 \text{ A;} \\ \text{(FS = full scale=} \\ 800 \text{ mA*current ratio);} \\ \text{T}_{j} = 25 \text{ °C to 125 °C} \\ \end{array} $ |      | 4% +<br>1%FS | 8% +<br>2%FS  |      |

| I <sub>CURRLSHC1/2 acc</sub> | LS current monitor accuracy in HC mode                                                  | $\begin{array}{l} 0 \text{ V} \leq \text{V}_{\text{CURR1/2}} \leq \text{V}_{\text{CC}} - 1 \text{ V}, \\ \text{V}_{\text{CC}} = 5 \text{ V}; \\ 0.4 \text{ A} \leq \text{I}_{\text{OUT1-8}} \leq 0.8 \text{ A} \\ \text{(FS = full scale=} \\ 800 \text{ mA*current ratio)} \end{array}$                       |      | 4% +<br>1%FS | 10% +<br>3%FS | -    |

| I <sub>CURRLSLC1/2 acc</sub> | LS current monitor accuracy in LC mode                                                  | $\begin{array}{l} 0 \text{ V} \leq \text{V}_{\text{CURR1/2}} \leq \text{V}_{\text{CC}} \text{ - 1 V}, \\ \text{V}_{\text{CC}} = 5 \text{ V}; \\ \text{I}_{\text{OUT 1-8 max}} = 0.4 \text{ A} \\ \text{(FS = full scale=} \\ 800 \text{ mA*current ratio)} \end{array}$                                        |      | 4% +<br>1%FS | 10% +<br>3%FS | -    |

Table 12. Current monitor dynamic characteristics

| Symbol            | Parameter | Test condition                                                                                                  | Min. | Тур. | Max. | Unit |

|-------------------|-----------|-----------------------------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>d-CM</sub> | time      | I <sub>OUT</sub> from 100 mA to<br>200 mA; t <sub>d-CM</sub> measured<br>from 50 % I <sub>OUT</sub> to 50 % ICM |      | 2    |      | μs   |

Table 13. SMPS switched mode power supply gate driver output

| Symbol              | Parameter                | Test condition                                  | Min. | Тур. | Max. | Unit |

|---------------------|--------------------------|-------------------------------------------------|------|------|------|------|

| V <sub>SMPSHI</sub> | SMPS output voltage high | $V_S = 8 \text{ V}, I_{SMPS} = -10 \text{ mA}$  | 4.5  | 5.5  | 6.5  | V    |

| V <sub>SMPL</sub>   | SMPS output voltage low  | V <sub>S</sub> = 8 V, I <sub>SMPS</sub> = 10 mA |      |      | 100  | mV   |

| t <sub>SMPSH</sub>  | Output rise time         | V <sub>S</sub> = 13.5 V, Cout = 2 nF            |      | 110  | 160  | ns   |

| t <sub>SMPSL</sub>  | Output fall time         | V <sub>S</sub> = 13.5 V, Cout = 2 nF            |      | 110  | 160  | ns   |

| Symbol                   | Parameter                           | Test condition                       | Min. | Тур. | Max. | Unit |  |

|--------------------------|-------------------------------------|--------------------------------------|------|------|------|------|--|

| t <sub>dONSMPS</sub>     | Output delay time, switch to high   | V <sub>S</sub> = 13.5 V, Cout = 2 nF |      | 110  | 160  | ns   |  |

| t <sub>dOFFSMPS</sub>    | Output delay time, switch to low    | V <sub>S</sub> = 13.5 V, Cout = 2 nF |      | 30   | 100  | ns   |  |

| t <sub>dON-OFFSMPS</sub> | Output delay time difference ON/OFF | V <sub>S</sub> = 13.5 V, Cout = 2 nF |      | 80   | 120  | ns   |  |

| R <sub>SMPS</sub>        | Pull down resistor, SMPS            |                                      | 23   | 50   | 100  | kΩ   |  |

Table 13. SMPS switched mode power supply gate driver output

Table 14. Oscillator

| Symbol           | Parameter                | Test condition | Min. | Тур. | Max. | Unit |

|------------------|--------------------------|----------------|------|------|------|------|

| f <sub>CLK</sub> | Internal clock frequency |                | 2.8  | 4    | 5.2  | MHz  |

### 4.4.1 SPI electrical characteristics

$\rm V_S$  = 6 to 18 V,  $\rm V_{CC}$  = 3.0 to 5.3 V,  $\rm T_j$  = -40 to 150 °C, unless otherwise specified.

The voltages are referred to GND and currents are assumed positive, when the current flows into the pin.

Table 15. DC characteristics

| Symbol              | Parameter                    | Test condition                                     | Min.               | Тур. | Max.               | Unit |  |  |

|---------------------|------------------------------|----------------------------------------------------|--------------------|------|--------------------|------|--|--|

| SDI, SCK, CSN, EN   |                              |                                                    |                    |      |                    |      |  |  |

| $V_{IL}$            | Input low voltage            |                                                    |                    |      | 0.3V <sub>CC</sub> | V    |  |  |

| V <sub>IH</sub>     | Input high voltage           |                                                    | 0.7V <sub>CC</sub> |      |                    | V    |  |  |

| I <sub>CSN in</sub> | Pull up current at input CSN | V <sub>CSN</sub> = 1.5 V;<br>V <sub>CC</sub> = 5 V | 8                  | 20   | 40                 | μΑ   |  |  |

Table 15. DC characteristics (continued)

| Symbol              | Parameter                      | Test condition                                     | Min.                  | Тур.                  | Max. | Unit |

|---------------------|--------------------------------|----------------------------------------------------|-----------------------|-----------------------|------|------|

| I <sub>SCK in</sub> | Pull down current at input SCK | V <sub>SCK</sub> = 1.5 V;<br>V <sub>CC</sub> = 5 V | 10                    | 25                    | 50   | μΑ   |

| I <sub>DI in</sub>  | Pull down current at input DI  | V <sub>DI</sub> = 1.5 V;<br>V <sub>CC</sub> = 5 V  | 10                    | 25                    | 50   | μΑ   |

| R <sub>EN in</sub>  | Pull down resistor at input EN | V <sub>EN</sub> = 1.5 V;<br>V <sub>CC</sub> = 5 V  | 25                    | 50                    | 115  | kΩ   |

| SDO                 |                                |                                                    |                       |                       |      |      |

| V <sub>OL</sub>     | Output low voltage             | I <sub>out</sub> = 2 mA                            |                       | 0.2                   | 0.4  | V    |

| V <sub>OH</sub>     | Output high voltage            | I <sub>out</sub> = +2 mA                           | V <sub>CC</sub> - 0.4 | V <sub>CC</sub> - 0.2 |      | V    |

| I <sub>DOLK</sub>   | 3-state leakage current        | $V_{CSN} = V_{CC},$<br>0 V < $V_{CC}$              | -10                   |                       | 10   | μΑ   |

Table 16. AC characteristics

| Symbol                          | Parameter                      | Test condition                | Min. | Тур. | Max. | Unit |

|---------------------------------|--------------------------------|-------------------------------|------|------|------|------|

| SDO, SDI, SCK, CSN, EN          |                                |                               |      |      |      |      |

| C <sub>OUT</sub> <sup>(1)</sup> | Output capacitance (SDO)       | V <sub>OUT</sub> = 0 V to 5 V | _    |      | 10   | pF   |

| C <sub>IN</sub> <sup>(1)</sup>  | Input capacitance (SDI)        | V <sub>IN</sub> = 0 V to 5 V  | _    | _    | 10   | pF   |

| OIN.                            | Input capacitance (other pins) | V <sub>IN</sub> = 0 V to 5 V  | _    | _    | 10   | pF   |

<sup>1.</sup> Guaranteed by design

Table 17. Dynamic characteristics<sup>(1)</sup>

| Symbol             | Parameter                        | Test condition            | Min. | Тур. | Max. | Unit |

|--------------------|----------------------------------|---------------------------|------|------|------|------|

| t <sub>EN</sub>    | EN high setup time               |                           |      |      | 100  | μs   |

| t <sub>SCSN</sub>  | CSN setup time before SCK rising |                           | 400  |      |      | ns   |

| t <sub>HCSN</sub>  | CSN high time                    |                           | 2    |      |      | μs   |

| t <sub>CSNQV</sub> | CSN falling until SDO valid      | C <sub>out</sub> = 100 pF |      |      | 100  | ns   |

| t <sub>CSNQT</sub> | CSN rising until SDO 3-state     | C <sub>out</sub> = 100 pF |      |      | 150  | ns   |

| t <sub>SSCK</sub>  | SCK setup time before CSN rising |                           | 50   |      |      | ns   |

| t <sub>SSDI</sub>  | SDI setup time before SCK rising |                           | 40   |      |      | ns   |

| t <sub>HSCK</sub>  | SCK high time                    |                           | 200  |      |      | ns   |

| t <sub>LSCK</sub>  | SCK low time                     |                           | 200  |      |      | ns   |

| t <sub>SCKQV</sub> | SCK falling until SDO valid      | C <sub>out</sub> = 100 pF |      |      | 150  | ns   |

Table 17. Dynamic characteristics<sup>(1)</sup>

| Symbol            | Parameter        | Test condition                                              | Min. | Тур. | Max. | Unit |

|-------------------|------------------|-------------------------------------------------------------|------|------|------|------|

| t <sub>QLQH</sub> | Output rise time | C <sub>out</sub> = 100 pF,<br>20 % - 80 % x V <sub>CC</sub> |      |      | 110  | ns   |

| t <sub>QHQL</sub> | Output fall time | C <sub>out</sub> = 100 pF,<br>80 % - 20 % x V <sub>CC</sub> |      |      | 110  | ns   |

| f <sub>SPI</sub>  | SPI frequency    |                                                             |      |      | 1    | MHz  |

<sup>1.</sup> See Section 4.4.2: SPI timing parameter definition.

### 4.4.2 SPI timing parameter definition

Figure 6. SPI timing

#### 5 **Functional description of the SPI**

#### 5.1 Signal description

#### 5.1.1 Serial clock (SCK)

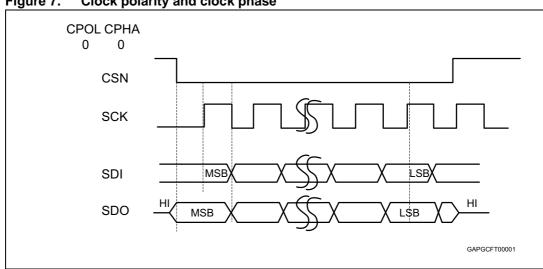

This input signal provides the timing of the serial interface. Data present at Serial Data Input (SDI) is latched on the rising edge of Serial Clock (SCK). Data on Serial Data Out (SDO) is shifted out at the falling edge of Serial Clock (see *Figure 7*).

The SPI can be driven by a microcontroller with its SPI peripherals running in following mode: CPOL=0 and CPHA=0 (see Figure 7).

#### 5.1.2 Serial data input (SDI)

This input is used to transfer data serially into the device. It receives the data to be written. Values are latched on the rising edge of Serial Clock (SCK).

#### Serial data output (SDO)

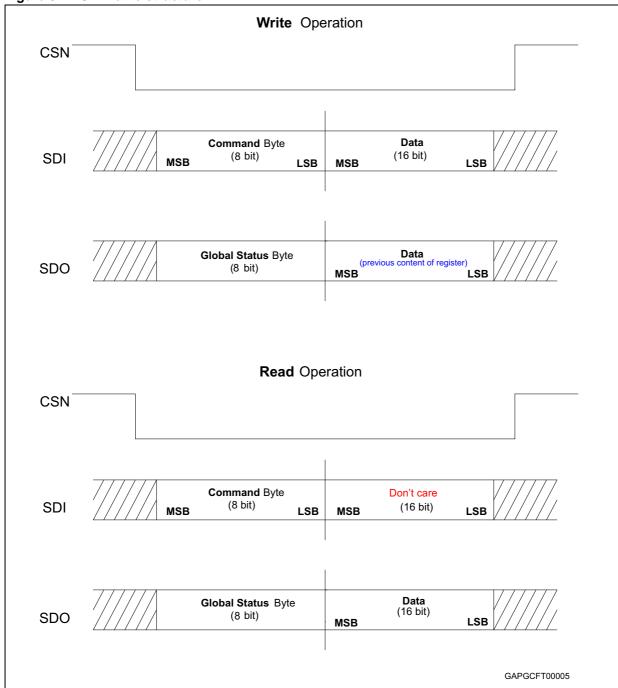

This output signal is used to transfer data serially out of the device. Data is shifted out on the falling edge of Serial Clock (SCK). SDO also reflects the status of the <Global Error Flag> (Bit 7 of the <Global Status Register>) while CSN is low and no clock signal is present.

### Chip select not (CSN)

When this input signal is High, the device is deselected and Serial Data Output (SDO) is high impedance (3-state). Driving this input low enables the communication. The communication must start and stop on a low level of Serial Clock (SCK).

Figure 7. Clock polarity and clock phase

577 22/54 Doc ID 17242 Rev 6

#### 5.2 SPI communication flow

### 5.2.1 General description

The proposed SPI communication is based on a standard SPI interface structure using CSN (Chip Select Not), SDI (Serial Data In), SDO (Serial Data Out/Error) and SCK (Serial Clock) signal lines. Maximum SPI frequency is 1 MHz.

At the beginning of each communication the master reads the <SPI-frame-ID> register (ROM address 3EH) of the slave device. This 8-bit register indicates the SPI frame length (24-bit for the L99MD01) and the availability of additional features.

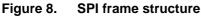

Each communication frame consists of an instruction byte which is followed by 2 data bytes (see *Figure 8*).

The data returned on SDO within the same frame always starts with the <Global Status> register. It provides general status information about the device. It is followed by 2bytes (i. e. 'In-frame-response', *Figure 8*).

For write cycles the *<Global Status>* register is followed by the previous content of the addressed register.

For read cycles the <Global Status> register is followed by the content of the addressed register.

Table 18. Command byte (8 bit)

|      | Operating code |     |    |    | Add | ress |    |    |

|------|----------------|-----|----|----|-----|------|----|----|

| Bit  | 23             | 22  | 21 | 20 | 19  | 18   | 17 | 16 |

| Name | OC1            | OC0 | A5 | A4 | А3  | A2   | A1 | A0 |

Table 19. Data byte

|      | Data byte 1 |                       |     |     |     |     |    |    | Data I | oyte 0 | 1  |    |    |    |    |    |

|------|-------------|-----------------------|-----|-----|-----|-----|----|----|--------|--------|----|----|----|----|----|----|

| Bit  | 15          | 15 14 13 12 11 10 9 8 |     |     |     |     | 7  | 6  | 5      | 4      | 3  | 2  | 1  | 0  |    |    |

| Name | D15         | D14                   | D13 | D12 | D11 | D10 | D9 | D8 | D7     | D6     | D5 | D4 | D3 | D2 | D1 | D0 |

#### 5.2.2 Command byte

Each communication frame starts with a command byte. It consists of an operating code which specifies the type of operation (<Read>, <Write>, <Read and Clear Status>, <Read Device Information>) and a 6 bit address.

Table 20. Operating code definition

| OC1 | OC0 | Meaning                                 |

|-----|-----|-----------------------------------------|

| 0   | 0   | <write mode=""></write>                 |

| 0   | 1   | <read mode=""></read>                   |

| 1   | 0   | <read and="" clear="" status=""></read> |

| 1   | 1   | <read device="" information=""></read>  |

The <Write Mode> and <Read Mode> operations allow access to the RAM of the device, i. e. write to control registers or read status information.

A <Read and Clear Status> operation addressed to a device specific status register reads back and subsequently clear this status register. A <Read and Clear Status> operation with address 3FH clears all status registers at a time and reads back the <Configuration> register.

A <Read and Clear Status> operation addressed to an unused RAM address register is identical to a <Read Mode> operation (in case of unused RAM address, the second byte is equal to 00H).

<Read Device Information> allows access to the ROM area which contains device related information such as the product family, product name, silicon version and register width.

Table 21. Global status byte

| Bit | Description                             | Polarity    | Comment                                                                                                                                                                                                                                                                                        |  |  |

|-----|-----------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|     |                                         |             | Depends on bit 5 of < Global Status Byte>:                                                                                                                                                                                                                                                     |  |  |

|     |                                         |             | Bit 5 Bit 0                                                                                                                                                                                                                                                                                    |  |  |

| 0   | Software reset or under/overvoltage     | Active high | 0 Set if software reset (SDI stuck at 1 or 0)                                                                                                                                                                                                                                                  |  |  |

|     |                                         |             | 1 Logical OR of the under- / overvoltage status bits                                                                                                                                                                                                                                           |  |  |

|     |                                         |             |                                                                                                                                                                                                                                                                                                |  |  |

| 1   | Overcurrent detected                    | Active high | Set by any overcurrent event                                                                                                                                                                                                                                                                   |  |  |

| 2   | Open-load detected                      | Active high | Set by any open-load event                                                                                                                                                                                                                                                                     |  |  |

| 3   | Temp warning                            | Active high |                                                                                                                                                                                                                                                                                                |  |  |

| 4   | Thermal shutdown / chip overload        | Active high |                                                                                                                                                                                                                                                                                                |  |  |

| 5   | Not (chip reset or communication error) | Active low  | Activated by all internal reset events that change device state or configuration registers (e. g. software reset, V <sub>CC</sub> under-voltage, etc.). The bit is set after a valid communication with any register. This bit is initially '0' and is set to '1' by a valid SPI communication |  |  |

| 6   | Communication Error                     | Active high | Bit is set if the number of clock cycles during CSN = low does not match with the specified frame width or if an invalid bus condition is detected (SDI stuck at 1 or 0).                                                                                                                      |  |  |

| 7   | Global Error Flag                       | Active high | Logic OR combination of all failures in the <global byte="" status="">.</global>                                                                                                                                                                                                               |  |  |

The *<Global Error Flag>* is generated by an OR-combination of all failure events of the device (i.e. bit 0 to bit 6 of the *<Global Status Byte>*.

Figure 9. Indication of the global error flag on SDO when CSN is low and SCK is stable.

The bit 0 of the *<Global Status Byte>* is a combination of an under/overvoltage warning and a software warning: If the bit 5 is one (this is the standard after a correct SPI communication), bit 0 is the logical OR of all under- and overvoltage status bits.

On the other hand, if there has been an SPI communication error or a chip reset (bit 5 is zero), then bit 0 gives a better indication about the SPI error: An SDI stuck-at error leads to a software reset and sets bit 0, while a clock pulse error only sets the communication error bit, clears bit 5 and clears also bit 0. This leads to the following table of possible states (assuming there is no under/overvoltage, overcurrent, openload or thermal error):

| T-1- |    | 00  | _ |      |

|------|----|-----|---|------|

| Tab  | ıe | 22. | R | eset |

| State                   | Description                                        | Global status |  |

|-------------------------|----------------------------------------------------|---------------|--|

| EN = 0 (power on reset) | All registers reset Outputs switched off (3-state) | 1000 0000     |  |

| Clock cycles != 24      | Ignore frame<br>No reset                           | 1100 0000     |  |

| SDI always 0            | Software reset Outputs switched off                | 1100 0001     |  |

| SDI always 1            | Software reset Outputs switched off                | 1100 0001     |  |

Writing to the selected data input register is only enabled if exactly one frame length is transmitted within one communication frame (i.e. CSN low). If more or less clock pulses are counted within one frame, the complete frame is ignored and a SPI frame error is signaled in the Global Status register. This safety function is implemented to avoid an unwanted activation of output stages by a wrong communication frame.

26/54 Doc ID 17242 Rev 6

For read operations, the *<communication error>* bit in the *<Global Status Byte>* is set, but the register to be read is still transferred to the SDO pin. If the number of clock cycles is smaller than the frame width, the data at SDO are truncated. If the number of clock cycles is larger than the frame width, the data at SDO are filled with '0' bits.

Due to this safety functionality a daisy chaining of SPI is not possible. Instead, a parallel operation of the SPI bus by controlling the CSN signal of the connected ICs is recommended.

Note:

As the frame width is 24 bits, an initial Read of <SPI-frame-ID> using a 16 bits communication sets the <communication Error bit> of the <Global Status Byte>. A subsequent correct length transaction is necessary to correct this bit.

### 5.3 Write operation

OC0, OC1: operating code (00 for 'write' mode)

The write operation starts with a command byte followed by 2 data bytes.

For write cycles the *<Global Status>* register is followed by the previous content of the addressed register.

The RAM memory area consists of 16 bit registers. All unused RAM addresses are read as '0'.

Failures are indicated by activating the corresponding bit of the <Global Status> register.

Note:

RAM address 00H is unused. An attempt to access this address is recognized as a communication line error ('Data-in stuck to GND') and all internal registers are cleared (software reset).

### 5.4 Read operation

OC0, OC1: operating code (01 for 'read' mode)

The read operation starts with a command byte followed by 2 data bytes. The content of the data bytes is 'don't care'. The content of the addressed register is shifted out at SDO within the same frame ('in-frame response').

The returned data byte represents the content of the register to be read.

Failures are indicated by activating the corresponding bit of the <Global Status> register.

### 5.5 Read and clear status operation

OC0, OC1: operating code (10 for 'read and clear status' mode)

The 'Read and Clear Status' operation starts with a command byte followed by 2 data bytes. The content of the data bytes is 'don't care'. The content of the addressed status register is transferred to SDO within the same frame ('in-frame response') and is subsequently cleared.

A 'Read and Clear Status' operation with address 3FH clears all Status registers simultaneously.

A <Read and Clear Status> operation addressed to an unused RAM address is identical to a <Read Mode> operation (in case of unused RAM address, the second byte is equal to 00H).

The returned data byte represents the content of the register to be read.

Failures are indicated by activating the corresponding bit of the <Global Status> register.

### 5.6 Read device information

OC0, OC1: operating code (11 for 'read device information mode).

The device information is stored at the ROM In the ROM memory area, the first 8 bits are used. All unused ROM addresses are read as '0'.

Note:

ROM address 3FH is unused. An attempt to access this address is recognized as a communication line error ('Data-in stuck to  $V_{CC}$ ') all internal registers are cleared (software reset).

# 6 SPI control and status register

Table 23. RAM memory map

| Address | Name               | Access     | Content                                                                    |

|---------|--------------------|------------|----------------------------------------------------------------------------|

| 01h     | Control register 1 | Read/write | Output switch on/off                                                       |

| 02h     | Control register 2 | Read/write | SMPS driver configuration                                                  |

| 03h     | Control register 3 | Read/write | Low-side high current mode V <sub>S</sub> configuration SMPS configuration |