# **Technical Note**

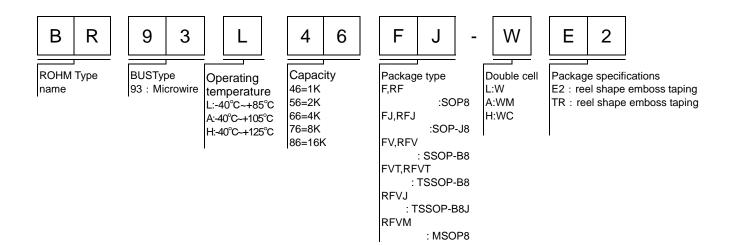

# High Reliability Serial EEPROMs High Reliability Series EEPROMs Microwire BUS

BR93LDD-W Series, BR93ADD-WM Series, BR93HDD-WC Series

No.11001EGT03

ROHM's series of serial EEPROMs represent the highest level of reliability on the market. A double cell structure provides a failsafe method of data reliability, while a double reset function prevents data miswriting. In addition, gold pads and gold wires are used for internal connections, pushing the boundaries of reliability to the limit.

BR93L $\Box$ -W Series are assort 1Kbit~16Kbit. BR93A $\Box$ -WM Series are possible to operate at 105°C and are assorted with 1K~16Kbit. BR93H $\Box$ -WC Series are possible to operate at 125°C, are assorted with 2K~16Kbit.

# Contents BR93L□□-W Series BR93L46-W, BR93L56-W, BR93L66-W, BR93L76-W, BR93L86-W BR93A□□-WM Series BR93A46-WM, BR93A56-WM, BR93A66-WM, BR93A76-WM, BR93A86-WM ····P2 BR93H□□-WC Series BR93H□□-WC Series BR93H56-WC, BR93H66-WC, BR93H76-WC, BR93H86-WC

# Serial EEPROM Series High Reliability Series EEPROMs Microwire BUS

BR93L -W Series, 93A -WM Series

#### Description

BR93L - W Series, BR93A - WM Series are serial EEPROM of serial 3-line interface method

#### Features

- 1) 3-line communications of chip select, serial clock, serial data input / output (the case where input and output are shared)

- 2) Actions available at high speed 2MHz clock(2.5~5.5V)

- 3) Speed write available (write time 5ms max.)

- 4) Same package and pin layout from 1Kbit to 16Kbit

- 5) 1.8~5.5V (BR93L W Series), 2.5~5.5V (BR93A WM Series) single power source action

- 6) Address auto increment function at read action

- 7) Write mistake prevention function

Write prohibition at power on

- Write prohibition by command code

- Write mistake prevention function at low voltage

- 8) Program cycle auto delete and auto end function

- 9) Program condition display by READY / BUSY

- 10) Low current consumption

- At write action (at 5V) : 1.2mA (Typ.)

- At read action (at 5V) : 0.3mA (Typ.)

- At standby action (at 5V) : 0.1µA (Typ.)(CMOS input)

- 11) TTL compatible( input / output s)

- 12) Compact package SOP8/SOP-J8/SSOP-B8/TSSOP-B8/MSOP8/TSSOP-B8J<sup>1</sup>

- 13) Data retention for 40 years

- 14) Endurance up to 1,000,000 times

- 15) Data at shipment all addresses FFFh

\*1 Only SOP8, SOP-J8, TSSOP-B8, MSOP8 for BR93A

#### ●BR93L, BR93A Series

|          | Package type |            | SOP8 SOP-J8          |   | SSOP-B8 |    | TSSOP-B8 |    | MSOP8 | TSSOP-B8J |      |      |      |

|----------|--------------|------------|----------------------|---|---------|----|----------|----|-------|-----------|------|------|------|

| Capacity | Bit format   | Туре       | Power source voltage | F | RF      | FJ | RFJ      | FV | RFV   | FVT       | RFVT | RFVM | RFVJ |

| 1Kbit    | 64×16        | BR93L46-W  | 1.8~5.5V             | • | •       | •  | •        | •  | •     | •         | •    | •    | •    |

| 2Kbit    | 128×16       | BR93L56-W  | 1.8~5.5V             | • | •       | •  | •        | •  | •     | •         | •    | •    | •    |

| 4Kbit    | 256×16       | BR93L66-W  | 1.8~5.5V             | • | •       | •  | •        | •  | •     | •         | •    | •    | •    |

| 8Kbit    | 512×16       | BR93L76-W  | 1.8~5.5V             | • | •       | •  | •        |    | •     |           | •    | •    | •    |

| 16Kbit   | 1K×16        | BR93L86-W  | 1.8~5.5V             | • | •       | •  | •        |    | •     |           | •    | •    | •    |

| 1Kbit    | 64×16        | BR93A46-WM | 2.5~5.5V             | • | •       | •  | •        |    |       |           | •    | •    |      |

| 2Kbit    | 128×16       | BR93A56-WM | 2.5~5.5V             | • | •       | •  | •        |    |       |           | •    | •    |      |

| 4Kbit    | 256×16       | BR93A66-WM | 2.5~5.5V             | • | •       | •  | •        |    |       |           | •    | •    |      |

| 8Kbit    | 512×16       | BR93A76-WM | 2.5~5.5V             | • | •       |    |          |    |       |           | •    | •    |      |

| 16Kbit   | 1K×16        | BR93A86-WM | 2.5~5.5V             | • | •       |    |          |    |       |           | •    | •    |      |

#### ●Absolute Maximum Ratings(Ta=25°C,BR93L□□-W)

| Parameter                 | Symbol | Limits                       | Unit |  |

|---------------------------|--------|------------------------------|------|--|

| Impressed voltage         | VCC    | -0.3~+6.5                    | V    |  |

|                           |        | 450 (SOP8) <sup>*1</sup>     |      |  |

|                           |        | 450 (SOP-J8) <sup>*2</sup>   |      |  |

|                           | Di     | 300 (SSOP-B8) <sup>*3</sup>  |      |  |

| Permissible dissipation   | Pd     | 330 (TSSOP-B8) <sup>*4</sup> | mW   |  |

|                           |        | 310 (MSOP8) <sup>*5</sup>    |      |  |

|                           |        | 310 (TSSOP-B8J) *6           |      |  |

| Storage temperature range | Tstg   | -65~+125                     | C°   |  |

| Action temperature range  | Topr   | -40~+85                      | C°   |  |

| Terminal voltage          | -      | -0.3~VCC+0.3                 | V    |  |

\* When using at Ta=25°C or higher, 4.5mW(\*1,\*2), 3.0mW(\*3) 3.3mW(\*4),

3.1mW(\*5, 6), to be reduced per 1°C.

#### ●Absolute Maximum Ratings (Ta=25°C,BR93A□□-WM)

| Parameter Symbol          |      | Limits                    | Unit |  |

|---------------------------|------|---------------------------|------|--|

| Impressed voltage         | VCC  | -0.3~+6.5                 | V    |  |

|                           |      | 450 (SOP8) <sup>*1</sup>  |      |  |

| Permissible               | Dd   | 450 (SOP-J8) *2           | mW   |  |

| dissipation               | Pd   | 330 (TSSOP-B8) *3         | TIVV |  |

|                           |      | 310 (MSOP8) <sup>*4</sup> |      |  |

| Storage temperature range | Tstg | -65~+125                  | C°   |  |

| Action temperature range  | Topr | -40~+105                  | °C   |  |

| Terminal voltage          | -    | -0.3~VCC+0.3              | V    |  |

\* When using at Ta=25°C or higher, 4.5mW(\*1,\*2), 3.3mW(\*3), 3.1 mW(\*4) to be reduced per 1°C.

#### ●Memory cell characteristics (VCC=1.8~5.5V,BR93L□□-W)

| Deremeter                        |           | Limit          | Unit | Condition |           |  |

|----------------------------------|-----------|----------------|------|-----------|-----------|--|

| Parameter                        | Min.      | /in. Typ. Max. |      | Unit      | Condition |  |

| Endurance <sup>*1</sup>          | 1,000,000 | -              | -    | Times     | Ta=25°C   |  |

| Data retention <sup>*1</sup>     | 40        | -              | -    | Years     | Ta=25°C   |  |

| OShipment data all address FFFFh |           |                |      |           | J         |  |

\*1 Not 100% TESTED

#### ●Memory cell characteristics (VCC=2.5~5.5V,BR93A□□-WM)

| Parameter                    |           | Limit       | Unit | Condition |          |

|------------------------------|-----------|-------------|------|-----------|----------|

| Faranielei                   | Min.      | Min. Typ. M |      |           | Unit     |

| <b>F</b> acture <b>a</b> *1  | 1,000,000 |             |      | Timoo     | Ta≦25°C  |

| Endurance '                  | 100,000   |             |      | Times     | Ta≦105°C |

| D. (. ): *1                  | 40        | -           | -    | Veere     | Ta≦25°C  |

| Data retention <sup>*1</sup> | 10        | -           | -    | Years     | Ta≦105°C |

OShipment data all address FFFFh

\*1 Not 100% TESTED

#### ●Recommended action conditions (BR93L□□-W)

| Parameter            | Symbol | Limits  | Unit |  |

|----------------------|--------|---------|------|--|

| Power source voltage | VCC    | 1.8~5.5 | V    |  |

| Input voltage        | VIN    | 0~VCC   | V    |  |

#### ●Recommended action conditions (BR93A□□-WM)

| Parameter            | Symbol | Limits  | Unit |  |

|----------------------|--------|---------|------|--|

| Power source voltage | VCC    | 2.5~5.5 | M    |  |

| Input voltage        | Vin    | 0~VCC   | V    |  |

#### Electrical characteristics

(Unless otherwise specified, VCC=2.5~5.5V, Ta=-40~+85°C, BR93L□□-W, Ta=-40~+105°C, BR93A□□-WM)

| Deremeter                        | Sumbol | Limits         |   |           | Linit     | Condition                       |

|----------------------------------|--------|----------------|---|-----------|-----------|---------------------------------|

| Parameter                        | Symbol | Min. Typ. Max. |   | Unit      | Condition |                                 |

| "L" input voltage 1              | VIL1   | -0.3           | - | +0.8      | V         | 4.0V≦VCC≦5.5V                   |

| "L" input voltage 2              | VIL2   | -0.3           | - | 0.2 x VCC | V         | VCC≦4.0V                        |

| "H" input voltage 1              | VIH1   | 2.0            | - | VCC+0.3   | V         | 4.0V≦VCC≦5.5V                   |

| "H" input voltage 2              | VIH2   | 0.7 x VCC      | - | VCC+0.3   | V         | VCC≦4.0V                        |

| "L" output voltage 1             | VOL1   | 0              | - | 0.4       | V         | IoL=2.1mA, 4.0V≦VCC≦5.5V        |

| "L" output voltage 2             | Vol2   | 0              | - | 0.2       | V         | IoL=100µA                       |

| "H" output voltage 1             | VOH1   | 2.4            | - | VCC       | V         | IOH=-0.4mA, 4.0V≦VCC≦5.5V       |

| "H" output voltage 2             | Voh2   | VCC-0.2        | - | VCC       | V         | Іон=-100μА                      |

| Input leak current               | ILI    | -1             | - | +1        | μA        | VIN=0V~VCC                      |

| Output leak current              | Ilo    | -1             | - | +1        | μA        | Vout=0V~VCC, CS=0V              |

|                                  | ICC1   | -              | - | 3.0       | mA        | fsk=2MHz, te/w=5ms (WRITE)      |

| Current consumption<br>at action | ICC2   | -              | - | 1.5       | mA        | fsĸ=2MHz (READ)                 |

|                                  | Іссз   | -              | - | 4.5       | mA        | fsk=2MHz, te/w=5ms (WRAL, ERAL) |

| Standby current                  | ISB    | -              | - | 2         | μA        | CS=0V, DO=OPEN                  |

©Radiation resistance design is not made.

#### (Unless otherwise specified, VCC=1.8~2.5V, Ta=-40~+85°C, BR93L□□-W)

| Doromotor                        | Sumbol | Limits    |           |           | Unit | Condition                         |  |

|----------------------------------|--------|-----------|-----------|-----------|------|-----------------------------------|--|

| Parameter                        | Symbol | Min.      | Тур. Мах. |           | Unit | Condition                         |  |

| "L" input voltage                | VIL    | -0.3      | -         | 0.2 x VCC | V    |                                   |  |

| "H" input voltage                | Vін    | 0.7 x VCC | -         | VCC+0.3   | V    |                                   |  |

| "L" output voltage               | Vol    | 0         | -         | 0.2       | V    | Ιο <b>L=100μ</b> Α                |  |

| "H" output voltage               | Vон    | VCC-0.2   | -         | VCC       | V    | Іон=-100μА                        |  |

| Input leak current               | LI     | -1        | -         | +1        | μA   | VIN=0V~VCC                        |  |

| Output leak current              | Ilo    | -1        | -         | +1        | μA   | Vout=0V~VCC, CS=0V                |  |

|                                  | ICC1   | -         | -         | 1.5       | mA   | fsk=500kHz, te/w=5ms (WRITE)      |  |

| Current consumption<br>at action | ICC2   | -         | -         | 0.5       | mA   | fsĸ=500kHz (READ)                 |  |

|                                  | Іссз   | -         | -         | 2         | mA   | fsĸ=500kHz, tɛ/w=5ms (WRAL, ERAL) |  |

| Standby current                  | lsв    | -         | -         | 2         | μA   | CS=0V, DO=OPEN                    |  |

©Radiation resistance design is not made.

#### •Action timing characteristics

(BR93L□□-W, Ta=-40~+85°C, VCC=2.5~5.5V, BR93A□□-WM, Ta=-40~+105°C, VCC=2.5~5.5V)

| Parameter                            | Symbol           | 2.5  | Unit |      |      |

|--------------------------------------|------------------|------|------|------|------|

| Falameter                            | Symbol           | Min. | Тур. | Max. | Unit |

| SK frequency                         | f <sub>sк</sub>  | -    | -    | 2    | MHz  |

| SK "H" time                          | t <sub>SKH</sub> | 230  | -    | -    | ns   |

| SK "L" time                          | t <sub>SKL</sub> | 230  | -    | -    | ns   |

| CS "L" time                          | t <sub>cs</sub>  | 200  | -    | -    | ns   |

| CS setup time                        | t <sub>CSS</sub> | 50   | -    | -    | ns   |

| DI setup time                        | t <sub>DIS</sub> | 100  | -    | -    | ns   |

| CS hold time                         | t <sub>CSH</sub> | 0    | -    | -    | ns   |

| DI hold time                         | t <sub>DIH</sub> | 100  | -    | -    | ns   |

| Data "1" output delay time           | t <sub>PD1</sub> | -    | -    | 200  | ns   |

| Data "0" output delay time           | t <sub>PD0</sub> | -    | -    | 200  | ns   |

| Time from CS to output establishment | t <sub>SV</sub>  | -    | -    | 150  | ns   |

| Time from CS to High-Z               | t <sub>DF</sub>  | -    | -    | 150  | ns   |

| Write cycle time                     | t <sub>E/W</sub> | -    | -    | 5    | ms   |

#### (BR93L□□-W, Ta=-40~+85°C, VCC=1.8~2.5V)

| Parameter                            | Symbol           | 1.8  | Unit      |     |       |  |

|--------------------------------------|------------------|------|-----------|-----|-------|--|

| Farameter                            | Symbol           | Min. | Min. Typ. |     | Offic |  |

| SK frequency                         | f <sub>sк</sub>  | -    | -         | 500 | kHz   |  |

| SK "H" time                          | t <sub>SKH</sub> | 0.8  | -         | -   | us    |  |

| SK "L" time                          | t <sub>SKL</sub> | 0.8  | -         | -   | us    |  |

| CS "L" time                          | t <sub>CS</sub>  | 1    | -         | -   | us    |  |

| CS setup time                        | t <sub>CSS</sub> | 200  | -         | -   | ns    |  |

| DI setup time                        | t <sub>DIS</sub> | 100  | -         | -   | ns    |  |

| CS hold time                         | t <sub>CSH</sub> | 0    | -         | -   | ns    |  |

| DI hold time                         | t <sub>DIH</sub> | 100  | -         | -   | ns    |  |

| Data "1" output delay time           | t <sub>PD1</sub> | -    | -         | 0.7 | us    |  |

| Data "0" output delay time           | t <sub>PD0</sub> | -    | -         | 0.7 | us    |  |

| Time from CS to output establishment | t <sub>SV</sub>  | -    | -         | 0.7 | us    |  |

| Time from CS to High-Z               | t <sub>DF</sub>  | -    | -         | 200 | ns    |  |

| Write cycle time                     | t <sub>E/W</sub> | -    | -         | 5   | ms    |  |

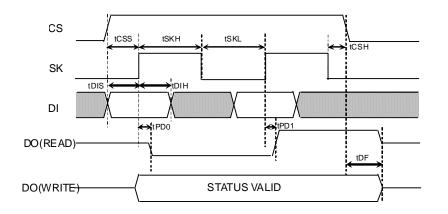

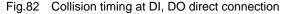

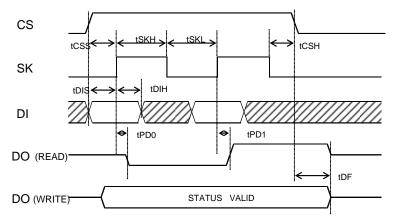

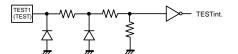

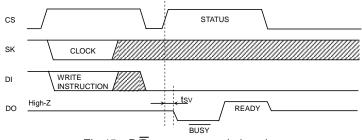

#### •Sync data input / output timing

#### Fig.1 Sync data input / output timing

OData is taken by DI sync with the rise of SK.

OAt read action, data is output from DO in sync with the rise of SK.

OThe status signal at write (READY / BUSY) is output after tCS from the fall of CS after write command input, at the area DO where CS is "H", and valid until the next command start bit is input. And, while CS is "L", DO becomes High-Z.

OAfter completion of each mode execution, set CS "L" once for internal circuit reset, and execute the following action mode.

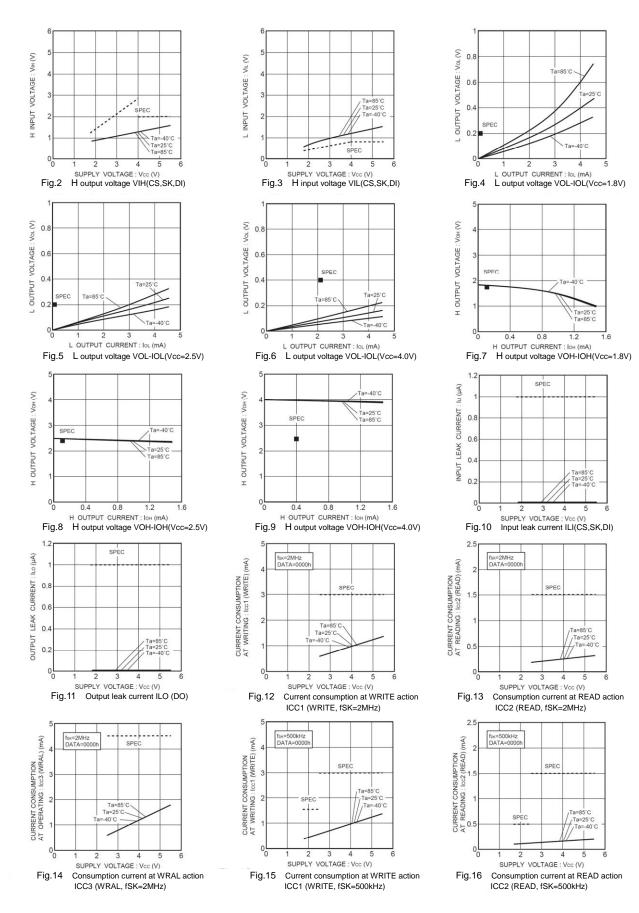

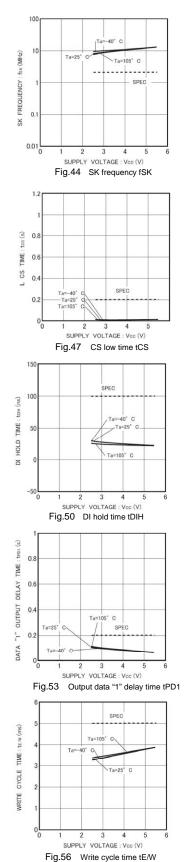

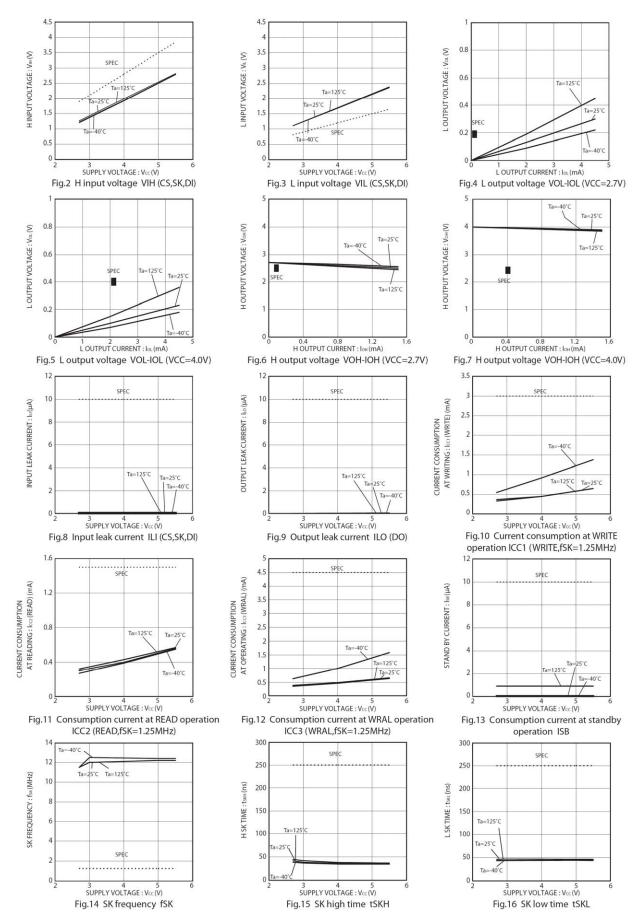

#### ●BR93L□□-W Characteristic data (The following characteristic data are Typ. values.)

5

#### ●BR93L□□-W Characteristic data (The following characteristic data are Typ. values.)

www.rohm.com © 2011 ROHM Co., Ltd. All rights reserved.

#### 8/40

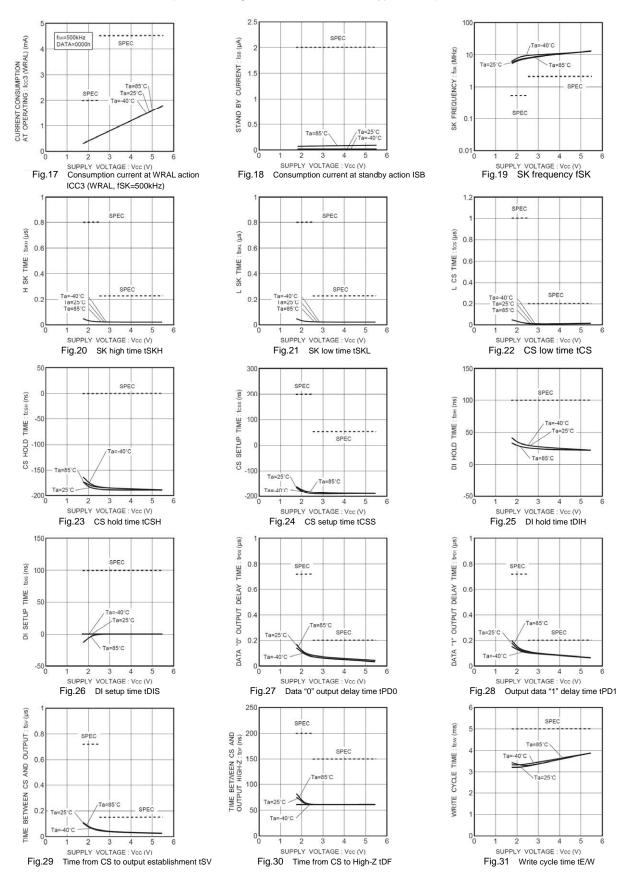

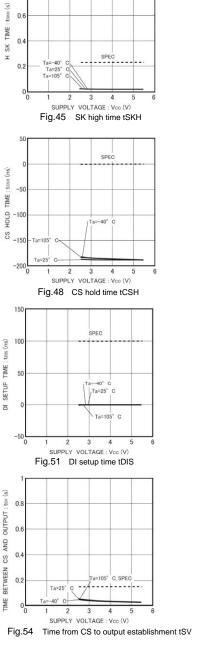

#### ●BR93A□□-WM Characteristic data (The following characteristic data are Typ. values.)

0.8

Fig.55 Time from CS to High-Z tDF

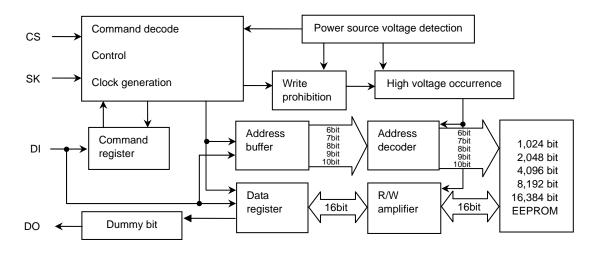

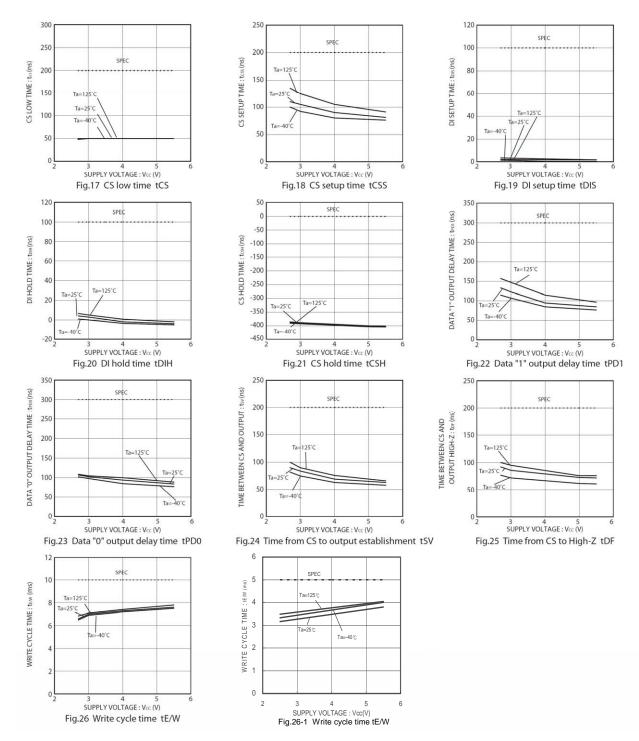

#### Block diagram

Fig.57 Block diagram

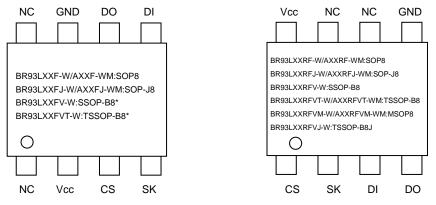

#### •Pin assignment and function

\*BR93L46/56/66-W

#### Fig.58 Pin assignment diagram

| Pin name | I/O    | Function                                                           |

|----------|--------|--------------------------------------------------------------------|

| VCC      | -      | Power source                                                       |

| GND      | -      | All input / output reference voltage, 0V                           |

| CS       | Input  | Chip select input                                                  |

| SK       | Input  | Serial clock input                                                 |

| DI       | Input  | Start bit, ope code, address, and serial data input                |

| DO       | Output | Serial data output, READY / BUSY internal condition display output |

| NC       | -      | Non connected terminal, Vcc, GND or OPEN                           |

#### Description of operations

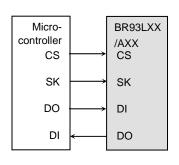

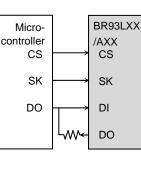

Communications of the Microwire Bus are carried out by SK (serial clock), DI (serial data input),DO (serial data output) ,and CS (chip select) for device selection.

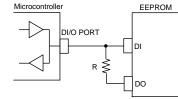

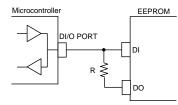

When to connect one EEPROM to a microcontroller, connect it as shown in Fig.59(a) or Fig.59(b). When to use the input and output common I/O port of the microcontroller, connect DI and DO via a resistor as shown in Fig.59(b) (Refer to pages 17/35.), and connection by 3 lines is available.

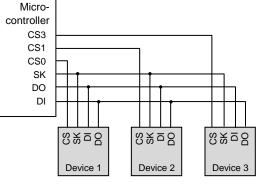

In the case of plural connections, refer to Fig. 59 (c).

Fig.59-(a) Connection by 4 lines

Fig.59-(b) Connection by 3 lines

Fig.59-(c) Connection example of plural devices

A7 of BR93L56-W/A56-WM becomes Don't Care.

A9 of BR93L76-W/A76-WM becomes Don't Care.

Fig.59 Connection method with microcontroller

Communications of the Microwire Bus are started by the first "1" input after the rise of CS. This input is called a start bit. After input of the start bit, input ope code, address and data. Address and data are input all in MSB first manners. "0" input after the rise of CS to the start bit input is all ignored. Therefore, when there is limitation in the bit width of PIO of the microcontroller, input "0" before the start bit input, to control the bit width.

#### Command mode

|                     | Start | Ope  |                                                                               |                         |                               |                    |

|---------------------|-------|------|-------------------------------------------------------------------------------|-------------------------|-------------------------------|--------------------|

| Command             | bit   | code | BR93L46-W BR93L56/66-W BR93L76/86-W<br>BR93A46-WM BR93A56/66-WM BR93A76/86-WM |                         |                               | Data               |

| Read (READ)         | 1 1   | 10   | A5,A4,A3,A2,A1,A0                                                             | A7,A6,A5,A4,A3,A2,A1,A0 | A9,A8,A7,A6,A5,A4,A3,A2,A1,A0 | D15~D0(READ DATA)  |

| Write enable (WEN)  | 1     | 00   | 1 1 ****                                                                      | 1 1 *****               | 1 1 ******                    |                    |

| Write (WRITE)       | 2 1   | 01   | A5,A4,A3,A2,A1,A0                                                             | A7,A6,A5,A4,A3,A2,A1,A0 | A9,A8,A7,A6,A5,A4,A3,A2,A1,A0 | D15~D0(WRITE DATA) |

| Write all (WRAL)    | 2 1   | 00   | 0 1 ****                                                                      | 0 1 *****               | 0 1 ******                    | D15~D0(WRITE DATA) |

| Write disable (WDS) | 1     | 00   | 0 0 ****                                                                      | 0 0 *****               | 0 0 *******                   |                    |

| Erase (ERASE)       | 1     | 11   | A5,A4,A3,A2,A1,A0                                                             | A7,A6,A5,A4,A3,A2,A1,A0 | A9,A8,A7,A6,A5,A4,A3,A2,A1,A0 |                    |

| Chip erase (ERAL)   | 1     | 00   | 1 0 ****                                                                      | 1 0 *****               | 1 0 *******                   |                    |

· Input the address and the data in MSB first manners.

As for \*, input either VIH or VIL.

\*Start bit

Acceptance of all the commands of this IC starts at recognition of the start bit.

The start bit means the first "1" input after the rise of CS.

\*1 As for read, by continuous SK clock input after setting the read command, data output of the set address starts, and

address data in significant order are sequentially output continuously. (Auto increment function)

\*2 When the read and the write all commands are executed, data written in the selected memory cell is automatically deleted, and input data is written.

#### Timing chart

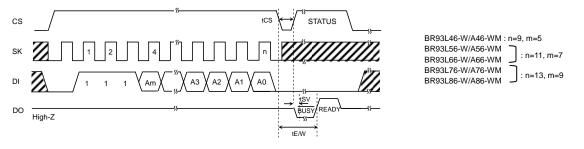

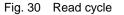

1) Read cycle (READ)

\*1 Start bit

When data "1" is input for the first time after the rise of CS, this is recognized as a start bit. And when "1" is input after plural "0" are input, it is recognized as a start bit, and the following operation is started. This is common to all the commands to described hereafter.

Fig. 60 Read cycle

OWhen the read command is recognized, input address data (16bit) is output to serial. And at that moment, at taking A0, in sync with the rise of SK, "0" (dummy bit) is output. And, the following data is output in sync with the rise of SK. This IC has an address auto increment function valid only at read command. This is the function where after the above read execution, by continuously inputting SK clock, the above address data is read sequentially. And, during the auto increment, keep CS at "H".

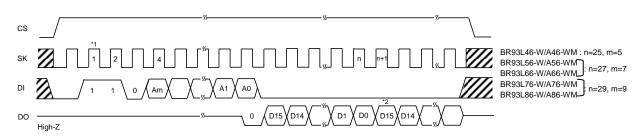

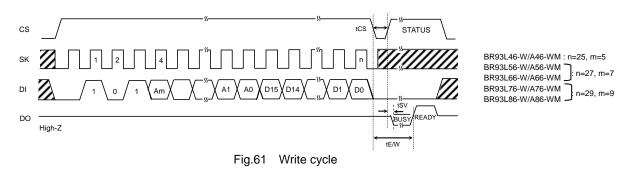

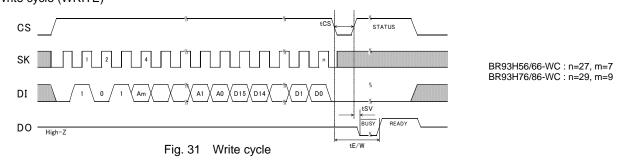

2) Write cycle (WRITE)

OIn this command, input 16bit data (D15~D0) are written to designated addresses (Am~A0). The actual write starts by the fall of CS of D0 taken SK clock.

When STATUS is not detected, (CS="L" fixed) Max. 5ms in conformity with tE/W, and when STATUS is detected (CS="H"), all commands are not accepted for areas where "L" (BUSY) is output from D0, therefore, do not input any command.

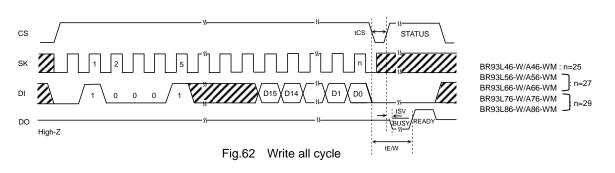

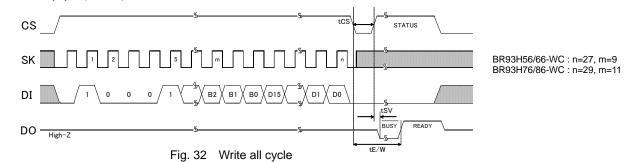

3) Write all cycyle (WRAL)

OIn this command, input 16bit data is written simultaneously to all adresses. Data is not written continuously per one word but is written in bulk, the write time is only Max. 5ms in conformity with tE/W.

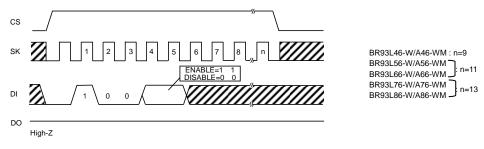

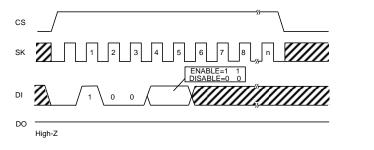

4) Write enable (WEN) / disable (WDS) cycle

Fig.63 Write enable (WEN) / disable (WDS) cycle

- O At power on, this IC is in write disable status by the internal RESET circuit. Before executing the write command, it is necessary to execute the write enable command. And, once this command is executed, it is valid unit the write disable command is executed or the power is turned off. However, the read command is valid irrespective of write enable / diable command. Input to SK after 6 clocks of this command is available by either "H" or "L", but be sure to input it.

- O When the write enable command is executed after power on, write enable status gets in. When the write disable command is executed then, the IC gets in write disable status as same as at power on, and then the write command is canceled thereafter in software manner. However, the read command is executable. In write enable status, even when the write command is input by mistake, write is started. To prevent such a mistake, it is recommended to execute the write disable command after completion of write.

- 5) Erase cycle timing (ERASE)

Fig.64 Erase cycle timing

OIn this command, data of the designated address is made into "1". The data of the designated address becomes "FFFFh". Actual ERASE starts at the fall of CS after the fall of A0 taken SK clock.

In ERASE, status can be detected in the same manner as in WRITE command.

6) Chip erase cycle timing (ERAL)

Fig.65 Chip erase cycle timing

OIn this command, data of all addresses is erased. Data of all addresses becomes "FFFFh". Actual ERASE starts at the fall of CS after the fall of the n-th clock from the start bit input. In ERAL, status can be detected in the same manner as in WRITE command.

#### Application

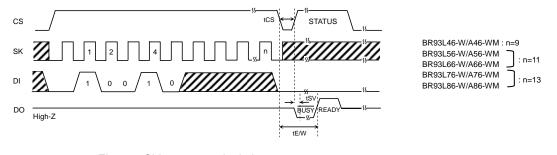

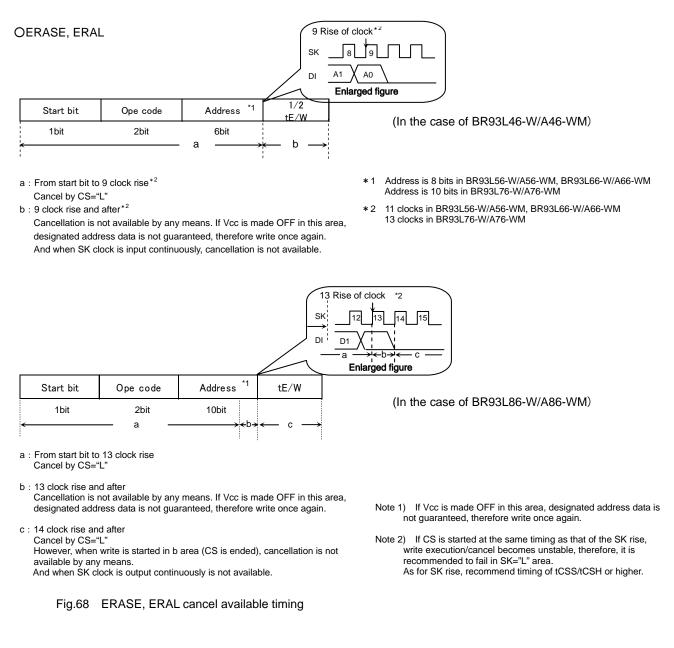

#### 1) Method to cancel each command

#### OREAD

| Start bit | Ope code | Address <sup>*1</sup> | Data  |

|-----------|----------|-----------------------|-------|

| 1bit      | 2bit     | 6bit                  | 16bit |

| ← Ca      | de. —    |                       |       |

(In the case of BR93L46-W/A46-WM)

\* 1 Address is 8 bits in BR93L56-W/A56-WM, BR93L-66W/A66-WM Address is 10 bits in BR93L76-W/A76-WM, BR93L86-W/A86-WM

·Method to cancel : cancel by CS="L"

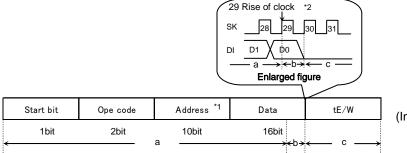

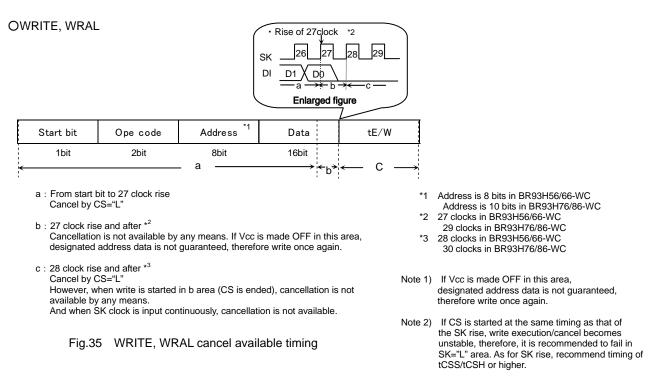

| OWRITE, WRA | L        |                       | • 25 Rise of cloc<br>SK2425<br>DI1 \D0<br>Enlarged f |       |                                   |

|-------------|----------|-----------------------|------------------------------------------------------|-------|-----------------------------------|

| Start bit   | Ope code | Address <sup>*1</sup> | Data                                                 | tE/W  | (In the case of BR93L46-W/A46-WM) |

| 1bit<br>≺   | 2bit     | 6bit<br>_ a           | 16bit                                                | ← b → |                                   |

a : From start bit to 25 clock rise\*2 Cancel by CS="L"

b: 25 clock rise and after\*2

Cancellation is not available by any means. If Vcc is made OFF in this area, designated address data is not guaranteed, therefore write once again. And when SK clock is input continuously, cancellation is not available.

\*1 Address is 8 bits in BR93L56-W/A56-WM, BR93L66-W/A66-WM Address is 10 bits in BR93L76-W/A76-WM BR93L86-W/A86-WM

27 clocks in BR93L56-W/A56-WM, BR93L66-W/A66-WM \*2

29 clocks in BR93L76-W/A76-WM BR93L86-W/A86-WM

#### (In the case of BR93L86-W/A86-WM)

a : From start bit to 29 clock rise Cancel by CS="L"

b: 29 clock rise and after

Cancellation is not available by any means. If Vcc is made OFF in this area, designated address data is not guaranteed, therefore write once again.

c: 30 clock rise and after

Cancel by CS="L"

However, when write is started in b area (CS is ended), cancellation is not available by any means

And when SK clock is output continuously is not available.

Fig.67 WRITE, WRAL cancel available timing

Note 1) If Vcc is made OFF in this area, designated address data is not guaranteed, therefore write once again.

Note 2) If CS is started at the same timing as that of the SK rise, write execution/cancel becomes unstable, therefore, it is recommended to fail in SK="L" area. As for SK rise, recommend timing of tCSS/tCSH or higher.

#### BR93LDD-W Series, 93ADD-WM Series, BR93HDD-WC Series

#### 2) At standby

#### OStandby current

When CS is "L", SK input is "L", DI input is "H", and even with middle electric potential, current does not increase.

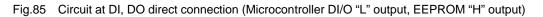

#### OTiming

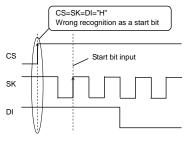

As shown in Fig.69, when SK at standby is "H", if CS is started, DI status may be read at the rise edge. At standby and at power ON/OFF, when to start CS, set SK input or DI input to "L" status. (Refer to Fig.70)

Fig.69 Wrong action timing

Fig.70 Normal action timing

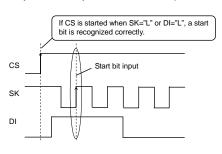

#### 3) Equivalent circuit

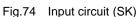

Fig.73 Input circuit (DI)

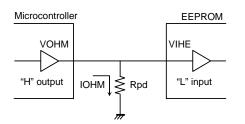

4) I/O peripheral circuit

4-1) Pull down CS.

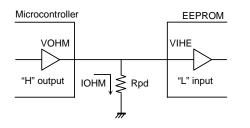

By making CS="L" at power ON/OFF, mistake in operation and mistake write are prevented. OPull down resistance Rpd of CS pin

To prevent mistake in operation and mistake write at power ON/OFF, CS pull down resistance is necessary. Select an appropriate value to this resistance value from microcontroller VOH, IOH, and VIL characteristics of this IC.

Fig.75 CS pull down resistance

Example) When V<sub>cc</sub> =5V, VIHE=2V, VOHM=2.4V, IOHM=2mA, from the equation ①,

$$Rpd \geq \frac{2.4}{2 \times 10^{-3}}$$

$$\therefore Rpd \geq 1.2 [k\Omega]$$

With the value of Rpd to satisfy the above equation, VOHM becomes 2.4V or higher, and VIHE (=2.0V), the equation ② is also satisfied.

: EEPROM VIH specifications VIHE

VOHM : Microcontroller VOH specifications

· IOHM : Microcontroller IOH specifications

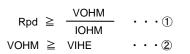

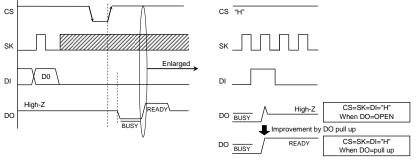

4-2) DO is available in both pull up and pull down. Do output become "High-Z" in other READY / BUSY output timing than after data output at read command and write command. When malfunction occurs at "High-Z" input of the microcontroller port connected to DO, it is necessary to pull down and pull up DO. When there is no influence upon the microcontroller actions, DO may be OPEN. If DO is OPEN, and at timing to output status READY, at timing of CS="H", SK="H", DI="H", EEPROM recognizes this as a start bit, resets READY output, and DO="High-Z", therefore, READY signal cannot be detected. To avoid such output, pull up DO pin for improvement.

Fig.76 READY output timing at DO=OPEN

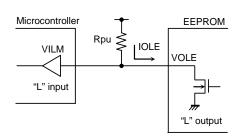

OPull up resistance Rpu and pull down resistance Rpd of DO pin

As for pull up and pull down resistance value, select an appropriate value to this resistance value from microcontroller VIH, VIL, and VOH, IOH, VOL, IOL characteristics of this IC.

$Rpu \geq \frac{Vcc-VOLE}{IOLE} \quad \cdot \quad \cdot \quad \Im$  $VOLE \leq VILM \quad \cdot \quad \cdot \quad \textcircled{4}$

Example) When  $V_{CC}$  =5V, VOLE=0.4V, IOLE=2.1mA, VILM=0.8V, from the equation (3),

Rpu

$$\geq \frac{5-0.4}{2.1 \times 10^{-3}}$$

$\therefore$  Rpu  $\geq$  2.2 [k $\Omega$ ]

With the value of Rpu to satisfy the above equation, VOLE becomes 0.4V or below, and with VILM(=0.8V), the equation 4 is also satisfied.

| <ul> <li>VOLE</li> </ul> | : EEPROM VOL specifications |

|--------------------------|-----------------------------|

|                          |                             |

| <ul> <li>IOLE</li> </ul> | : EEPROM IOL specifications |

|--------------------------|-----------------------------|

• VILM : Microcontroller VIL specifications

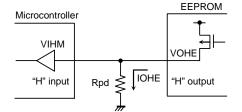

$$Rpd \geq \frac{VOHE}{IOHE} \quad \cdot \cdot \cdot \mathbb{S}$$

$$VOHE \geq VIHM \quad \cdot \cdot \cdot \mathbb{G}$$

Example) When  $V_{cc}$  =5V, VOHE=Vcc-0.2V, IOHE=0.1mA, VIHM=Vcc $\times 0.7V$  from the equation (\$),

Rpd

$$\geq \frac{5-0.2}{0.1 \times 10^{-3}}$$

$\therefore$  Rpd  $\geq$  48 [k  $\Omega$ ]

With the value of Rpd to satisfy the above equation, VOHE becomes 2.4V or below, and with VIHM (=3.5V), the equation (6) is also satisfied.

VOHE : EEPROM VOH specifications

IOHE : EEPROM IOH specifications

VIHM : Microcontroller VIH specifications

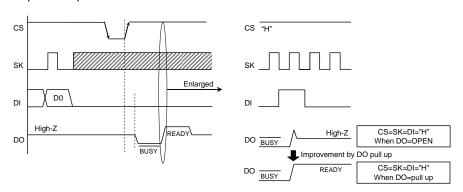

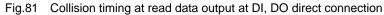

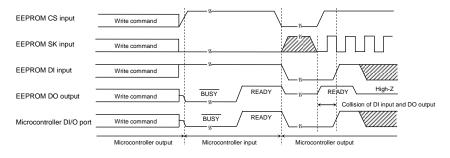

5) READY / BUSY status display (DO terminal)

Fig.78 DO pull down resistance

(common to BR93L46-W/A46-WM,BR93L56-W/A56-WM, BR93L66-W/A66-WM, BR93L76-W/A76-WM, BR93L86-W/A86-WM) This display outputs the internal status signal. When CS is started after tCS (Min.200ns) from CS fall after write command input, "H" or "L" is output.

$R/\overline{B}$  display="L" ( $\overline{BUSY}$ ) = write under execution

(DO status) After the timer circuit in the IC works and creates the period of tE/W, this time circuit completes automatically. And write to the memory cell is made in the period of tE/W, and during this period, other command is not accepted.

$R/\overline{B}$  display = "H" (READY) = command wait status

(DO status) Even after tE/W (max.5ms) from write of the memory cell, the following command is accepted.

Therefore, CS="H" in the period of tE/W, and when input is in SK, DI, malfunction may occur, therefore, DI="L" in the area CS="H". (Especially, in the case of shared input port, attention is required.)

\*Do not input any command while status signal is output. Command input in BUSY area is cancelled, but command input in READY area is accepted. Therefore, status READY output is cancelled, and malfunction and mistake write may be made.

Fig.79 R/B status output timing chart

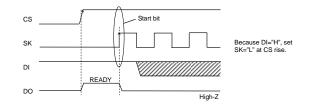

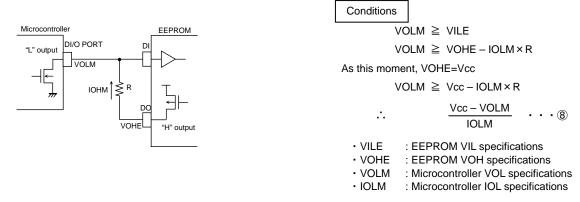

#### 6) When to directly connect DI and DO

This IC has independent input terminal DI and output terminal DO, and separate signals are handled on timing chart, meanwhile, by inserting a resistance R between these DI and DO terminals, it is possible to carry out control by 1 control line.

Fig.80 DI, DO control line common connection

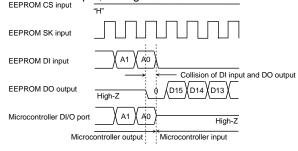

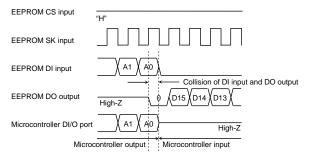

OData collision of microcontroller DI/O output and DO output and feedback of DO output to DI input. Drive from the microcontroller DI/O output to DI input on I/O timing, and signal output from DO output occur at the same

time in the following points.

- (1) 1 clock cycle to take in A0 address data at read command

- Dummy bit "0" is output to DO terminal.

$\rightarrow$ When address data A0 = "1" input, through current route occurs.

(2) Timing of CS = "H" after write command. DO terminal in READY / BUSY function output. When the next start bit input is recognized, "HIGH-Z" gets in.

Example a start of the st

$\rightarrow$ Especially, at command input after write, when CS input is started with microcontroller DI/O output "L", READY output "H" is output from DO terminal, and through current route occurs.

Feedback input at timing of these (1) and (2) does not cause disorder in basic operations, if resistance R is inserted.

Note) As for the case (2), attention must be paid to the following.

When status READY is output, DO and DI are shared, DI="H" and the microcontroller DI/O="High-Z" or the microcontroller DI/O="H", if SK clock is input, DO output is input to DI and is recognized as a start bit, and malfunction may occur. As a method to avoid malfunction, at status READY output, set SK="L", or start CS within 4 clocks after "H" of READY signal is output.

Fig.83 Start bit input timing at DI, DO direct connection

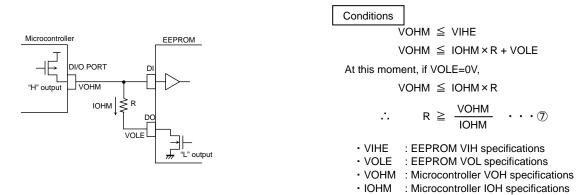

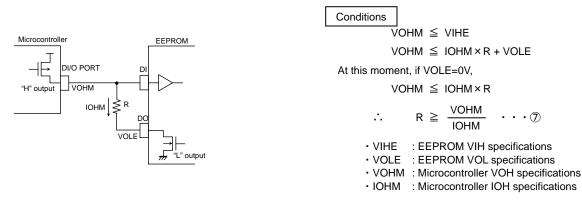

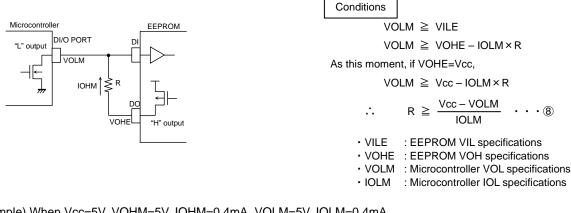

#### OSelection of resistance value R

The resistance R becomes through current limit resistance at data collision. When through current flows, noises of power source line and instantaneous stop of power source may occur. When allowable through current is defined as I, the following relation should be satisfied. Determine allowable current amount in consideration of impedance and so forth of power source line in set. And insert resistance R, and set the value R to satisfy EEPROM input level VIH/VIL even under influence of voltage decline owing to leak current and so forth. Insertion of R will not cause any influence upon basic operations.

(1) Address data A0 = "1" input, dummy bit "0" output timing

(When microcontroller DI/O output is "H", EEPROM DO outputs "L", and "H" is input to DI)

- Make the through current to EEPROM 10mA or below.

- · See to it that the level VIH of EEPROM should satisfy the following.

#### (2) DO status READY output timing

(When the microcontroller DI/O is "L", EEPROM DO output "H", and "L" is input to DI)

· Set the EEPROM input level VIL so as to satisfy the following.

Example) When Vcc=5V, VOHM=5V, IOHM=0.4mA, VOLM=5V, IOLM=0.4mA,

From the equation  $\overline{\mathcal{O}}$ ,

From the equation<sup>®</sup>,

|   | R ≧ | VOHM<br>IOHM                   |      |          | R ≧      | Vcc – VOLN<br>IOLM                 | <u>/</u>     |     |

|---|-----|--------------------------------|------|----------|----------|------------------------------------|--------------|-----|

|   | R ≧ | $\frac{5}{0.4 \times 10^{-3}}$ |      |          | R ≧      | $\frac{5-0.4}{2.1 \times 10^{-3}}$ |              |     |

| ÷ | R ≧ | 12.5 [kΩ]                      | •••• | <i>.</i> | R ≧      | 2.2 [kΩ]                           | ••••         |     |

|   |     |                                |      | Theref   | ore, fro | m the equat                        | ions (9) and | 10, |

∴ R ≧ 12.5 [kΩ]

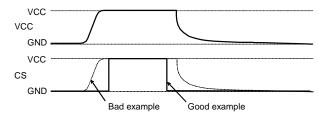

#### 7) Notes on power ON/OFF

At power ON/OFF, set CS "L".

When CS is "H", this IC gets in input accept status (active). If power is turned on in this status, noises and the likes may cause malfunction, mistake write or so. To prevent these, at power ON, set CS "L". (When CS is in "L" status, all inputs are cancelled.) And at power decline, owing to power line capacity and so forth, low power status may continue long. At this case too, owing to the same reason, malfunction, mistake write may occur, therefore, at power OFF too, set CS "L".

Fig.86 Timing at power ON/OFF

(Bad example) CS pin is pulled up to Vcc.

In this case, CS becomes "H" (active status), and EEPROM may have malfunction, mistake write owing to noise and the likes.

Even when CS input is High-Z, the status becomes like this case, which please note.

(Good example) It is "L" at power ON/OFF. Set 10ms or higher to recharge at power OFF. When power is turned on without observing this condition, IC internal circuit may not be reset, which please note.

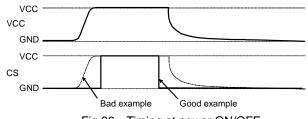

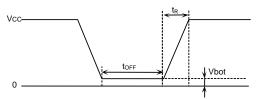

#### **OPOR** citcuit

This IC has a POR (Power On Reset) circuit as a mistake write countermeasure. After POR action, it gets in write disable status. The POR circuit is valid only when power is ON, and does not work when power is OFF. However, if CS is "H" at power ON/OFF, it may become write enable status owing to noises and the likes. For secure actions, observe the follwing conditions.

#### 1. Set CS="L"

2. Turn on power so as to satisfy the recommended conditions of tR, tOFF, Vbot for POR circuit action.

Recommended conditions of tR, tOFF, Vbot

| t <sub>R</sub> | t <sub>OFF</sub> | Vbot                     |

|----------------|------------------|--------------------------|

| 10ms or below  | 10ms or higher   | $0.3 V \mbox{ or below}$ |

| 100ms or below | 10ms or higher   | 0.2V or below            |

#### OLVCC circuit

LVCC (VCC-Lockout) circuit prevents data rewrite action at low power, and prevents wrong write. At LVCC voltage (Typ.=1.2V) or below, it prevent data rewrite.

Fig.87

#### 8) Noise countermeasures

OVCC noise (bypass capacitor)

When noise or surge gets in the power source line, malfunction may occur, therefore, for removing these, it is recommended to attach a by pass capacitor (0.1  $\mu$  F) between IC VCC and GND, At that moment, attach it as close to IC as possible.And, it is also recommended to attach a bypass capacitor between board VCC and GND.

Rise waveform diagram

#### OSK noise

When the rise time (tR) of SK is long, and a certain degree or more of noise exists, malfunction may occur owing to clock bit displacement. To avoid this, a Schmitt trigger circuit is built in SK input. The hysteresis width of this circuit is set about 0.2V, if noises exist at SK input, set the noise amplitude 0.2Vp-p or below. And it is recommended to set the rise time (tR) of SK 100ns or below. In the case when the rise time is 100ns or higher, take sufficient noise countermeasures. Make the clock rise, fall time as small as possible.

#### Note ofn use

- (1) Described numeric values and data are design representative values, and the values are not guaranteed.

- (2) We believe that application circuit examples are recommendable, however, in actual use, confirm characteristics further sufficiently. In the case of use by changing the fixed number of external parts, make your decision with sufficient margin in consideration of static characteristics and transition characteristics and fluctuations of external parts and our IC.

- (3) Absolute Maximum Ratings

If the absolute maximum ratings such as impressed voltage and action temperature range and so forth are exceeded, IC may be destructed. Do not impress voltage and temperature exceeding the absolute maximum ratings. In the case of fear exceeding the absolute maximum ratings, take physical safety countermeasures such as fuses, and see to it that conditions exceeding the absolute maximum ratings should not be impressed to IC.

(4) GND electric potential

Set the voltage of GND terminal lowest at any action condition. Make sure that each terminal voltage is not lower than that of GND terminal in consideration of transition status.

(5) Heat design

In consideration of allowable loss in actual use condition, carry out heat design with sufficient margin.

- (6) Terminal to terminal shortcircuit and wrong packaging When to package IC onto a board, pay sufficient attention to IC direction and displacement. Wrong packaging may destruct IC. And in the case of shortcircuit between IC terminals and terminals and power source, terminal and GND owing to foreign matter, IC may be destructed.

- (7) Use in a strong electromagnetic field may cause malfunction, therefore, evaluate design sufficiently

# Serial EEPROM Series High Reliability Series EEPROMs Microwire BUS

#### BR93HDD-WC Series

#### Description

BR93HDD-WC Series is a serial EEPROM of serial 3-line interface method.

#### Features

- 1) Withstands electrostatic voltage 8kV, (twice more than other series) (HBM method typ., except BR93H66RFVM-WC)

- 2) Wide action range -40°C~+125°C (-40°C~+85°C, -40°C~+105°C in other series)

- 3) Conforming to Microwire BUS

- 4) Address auto increment function at read action

- 5) Write mistake prevention function

- Write prohibition at power on Write prohibition by command code

- Write mistake prevention circuit at low voltage 6) Program cycle auto delete and auto end function

- 7) Program condition display by READY / BUSY

- 8) Low current consumption

- At write action (at 5V) : 0.6mA (Typ.) At read action (at 5V) : 0.6mA (Typ.)

- At standby action (at 5V) : 0.1µA (Typ.)(CMOS input)

- 9) Built-in noise filter CS, SK, DI terminals

- 10) Compact package SOP8/SOP-J8/MSOP8

- 11) High reliability by ROHM original Double-Cell structure

- 12) High reliability ultrafine CMOS process

- 13) Easily connectable with serial port BR93H series

- 14) Data retention for 20 years (Ta $\leq$ 125°C)

- 15) Endurance up to 1,000,000 times (Ta $\leq$ 125°C)

- 16) Data at shipment all address FFFh

#### BR93H Series

|          | P          | SOP8       | SOP-J8                  | MSOP8 |     |      |

|----------|------------|------------|-------------------------|-------|-----|------|

| Capacity | Bit format | Туре       | Power source<br>voltage | RF    | RFJ | RFVM |

| 2Kbit    | 128×16     | BR93H56-WC | 2.7~5.5V                | •     | •   |      |

| 4Kbit    | 256×16     | BR93H66-WC | 2.7~5.5V                | •     | •   | •    |

| 8Kbit    | 512×16     | BR93H76-WC | 2.7~5.5V                | •     | •   |      |

| 16Kbit   | 1K×16      | BR93H86-WC | 2.7~5.5V                |       | •   |      |

#### ●Absolute Maximum Ratings (Ta=25°C)

| Parameter                 | Symbol | Limits                     | Unit |  |

|---------------------------|--------|----------------------------|------|--|

| Impressed voltage         | VCC    | -0.3~+6.5                  | V    |  |

|                           |        | 560 (SOP8) <sup>*1</sup>   |      |  |

| Permissible dissipation   | Pd     | 560 (SOP-J8) <sup>*2</sup> | mW   |  |

|                           |        | 380 (MSOP8) <sup>*3</sup>  |      |  |

| Storage temperature range | Tstg   | -65~+150                   | °C   |  |

| Action temperature range  | Topr   | -40~+125                   | °C   |  |

| Terminal voltage          | -      | -0.3~VCC+0.3               | V    |  |

\*When using at Ta=25°C or higher, 4.5mW(\*1,\*2), 3.1mW(\*3), to be reduced per 1°C.

#### Memory cell characteristics (VCC=2.7~5.5V)

| Parameter                     |           | Limit |      | Limit  | Limit    |

|-------------------------------|-----------|-------|------|--------|----------|

| Falameter                     | Min.      | Тур.  | Max. | LIIIII | LIIIII   |

|                               | 1,000,000 | -     | -    | Times  | Ta≦85°C  |

| Endurance <sup>*1</sup>       | 500,000   | -     | -    | Times  | Ta≦105°C |

|                               | 300,000   | -     | -    | Times  | Ta≦125°C |

| Data retention *1             | 40        | -     | -    | Years  | Ta≦25°C  |

|                               | 20        | -     | -    | Years  | Ta≦125°C |

| <sup>*1</sup> Not 100% TESTED |           |       |      |        |          |

#### Recommended action conditions

| Parameter            | Symbol | Limits  | Unit |  |

|----------------------|--------|---------|------|--|

| Power source voltage | VCC    | 2.7~5.5 | N/   |  |

| Input voltage        | Vin    | 0~VCC   | V    |  |

#### ●Electrical characteristics (Unless otherwise specified, Ta=-40~+125°C, Vcc=2.7~5.5V)

| Parameter                     | Symphol | Symbol  |      | Unit    | Conditions |                                |

|-------------------------------|---------|---------|------|---------|------------|--------------------------------|

| Parameter                     | Symbol  | Min.    | Тур. | Max.    | Unit       | Conditions                     |

| "L" input voltage             | VIL     | -0.3    | -    | 0.3xVCC | V          |                                |

| "H" input voltage             | Vін     | 0.7xVCC | -    | VCC+0.3 | V          |                                |

| "L" output voltage 1          | VOL1    | 0       | -    | 0.4     | V          | IoL=2.1mA, 4.0V≦VCC≦5.5V       |

| "L" output voltage 2          | Vol2    | 0       | -    | 0.2     | V          | IoL=100μA                      |

| "H" output voltage 1          | Voh1    | 2.4     | -    | VCC     | V          | Iон=-0.4mА, 4.0V≦VCC≦5.5V      |

| "H" output voltage 2          | Voh2    | VCC-0.2 | -    | VCC     | V          | Іон=-100µА                     |

| Input leak current            | LI      | -10     | -    | 10      | μA         | VIN=0V~VCC                     |

| Output leak current           | Ilo     | -10     | -    | 10      | μA         | Vout=0V~VCC, CS=0V             |

|                               | ICC1    | -       | -    | 3.0     | mA         | fsk=1.25MHz, te/w=10ms (WRITE) |

| Current consumption at action | ICC2    | -       | -    | 1.5     | mA         | fsk=1.25MHz (READ)             |

|                               | Іссз    | -       | -    | 4.5     | mA         | fsk=1.25MHz, te/w=10ms (WRAL)  |

| Standby current               | ISB     | -       | 0.1  | 10      | μA         | CS=0V, DO=OPEN                 |

©Radiation resistance design is not made.

#### ●Action timing characteristics (Unless otherwise specified, Ta=-40~+125°C, Vcc=2.7~5.5V)

| Parameter                            | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------------------|--------|------|------|------|------|

| SK frequency                         | fsĸ    | -    | -    | 1.25 | MHz  |

| SK "H" time                          | tsкн   | 250  | -    | -    | ns   |

| SK "L" time                          | tSKL   | 250  | -    | -    | ns   |

| CS "L" time                          | tcs    | 200  | -    | -    | ns   |

| CS setup time                        | tcss   | 200  | -    | -    | ns   |

| DI setup time                        | tDIS   | 100  | -    | -    | ns   |

| CS hold time                         | tCSH   | 0    | -    | -    | ns   |

| DI hold time                         | tdiн   | 100  | -    | -    | ns   |

| Data "1" output delay time           | tPD1   | -    | -    | 300  | ns   |

| Data "0" output delay time           | tPD0   | -    | -    | 300  | ns   |

| Time from CS to output establishment | tsv    | -    | -    | 200  | ns   |

| Time from CS to High-Z               | tDF    | -    | -    | 200  | ns   |

| Write cycle time                     | tE/W   | -    | 7    | 10   | ms   |

| Write cycle time(BR93H66RFVM-WC)     | tE/W   | -    | -    | 5    | ms   |

#### •Sync data input / output timing

Fig.1 Sync data input / output timing diagram

OData is taken by DI sync with the rise of SK.

OAt read action, data is output from DO in sync with the rise of SK.

OThe status signal at write (READY / BUSY) is output after tCS from the fall of CS after write command input, at the area DO where CS is "H", and valid until the next command start bit is input. And, white CS is "L", DO becomes High-Z.

OAfter completion of each mode execution, set CS "L" once for internal circuit reset, and execute the following action mode.

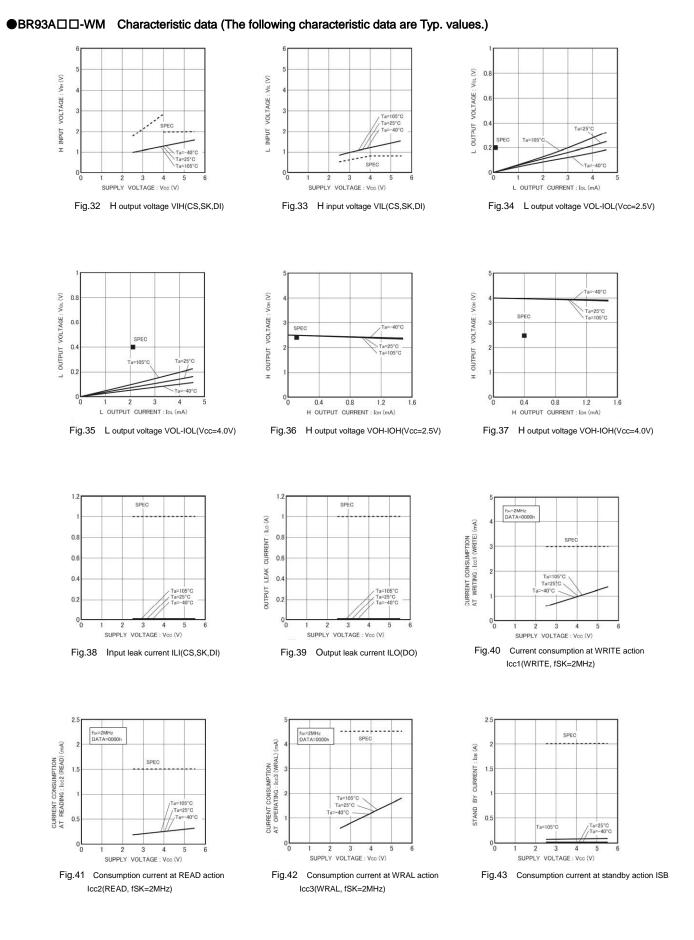

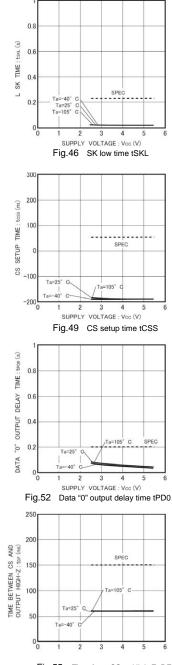

#### ●BR93H□□-WC Characteristic data

#### ●BR93H□□-WC Characteristic data

#### Block diagram

Fig. 27 Block diagram

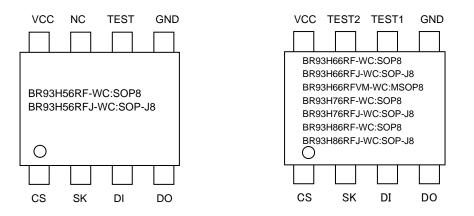

#### Pin assignment and function

| Pin name | I/O    | Function                                                           |  |

|----------|--------|--------------------------------------------------------------------|--|

| Vcc      | -      | Power source                                                       |  |

| GND      | -      | All input / output reference voltage, 0V                           |  |

| CS       | Input  | Chip select input                                                  |  |

| SK       | Input  | Serial clock input                                                 |  |

| DI       | Input  | Start bit, ope code, address, and serial data input                |  |

| DO       | Output | Serial data output, READY / BUSY internal condition display output |  |

| NC       | -      | Non connected terminal, Vcc, GND or OPEN                           |  |

| TEST1    | -      | TEST terminal, GND or OPEN                                         |  |

| TEST2    | -      | TEST terminal, Vcc, GND or OPEN                                    |  |

| TEST     | -      | TEST terminal, GND or OPEN                                         |  |

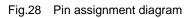

#### Description of operations

Communications of the Microwire Bus are carried out by SK (serial clock), DI (serial data input), DO (serial data output), and CS (chip select) for device selection.

When to connect one EEPROM to a microcontroller, connect it as shown in Fig.29-(a) or Fig.29-(b). When to use the input and output common I/O port of the microcontroller, connect DI and DO via a resistor as shown in Fig.29-(b) (Refer to pages 31/35.), and connection by 3 lines is available.

In the case of plural connections, refer to Fig. 29-(c).

Fig.29 Connection method with microcontroller

Communications of the Microwire Bus are started by the first "1" input after the rise of CS. This input is called a start bit. After input of the start bit, input ope code, address and data. Address and data are input all in MSB first manners.

"0" input after the rise of CS to the start bit input is all ignored. Therefore, when there is limitation in the bit width of PIO of the microcontroller, input "0" before the start bit input, to control the bit width.

#### Command mode

| Command               | Start | Ope  | Address                 |                               | Dete               |  |

|-----------------------|-------|------|-------------------------|-------------------------------|--------------------|--|

| Command               | bit   | code | BR93H56/66-WC           | BR93H76/86-WC                 | – Data             |  |

| Read (READ) *1        | 1     | 10   | A7,A6,A5,A4,A3,A2,A1,A0 | A9,A8,A7,A6,A5,A4,A3,A2,A1,A0 | D15~D0(READ DATA)  |  |

| Write enable (WEN)    | 1     | 00   | 1 1 *****               | 1 1 ******                    |                    |  |

| Write (WRITE) *2      | 1     | 01   | A7,A6,A5,A4,A3,A2,A1,A0 | A9,A8,A7,A6,A5,A4,A3,A2,A1,A0 | D15~D0(WRITE DATA) |  |

| Write all (WRAL) *2,3 | 1     | 00   | 0 1 ****B0              | 0 1 * * * * * B2,B1,B0        | D15~D0(WRITE DATA) |  |

| Write disable (WDS)   | 1     | 00   | 0 0 *****               | 0 0 ******                    |                    |  |

Input the address and the data in MSB first manners. As for \*, input either VIH or VIL.

\*Start bit

Acceptance of all the commands of this IC starts at recognition of the start bit. The start bit means the first "1" input after the rise of CS.

A7 and B0 of BR93H56-WC becomes Don't Care. A9 and B2 of BR93H76-WC becomes Don't Care.

\*1 As for read, by continuous SK clock input after setting the read command, data output of the set address starts, and address data in significant order are sequentially output continuously. (Auto increment function)

\*2 When the read and the write all commands are executed, data written in the selected memory cell is automatically deleted, and input data is written. For the write all command, data written in memory cell of the areas designated by B2, B1, and B0, are automatically

deleted, and input data is written in bulk.

#### Write all area

| B2 | B1 | B0 | Write area |

|----|----|----|------------|

| 0  | 0  | 0  | 000h~07Fh  |

| 0  | 0  | 1  | 080h~0FFh  |

| 0  | 1  | 0  | 100h~17Fh  |

| 0  | 1  | 1  | 180h~1FFh  |

| 1  | 0  | 0  | 200h~27Fh  |

| 1  | 0  | 1  | 280h~2FFh  |

| 1  | 1  | 0  | 300h~37Fh  |

| 1  | 1  | 1  | 380h~3FFh  |

Designation of B2, B1, and B0

| H56 | *  | *  | *  |

|-----|----|----|----|

| H66 | *  | *  | B0 |

| H76 | *  | B1 | B0 |

| H86 | B2 | B1 | B0 |

• The write all command is written in bulk in 2Kbit unit.

The write area can be selected up to 3bit. Confirm the settings and write areas of the above B2, B1, and B0.

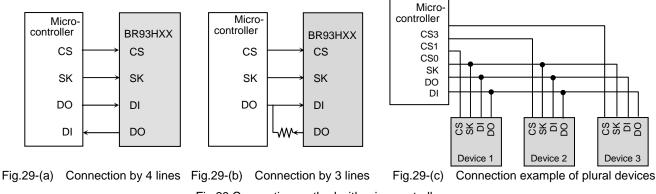

#### Timing chart

\*1 Start bit

When data "1" is input for the first time after the rise of CS, this is recognized as a start bit. And when "1" is input after plural "0" are input, it is recognized as a start bit, and the following operation is started. This is common to all the commands to described hereafter.

OWhen the read command is recognized, input address data (16bit) is output to serial. And at that moment, at taking A0, in sync with the rise of SK, "0" (dummy bit) is output. And, the following data is output in sync with the rise of SK. This IC has address auto increment function valid only at read command. This is the function where after the above read execution, by continuously inputting SK clock, the above address data is read sequentially. And, during the auto increment,

2) Write cycle (WRITE)

keep CS at "H".

OIn this command, input 16bit data (D15~D0) are written to designated addresses (Am~A0). The actual write starts by the fall of CS of D0 taken SK clock(n-th clock from the start bit input), to the rise of the (n+1)-th clock.

When STATUS is not detected, (CS="L" fixed) Max. 10ms(Max.5ms:BR93H66RFVM-WC) in conformity with tE/W, and when STATUS is detected (CS="H"), all commands are not accepted for areas where "L" (BUSY) is output from D0, therefore, do not input any command.

Write is not made even if CS is started after input of clock after (n+1)-th clocks.

Note) Take tSKH or more from the rise of the n-th clock to the fall of CS.

Write all cycyle (WRAL)

OIn this command, input 16bit data is written simultaneously to designated block for 128 words. Data is writen in bulk at a write time of only Max. 10ms(Max.5ms:BR93H66RFVM-WC) in conformity with tE/W. When writing data to all addresses, designate each block by B2, B1, and B0, and execute write. Write time is Max.10ms(Max.5ms:BR93H66RFVM-WC). The actual write starts by the fall of CS from the rise of D0 taken at SK clock (n-th clock from the start bit input), to the rise of the (n+1)-th clock. When CS is ended after clock input after the rise of the (n+1)-th clock, command is cancelled, and write is not completed.

Note)Take tSKH or more from the rise of the n-th clock to the fall of CS.

4) Write enable (WEN) / disable (WDS) cycle

BR93H56/66-WC : n=11 BR93H76/86-WC : n=13

Address is 8 bits in BR93H56-WC, and BR93H66-WC.

Address is 10 bits in BR93H76-WC, and BR93H86-WC.

Fig. 33 Write enable (WEN) / disable (WDS) cycle

OAt power on, this IC is in write disable status by the internal RESET circuit. Before executing the write command, it is necessary to execute the write enable command. And, once this command is executed, it is valid unitl the write disable command is executed or the power is turned off. However, the read command is valid irrespective of write enable / disable command. Input to SK after 6 clocks of this command is available by either "H" or "L", but be sure to input it.

OWhen the write enable command is executed after power on, write enable status gets in. When the write disable command is executed then, the IC gets in write disable status as same as at power on, and then the write command is cancelled thereafter in software manner. However, the read command is executable. In write enable status, even when the write command is input by mistake, write is started. To prevent such a mistake, it is recommended to execute the write disable command after completion of write.

\*1

#### Application

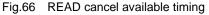

1) Method to cancel each command

#### OREAD

|    | Start bit                                      | Ope code | Address *1 | Data  |  |  |  |  |

|----|------------------------------------------------|----------|------------|-------|--|--|--|--|

|    | 1bit                                           | 2bit     | 8bit       | 16bit |  |  |  |  |

| ¦← | Cancel is available in all areas in read mode. |          |            |       |  |  |  |  |

|    | ●Method to cancel : cancel by CS= "I "         |          |            |       |  |  |  |  |

Method to cancel : cancel by CS

#### Fig.34 READ cancel available timing

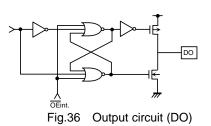

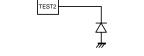

2) Equivalent circuit OOutput circuit

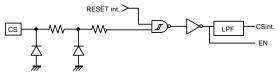

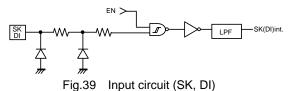

OInput circuit

Fig.37 Input circuit (CS)

Fig.38 Input circuit (TEST1, TEST)

Fig.40 Input circuit (TEST2)

- 3) I/O peripheral circuit

- 3-1) Pull down CS.

By making CS="L" at power ON/OFF, mistake in operation and mistake write are prevented. Refer to the item 6) Notes at power ON/OFF in page 34/35.

#### OPull down resistance Rpd of CS pin

To prevent mistake in operation and mistake write at power ON/OFF, CS pull down resistance is necessary. Select an appropriate value to this resistance value from microcontroller VOH, IOH, and VIL characteristics of this IC.

V

Fig.41 CS pull down resistance

| Rpd ≧   | VOHM | •••①    |

|---------|------|---------|

| itipu ≦ | IOHM |         |

| ОНМ ≧   | VIHE | · · · 2 |

Example) When V<sub>CC</sub> =5V, VIHE=2V, VOHM=2.4V, IOHM=2mA, from the equation 1,

$$Rpd \geq \frac{2.4}{2 \times 10^{-3}}$$

$\therefore$  Rpd  $\geq$  1.2 [k  $\Omega$ ]

With the value of Rpd to satisfy the above equation, VOHM becomes 2.4V or higher, and VIHE (=2.0V), the equation 2 is also satisfied.

- VIHE : EEPROM VIH specifications

- VOHM : Microcontroller VOH specifications

- IOHM :Microcontroller IOH specifications

3-2) DO is available in both pull up and pull down.

Do output become "High-Z" in other READY / BUSY output timing than after data output at read command and write command. When malfunction occurs at "High-Z" input of the microcontroller port connected to DO, it is necessary to pull down and pull up DO. When there is no influence upon the microcontroller actions, DO may be OPEN. If DO is OPEN, and at timing to output status READY, at timing of CS="H", SK="H", DI="H", EEPROM recognizes thisas a start bit, resets READY output, and DO="High-Z", therefore, READY signal cannot be detected. To avoid such output, pull up DO pin for improvement.

Fig.42 READY output timing at DO=OPEN

OPull up resistance Rpu and pull down resistance Rpd of DO pin

As for pull up and pull down resistance value, select an appropriate value to this resistance value from microcontroller VIH, VIL, and VOH, IOH, VOL, IOL characteristics of this IC.

VOLE

IOLE

VILM

$$Rpu \ge \frac{Vcc - VOLE}{IOLE} \cdots 3$$

Example) When  $V_{CC}$  =5V, VOLE=0.4V, IOLE=2.1mA, VILM=0.8V, from the equation (3),

$$\mathsf{Rpu} \geq \frac{5-0.4}{2.1 \times 10^{-3}}$$

$\therefore$  Rpu  $\geq$  2.2 [k $\Omega$ ]

With the value of Rpu to satisfy the above equation, VOLE becomes 0.4V or below, and with VILM(=0.8V), the equation 4 is also satisfied.

VOLE : EEPROM VOL specifications

IOLE : EEPROM IOL specifications

VILM : Microcontroller VIL specifications

$$Rpd \ge \frac{VOHE}{IOHE} \cdots (5)$$

Example) When V<sub>cc</sub> =5V, VOHE=Vcc-0.2V, IOHE=0.1mA, VIHM=Vcc $\times 0.7$ V from the equation (5)

$$\mathsf{Rpd} \geq \frac{5-0.2}{0.1 \times 10^{-3}}$$

Rpd ≧ 48[kΩ]

÷.,

With the value of Rpd to satisfy the above equation, VOHE becomes 2.4V or below, and with VIHM (=3.5V), the equation 6 is also satisfied.

VOHE : EEPROM VOH specifications

| • | IOHE | : EEPROM IOH specifications |

|---|------|-----------------------------|

VIHM : Microcontroller VIH specifications

Fig.43 DO pull up resistance

Fig.44 DO pull down resistance

#### OREADY / BUSY status display (DO terminal)

(common to BR93H56-WC, BR93H66-WC, BR93H76-WC, BR93H86-WC) This display outputs the internal status signal. When CS is started after tCS (Min.200ns) from CS fall after write command input, "H" or "L" output.

#### $R/\overline{B}$ display="L" ( $\overline{BUSY}$ ) = write under execution

(DO status) After the timer circuit in the IC works and creates the period of tE/W, this time circuit completes automatically. And write to the memory cell is made in the period of tE/W, and during this period, other command is not

accepted.

$R/\overline{B}$  display = "H" (READY) = command wait status

<sup>(DO status)</sup> Even after tE/W (max.10ms) (Max.5ms:BR93H66RFVM-WC) from write of the memory cell, the following command is accepted.

Therefore, CS="H" in the period of tE/W, and when input is in SK, DI, malfunction may occur, therefore,

#### DI="L" in the area

CS="H". (Especially, in the case of shared input port, attention is required.)

\*Do not input any command while status signal is output. Command input in BUSY area is cancelled, but command input in READY area is accepted. Therefore, status READY output is cancelled, and malfunction and mistake write may be made.

Fig.45 R/B status output timing chart

#### 4) When to directly connect DI and DO

This IC has independent input terminal DI and output terminal DO, and separate signals are handled on timing chart, meanwhile, by inserting a resistance R between these DI and DO terminals, it is possible to carry out control by 1 control line.

Fig.46 DI, DO control line common connection

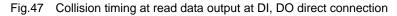

OData collision of microcontroller DI/O output and DO output and feedback of DO output to DI input.

Drive from the microcontroller DI/O output to DI input on I/O timing, and signal output from DO output occur at the same time in the following points.

4-1) 1 clock cycle to take in A0 address data at read command

Dummy bit "0" is output to DO terminal.

$\rightarrow$ When address data A0 = "1" input, through current route occurs.

4-2) Timing of CS = "H" after write command. DO terminal in READY / BUSY function output.

When the next start bit input is recognized, "HIGH-Z" gets in.

→Especially, at command input after write, when CS input is started with microcontroller DI/O output "L",

READY output "H" is output from DO terminal, and through current route occurs.

Feedback input at timing of these 4-1) and 4-2) does not cause disorder in basic operations, if resistance R is inserted.

Fig.48 Collision timing at DI, DO direct connection

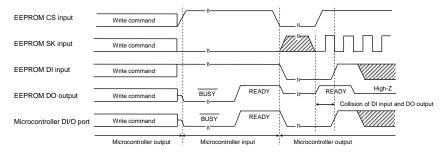

OSelection of resistance value R

The resistance R becomes through current limit resistance at data collision. When through current flows, noises of power source line and instantaneous stop of power source may occur. When allowable through current is defined as I, the following relation should be satisfied. Determine allowable current amount in consideration of impedance and so forth of power source line in set. And insert resistance R, and set the value R to satisfy EEPROM input level VIH/VIL, even under influence of voltage decline owing to leak current and so forth. Insertion of R will not cause any influence upon basic operations.

4-3) Address data A0 = "1" input, dummy bit "0" output timing

(When microcontroller DI/O output is "H", EEPROM DO outputs "L", and "H" is input to DI)

• Make the through current to EEPROM 10mA or below.

- See to it that the input level VIH of EEPROM should satisfy the following.

Fig.49 Circuit at DI, DO direct connection (Microcontroller DI/O "H" output, EEPROM "L" output)

#### 4-4) DO status READY output timing

- (When the microcontroller DI/O is "L", EEPROM DO outputs "H", and "L" is input to DI)

- $\boldsymbol{\cdot}$  Set the EEPROM input level VIL so as to satisfy the following.

Example) When Vcc=5V, VOHM=5V, IOHM=0.4mA, VOLM=5V, IOLM=0.4mA,

| From        | the equ | ation ⑦,                       |      | From | n the eq | uation   | 8,                                   |                         |

|-------------|---------|--------------------------------|------|------|----------|----------|--------------------------------------|-------------------------|

|             | R ≧     | VOHM<br>IOHM                   |      |      |          | R ≧ \    | /cc – VOLN<br>IOLM                   | ļ                       |

|             | R ≧     | $\frac{5}{0.4 \times 10^{-3}}$ |      |      |          | R ≧      | $\frac{5 - 0.4}{2.1 \times 10^{-3}}$ |                         |

| <i>.</i> :. | R ≧     | 12.5 [kΩ]                      | •••• |      | <i>.</i> | R ≧      | 2.2 [kΩ]                             | ••••                    |

|             |         |                                |      |      | Theref   | ore, fro | m the equat                          | ions $(9)$ and $(10)$ , |

|             |         |                                |      |      | <i>.</i> | R ≧      | 12.5 [kΩ]                            |                         |

Fig.50 Circuit at DI, DO direct connection (Microcontroller DI/O "L" output, EEPROM "H" output)

#### 5) Notes at test pin wrong input

There is no influence of external input upon TEST2 pin. For TEST1 (TEST)pin, input must be GND or OPEN. If H level is input, the following may occur,

\* BR93H56-WC, BR93H66-WC, address 8 bits

- 1. At WEN, WDS, READ command input There is no influence by TEST1 (TEST) pin.

- 2. WRITE, WRAL command input

|   |           | 10 bits        |                 |        |                               |

|---|-----------|----------------|-----------------|--------|-------------------------------|

|   | Start bit | Ope code       | Address*        | Data   | tE/W                          |

|   | 1bits     | 2bits          | 8bits           | 16bits |                               |

| ← |           | a              |                 |        | $\longleftrightarrow$         |

|   | Fig.51 T  | EST1(TEST) pin | wrong input tim | ning   | Write start<br>CS rise timing |

a : There is no influence by TEST1 (TEST) pin.

b : If H during write execution, it may not be written correctly. And H area remains BUSY and READY does not go back. Avoid noise input, and at use, be sure to connect it to GND terminal or set it OPEN.

#### 6) Notes on power ON/OFF

At power ON/OFF, set CS "L".

When CS is "H", this IC gets in input accept status (active). At power ON, set CS "L" to prevent malfunction from noise. (When CS is in "L" status, all inputs are cancelled.) At power decline low power status may prevail. Therefore, at power OFF, set CS "L" to prevent malfunction from noise.

Fig.52 Timing at power ON/OFF

(Bad example) CS pin is pulled up to Vcc.

In this case, CS becomes "H" (active status), EEPROM may malfunction or have write error due to noises. This is true even when CS input is High-Z.

(Good example) It is "L" at power ON/OFF. Set 10ms or higher to recharge at power OFF. When power is turned on without observing this condition, IC internal circuit may not be reset.

#### OPOR citcuit

This IC has a POR (Power On Reset) circuit as a mistake write countermeasure. After POR action, it gets in write disable status. The POR circuit is valid only when power is ON, and does not work when power is OFF. However, if CS is "H" at power ON/OFF, it may become write enable status owing to noises and the likes. For secure actions, observe the follwing conditions.

#### 1. Set CS="L"

2. Turn on power so as to satisfy the recommended conditions of tR, tOFF, Vbot for POR circuit action.

| Recommended conditions of tR, tOFF, Vbot |                |                          |  |  |  |

|------------------------------------------|----------------|--------------------------|--|--|--|

| t <sub>R</sub>                           | Vbot           |                          |  |  |  |

| 10ms or below                            | 10ms or higher | $0.3 V \mbox{ or below}$ |  |  |  |

| 100ms or below                           | 10ms or higher | 0.2V or below            |  |  |  |

#### OLVCC circuit

LVCC (VCC-Lockout) circuit prevents data rewrite action at low power, and prevents wrong write.

Fig.53 Rise waveform diagram

At LVCC voltage (Typ.=1.9V) or below, it prevent data rewrite.

#### 7) Noise countermeasures

OVCC noise (bypass capacitor)

When noise or surge gets in the power source line, malfunction may occur, therefore, for removing these, it is recommended to attach a by pass capacitor (0.1  $\mu$  F) between IC VCC and GND, At that moment, attach it as close to IC as possible.And, it is also recommended to attach a bypass capacitor between board VCC and GND.

#### OSK noise

When the rise time (tR) of SK is long, and a certain degree or more of noise exists, malfunction may occur owing to clock bit displacement.

To avoid this, a Schmitt trigger circuit is built in SK input. The hysteresis width of this circuit is set about 0.3, if noises exist at SK input, set the noise amplitude 0.3p-p or below. And it is recommended to set the rise time (tR) of SK 100ns or below. In the case when the rise time is 100ns or higher, take sufficient noise countermeasures. Make the clock rise, fall time as small as possible.

#### Cautions on use

- (1) Described numeric values and data are design representative values, and the values are not guaranteed.

- (2) We believe that application circuit examples are recommendable, however, in actual use, confirm characteristics further sufficiently. In the case of use by changing the fixed number of external parts, make your decision with sufficient margin in consideration of static characteristics and transition characteristics and fluctuations of external parts and our IC.

- (3) Absolute Maximum Ratings

If the absolute maximum ratings such as impressed voltage and action temperature range and so forth are exceeded, IC may be destructed. Do not impress voltage and temperature exceeding the absolute maximum ratings. In the case of fear exceeding the absolute maximum ratings, take physical safety countermeasures such as fuses, and see to it that conditions exceeding the absolute maximum ratings should not be impressed to IC.

(4) GND electric potential

Set the voltage of GND terminal lowest at any action condition. Make sure that each terminal voltage is not lower than that of GND terminal in consideration of transition status.

(5) Heat design

In consideration of allowable loss in actual use condition, carry out heat design with sufficient margin.

- (6) Terminal to terminal shortcircuit and wrong packaging When to package IC onto a board, pay sufficient attention to IC direction and displacement. Wrong packaging may destruct IC. And in the case of shortcircuit between IC terminals and terminals and power source, terminal and GND owing to foreign matter, IC may be destructed.

- (7) Use in a strong electromagnetic field may cause malfunction, therefore, evaluate design sufficiently.

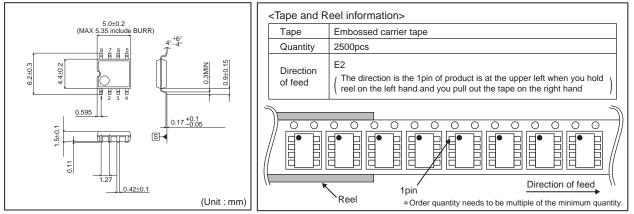

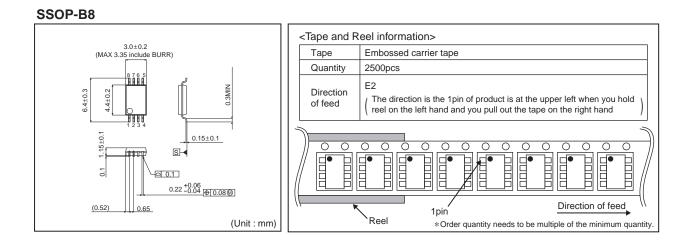

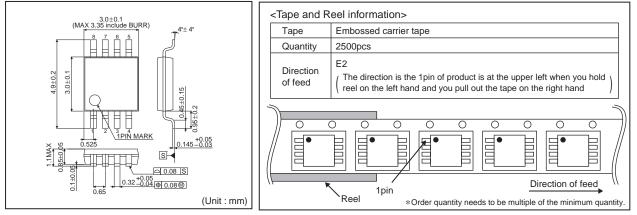

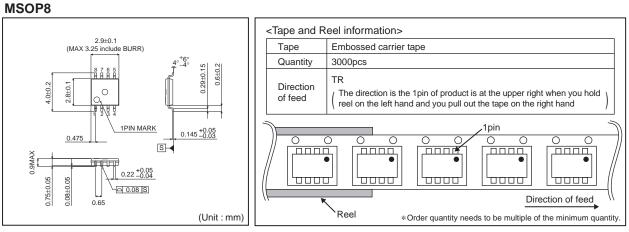

#### SOP8

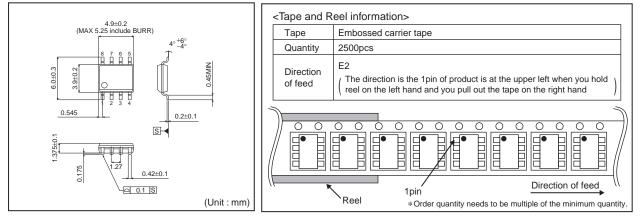

SOP-J8

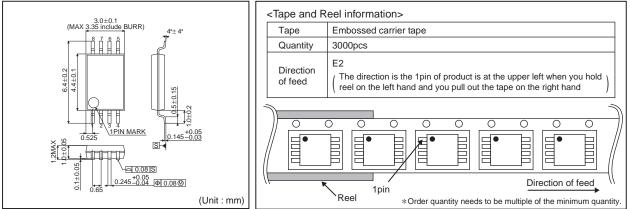

**TSSOP-B8**

**TSSOP-B8J**

# Notice

#### Precaution on using ROHM Products

1. Our Products are designed and manufactured for application in ordinary electronic equipments (such as AV equipment, OA equipment, telecommunication equipment, home electronic appliances, amusement equipment, etc.). If you intend to use our Products in devices requiring extremely high reliability (such as medical equipment <sup>(Note 1)</sup>, transport equipment, traffic equipment, aircraft/spacecraft, nuclear power controllers, fuel controllers, car equipment including car accessories, safety devices, etc.) and whose malfunction or failure may cause loss of human life, bodily injury or serious damage to property ("Specific Applications"), please consult with the ROHM sales representative in advance. Unless otherwise agreed in writing by ROHM in advance, ROHM shall not be in any way responsible or liable for any damages, expenses or losses incurred by you or third parties arising from the use of any ROHM's Products for Specific Applications.

| JAPAN  | USA    | EU         | CHINA  |

|--------|--------|------------|--------|

| CLASSⅢ | CLASSⅢ | CLASS II b | CLASSI |

| CLASSⅣ |        | CLASSⅢ     |        |

- 2. ROHM designs and manufactures its Products subject to strict quality control system. However, semiconductor products can fail or malfunction at a certain rate. Please be sure to implement, at your own responsibilities, adequate safety measures including but not limited to fail-safe design against the physical injury, damage to any property, which a failure or malfunction of our Products may cause. The following are examples of safety measures:

- [a] Installation of protection circuits or other protective devices to improve system safety

- [b] Installation of redundant circuits to reduce the impact of single or multiple circuit failure

- 3. Our Products are designed and manufactured for use under standard conditions and not under any special or extraordinary environments or conditions, as exemplified below. Accordingly, ROHM shall not be in any way responsible or liable for any damages, expenses or losses arising from the use of any ROHM's Products under any special or extraordinary environments or conditions. If you intend to use our Products under any special or extraordinary environments or conditions (as exemplified below), your independent verification and confirmation of product performance, reliability, etc, prior to use, must be necessary:

- [a] Use of our Products in any types of liquid, including water, oils, chemicals, and organic solvents

- [b] Use of our Products outdoors or in places where the Products are exposed to direct sunlight or dust

- [C] Use of our Products in places where the Products are exposed to sea wind or corrosive gases, including Cl<sub>2</sub>, H<sub>2</sub>S, NH<sub>3</sub>, SO<sub>2</sub>, and NO<sub>2</sub>

- [d] Use of our Products in places where the Products are exposed to static electricity or electromagnetic waves

- [e] Use of our Products in proximity to heat-producing components, plastic cords, or other flammable items

- [f] Sealing or coating our Products with resin or other coating materials

- [g] Use of our Products without cleaning residue of flux (even if you use no-clean type fluxes, cleaning residue of flux is recommended); or Washing our Products by using water or water-soluble cleaning agents for cleaning residue after soldering

- [h] Use of the Products in places subject to dew condensation

- 4. The Products are not subject to radiation-proof design.

- 5. Please verify and confirm characteristics of the final or mounted products in using the Products.

- 6. In particular, if a transient load (a large amount of load applied in a short period of time, such as pulse. is applied, confirmation of performance characteristics after on-board mounting is strongly recommended. Avoid applying power exceeding normal rated power; exceeding the power rating under steady-state loading condition may negatively affect product performance and reliability.

- 7. De-rate Power Dissipation (Pd) depending on Ambient temperature (Ta). When used in sealed area, confirm the actual ambient temperature.

- 8. Confirm that operation temperature is within the specified range described in the product specification.

- 9. ROHM shall not be in any way responsible or liable for failure induced under deviant condition from what is defined in this document.

#### Precaution for Mounting / Circuit board design

- 1. When a highly active halogenous (chlorine, bromine, etc.) flux is used, the residue of flux may negatively affect product performance and reliability.

- 2. In principle, the reflow soldering method must be used; if flow soldering method is preferred, please consult with the ROHM representative in advance.