# Rambus<sup>®</sup> XDR<sup>™</sup> Clock Generator

#### **Features**

- Meets Rambus<sup>®</sup> Extended Data Rate (XDR<sup>™</sup>) clocking requirements

- 25 ps typical cycle-to-cycle jitter

□ 135 dBc/Hz typical phase noise at 20 MHz offset

- 100 or 133 MHz differential clock input

- 300–800 MHz high speed clock support

- Quad (open drain) differential output drivers

- Supports frequency multipliers: 3, 4, 5, 6, 8, 9/2, 15/2, and 15/4

- Spread Aware<sup>™</sup>

- 2.5 V operation

- 28-pin TSSOP package

- For a complete list of related documentation, click here.

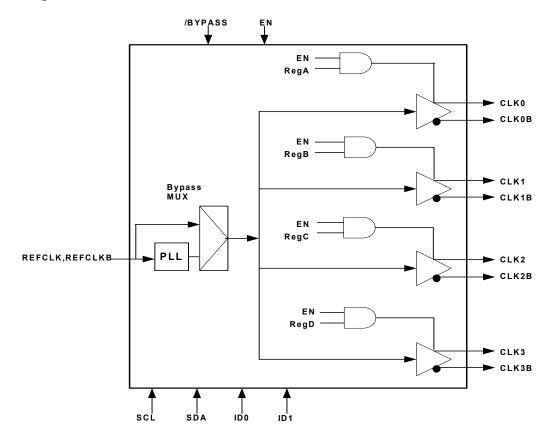

# **Logic Block Diagram**

# Contents

| Pinouts                            | 3  |

|------------------------------------|----|

| Pin Definitions                    | 4  |

| PLL Multiplier                     | 5  |

| Device ID and SMBus Device Address | 6  |

| Modes of Operation                 | 6  |

| SMBus Protocol                     | 7  |

| Input Clock Signal                 | 7  |

| SMBus Data Byte Definitions        | 7  |

| Absolute Maximum Conditions        | 9  |

| DC Operating Conditions            | 9  |

| AC Operating Conditions            |    |

| DC Electrical Specifications       | 11 |

| AC Electrical Specification        |    |

| Test and Measurement Setup         |    |

| Signal Waveforms                   | 13 |

|                                    |    |

| Jitter                                  | 13 |

|-----------------------------------------|----|

| Ordering Information                    | 15 |

| Ordering Code Definitions               |    |

| Package Drawing and Dimension           |    |

| Acronyms                                |    |

| Document Conventions                    |    |

| Units of Measure                        | 17 |

| Document History Page                   |    |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      |    |

| Products                                |    |

| PSoC® Solutions                         |    |

| Cypress Developer Community             |    |

| Technical Support                       |    |

|                                         |    |

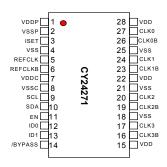

# **Pinouts**

Figure 1. 28-pin TSSOP pinout

# **Pin Definitions**

28-pin TSSOP

| Pin No. | Name    | I/O | Description                                             |

|---------|---------|-----|---------------------------------------------------------|

| 1       | VDDP    | PWR | 2.5 V power supply for phased lock loop (PLL)           |

| 2       | VSSP    | GND | Ground                                                  |

| 3       | ISET    | I   | Set clock driver current (external resistor)            |

| 4       | VSS     | GND | Ground                                                  |

| 5       | REFCLK  | I   | Reference clock input (connect to clock source)         |

| 6       | REFCLKB | I   | Complement of reference clock (connect to clock source) |

| 7       | VDDC    | PWR | 2.5 V power supply for core                             |

| 8       | VSSC    | GND | Ground                                                  |

| 9       | SCL     | I   | SMBus clock (connect to smbus)                          |

| 10      | SDA     | I   | SMBus data (connect to smbus)                           |

| 11      | EN      | I   | Output Enable (CMOS signal)                             |

| 12      | ID0     | I   | Device ID (CMOS signal)                                 |

| 13      | ID1     | I   | Device ID (CMOS signal)                                 |

| 14      | /BYPASS | I   | REFCLK bypassing PLL (CMOS signal)                      |

| 15      | VDD     | PWR | Power supply for outputs                                |

| 16      | CLK3B   | 0   | Complement clock output                                 |

| 17      | CLK3    | 0   | Clock output                                            |

| 18      | VSS     | GND | Ground                                                  |

| 19      | CLK2B   | 0   | Complement clock output                                 |

| 20      | CLK2    | 0   | Clock output                                            |

| 21      | VSS     | GND | Ground                                                  |

| 22      | VDD     | PWR | Power supply for outputs                                |

| 23      | CLK1B   | 0   | Complement clock output                                 |

| 24      | CLK1    | 0   | Clock output                                            |

| 25      | VSS     | GND | Ground                                                  |

| 26      | CLK0B   | 0   | Complement clock output                                 |

| 27      | CLK0    | 0   | Clock output                                            |

| 28      | VDD     | PWR | Power supply for outputs                                |

# **PLL Multiplier**

Table 1 shows the frequency multipliers in the PLL, selectable by programming the SMBus registers MULT0, MULT1, and MULT2. Default multiplier at power up is 4.

Table 1. PLL Multiplier Selection

|       | Register |       | Eroguanov Multipliar | Output Frequency (MHz)                          |                                              |  |  |  |

|-------|----------|-------|----------------------|-------------------------------------------------|----------------------------------------------|--|--|--|

| MULT2 | MULT1    | MULT0 | Frequency Multiplier | REFCLK = $100 \text{ MHz}^{[1]}$ , REFSEL = $0$ | REFCLK = 133 MHz <sup>[1]</sup> , REFSEL = 1 |  |  |  |

| 0     | 0        | 0     | 3                    | 300                                             | 400                                          |  |  |  |

| 0     | 0        | 1     | 4                    | 400 <sup>[2]</sup>                              | 533 <sup>[3]</sup>                           |  |  |  |

| 0     | 1        | 0     | 5                    | 500                                             | 667                                          |  |  |  |

| 0     | 1        | 1     | 6                    | 600                                             | 800                                          |  |  |  |

| 1     | 0        | 0     | 8                    | 800                                             | 1067 <sup>[3]</sup>                          |  |  |  |

| 1     | 0        | 1     | 9/2                  | 450                                             | 600                                          |  |  |  |

| 1     | 1        | 0     | 15/2                 | 750                                             | 1000 <sup>[3]</sup>                          |  |  |  |

| 1     | 1        | 1     | 15/4                 | 375                                             | 500                                          |  |  |  |

Output frequencies shown in Table 1 are based on nominal input frequencies of 100 MHz and 133.3 MHz. The PLL multipliers are applicable to spread spectrum

modulated input clock with maximum and minimum input cycle time. The REFSEL bit in SMBus 81h is set correctly as shown.

<sup>2.</sup> Default PLL multiplier at power up.

<sup>3.</sup> Contact the factory if operation at these frequencies is required.

#### **Device ID and SMBus Device Address**

The device ID (ID0 and ID1) is a part of the SMBus device 8-bit address. The least significant bit of the address designates a write or read operation. Table 2 shows the addresses for four CY24271 devices on the same SMBus.

#### **Modes of Operation**

The modes of operation are determined by the logic signals applied to the EN and /BYPASS pins and the values in the five

SMBus Registers: RegTest, RegA, RegB, RegC, and RegD. Table 3 shows selection from one to all four of the outputs, the Outputs Disabled Mode (EN = low), and Bypass Mode (EN = high, /BYPASS = low). There is an option reserved for vendor test. Disabled outputs are set to High Z.

At power up, the SMBus registers default to the last entry in Table 3. The value at RegTest is 0. The values at RegA, RegB, RegC, and RegD are all '1'. Thus, all outputs are controlled by the logic applied to EN and /or BYPASS.

Table 2. SMBus Device Addresses for CY24271

| XCG    |           | Hex Address | 8-bit SMBus Device Address Including Operation |                            |   |   |     |     |     |          |   |   |  |   |

|--------|-----------|-------------|------------------------------------------------|----------------------------|---|---|-----|-----|-----|----------|---|---|--|---|

| Device | Operation | Hex Address | Fi                                             | Five Most Significant Bits |   |   | its | ID1 | ID0 | WR# / RD |   |   |  |   |

| 0      | Write     | D8          |                                                |                            |   |   |     | 0   | 0   | 0        |   |   |  |   |

|        | Read      | D9          |                                                |                            |   |   |     |     |     |          |   |   |  | 1 |

| 1      | Write     | DA          |                                                |                            |   |   |     | 0   | 1   | 0        |   |   |  |   |

| '      | Read      | DB          | 1                                              | 1                          | 1 | 1 | 0   | 1   | 1   |          | ' | 1 |  |   |

| 2      | Write     | DC          | '                                              | '                          |   | ' | '   | 1   | 1 0 | 0        |   |   |  |   |

| 2      | Read      | DD          |                                                |                            |   |   |     | '   | U   | 1        |   |   |  |   |

| 3      | Write     | DE          |                                                |                            |   |   |     | 1   | 1   | 0        |   |   |  |   |

| 3      | Read      | DF          |                                                |                            |   |   |     |     |     | 1        |   |   |  |   |

Table 3. Modes of Operation for CY24271

| EN | /BYPASS | RegTest          | RegA             | RegB             | RegC             | RegD             | CLK0/CLK0B                        | CLK1/CLK1B         | CLK2/CLK2B         | CLK3/CLK3B         |

|----|---------|------------------|------------------|------------------|------------------|------------------|-----------------------------------|--------------------|--------------------|--------------------|

| L  | Х       | Х                | Х                | Х                | Х                | Х                | High Z                            | High Z             | High Z             | High Z             |

| Н  | X       | 1                | Х                | Х                | Х                | Х                |                                   | Reserved for       | Vendor Test        |                    |

| Н  | L       | 0                | Х                | Х                | Х                | Х                | REFCLK/<br>REFCLKB <sup>[4]</sup> | REFCLK/<br>REFCLKB | REFCLK/<br>REFCLKB | REFCLK/<br>REFCLKB |

| Н  | Н       | 0                | 0                | 0                | 0                | 0                | High Z                            | High Z             | High Z             | High Z             |

| Н  | Н       | 0                | 0                | 0                | 0                | 1                | High Z                            | High Z             | High Z             | CLK/CLKB           |

| Н  | Н       | 0                | 0                | 0                | 1                | 0                | High Z                            | High Z             | CLK/CLKB           | High Z             |

| Н  | Н       | 0                | 0                | 0                | 1                | 1                | High Z                            | High Z             | CLK/CLKB           | CLK/CLKB           |

| Н  | Н       | 0                | 0                | 1                | 0                | 0                | High Z                            | CLK/CLKB           | High Z             | High Z             |

| Н  | Н       | 0                | 0                | 1                | 0                | 1                | High Z                            | CLK/CLKB           | High Z             | CLK/CLKB           |

| Н  | Н       | 0                | 0                | 1                | 1                | 0                | High Z                            | CLK/CLKB           | CLK/CLKB           | High Z             |

| Н  | Н       | 0                | 0                | 1                | 1                | 1                | High Z                            | CLK/CLKB           | CLK/CLKB           | CLK/CLKB           |

| Н  | Н       | 0                | 1                | 0                | 0                | 0                | CLK/CLKB                          | High Z             | High Z             | High Z             |

| Н  | Н       | 0                | 1                | 0                | 0                | 1                | CLK/CLKB                          | High Z             | High Z             | CLK/CLKB           |

| Н  | Н       | 0                | 1                | 0                | 1                | 0                | CLK/CLKB                          | High Z             | CLK/CLKB           | High Z             |

| Н  | Н       | 0                | 1                | 0                | 1                | 1                | CLK/CLKB                          | High Z             | CLK/CLKB           | CLK/CLKB           |

| Н  | Н       | 0                | 1                | 1                | 0                | 0                | CLK/CLKB                          | CLK/CLKB           | High Z             | High Z             |

| Н  | Н       | 0                | 1                | 1                | 0                | 1                | CLK/CLKB                          | CLK/CLKB           | High Z             | CLK/CLKB           |

| Н  | Н       | 0                | 1                | 1                | 1                | 0                | CLK/CLKB                          | CLK/CLKB           | CLK/CLKB           | High Z             |

| Н  | Н       | 0 <sup>[5]</sup> | 1 <sup>[5]</sup> | 1 <sup>[5]</sup> | 1 <sup>[5]</sup> | 1 <sup>[5]</sup> | CLK/CLKB                          | CLK/CLKB           | CLK/CLKB           | CLK/CLKB           |

- 4. Bypass Mode: REFCLK bypasses the PLL to the output drivers.

- 5. Default mode of operation is at power up.

#### **SMBus Protocol**

The CY24271 is a slave receiver supporting operations in the word and byte modes described in sections 5.5.4 and 5.5.5 of the SMBus Specification 2.0.

DC specifications are modified to RAMBUS standard to support 1.8, 2.5, and 3.3 volt devices. Time-out detection and packet error protocol SMBus features are not supported.

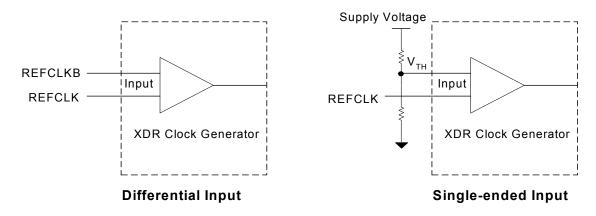

### **Input Clock Signal**

The XCG receives either a differential (REFCLK/REFCLKB) or a single-ended reference clocking input (REFCLK).

When the reference input clock is from a different clock source, it must meet the voltage levels and timing requirements listed in DC Operating Conditions on page 9 and AC Operating Conditions on page 10.

For a single-ended clock input, an external voltage divider and a supply voltage, as shown in Figure 2 on page 8, provide a reference voltage  $V_{TH}$  at the REFCLKB pin. This determines the proper trip point of REFCLK. For the range of  $V_{TH}$  specified in DC Operating Conditions on page 9, the outputs also meet the DC and AC Operating Conditions tables.

#### **SMBus Data Byte Definitions**

Three data bytes are defined for the CY24271. Byte 0 is for programming the PLL multiplier registers and clock output registers.

The definition of Byte 2 is shown in Table 4 on page 7, Table 5 on page 7, and Table 6 on page 8. The upper five bits are the revision numbers of the device and the lower three bits are the ID numbers assigned to the vendor by Rambus.

Table 4. Command Code 80h [6]

| Bit | Register | POD | Туре | Description                     |

|-----|----------|-----|------|---------------------------------|

| 7   | Reserved | 0   | RW   | Reserved (no internal function) |

| 6   | MULT2    | 0   | RW   | PLL Multiplier Select           |

| 5   | MULT1    | 0   | RW   |                                 |

| 4   | MULT0    | 1   | RW   |                                 |

| 3   | RegA     | 1   | RW   | Clock 0 Output Select           |

| 2   | RegB     | 1   | RW   | Clock 1 Output Select           |

| 1   | RegC     | 1   | RW   | Clock 2 Output Select           |

| 0   | RegD     | 1   | RW   | Clock 3 Output Select           |

Table 5. Command Code 81h [6]

| Bit | Register | POD | Туре | Description                                              |

|-----|----------|-----|------|----------------------------------------------------------|

| 7   | Reserved | 0   | RW   | Reserved (no internal function)                          |

| 6   | Reserved | 0   | RW   |                                                          |

| 5   | Reserved | 0   | RW   |                                                          |

| 4   | Reserved | 0   | RW   |                                                          |

| 3   | Reserved | 1   | RW   | Reserved (must be set to '1' for proper operation)       |

| 2   | REFSEL   | 0   | RW   | Reference Frequency Select (reference Table 1 on page 5) |

| 1   | Reserved | 0   | RW   | Reserved (must be set to '0' for proper operation)       |

| 0   | RegTest  | 0   | RW   | Reserved (must be set to '0' for proper operation)       |

#### Note

<sup>6.</sup> RW = Read and Write, RO = Read Only, POD = Power on default. See Table 1 on page 5 for PLL multipliers and Table 3 on page 6 for clock output selections.

Table 6. Command Code 82h [7]

| Bit | Register           | POD | Туре | Description                                             |

|-----|--------------------|-----|------|---------------------------------------------------------|

| 7   | Device             | ?   | RO   | Contact factory for Device Revision Number information. |

| 6   | Revision<br>Number | ?   | RO   |                                                         |

| 5   | Number             | ?   | RO   |                                                         |

| 4   |                    | ?   | RO   |                                                         |

| 3   | ?                  | ?   | RO   |                                                         |

| 2   | Vendor ID          | 0   | RO   | RAMBUS assigned Vendor ID Code                          |

| 1   |                    | 1   | RO   |                                                         |

| 0   |                    | 0   | RO   |                                                         |

Figure 2. Differential and Single-Ended Clock Inputs

Note

7. RW = Read and Write, RO = Read Only, POD = Power on default. See Table 1 on page 5 for PLL multipliers and Table 3 on page 6 for clock output selections.

# **Absolute Maximum Conditions**

| Parameter          | Description                       | Condition                   | Min  | Max                   | Unit |

|--------------------|-----------------------------------|-----------------------------|------|-----------------------|------|

| $V_{DD}$           | Clock Buffer Supply Voltage       |                             | -0.5 | 4.6                   | V    |

| $V_{DDC}$          | Core Supply Voltage               |                             | -0.5 | 4.6                   | V    |

| $V_{DDP}$          | PLL Supply Voltage                |                             | -0.5 | 4.6                   | V    |

| V <sub>IN</sub>    | Input Voltage (SCL and SDA)       | Relative to V <sub>SS</sub> | -0.5 | 4.6                   | V    |

| V <sub>IN</sub>    | Input Voltage<br>(REFCLK/REFCLKB) | Relative to V <sub>SS</sub> | -0.5 | V <sub>DD</sub> + 1.0 | V    |

|                    | Input Voltage                     | Relative to V <sub>SS</sub> | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| T <sub>S</sub>     | Temperature, Storage              | Non-functional              | -65  | 150                   | °C   |

| T <sub>A</sub>     | Temperature, Operating Ambient    | Functional                  | 0    | 70                    | °C   |

| T <sub>J</sub>     | Temperature, Junction             | Functional                  | _    | 150                   | °C   |

| ESD <sub>HBM</sub> | ESD Protection (Human Body Model) | MIL-STD-883, Method 3015    | 2000 | _                     | V    |

# **DC Operating Conditions**

| Parameter                          | Description                                             | Condition  | Min                   | Max                   | Unit |

|------------------------------------|---------------------------------------------------------|------------|-----------------------|-----------------------|------|

| $V_{\mathrm{DDP}}$                 | Supply Voltage for PLL                                  | 2.5 V ± 5% | 2.375                 | 2.625                 | V    |

| $V_{DDC}$                          | Supply Voltage for Core                                 | 2.5 V ± 5% | 2.375                 | 2.625                 | V    |

| $V_{DD}$                           | Supply Voltage for Clock Buffers                        | 2.5 V ± 5% | 2.375                 | 2.625                 | V    |

| V <sub>IHCLK</sub>                 | Input High Voltage,<br>REFCLK/REFCLKB                   |            | 0.6                   | 0.95                  | V    |

| V <sub>ILCLK</sub>                 | Input Low Voltage,<br>REFCLK/REFCLKB                    |            | -0.15                 | +0.15                 | V    |

| V <sub>IXCLK</sub> [8]             | Crossing Point Voltage,<br>REFCLK/REFCLKB               |            | 200                   | 550                   | mV   |

| ΔV <sub>IXCLK</sub> <sup>[8]</sup> | Difference in Crossing Point Voltage, REFCLK/REFCLKB    |            | -                     | 150                   | mV   |

| V <sub>IH</sub>                    | Input Signal High Voltage at ID0, ID1, EN, and /BYPASS  |            | 1.4                   | 2.625                 | V    |

| V <sub>IL</sub>                    | Input Signal Low Voltage at ID0, ID1, EN, and /BYPASS   |            | -0.15                 | 0.8                   | V    |

| V <sub>IH,SM</sub>                 | Input Signal High Voltage at SCL and SDA <sup>[9]</sup> |            | 1.4                   | 3.465                 | V    |

| $V_{IL,SM}$                        | Input Signal Low Voltage at SCL and SDA                 |            | -0.15                 | 0.8                   | V    |

| V <sub>TH</sub> <sup>[10]</sup>    | Input Threshold Voltage for single-ended REFCLK         |            | 0.35                  | 0.5 × V <sub>DD</sub> | V    |

| V <sub>IH,SE</sub>                 | Input Signal High Voltage for single-ended REFCLK       |            | V <sub>TH</sub> + 0.3 | 2.625                 | V    |

| $V_{IL,SE}$                        | Input Signal Low Voltage for single-ended REFCLK        |            | -0.15                 | V <sub>TH</sub> – 0.3 | V    |

| T <sub>A</sub>                     | Ambient Operating Temperature                           |            | 0                     | 70                    | °C   |

Not 100% tested except V<sub>IXCLK</sub> and ΔV<sub>IXCLK</sub>. Parameters guaranteed by design and characterizations, not 100% tested in production.

This range of SCL and SDA input high voltage enables the 3.3 V, 2.5 V, or 1.8 V SMBus voltages to use CY24271.

Single-ended operation guaranteed only when 0.8 < (V<sub>IH,SE</sub> – V<sub>TH</sub>)/(V<sub>TH</sub> – V<sub>IL·SE</sub>) < 1.2.</li>

# **AC Operating Conditions**

The AC operating conditions follow.

| Parameter [11]                       | Description                                                       | Condition                                                          | Min | Max                    | Unit               |

|--------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------|-----|------------------------|--------------------|

| t <sub>CYCLE,IN</sub>                | REFCLK, REFCLKB input cycle                                       | REFSEL = 0, /BYPASS = High                                         | 9   | 11                     | ns                 |

|                                      | time                                                              | REFSEL = 1, /BYPASS = High                                         | 7   | 8                      | ns                 |

|                                      |                                                                   | /BYPASS = Low                                                      | 4   | _                      | ns                 |

| t <sub>JIT,IN(cc)</sub>              | Input Cycle to Cycle Jitter <sup>[12]</sup>                       |                                                                    | _   | 185                    | ps                 |

| t <sub>DCIN</sub> <sup>[13]</sup>    | Input Duty Cycle                                                  | Over 10,000 cycles                                                 | 40% | 60%                    | t <sub>CYCLE</sub> |

| t <sub>RIN</sub> / t <sub>FIN</sub>  | Rise and Fall Times                                               | Measured at 20%–80% of input voltage for REFCLK and REFCLKB inputs | 175 | 700                    | ps                 |

| Δt <sub>RIN</sub> / t <sub>FIN</sub> | Rise and Fall Times Difference                                    |                                                                    | _   | 150                    | ps                 |

| p <sub>MIN</sub> <sup>[14]</sup>     | Modulation Index for triangular modulation                        |                                                                    | _   | 0.6                    | %                  |

|                                      | Modulation Index for non-triangular modulation                    |                                                                    | -   | -<br>185<br>60%<br>700 | %                  |

| f <sub>MIN</sub> <sup>[14]</sup>     | Input Frequency Modulation                                        |                                                                    | 30  | 33                     | kHz                |

| t <sub>SR,IN</sub>                   | Input Slew Rate (measured at 20%–80% of input voltage) for REFCLK |                                                                    | 1   | 4                      | V/ns               |

| C <sub>IN,REF</sub>                  | Capacitance at REFCLK inputs                                      |                                                                    | -   | 7                      | pF                 |

| C <sub>IN,CMOS</sub>                 | Capacitance at CMOS inputs                                        |                                                                    | -   | 10                     | pF                 |

| f <sub>SCL</sub>                     | SMBus clock frequency input in SCL pin                            |                                                                    | DC  | 100                    | kHz                |

<sup>Notes

11. Not 100% tested except V<sub>IXCLK</sub> and ΔV<sub>IXCLK</sub>. Parameters guaranteed by design and characterizations, not 100% tested in production.

12. Jitter measured at crossing points and is the absolute value of the worst case deviation.

13. Measured at crossing points.

14. If input modulation is used; input modulation is allowed but not required.

15. The amount of allowed spreading for any non-triangular modulation is determined by the induced downstream tracking skew that cannot exceed the skew generated by the specified 0.6% triangular modulation. Typically, the amount of allowed non-triangular modulation is about 0.5%.</sup>

# **DC Electrical Specifications**

| Parameter                         | Description                                                                                 | Min  | Тур | Max  | Unit |

|-----------------------------------|---------------------------------------------------------------------------------------------|------|-----|------|------|

| V <sub>OX</sub> <sup>[16]</sup>   | Differential output crossing point voltage <sup>[17]</sup>                                  | 0.9  | 1.0 | 1.1  | V    |

| V <sub>COS</sub> <sup>[16]</sup>  | Output voltage swing (peak-to-peak single-ended) <sup>[18]</sup>                            | 300  | 325 | 350  | mV   |

| V <sub>OL,ABS</sub>               | Absolute output low voltage at CLK[3:0], CLK[3:0]B <sup>[19]</sup>                          | 0.85 | -   | -    | V    |

| V <sub>ISET</sub>                 | Reference voltage for swing controlled current, I <sub>REF</sub>                            | 0.98 | 1.0 | 1.02 | V    |

| I <sub>DD</sub> <sup>[16]</sup>   | Power Supply Current at 2.625 V, f <sub>ref</sub> = 100 MHz, and f <sub>out</sub> = 300 MHz | -    | -   | 85   | mA   |

| I <sub>DD</sub> <sup>[16]</sup>   | Power Supply Current at 2.625 V, f <sub>ref</sub> = 133 MHz, and f <sub>out</sub> = 667 MHz | -    | -   | 125  | mA   |

| I <sub>DD</sub> <sup>[16]</sup>   | Power Supply Current at 2.625 V, f <sub>ref</sub> = 133 MHz, and f <sub>out</sub> = 800 MHz | -    | -   | 130  | mA   |

| I <sub>OL</sub> /I <sub>REF</sub> | Ratio of output low current to reference current <sup>[20]</sup>                            | 6.8  | 7.0 | 7.2  |      |

| I <sub>OL,ABS</sub>               | Minimum current at V <sub>OL,ABS</sub> <sup>[21]</sup>                                      | 45   | -   | -    | mA   |

| V <sub>OL,SDA</sub>               | SDA output low voltage at test condition of SDA output low current = 4 mA                   | _    | _   | 0.4  | V    |

| I <sub>OL,SDA</sub>               | SDA output low voltage at test condition of SDA voltage = 0.8 V                             | 6    | -   | _    | mA   |

| I <sub>OZ</sub>                   | Current during High Z per pin at CLK[3:0], CLK[3:0]B                                        | -    | -   | 10   | μА   |

| Z <sub>OUT</sub>                  | Output dynamic impedance when clock output signal is at $V_{OL} = 0.9 \text{ V}^{[22]}$     |      | _   | _    | Ω    |

Notes

16. Not 100% tested except V<sub>IXCLK</sub> and ΔV<sub>IXCLK</sub>. Parameters guaranteed by design and characterizations, not 100% tested in production.

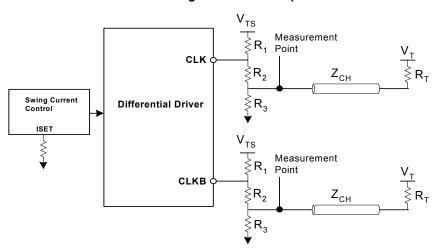

17. V<sub>OX</sub> is measured on external divider network.

18. V<sub>COS</sub> = (clock output high voltage – clock output low voltage), measured on the external divider network.

19. V<sub>OL\_ABS</sub> is measured at the clock output pins of the package.

20. I<sub>REF</sub> is equal to V<sub>ISET</sub>/R<sub>RC</sub>.

21. Minimum I<sub>OL,ABS</sub> is measured at the clock output pin with R<sub>RC</sub> = 148 ohms or less.

22. Z<sub>OUT</sub> is defined at the output pins as (0.94 V – 0.90 V)/(I<sub>0.94</sub> – I<sub>0.90</sub>) under conditions specified for I<sub>OL,ABS</sub>.

# **AC Electrical Specification**

The AC Electrical specifications follow.

| Parameter [23]                                                                                                                                                                                                                                                                   | Description                                                                                                                                              | Min  | Тур  | Max  | Unit               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------------------|

| t <sub>CYCLE</sub>                                                                                                                                                                                                                                                               | Clock Cycle time <sup>[24]</sup>                                                                                                                         | 1.25 | _    | 3.34 | ns                 |

| t <sub>JIT(cc)</sub>                                                                                                                                                                                                                                                             | Jitter over 1-6 clock cycles at 400–635 MHz <sup>[25]</sup>                                                                                              | -    | 25   | 40   | ps                 |

|                                                                                                                                                                                                                                                                                  | Jitter over 1-6 clock cycles at 638–800 MHz                                                                                                              | -    | 25   | 30   | ps                 |

| Phase noise SSB spectral purity L(f) at 20 MHz offset: $400-500$ MHz (In addition, device must not exceed L(f) = $10\log[1+(50x10^6/f)^{2.4}] - 138$ for f = 1 MHz to $100$ MHz except for the region near f = REFCLK/Q where Q is the value of the internal reference divider.) |                                                                                                                                                          | -    | -135 | -128 | dBC/Hz             |

|                                                                                                                                                                                                                                                                                  | 533 MHz and faster output                                                                                                                                | -    | _    | TBD  |                    |

| t <sub>JIT(hper,cc)</sub>                                                                                                                                                                                                                                                        | Cycle-to-cycle duty cycle error at 400–635 MHz                                                                                                           | -    | 25   | 40   | ps                 |

|                                                                                                                                                                                                                                                                                  | Cycle-to-cycle duty cycle error at 636–800 MHz                                                                                                           |      | 25   | 30   | ps                 |

| Δt <sub>SKEW</sub>                                                                                                                                                                                                                                                               | Drift in t <sub>SKEW</sub> when ambient temperature varies between 0 °C and 70 °C and supply voltage varies between 2.375 V and 2.625 V. <sup>[26]</sup> |      | _    | 15   | ps                 |

| DC                                                                                                                                                                                                                                                                               | Long term average output duty cycle                                                                                                                      | 45%  | 50   | 55%  | t <sub>CYCLE</sub> |

| t <sub>EER,SCC</sub>                                                                                                                                                                                                                                                             | PLL output phase error when tracking SSC                                                                                                                 | -100 | _    | 100  | ps                 |

| t <sub>CR</sub> ,t <sub>CF</sub>                                                                                                                                                                                                                                                 | Output rise and fall times at 400–800 MHz (measured at 20%–80% of output voltage)                                                                        |      | _    | 300  | ps                 |

| t <sub>CR,CF</sub>                                                                                                                                                                                                                                                               | Difference between output rise and fall times on the same pin of the single device (20%–80%) of 400–800 MHz <sup>[27]</sup>                              |      | _    | 100  | ps                 |

<sup>23.</sup> Not 100% tested except V<sub>IXCLK</sub> and ΔV<sub>IXCLK</sub>. Parameters guaranteed by design and characterizations, not 100% tested in production.

24. Max and min output clock cycle times are based on nominal outputs frequency of 300 and 800 MHz, respectively. For spread spectrum modulated differential or single-ended REFCLK, the output clock tracks the modulation of the input.

<sup>25.</sup> Output short term jitter spec is the absolute value of the worst case deviation.

<sup>26.</sup> t<sub>SKEW</sub> is the timing difference between any two of the four differential clocks and is measured at common mode voltage. Δt<sub>SKEW</sub> is the change in t<sub>SKEW</sub> when the operating temperature and supply voltage change.

<sup>27.</sup> t<sub>CR,CF</sub> applies only when appropriate R<sub>RC</sub> and output resistor network resistor values are selected to match pull up and pull down currents.

#### **Test and Measurement Setup**

Figure 3. Clock Outputs

Table 7. Example External Resistor Values and Termination Voltages for a 50  $\Omega$  Channel

| Parameter       | Value | Unit |

|-----------------|-------|------|

| R <sub>1</sub>  | 39.2  | Ω    |

| R <sub>2</sub>  | 66.5  | Ω    |

| R <sub>3</sub>  | 93.1  | Ω    |

| R <sub>T</sub>  | 49.9  | Ω    |

| R <sub>RC</sub> | 200   | Ω    |

| V <sub>TS</sub> | 2.5V  | V    |

| V <sub>T</sub>  | 1.2V  | V    |

## **Signal Waveforms**

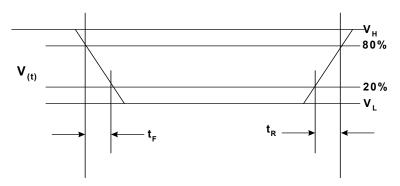

A physical signal that appears at the pins of a device is deemed valid or invalid depending on its voltage and timing relations with other signals. Input and output voltage waveforms are defined as shown in Figure 4. Both rise and fall times are defined between

the 20% and 80% points of the voltage swing, with the swing defined as  $V_H\!-\!V_L.$

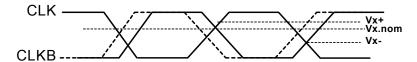

Figure 5 shows the definition of the output crossing point. The nominal crossing point between the complementary outputs is defined as the 50% point of the DC voltage levels. There are two crossing points defined: Vx+ at the rising edge of CLK and Vx– at the falling edge of CLK. For some waveforms, both Vx+ and Vx– are below Vx,nom (for example, if  $t_{CR}$  is larger than  $t_{CF}$ ).

#### **Jitter**

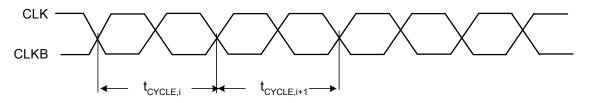

This section defines the specifications that relate to timing uncertainty (or jitter) of the input and output waveforms. Figure 6 on page 14 shows the definition of cycle-to-cycle jitter with respect to the falling edge of the CLK signal. Cycle-to-cycle jitter is the difference between cycle times of adjacent cycles. Equal requirements apply rising edges of the CLK signal. Figure 7 on page 14 shows the definition of cycle-to-cycle duty cycle error ( $t_{DC,ERR}$ ). Cycle-to-cycle duty cycle is defined as the difference between  $t_{PW+}$  (high times) of adjacent differential clock cycles. Equal requirements apply to  $t_{PW-}$ , low times of the differential click cycles.

Figure 4. Input and Output Waveforms

Figure 5. Crossing Point Voltage

Figure 6. Cycle-to-cycle Jitter

$t_{J} = t_{CYCLE,i} - t_{CYCLE,i+1 \text{ over } 10,000 \text{ consecutive cycles}}$

Figure 7. Cycle-to-cycle Duty-cycle Error

$$t_{DC,ERR} = t_{PW}(i) - t_{PW}(i+1)$$

and  $t_{PW}(i+1) - t_{PW}(i+1)$

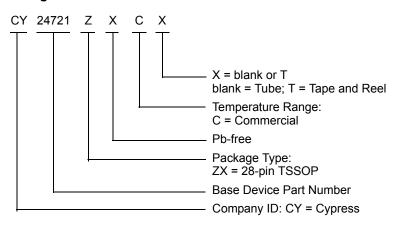

# **Ordering Information**

| Part Number | Package Type                 | Product Flow              |

|-------------|------------------------------|---------------------------|

| Pb-free     |                              |                           |

| CY24271ZXC  | 28-pin TSSOP                 | Commercial, 0 °C to 70 °C |

| CY24271ZXCT | 28-pin TSSOP – Tape and Reel | Commercial, 0 °C to 70 °C |

# **Ordering Code Definitions**

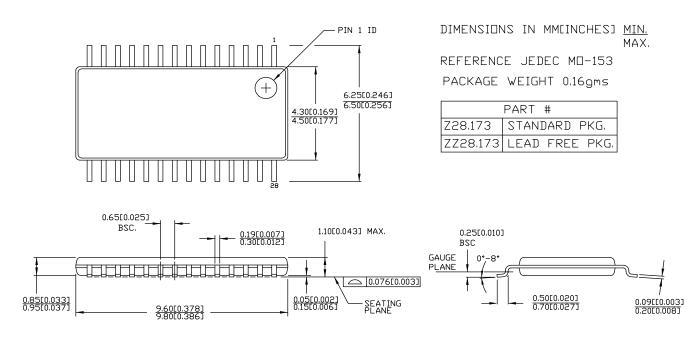

# **Package Drawing and Dimension**

Figure 8. 28-pin TSSOP (4.40 mm Body) Package Outline, 51-85120

51-85120 \*D

# Acronyms

| Acronym | Description                             |

|---------|-----------------------------------------|

| CMOS    | Complementary Metal Oxide Semiconductor |

| ESD     | Electrostatic Discharge                 |

| PLL     | Phase Locked Loop                       |

| TSSOP   | Thin Shrunk Small Outline Package       |

| XDR     | Extended Data Rate                      |

# **Document Conventions**

#### **Units of Measure**

| Symbol | Unit of Measure |

|--------|-----------------|

| °C     | degree Celsius  |

| Hz     | hertz           |

| kHz    | kilohertz       |

| MHz    | megahertz       |

| μΑ     | microampere     |

| mA     | milliampere     |

| ms     | millisecond     |

| mV     | millivolt       |

| ns     | nanosecond      |

| Ω      | ohm             |

| %      | percent         |

| pF     | picofarad       |

| ps     | picosecond      |

| V      | volt            |

# **Document History Page**

| Rev. | ECN No. | Issue Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|---------|------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 378263  | See ECN    | RGL                | New data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| *A   | 492065  | See ECN    | KKVTMP             | 1) New Pin definition table 2) Throughout the data sheet Change all instances of VSSC from VSSC to VSS Change all instances of VSSB from VSSB to VSSC Change all instances of SCLK from SCLK to SCL Change all instances of SDATA from SDATA to SDA Change all instances of BYPASSB from BYPASSB to /BYPASS Change all instances of VDDO from VDDO to VDD Change all instances of VSSO from VSSO to VSS Change all instances of VSSG from VSSG to VSS |

| *B   | 1333483 | See ECN    | FGA / SFV          | Added IDD values in DC Electrical Specifications table                                                                                                                                                                                                                                                                                                                                                                                                |

| *C   | 3162845 | 02/04/2011 | BASH               | Added Ordering Code Definitions under Ordering Information. Updated Package Drawing and Dimension. Added Acronyms and Units of Measure. Updated in new template.                                                                                                                                                                                                                                                                                      |

| *D   | 4292206 | 02/26/2014 | CINM               | Updated Package Drawing and Dimension: spec 51-85120 – Changed revision from *B to *C. Updated in new template. Completing Sunset Review.                                                                                                                                                                                                                                                                                                             |

| *E   | 4581659 | 11/27/2014 | AJU                | Added related documentation hyperlink in page 1. Updated package diagram.                                                                                                                                                                                                                                                                                                                                                                             |

### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

Automotive Clocks & Buffers Interface

Lighting & Power Control

Memory

PSoC

Touch Sensing

USB Controllers

Wireless/RF

cypress.com/go/automotive cypress.com/go/clocks cypress.com/go/interface cypress.com/go/powerpsoc cypress.com/go/plc cypress.com/go/memory cypress.com/go/psoc cypress.com/go/touch cypress.com/go/USB cypress.com/go/wireless

# PSoC® Solutions

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

#### **Technical Support**

cypress.com/go/support

© Cypress Semiconductor Corporation, 2005-2014. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 001-00411 Rev. \*E

Revised December 1, 2014

# AMEYA360 Components Supply Platform

# **Authorized Distribution Brand:**

# Website:

Welcome to visit www.ameya360.com

# Contact Us:

# > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

# > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

# Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com