#### **General Description**

The MAX6892/MAX6893/MAX6894 pin-selectable, multivoltage supply sequencers/supervisors monitor several voltage-detector inputs and one watchdog input, asserting the respective voltage detector or watchdog output when the inputs drop below the configured voltage thresholds or the watchdog timer expires. The MAX6892 features eight voltage detector inputs and 10 outputs. The MAX6893 features six voltage-detector inputs and eight outputs, while the MAX6894 features four voltage detector inputs and six outputs. A RESET output ensures all monitored inputs are above the set thresholds. The voltage detector outputs are configured as open drain. Manual reset and margin disable inputs offer additional flexibility.

The thresholds of the MAX6892/MAX6893/MAX6894 are selected through five logic inputs (TH0-TH4). The logic on these five inputs selects the supply voltage tolerance (5% or 10%) and one of 32 factory-set thresholds settings. Watchdog and reset timeout periods can use factory default settings or are independently adjustable by connecting external capacitors.

When any of the monitored voltages falls below its threshold, the respective output asserts and remains asserted for 6.25ms (typ) after the monitored voltage exceeds the threshold. The outputs can be connected to the shutdown or enable inputs of DC-DC regulators to provide turn-on power sequencing to ensure proper system initialization.

The MAX6892 is available in a 5mm x 5mm x 0.8mm. 32-pin, Thin QFN package, while the MAX6893/ MAX6894 are available in a 5mm x 5mm x 0.8mm, 28pin, Thin QFN package. The MAX6892/MAX6893/ MAX6894 are specified to operate over the extended temperature range (-40°C to +85°C).

### **Applications**

Telecommunication/Central Office Systems

**Networking Systems**

Servers/Workstations

**Base Stations**

Storage Equipment

Multimicroprocessor/Voltage Systems

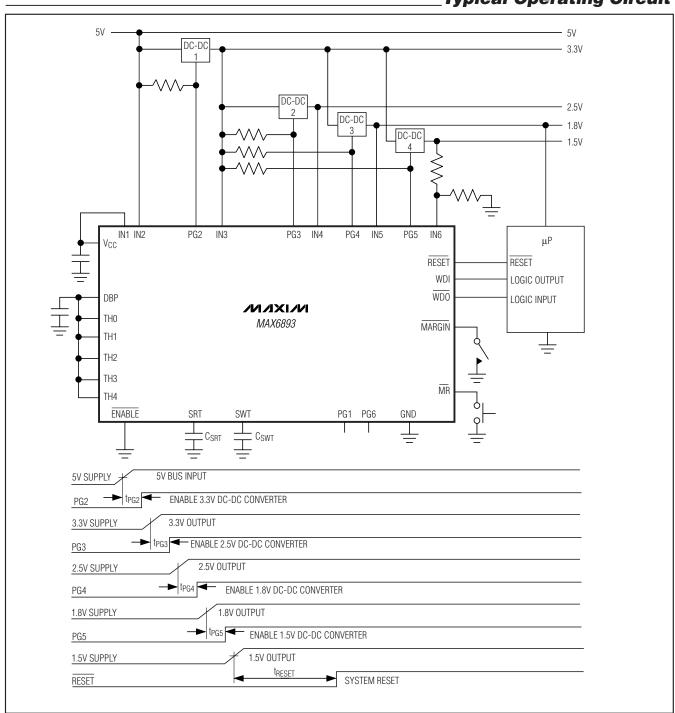

Typical Operating Circuit appears at end of data sheet.

#### **Features**

- Pin-Selectable or User-Adjustable Voltage **Detector Thresholds**

- **♦ Dedicated RESET and WDO Outputs**

- Capacitor-Adjustable Reset and Watchdog **Timeout Periods**

- ◆ Factory-Default Reset and Watchdog Timeout **Periods**

- ♦ Up to Eight Independent, Open-Drain Power-Good Outputs

- **♦** Enable Margining Disable and Manual Reset Controls

- ◆ -40°C to +85°C Operating Temperature Range

- ♦ Small 5mm x 5mm Thin QFN Package

- **♦ Few External Components**

- **♦** ±1% Threshold Accuracy

#### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE     |

|------------|----------------|-----------------|

| MAX6892ETJ | -40°C to +85°C | 32 Thin QFN-EP* |

| MAX6893ETI | -40°C to +85°C | 28 Thin QFN-EP* |

| MAX6894ETI | -40°C to +85°C | 28 Thin QFN-EP* |

Note: Devices are also available in a lead(Pb)-free/RoHS-compliant package. Specify lead-free by adding a plus (+) to the part number when ordering.

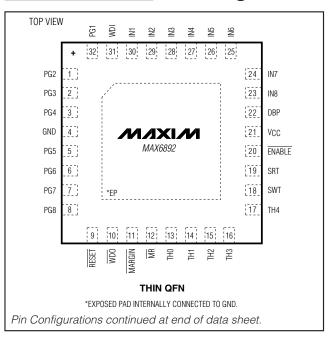

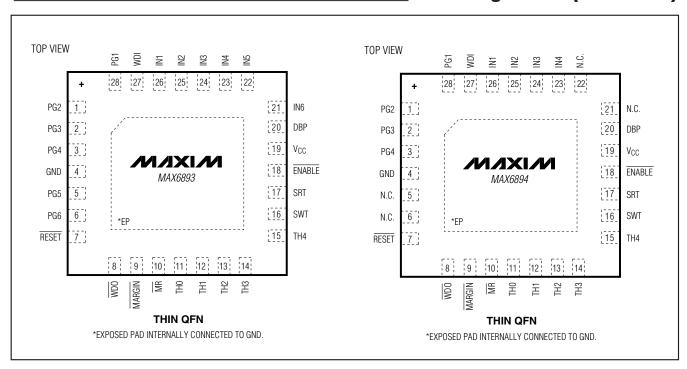

### **Pin Configurations**

<sup>\*</sup>EP = Exposed pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.)                     | 32-Pin Thin QFN (derate 21.3mW/°C        |

|-------------------------------------------------------|------------------------------------------|

| PG_, RESET, WDO0.3V to +14V                           | above +70°C)1702mW                       |

| IN1-IN8, TH0-TH4, ENABLE, WDI, MR, MARGIN,            | Maximum Junction Temperature+150°C       |

| SRT, SWT, V <sub>CC</sub> 0.3V to +6V                 | Operating Temperature Range40°C to +85°C |

| DBP0.3V to +3V                                        | Storage Temperature Range65°C to +150°C  |

| Input/Output Current (all pins)±20mA                  | Lead Temperature (soldering, 10s)+300°C  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) | Soldering Temperature (reflow)           |

| 28-Pin Thin QFN (derate 21.3mW/°C                     | Lead(Pb)-Free+260°C                      |

| above +70°C)1702mW                                    | Containing Lead (Pb)+240°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN1} = V_{IN6} - V_{IN8} = V_{GND}, V_{IN2} - V_{IN5} = 2.7V \text{ to } 5.5V, WDI = \overline{ENABLE} = GND, TH0-TH4 = \overline{MARGIN} = \overline{MR} = DBP, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Notes 1, 2)

| PARAMETER                        | SYMBOL                | CONDITIONS                          |                                                                                                         | MIN   | TYP  | MAX   | UNITS             |

|----------------------------------|-----------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------|-------|------|-------|-------------------|

| Operating Voltage Range (Note 3) |                       | 9                                   | ner one of IN2-IN5 or V <sub>CC</sub> that e part is fully operational                                  | 2.7   |      | 5.5   | V                 |

| Undervoltage Lockout             | V <sub>UVLO</sub>     | ,                                   | -V <sub>IN5</sub> or V <sub>CC</sub> ) < V <sub>UVLO</sub> ,<br>d down to GND with a 10μA               |       |      | 2.5   | V                 |

| Digital Bypass Voltage           | V <sub>DBP</sub>      | No load                             |                                                                                                         | 2.48  | 2.55 | 2.67  | V                 |

| Supply Current                   | Icc                   | $V_{IN2} = 5.5V, V$ load            | $I_{IN1}$ , $V_{IN3}$ – $V_{IN8}$ = $V_{GND}$ , no                                                      |       | 0.9  | 1.1   | mA                |

| Threehold Accuracy (Table 0)     | \                     | IN1-IN8,                            | $T_A = +25^{\circ}C \text{ to } +85^{\circ}C$                                                           | -1    |      | +1    | 0/ \/             |

| Threshold Accuracy (Table 2)     | V <sub>TH</sub>       | IN_ falling                         | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                                           | -2    |      | +2    | % V <sub>TH</sub> |

| Threshold Hysteresis             | V <sub>TH-H</sub> YS  |                                     | •                                                                                                       |       | 0.3  |       | % V <sub>TH</sub> |

| Threshold Tempco                 | ΔV <sub>TH</sub> /°C  |                                     |                                                                                                         |       | 10   |       | ppm/°C            |

|                                  |                       | IN1, IN6-IN8                        |                                                                                                         | 50    |      | 50    |                   |

| Input Leakage Current            | IIN                   | IN2-IN5 set as                      | s adjustable thresholds                                                                                 | -50   |      | +50   | nA                |

| IN2-IN5 Input Impedance          | R <sub>IN2</sub> -IN5 | _                                   | For IN_ voltages < the highest IN_ supply or < V <sub>CC</sub> and thresholds are not set as adjustable |       | 400  | 555   | kΩ                |

| Power-Up Delay                   | t <sub>D-PO</sub>     | V <sub>CC</sub> ≥ V <sub>UVLO</sub> | V <sub>CC</sub> ≥ V <sub>UV</sub> LO                                                                    |       |      | 3     | ms                |

| IN_ to PG_ Delay                 | t <sub>D-R</sub>      | IN_ falling/rising, 100mV overdrive |                                                                                                         |       | 25   |       | μs                |

| PG_ Timeout Period               | tpg                   |                                     |                                                                                                         | 5.625 | 6.25 | 6.875 | ms                |

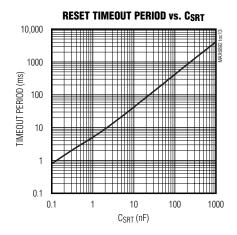

| RESET Default Timeout Period     | t <sub>RP</sub>       | VSRT = VCC                          |                                                                                                         | 180   | 200  | 220   | ms                |

| RESET Adjustable Timeout Period  | t <sub>RP-ADJ</sub>   | C <sub>SRT</sub> = 47nF             |                                                                                                         | 135   | 207  | 280   | ms                |

| SRT Adjustable Timeout Current   | ISRT                  | V <sub>SRT</sub> = V <sub>GND</sub> |                                                                                                         | 180   | 230  | 280   | nA                |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN6} - V_{IN8} = V_{GND}, V_{IN2} - V_{IN5} = 2.7V \text{ to } 5.5V, WDI = \overline{ENABLE} = GND, TH0-TH4 = \overline{MARGIN} = \overline{MR} = DBP, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Notes 1, 2)

| PARAMETER                                              | SYMBOL               | CONDITIONS                                                                                           | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------|------|------|------|-------|

| SRT Default Timeout Threshold                          | VSRT-DEF             | V <sub>SRT</sub> ≥ V <sub>SRT-DEF</sub> , selects reset default timeout                              | 1.1  | 1.25 | 1.5  | V     |

| SRT Adjustable Timeout<br>Threshold                    | VSRT-ADJ             | (Note 4)                                                                                             | 0.95 | 1.0  | 1.05 | V     |

| SRT Adjustable Timeout<br>Discharge Threshold          | V <sub>SRT-DIS</sub> | (Note 5)                                                                                             |      | 100  |      | mV    |

| SRT Adjustable Timeout Output<br>Low Discharge Current | I <sub>SRT-DIS</sub> | V <sub>SRT</sub> = 0.3V                                                                              | 0.7  |      |      | mA    |

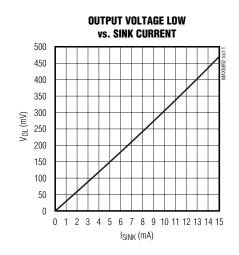

| PG_, RESET, WDO Output Low                             | V <sub>OL</sub>      | I <sub>SINK</sub> = 4mA, output asserted                                                             |      |      | 0.4  | V     |

| PG_, RESET, WDO Output Initial Pulldown Current        | lυγ                  | V <sub>CC</sub> ≤ V <sub>UV</sub> LO, V <sub>PG</sub> , V <del>RESET</del> , V <del>WDO</del> = 0.8V |      | 10   | 40   | μΑ    |

| PG_, RESET, WDO Output Open-<br>Drain Leakage Current  | I <sub>LKG</sub>     | Output high impedance                                                                                | -1   |      | +1   | μΑ    |

| MR, MARGIN, ENABLE,                                    | VIL                  |                                                                                                      |      |      | 0.6  | V     |

| TH0-TH4, WDI Input Voltage                             | VIH                  |                                                                                                      | 1.4  |      |      | V     |

| MR Input Pulse Width                                   | TMR                  |                                                                                                      | 1    |      |      | μs    |

| MR Glitch Rejection                                    |                      |                                                                                                      |      | 100  |      | ns    |

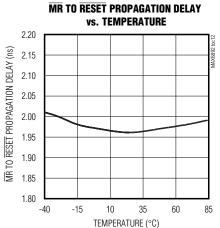

| MR to RESET Delay                                      | t <sub>D-MR</sub>    |                                                                                                      |      | 2    |      | μs    |

| MR to DBP Pullup Current                               | IMR                  | V <u>MR</u> = 1.4V                                                                                   | 5    | 10   | 15   | μΑ    |

| MARGIN to DBP Pullup Current                           | IMARGIN              | V <sub>MARGIN</sub> = 1.4V                                                                           | 5    | 10   | 15   | μΑ    |

| ENABLE to PG_ Delay                                    | tD-ENPG              |                                                                                                      |      | 200  |      | ns    |

| ENABLE Pulldown Current                                |                      | VENABLE = 0.6V                                                                                       | 5    | 10   | 15   | μΑ    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN6} - V_{IN8} = V_{GND}, V_{IN2} - V_{IN5} = 2.7V \text{ to } 5.5V, WDI = \overline{ENABLE} = GND, TH0-TH4 = \overline{MARGIN} = \overline{MR} = DBP, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Notes 1, 2)

| PARAMETER                                              | SYMBOL               | CONDITIONS                                                    |                          | MIN   | TYP   | MAX    | UNITS |

|--------------------------------------------------------|----------------------|---------------------------------------------------------------|--------------------------|-------|-------|--------|-------|

| TH0-TH4 Input Current                                  |                      |                                                               |                          | -1    |       | +1     | μΑ    |

| WDI Pulldown Current                                   | I <sub>WDI</sub>     | $V_{WDI} = 0.6V$                                              |                          | 5     | 10    | 15     | μΑ    |

| WDI Input Pulse Width                                  |                      |                                                               |                          | 50    |       |        | ns    |

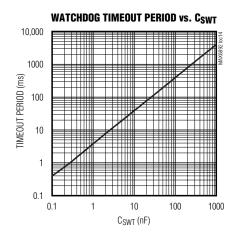

| Watahdag Dafault Timaaut Bariad                        | +                    | \/ou\/o_o                                                     | Initial mode             | 92.16 | 102.4 | 112.64 |       |

| Watchdog Default Timeout Period                        | tw□                  | V <sub>SWT</sub> = V <sub>CC</sub>                            | Normal mode              | 1.44  | 1.6   | 1.76   | S     |

| Watchdog Adjustable Timeout                            |                      | 0 000 5                                                       | Initial mode             | 53.7  | 82.5  | 111.9  |       |

| Period                                                 | twd-adj              | C <sub>SWT</sub> = 0.33µF                                     | Normal mode              | 0.93  | 1.43  | 1.94   | S     |

| SWT Adjustable Timeout Current                         | Iswr                 | V <sub>SWT</sub> = V <sub>GND</sub>                           |                          | 180   | 230   | 280    | nA    |

| SWT Default Timeout Threshold                          | V <sub>SWT-DEF</sub> | V <sub>SWT</sub> ≥ V <sub>SWT-DEF</sub> , s<br>timeout period | selects watchdog default | 1.1   | 1.25  | 1.5    | V     |

| SWT Adjustable Timeout<br>Threshold                    | Vswt-adj             | (Note 4)                                                      |                          | 0.95  | 1.0   | 1.05   | V     |

| SWT Adjustable Timeout<br>Discharge Threshold          | VswT-DIS             | (Note 5)                                                      |                          |       | 100   |        | mV    |

| SWT Adjustable Timeout Output<br>Low Discharge Current | IswT-DIS             | V <sub>SWT</sub> = 0.3V                                       |                          | 0.7   |       |        | mA    |

Note 1: 100% production tested at  $T_A = +25$ °C and  $T_A = +85$ °C. Specifications at  $T_A = -40$ °C are guaranteed by design.

**Note 2:** Device may be supplied from any one of IN2–IN5, or V<sub>CC</sub>.

Note 3: The internal supply voltage, measured at V<sub>CC</sub>, equals the maximum of IN2–IN5.

Note 4: External capacitor is charged by Is T when Vs T-DIS < Vs T < Vs T-ADJ.

Note 5: External capacitor is discharged by Is\_T-DIS down to Vs\_T-DIS after Vs\_T reaches Vs\_T-ADJ.

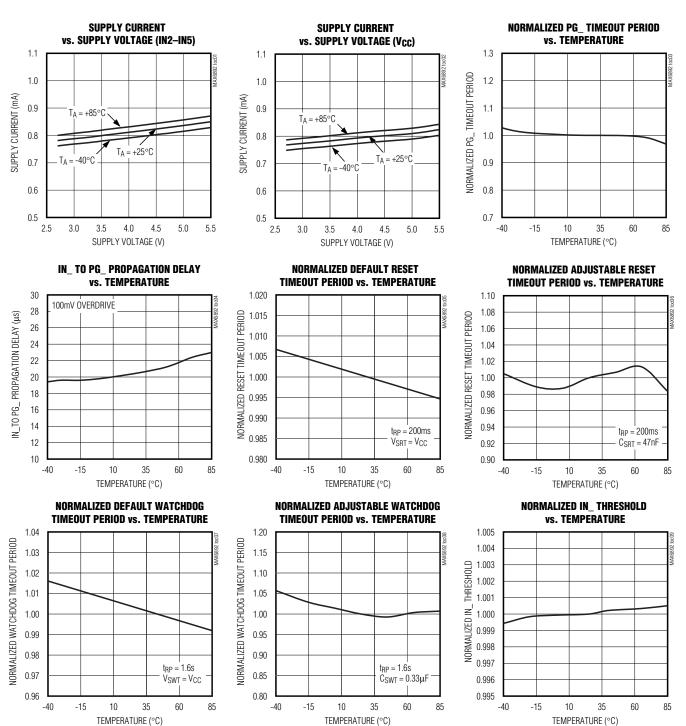

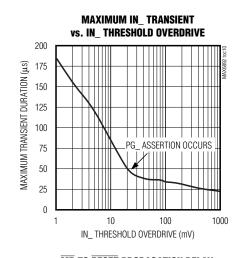

### Typical Operating Characteristics

$(V_{IN1} = V_{IN6} - V_{IN8} = V_{GND}, V_{IN2} - V_{IN5} = 2.7V \text{ to } 5.5V, V_{WDI} = V_{GND}, V_{TH0} - V_{TH4} = V_{\overline{MARGIN}} = V_{\overline{MR}} = V_{DBP}$ . Typical values are at  $T_A = +25^{\circ}C$ .)

### Typical Operating Characteristics (continued)

$(V_{IN1} = V_{IN6} - V_{IN8} = V_{GND}, V_{IN2} - V_{IN5} = 2.7V \text{ to } 5.5V, V_{WDI} = V_{GND}, V_{TH0} - V_{TH4} = V_{\overline{MARGIN}} = V_{\overline{MR}} = V_{DBP}$ . Typical values are at  $T_A = +25^{\circ}C$ .)

### **Pin Description**

| PIN     |         |         |        | ELINCTION                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|---------|---------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MAX6892 | MAX6893 | MAX6894 | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 1       | 1       | 1       | PG2    | Open-Drain, Power-Good Output 2. PG2 asserts low when the voltage input at IN2 is below the pin-selectable/adjustable input threshold or ENABLE is pulled high. PG2 deasserts with a factory preset timeout period of 6.25ms.                                                                                                                                                                |  |  |  |  |

| 2       | 2       | 2       | PG3    | Open-Drain, Power-Good Output 3. PG3 asserts low when the voltage input at IN3 is below the pin-selectable/adjustable input threshold or ENABLE is pulled high. PG3 deasserts with a factory preset timeout period of 6.25ms.                                                                                                                                                                |  |  |  |  |

| 3       | 3       | 3       | PG4    | Open-Drain, Power-Good Output 4. PG4 asserts low when the voltage input at IN4 is below the pin-selectable/adjustable input threshold or ENABLE is pulled high. PG4 deasserts with a factory preset timeout period of 6.25ms.                                                                                                                                                                |  |  |  |  |

| 4       | 4       | 4       | GND    | Ground                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 5       | 5       | _       | PG5    | Open-Drain, Power-Good Output 5. PG5 asserts low when the voltage input at IN5 is below the pin-selectable/adjustable input threshold or ENABLE is pulled high. PG5 deasserts with a factory preset timeout period of 6.25ms.                                                                                                                                                                |  |  |  |  |

| 6       | 6       | _       | PG6    | Open-Drain, Power-Good Output 6. PG6 asserts low when the voltage input at IN6 is below the pin-selectable/adjustable input threshold or ENABLE is pulled high. PG6 deasserts with a factory preset timeout period of 6.25ms.                                                                                                                                                                |  |  |  |  |

| 7       | _       | _       | PG7    | Open-Drain, Power-Good Output 7. PG7 asserts low when the voltage input at IN7 is below the pin-selectable/adjustable input threshold or ENABLE is pulled high. PG7 deasserts with a factory preset timeout period of 6.25ms.                                                                                                                                                                |  |  |  |  |

| 8       | _       | _       | PG8    | Open-Drain, Power-Good Output 8. PG8 asserts low when the voltage input at IN8 is below the pin-selectable/adjustable input threshold or ENABLE is pulled high. PG8 deasserts with a factory preset timeout period of 6.25ms.                                                                                                                                                                |  |  |  |  |

| 9       | 7       | 7       | RESET  | Open-Drain, Active-Low Reset Output Stage. RESET asserts low when any monitored input (IN_) is below the selected threshold or manual reset (MR) is pulled low. RESET remains low for the reset timeout period after all resetcausing conditions are cleared, and then deasserts.                                                                                                            |  |  |  |  |

| 10      | 8       | 8       | WDO    | Open-Drain, Active-Low Watchdog Output Stage. If WDI remains high or low for longer than the watchdog timeout period, the internal watchdog timer runs out and the WDO output asserts low. The internal watchdog timer clears whenever RESET is asserted or WDI sees a rising or falling edge. Connect WDO to MR to automatically assert the RESET output after each watchdog timeout fault. |  |  |  |  |

| 11      | 9       | 9       | MARGIN | Margin Input. MARGIN holds PG_, RESET, and WDO in their existing states when driven low. Leave MARGIN unconnected or connect to DBP if unused. MARGIN overrides MR if both assert at the same time. MARGIN is internally pulled up to DBP through a 10µA current source.                                                                                                                     |  |  |  |  |

| 12      | 10      | 10      | MR     | Active-Low Manual Reset Input. Pull $\overline{\text{MR}}$ low to assert $\overline{\text{RESET}}$ . $\overline{\text{RESET}}$ remains asserted for its preset/adjustable reset timeout period when $\overline{\text{MR}}$ is driven/pulled high. $\overline{\text{MR}}$ is internally pulled up to DBP through a 10µA current source.                                                       |  |  |  |  |

| 13      | 11      | 11      | THO    | Threshold Selection Input 0. Logic input to select desired thresholds. Connect TH0 to GND or DBP. See Table 2 for available thresholds. Input has no internal pullup or pulldown.                                                                                                                                                                                                            |  |  |  |  |

### **Pin Description (continued)**

| PIN     |         |         |        |                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|---------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX6892 | MAX6893 | MAX6894 | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14      | 12      | 12      | TH1    | Threshold Selection Input 1. Logic input to select desired thresholds. Connect TH1 to GND or DBP. See Table 2 for available thresholds. Input has no internal pullup or pulldown.                                                                                                                                                                                                                            |

| 15      | 13      | 13      | TH2    | Threshold Selection Input 2. Logic input to select desired thresholds. Connect TH2 to GND or DBP. See Table 2 for available thresholds. Input has no internal pullup or pulldown.                                                                                                                                                                                                                            |

| 16      | 14      | 14      | TH3    | Threshold Selection Input 3. Logic input to select desired thresholds. Connect TH3 to GND or DBP. See Table 2 for available thresholds. Input has no internal pullup or pulldown.                                                                                                                                                                                                                            |

| 17      | 15      | 15      | TH4    | Threshold Selection Input 4. Logic input to select desired thresholds. Connect TH4 to GND or DBP. See Table 2 for available thresholds. Input has no internal pullup or pulldown.                                                                                                                                                                                                                            |

| 18      | 16      | 16      | SWT    | Watchdog Timeout Adjust Input. Connect SWT to $V_{CC}$ to select the default watchdog timeout period. Connect an external capacitor between SWT and GND to adjust the watchdog timeout period. The adjustable timeout period is calculated by $t_{WP} = 4.348E6 \times C_{SWT}$ ( $t_{WP}$ in seconds and $C_{SWT}$ in Farads). Disable the watchdog timer by connecting SWT to GND.                         |

| 19      | 17      | 17      | SRT    | Reset Timeout Adjust Input. Connect SRT to $V_{CC}$ to select the default reset timeout period. Connect an external capacitor between SRT and GND to adjust the reset timeout period. The adjustable timeout period is calculated by $t_{RP} = 4.348E6 \times C_{SWT}$ ( $t_{RP}$ in seconds and $C_{SRT}$ in Farads).                                                                                       |

| 20      | 18      | 18      | ENABLE | Active-Low, PG_ Enable Input. Pull ENABLE high to force all PG_ outputs low. PG_ outputs remain asserted for their timeout period when ENABLE is driven/pulled low. ENABLE is internally pulled down to GND through a 10µA current sink.                                                                                                                                                                     |

| 21      | 19      | 19      | Vcc    | Internal Supply Voltage. Bypass $V_{CC}$ to GND with a 1 $\mu$ F capacitor as close to the device as possible. $V_{CC}$ supplies power to the internal circuitry. $V_{CC}$ is internally powered from the highest of the monitored IN2–IN5 voltages. Do not use $V_{CC}$ to supply power to external circuitry. To externally supply $V_{CC}$ , see the <i>Powering the MAX6892/MAX6893/MAX6894</i> section. |

| 22      | 20      | 20      | DBP    | Digital Bypass Voltage. DBP supplies power to the output stages. Bypass DBP to GND with a 1µF capacitor as close to the device as possible. Do not use DBP to supply power to external circuitry.                                                                                                                                                                                                            |

| 23      | _       | _       | IN8    | Input Voltage 8. Select undervoltage threshold using TH0-TH4. See Table 2. For improved noise immunity, bypass IN8 to GND with a 0.1µF capacitor as close to the device as possible.                                                                                                                                                                                                                         |

| 24      | _       | _       | IN7    | Input Voltage 7. Select undervoltage threshold using TH0-TH4. See Table 2. For improved noise immunity, bypass IN7 to GND with a 0.1µF capacitor as close to the device as possible.                                                                                                                                                                                                                         |

### **Pin Description (continued)**

| PIN     |         | PIN          |      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|---------|---------|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MAX6892 | MAX6893 | MAX6894      | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 25      | 21      | _            | IN6  | Input Voltage 6. Select undervoltage threshold using TH0–TH4. See Table 2. For improved noise immunity, bypass IN6 to GND with a 0.1µF capacitor as close to the device as possible.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 26      | 22      | _            | IN5  | Input Voltage 5. Select undervoltage threshold using TH0–TH4. See Table 2. Power the device through IN2–IN5 or V <sub>CC</sub> (see the <i>Powering the MAX6892/MAX6893/MAX6894</i> section). For improved noise immunity, bypass IN5 to GND with a 0.1µF capacitor as close to the device as possible.                                                                                                                                                                                                                                                                                               |  |  |  |

| 27      | 23      | 23           | IN4  | Input Voltage 4. Select undervoltage threshold using TH0–TH4. See Table 2. Power the device through IN2–IN5 or V <sub>CC</sub> (see the <i>Powering the MAX6892/MAX6893/MAX6894</i> section). For improved noise immunity, bypass IN4 to GND with a 0.1µF capacitor as close to the device as possible.                                                                                                                                                                                                                                                                                               |  |  |  |

| 28      | 24      | 24           | IN3  | Input Voltage 3. Select undervoltage threshold using TH0–TH4. See Table 2. Power the device through IN2–IN5 or V <sub>CC</sub> (see the <i>Powering the MAX6892/MAX6893/MAX6894</i> section). For improved noise immunity, bypass IN3 to GND with a 0.1µF capacitor as close to the device as possible.                                                                                                                                                                                                                                                                                               |  |  |  |

| 29      | 25      | 25           | IN2  | Input Voltage 2. Select undervoltage threshold using TH0–TH4. See Table 2. Power the device through IN2–IN5 or V <sub>CC</sub> (see the <i>Powering the MAX6892/MAX6893/MAX6894</i> section). For improved noise immunity, bypass IN2 to GND with a 0.1µF capacitor as close to the device as possible.                                                                                                                                                                                                                                                                                               |  |  |  |

| 30      | 26      | 26           | IN1  | Input Voltage 1. Select undervoltage threshold using TH0–TH4. See Table 2. For improved noise immunity, bypass IN1 to GND with a 0.1µF capacitor as close to the device as possible.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 31      | 27      | 27           | WDI  | Watchdog Timer Input. Logic input for the watchdog timer function. If WDI is not strobed with a valid low-to-high or high-to-low transition within the watchdog timeout period, the watchdog output asserts low. The watchdog timeout period is externally adjustable with capacitor C <sub>SWT</sub> or selectable for a fixed internal timeout period. The watchdog has a long timeout period (92.16s minimum fixed or 64x the adjusted short timeout period) after each reset event and a short timeout period (1.44s minimum or an adjusted timeout period) after the first valid WDI transition. |  |  |  |

| 32      | 28      | 28           | PG1  | Open-Drain, Power-Good Output 1. PG1 asserts low when the voltage input at IN1 is below the pin-selectable/adjustable input threshold or ENABLE is pulled high. PG1 deasserts with a factory preset timeout period of 6.25ms.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| _       | _       | 5, 6, 21, 22 | N.C. | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| _       | _       | _            | EP   | Exposed Pad. Internally connected to GND. Connect EP to GND or leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

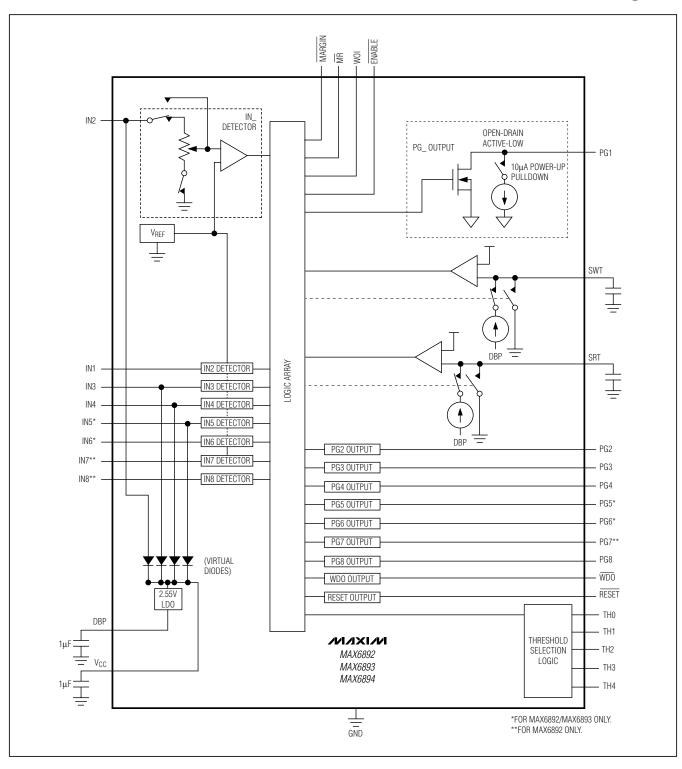

Functional Diagram

10 \_\_\_\_\_\_ **/\!/**X**!/\!**

### **Detailed Description**

The MAX6892/MAX6893/MAX6894 pin-selectable, multivoltage supply sequencers/supervisors monitor several voltage detector inputs and one watchdog input, asserting the outputs when the respective input thresholds have been reached or a timeout occurs. All versions have an enable manual reset and margin input disable. The MAX6892/MAX6893/MAX6894 voltage thresholds are selected by logic inputs and/or an external voltage-divider. A RESET output ensures all monitored inputs are above the pin-selected/adjustable thresholds. Watchdog and reset timeout periods can use factory default settings or are independently adjustable by connecting external capacitors. In addition, all devices can be powered through the voltage detector inputs alone, or externally supplied from a constant supply on the VCC pin (see the *Powering the* MAX6892/MAX6893/MAX6894 section). The outputs are factory configured as open drain.

### Powering the MAX6892/MAX6893/MAX6894

The MAX6892/MAX6893/MAX6894 derive power from the voltage detector inputs: IN2-IN5 (MAX6892/MAX6893), IN2-IN4 (MAX6894), or through an externally supplied VCC. A virtual diode-ORing scheme selects the positive input that supplies power to the device (see the *Functional Diagram*). The highest input voltage on IN2-IN5 (MAX6892/MAX6893)/IN2-IN4 (MAX6894) supplies power to the device. One of IN2-IN5 (MAX6889/MAX6890)/IN2-IN4 (MAX6891) or VCC must be at least 2.7V to ensure proper operation.

Internal hysteresis ensures that the supply input that initially powered the device continues to power the device when multiple input voltages are within 50mV of each other.

VCC powers the analog circuitry and is the bypass connection for the MAX6892/MAX6893/MAX6894 internal supply. Bypass VCC to GND with a 1µF ceramic capacitor installed as close to the device as possible. The internal supply voltage, measured at VCC, equals the maximum of IN2–IN5. If VCC is externally supplied, VCC must be at least 200mV higher than any voltage applied to IN2–IN5 and VCC must be brought up first. VCC always powers the device when all IN\_ are factory set as "ADJ." Do not use the internally generated VCC to provide power to external circuitry.

The MAX6892/MAX6893/MAX6894 also generate a digital supply voltage (DBP) for the internal logic circuitry and the output stages. Bypass DBP to GND with a 1µF ceramic capacitor installed as close to the device as possible. The nominal DBP output voltage is 2.55V. Do not use DBP to provide power to external circuitry.

#### Inputs

The MAX6892/MAX6893/MAX6894 contain multiple logic and voltage detector inputs. Each voltage detector input is monitored for undervoltage thresholds.

#### Voltage Detector Inputs (IN\_)

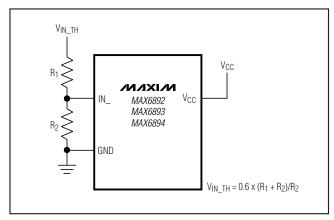

The MAX6892/MAX6893/MAX6894 offer several monitor options with both pin-selectable and adjustable reset thresholds. The threshold voltage at each adjustable IN\_ input is typically 0.6V. To monitor a voltage > 0.6V, connect a resistor-divider network to the circuit as shown in Figure 1:

$$V_{IN} T_H = V_{TH} (R_1 + R_2)/R_2$$

(Equation 1)

where  $V_{IN\_TH}$  is the desired reset threshold voltage for the respective IN\_ and  $V_{TH}$  is the input threshold (0.6V).

Resistors  $R_1$  and  $R_2$  can have high values to minimize current consumption due to low-leakage currents. Set  $R_2$  to some conveniently high value (10k $\Omega$ , for example) and calculate  $R_1$  based on the desired reset threshold voltage, using the following formula:

$$R_1 = R_2 \times (V_{IN} TH/V_{TH} - 1)$$

Figure 1. Adjusting the Monitored Threshold

#### Threshold Logic Inputs (TH0-TH4)

The TH0-TH4 logic inputs select the undervoltage thresholds and tolerance of the IN1-IN8 inputs (MAX6892), IN1-IN6 inputs (MAX6893), and IN1-IN4 inputs (MAX6894). TH0-TH4 define 32 unique options for the supervisor functionality. Connect the respective TH\_ to GND for a logic 0 or to DBP for a logic 1. Tables 1 and 2 show the 32 unique threshold options available. TH4 sets

the threshold tolerance of the undervoltage threshold. A logic 1 selects a 5% supply tolerance and a logic 0 selects 10% supply tolerance. The MAX6892/MAX6893/MAX6894 logic determines which thresholds should be used for the IN inputs only at power-up. Use the voltage-divider circuit of Figure 1 and Equation 1 to set the threshold for the user-adjustable inputs as described in the *Voltage Detector Inputs (IN)* section.

**Table 1. Nominal Monitored Supply Voltages**

| OFI FOTION | T114 T110 | MONITORED SUPPLY VOLTAGES (V) |     |     |     |     |     |     |     | SUPPLY        |

|------------|-----------|-------------------------------|-----|-----|-----|-----|-----|-----|-----|---------------|

| SELECTION  | TH4-TH0   | IN1                           | IN2 | IN3 | IN4 | IN5 | IN6 | IN7 | IN8 | TOLERANCE (%) |

| 1          | 11111     | ADJ                           | 5   | 3.3 | 2.5 | 1.8 | ADJ | ADJ | ADJ | 5             |

| 2          | 11110     | ADJ                           | 5   | 3   | 2.5 | 1.8 | ADJ | ADJ | ADJ | 5             |

| 3          | 11101     | ADJ                           | 5   | 3.3 | 2.5 | ADJ | ADJ | ADJ | ADJ | 5             |

| 4          | 11100     | ADJ                           | 5   | 3   | 2.5 | ADJ | ADJ | ADJ | ADJ | 5             |

| 5          | 11011     | ADJ                           | 5   | 3.3 | 1.8 | ADJ | ADJ | ADJ | ADJ | 5             |

| 6          | 11010     | ADJ                           | 5   | 3   | 1.8 | ADJ | ADJ | ADJ | ADJ | 5             |

| 7          | 11001     | ADJ                           | 5   | 3.3 | ADJ | ADJ | ADJ | ADJ | ADJ | 5             |

| 8          | 11000     | ADJ                           | 5   | 3   | ADJ | ADJ | ADJ | ADJ | ADJ | 5             |

| 9          | 10111     | ADJ                           | 3.3 | 2.5 | 1.8 | ADJ | ADJ | ADJ | ADJ | 5             |

| 10         | 10110     | ADJ                           | 3   | 2.5 | 1.8 | ADJ | ADJ | ADJ | ADJ | 5             |

| 11         | 10101     | ADJ                           | 3.3 | 2.5 | ADJ | ADJ | ADJ | ADJ | ADJ | 5             |

| 12         | 10100     | ADJ                           | 3   | 2.5 | ADJ | ADJ | ADJ | ADJ | ADJ | 5             |

| 13         | 10011     | ADJ                           | 3.3 | 1.8 | ADJ | ADJ | ADJ | ADJ | ADJ | 5             |

| 14         | 10010     | ADJ                           | 3   | 1.8 | ADJ | ADJ | ADJ | ADJ | ADJ | 5             |

| 15         | 10001     | ADJ                           | 3.3 | 2.5 | 1.8 | 1.5 | ADJ | ADJ | ADJ | 5             |

| 16         | 10000     | ADJ                           | 3   | 2.5 | 1.8 | 1.5 | ADJ | ADJ | ADJ | 5             |

| 17         | 01111     | ADJ                           | 5   | 3.3 | 2.5 | 1.8 | ADJ | ADJ | ADJ | 10            |

| 18         | 01110     | ADJ                           | 5   | 3   | 2.5 | 1.8 | ADJ | ADJ | ADJ | 10            |

| 19         | 01101     | ADJ                           | 5   | 3.3 | 2.5 | ADJ | ADJ | ADJ | ADJ | 10            |

| 20         | 01100     | ADJ                           | 5   | 3   | 2.5 | ADJ | ADJ | ADJ | ADJ | 10            |

| 21         | 01011     | ADJ                           | 5   | 3.3 | 1.8 | ADJ | ADJ | ADJ | ADJ | 10            |

| 22         | 01010     | ADJ                           | 5   | 3   | 1.8 | ADJ | ADJ | ADJ | ADJ | 10            |

| 23         | 01001     | ADJ                           | 5   | 3.3 | ADJ | ADJ | ADJ | ADJ | ADJ | 10            |

| 24         | 01000     | ADJ                           | 5   | 3   | ADJ | ADJ | ADJ | ADJ | ADJ | 10            |

| 25         | 00111     | ADJ                           | 3.3 | 2.5 | 1.8 | ADJ | ADJ | ADJ | ADJ | 10            |

| 26         | 00110     | ADJ                           | 3   | 2.5 | 1.8 | ADJ | ADJ | ADJ | ADJ | 10            |

| 27         | 00101     | ADJ                           | 3.3 | 2.5 | ADJ | ADJ | ADJ | ADJ | ADJ | 10            |

| 28         | 00100     | ADJ                           | 3   | 2.5 | ADJ | ADJ | ADJ | ADJ | ADJ | 10            |

| 29         | 00011     | ADJ                           | 3.3 | 1.8 | ADJ | ADJ | ADJ | ADJ | ADJ | 10            |

| 30         | 00010     | ADJ                           | 3   | 1.8 | ADJ | ADJ | ADJ | ADJ | ADJ | 10            |

| 31         | 00001     | ADJ                           | 3.3 | 2.5 | 1.8 | 1.5 | ADJ | ADJ | ADJ | 10            |

| 32         | 00000     | ADJ                           | ADJ | ADJ | ADJ | ADJ | ADJ | ADJ | ADJ | _             |

**Table 2. Threshold Options**

| OF LEGISON | THA THOS |      |      | TI   | HRESHOLD | VOLTAGES | (V)  |      |      |

|------------|----------|------|------|------|----------|----------|------|------|------|

| SELECTION  | TH4-TH0* | IN1  | IN2  | IN3  | IN4      | IN5      | IN6  | IN7  | IN8  |

| 1          | 11111    | 0.60 | 4.62 | 3.06 | 2.31     | 1.67     | 0.60 | 0.60 | 0.60 |

| 2          | 11110    | 0.60 | 4.62 | 2.78 | 2.31     | 1.67     | 0.60 | 0.60 | 0.60 |

| 3          | 11101    | 0.60 | 4.62 | 3.06 | 2.31     | 0.60     | 0.60 | 0.60 | 0.60 |

| 4          | 11100    | 0.60 | 4.62 | 2.78 | 2.31     | 0.60     | 0.60 | 0.60 | 0.60 |

| 5          | 11011    | 0.60 | 4.62 | 3.06 | 1.67     | 0.60     | 0.60 | 0.60 | 0.60 |

| 6          | 11010    | 0.60 | 4.62 | 2.78 | 1.67     | 0.60     | 0.60 | 0.60 | 0.60 |

| 7          | 11001    | 0.60 | 4.62 | 3.06 | 0.60     | 0.60     | 0.60 | 0.60 | 0.60 |

| 8          | 11000    | 0.60 | 4.62 | 2.78 | 0.60     | 0.60     | 0.60 | 0.60 | 0.60 |

| 9          | 10111    | 0.60 | 3.06 | 2.31 | 1.8      | 0.60     | 0.60 | 0.60 | 0.60 |

| 10         | 10110    | 0.60 | 2.78 | 2.31 | 1.8      | 0.60     | 0.60 | 0.60 | 0.60 |

| 11         | 10101    | 0.60 | 3.06 | 2.31 | 0.60     | 0.60     | 0.60 | 0.60 | 0.60 |

| 12         | 10100    | 0.60 | 2.78 | 2.31 | 0.60     | 0.60     | 0.60 | 0.60 | 0.60 |

| 13         | 10011    | 0.60 | 3.06 | 1.67 | 0.60     | 0.60     | 0.60 | 0.60 | 0.60 |

| 14         | 10010    | 0.60 | 2.78 | 1.67 | 0.60     | 0.60     | 0.60 | 0.60 | 0.60 |

| 15         | 10001    | 0.60 | 3.06 | 2.31 | 1.67     | 1.39     | 0.60 | 0.60 | 0.60 |

| 16         | 10000    | 0.60 | 2.78 | 2.31 | 1.67     | 1.39     | 0.60 | 0.60 | 0.60 |

| 17         | 01111    | 0.60 | 4.38 | 2.88 | 2.19     | 1.58     | 0.60 | 0.60 | 0.60 |

| 18         | 01110    | 0.60 | 4.38 | 2.62 | 2.19     | 1.58     | 0.60 | 0.60 | 0.60 |

| 19         | 01101    | 0.60 | 4.38 | 2.88 | 2.19     | 0.60     | 0.60 | 0.60 | 0.60 |

| 20         | 01100    | 0.60 | 4.38 | 2.62 | 2.19     | 0.60     | 0.60 | 0.60 | 0.60 |

| 21         | 01011    | 0.60 | 4.38 | 2.88 | 1.58     | 0.60     | 0.60 | 0.60 | 0.60 |

| 22         | 01010    | 0.60 | 4.38 | 2.62 | 1.58     | 0.60     | 0.60 | 0.60 | 0.60 |

| 23         | 01001    | 0.60 | 4.38 | 2.88 | 0.60     | 0.60     | 0.60 | 0.60 | 0.60 |

| 24         | 01000    | 0.60 | 4.38 | 2.62 | 0.60     | 0.60     | 0.60 | 0.60 | 0.60 |

| 25         | 00111    | 0.60 | 2.88 | 2.19 | 1.8      | 0.60     | 0.60 | 0.60 | 0.60 |

| 26         | 00110    | 0.60 | 2.62 | 2.19 | 1.8      | 0.60     | 0.60 | 0.60 | 0.60 |

| 27         | 00101    | 0.60 | 2.88 | 2.19 | 0.60     | 0.60     | 0.60 | 0.60 | 0.60 |

| 28         | 00100    | 0.60 | 2.62 | 2.19 | 0.60     | 0.60     | 0.60 | 0.60 | 0.60 |

| 29         | 00011    | 0.60 | 2.88 | 1.58 | 0.60     | 0.60     | 0.60 | 0.60 | 0.60 |

| 30         | 00010    | 0.60 | 2.62 | 1.58 | 0.60     | 0.60     | 0.60 | 0.60 | 0.60 |

| 31         | 00001    | 0.60 | 2.88 | 2.19 | 1.58     | 1.31     | 0.60 | 0.60 | 0.60 |

| 32         | 00000    | 0.60 | 0.60 | 0.60 | 0.60     | 0.60     | 0.60 | 0.60 | 0.60 |

<sup>\*</sup>TH4 = '1' selects 7.5% threshold tolerance, TH4 = '0' selects 12.5% threshold tolerance. Contact factory for alternative thresholds.

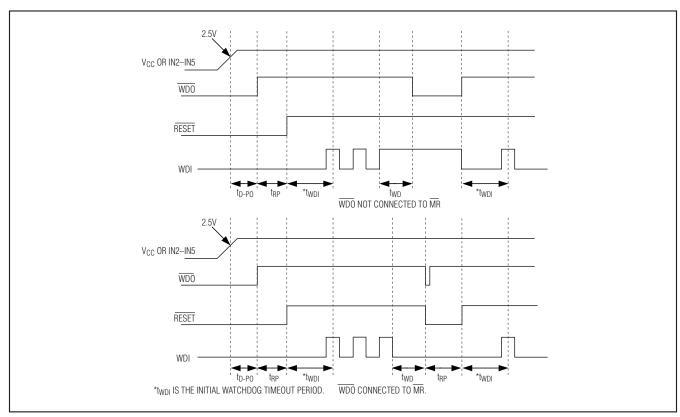

#### Watchdog Timer

The MAX6892/MAX6893/MAX6894s' watchdog circuit monitors the microprocessor's ( $\mu$ P's) activity. If the  $\mu$ P does not toggle the watchdog input (WDI) within the watchdog timeout period, the watchdog output (WDO) asserts. The internal watchdog timer is cleared by RESET, or by a transition at WDI (which can detect pulses as short as 50ns). The watchdog timer remains cleared while reset is asserted. The timer starts counting as soon as WDO is released (see Figure 2).

The MAX6892/MAX6893/MAX6894 feature two modes of watchdog timer operation: normal mode and initial mode. At power-up, after a reset event, or after the watchdog timer expires, the initial watchdog timeout is active. After the first transition on WDI, the normal watchdog timeout is active. The initial and normal watchdog timeouts are determined by the value of the capacitor connected between SWT and ground or by connecting SWT to VCC (see the *Selecting the Reset and*

Watchdog Timeout Capacitor section). The initial watchdog timeout is approximately 64 times the normal watchdog timeout. For example, in initial mode a  $1\mu F$  capacitor gives a watchdog timeout period of about 5min.

If  $\overline{\text{WDO}}$  is connected to  $\overline{\text{MR}}$ , the  $\overline{\text{WDO}}$  asserts for a short duration (~5 $\mu$ s), long enough to assert the  $\overline{\text{RESET}}$  output. Asserting  $\overline{\text{RESET}}$  clears the watchdog timer and  $\overline{\text{WDO}}$  goes high. The reset output remains asserted for its timeout period after a watchdog fault. The watchdog timer stays cleared as long as  $\overline{\text{RESET}}$  is low.

The watchdog timeout period is determined by the value of the capacitor connected between SWT and ground (see the *Selecting the Reset/Watchdog Timeout Capacitor* section). Connect SWT to DBP to select factory-programmed watchdog timeout. To disable the watchdog timer connect SWT to GND.

Figure 2. Watchdog, Reset, and Power-Up Timing Diagram

#### Manual Reset (MR)

Many  $\mu P$ -based products require manual reset capability to allow an operator or external logic circuitry to initiate a reset. The manual reset input ( $\overline{MR}$ ) can connect directly to a switch without an external pullup resistor or debouncing network.  $\overline{MR}$  is internally pulled up to DBP through a  $10\mu A$  current source and, therefore, can be left unconnected if unused.

MR is designed to reject fast falling transients (typically 100ns pulses) and it must be held low for a minimum of 1µs to assert RESET. After MR transitions from low to high, RESET remains asserted for the duration of the reset timeout period.

#### Margin Output Disable (MARGIN)

MARGIN allows system-level testing while power supplies exceed the normal ranges. Driving MARGIN low forces PG\_, RESET, and WDO to hold the last state while system-level testing occurs. Leave MARGIN unconnected or connect to DBP if unused. An internal 10μA current source pulls MARGIN to DBP. The state of each programmable output, RESET, and WDO does not change while MARGIN = GND.

#### Enable Input

ENABLE is an active-low, logic input. Driving ENABLE high pulls all PG\_ low. Drive ENABLE low or leave unconnected for normal operation. ENABLE is internally pulled down to GND through a 10µA current sink.

#### **Power-Good Outputs**

The MAX6892 features eight power-good outputs, the MAX6893 features six power-good outputs, and the MAX6894 features four power-good outputs. Each output (PG\_) responds to its respective input (IN\_). Each PG\_ is open drain. During power-up, the outputs pull down to GND with an internal 10μA current sink for 1V < VCC < VUVI O.

#### **RESET Output**

The reset output is typically connected to the reset input of a  $\mu$ P. A  $\mu$ P's reset input starts or restarts the  $\mu$ P in a known state. The MAX6892/MAX6893/MAX6894 supervisory circuits provide the reset logic to prevent code-execution errors during power-up, power-down, and brownout conditions.

RESET changes from high to low whenever one or more input voltage (IN1–IN8) monitors drop below their respective reset threshold voltage or when MR is pulled low for a minimum of 1µs. Once the affected input voltage monitor(s) exceeds its respective reset threshold voltage(s), RESET remains low for the reset timeout period, then deaaserts.

### **Applications Information**

#### Selecting the Reset/Watchdog Timeout Capacitor

The reset timeout period can be adjusted to accommodate a variety of  $\mu P$  applications. Adjust the reset timeout period ( $t_{RP}$ ) by connecting a capacitor ( $C_{SRT}$ ) between SRT and ground. Calculate the reset timeout capacitor as follows:

$$C_{SRT} = t_{RP}/(4.348 \times 106)$$

with t<sub>RP</sub> in seconds and C<sub>SRT</sub> in Farads. Connect SRT to V<sub>CC</sub> for a factory-programmed reset timeout of 200ms (typ).

The watchdog timeout period can be adjusted to accommodate a variety of µP applications. With this feature, the watchdog timeout can be optimized for software execution. The programmer can determine how often the watchdog timer should be serviced. Adjust the watchdog timeout period (twp) by connecting a specific value capacitor (CSWT) between SWT and GND. For normal mode operation, calculate the watchdog timeout capacitor as follows:

$$C_{SWT} = t_{WD}/(4.348 \times 10^6)$$

with two in seconds and C<sub>SWT</sub> in Farads. Connect SWT to V<sub>CC</sub> for a factory-programmed watchdog timeout of 1.6s (normal mode) and 102.4s (initial mode).

CSRT and CSWT must be a low-leakage (< 10nA) type capacitor. Ceramic capacitors are recommended.

#### Layout and Bypassing

For better noise immunity, bypass each of the voltage detector inputs to GND with  $0.1\mu F$  capacitors installed as close to the device as possible. Bypass  $V_{CC}$  and DBP to GND with  $1\mu F$  capacitors installed as close to the device as possible.

Pin Configuration (continued)

### Typical Operating Circuit

\_\_\_\_\_Chip Information

PROCESS: BICMOS

#### \_Package Information

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| ·               | <u> </u>        |                |                     |

|-----------------|-----------------|----------------|---------------------|

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE NO.    | LAND<br>PATTERN NO. |

| 28 Thin QFN     | T2855+8         | <u>21-0140</u> | 90-0028             |

| 32 Thin QFN     | T3255+4         | 21-0140        | 90-0012             |

8 \_\_\_\_\_\_ /II/XI/M

### **Revision History**

| 1 | EVISION<br>IUMBER | REVISION<br>DATE | DESCRIPTION                                                                                       | PAGES<br>CHANGED                 |

|---|-------------------|------------------|---------------------------------------------------------------------------------------------------|----------------------------------|

|   | 0                 | 2/05             | Initial release                                                                                   | _                                |

|   | 1                 | 9/10             | Add lead-free package, add exposed pad info, update <i>Absolute Maximum Ratings</i> , style edits | 1–6, 8–11, 13,<br>15, 16, 18, 19 |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

# AMEYA360 Components Supply Platform

### **Authorized Distribution Brand:**

### Website:

Welcome to visit www.ameya360.com

### Contact Us:

### > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

### > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

### Customer Service :

Email service@ameya360.com

### Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com