# 8 channel high-side LED driver for automotive applications

Datasheet - production data

#### **Features**

- Octal fully protected high-side switches with programmable overcurrent threshold and RDSON

- Split supply for flexible application assignment (6 V to 24V)

- SPI communication interface with daisy chain capability

- Digital diagnosis individually for each switch

- Analogue current sense output with SPI programmable multiplexer

- Integrated synchronous PWM module with programmable phase shift, pulse skipping feature and guick access via direct drive pins

- Improved EMC behavior by phase shift control and output edge shaping

- Limp home function with 6 independent direct drive pins

- Integrated fail mode handling

- Ultra low power mode (< 5 μA max at 25°C)

# **Applications**

- · Automotive interior lighting

- Automotive exterior lighting

# **Description**

The L99CL01XP is designed to provide a cost effective solution for exterior and interior automotive lighting applications with LEDs.

Table 1. Device summary

| Packago     | Order code         |               |  |

|-------------|--------------------|---------------|--|

| Package     | Tube               | Tape and real |  |

| PowerSSO-36 | Root part number 1 | L99CL01XPTR   |  |

Contents L99CL01XP

# **Contents**

| 1 | Bloc | Block diagram and pin description |                                            |    |  |  |  |

|---|------|-----------------------------------|--------------------------------------------|----|--|--|--|

|   | 1.1  | Power                             | r supply (VS, GND)                         | 10 |  |  |  |

|   | 1.2  | VDD (                             | logic interface supply voltage)            | 10 |  |  |  |

|   | 1.3  | ENAB                              | LE (active high)                           | 10 |  |  |  |

| 2 | Fund | ctional                           | description                                | 11 |  |  |  |

|   | 2.1  | Switch                            | n supply terminals (VSA, VSB, VSC and VSD) | 11 |  |  |  |

|   | 2.2  | Power                             | r Outputs [OUT1 ~ OUT8]                    |    |  |  |  |

|   | 2.3  | Curre                             | nt Sense (CS) – analog diagnosis           | 12 |  |  |  |

|   | 2.4  |                                   | ol inputs (IN1, IN2, IN3, IN5, IN6, IN7)   |    |  |  |  |

|   | 2.5  |                                   | CLK input / wake output pin                |    |  |  |  |

|   |      | 2.5.1                             | PWMCLK input                               |    |  |  |  |

|   |      | 2.5.2                             | WAKE output                                |    |  |  |  |

|   | 2.6  | Limp i                            | nput                                       |    |  |  |  |

|   | 2.7  | -                                 | ol, protection and diagnosis               |    |  |  |  |

|   |      | 2.7.1                             | Smart switches and gate drivers            |    |  |  |  |

|   |      | 2.7.2                             | PWM module                                 |    |  |  |  |

|   |      | 2.7.3                             | Overcurrent detection                      | 17 |  |  |  |

|   |      | 2.7.4                             | External resistor                          | 17 |  |  |  |

|   |      | 2.7.5                             | Channel voltage level comparator           | 17 |  |  |  |

|   |      | 2.7.6                             | Device protection                          | 17 |  |  |  |

| 3 | SPI  | interfac                          | e                                          | 19 |  |  |  |

|   | 3.1  | SPI co                            | ommunication                               | 19 |  |  |  |

|   |      | 3.1.1                             | CSN (chip select (active low))             | 19 |  |  |  |

|   |      | 3.1.2                             | SCK (serial input clock)                   | 19 |  |  |  |

|   |      | 3.1.3                             | SDI (serial data input)                    | 19 |  |  |  |

|   |      | 3.1.4                             | SDO (serial data output)                   | 20 |  |  |  |

|   |      | 3.1.5                             | Control Data Registers (CDR)               | 20 |  |  |  |

|   |      | 3.1.6                             | Status Data Registers                      | 29 |  |  |  |

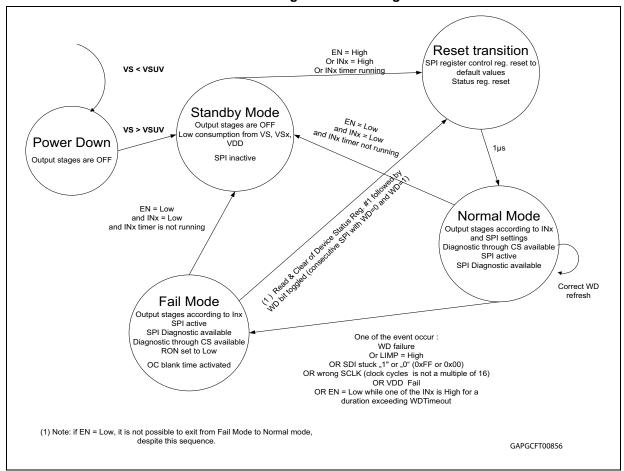

|   | 3.2  | Opera                             | iting modes                                | 40 |  |  |  |

|   |      | 3.2.1                             | Standby mode                               |    |  |  |  |

|   |      | 3.2.2                             | Wake up and operating modes                | 40 |  |  |  |

47/

|   |      | 3.2.3     | Cold start – power up reset4                                            | 11         |

|---|------|-----------|-------------------------------------------------------------------------|------------|

|   |      | 3.2.4     | Normal Mode                                                             | 11         |

|   |      | 3.2.5     | Fail Mode                                                               | 12         |

|   |      | 3.2.6     | Warm start – (Transition from FailMode to Normal over Internal Reset) 4 | 14         |

| 4 | Elec | trical sp | pecifications 4                                                         | .5         |

|   | 4.1  | Absolu    | ute maximum rating                                                      | ŀ5         |

|   | 4.2  | Therm     | al data4                                                                | <b>l</b> 6 |

|   | 4.3  | Electri   | cal characteristics                                                     | ١7         |

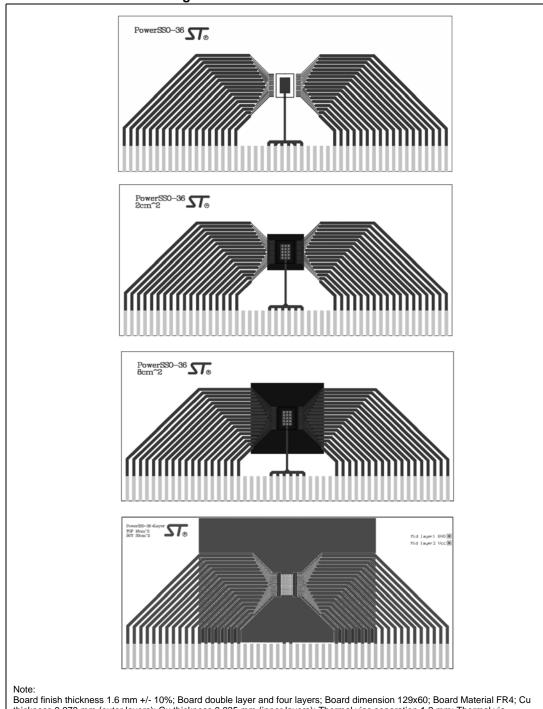

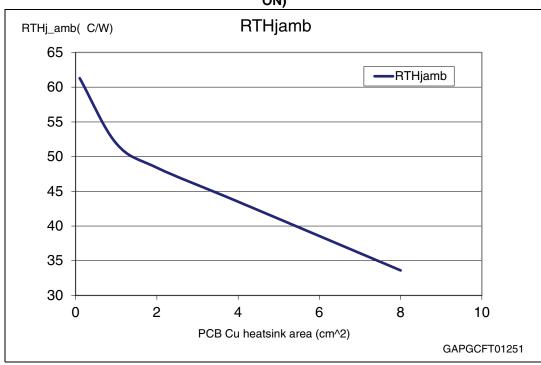

| 5 | Pack | kage an   | d PCB thermal data5                                                     | 3          |

|   | 5.1  | Power     | SSO-36 thermal data 5                                                   | 53         |

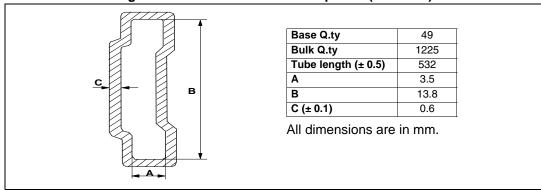

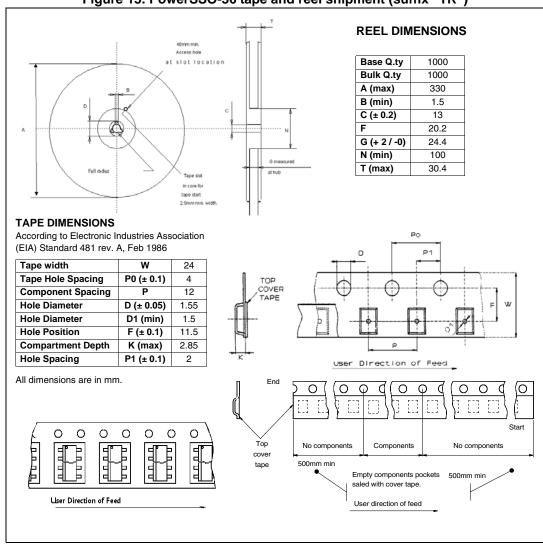

| 6 | Pack | kage inf  | ormation                                                                | 5          |

|   | 6.1  | ECOP      | ACK <sup>®</sup> 5                                                      | 55         |

|   | 6.2  | Power     | SSO-36™ mechanical data5                                                | 56         |

|   | 6.3  | Packir    | ng information                                                          | 58         |

| 7 | Revi | sion his  | story 5                                                                 | 9          |

List of tables L99CL01XP

# List of tables

| Table 1.  | Device summary                                                                          | . 1 |

|-----------|-----------------------------------------------------------------------------------------|-----|

| Table 2.  | Pin function                                                                            |     |

| Table 3.  | PWM mode selection for OUTx (x = 1, 2, 3, 5, 6 or 7) when INx is disabled               | 14  |

| Table 4.  | PWM mode selection for OUTx ( $x = 1, 2, 3, 5, 6$ or 7) when INx is enabled and INx = 0 |     |

| Table 5.  | PWM mode selection for OUTx ( $x = 1, 2, 3, 5, 6$ or 7) when INx is enabled and INx = 1 |     |

| Table 6.  | Examples of settings for INSELx[1:0] and PWMSELx[1:0] resulting in OUTx states, which   |     |

|           | are independent from INx                                                                |     |

| Table 7.  | Examples of settings for INSELx[1:0] and PWMSELx[1:0] resulting in OUTx states, which   | า   |

|           | are dependent from INx                                                                  |     |

| Table 8.  | PWM mode selection for OUT4 and OUT8                                                    | 16  |

| Table 9.  | Duty cycle selection (PSF enabled)                                                      | 16  |

| Table 10. | Error handling                                                                          | 18  |

| Table 11. | CDR registers                                                                           | 20  |

| Table 12. | Control Data Register                                                                   | 28  |

| Table 13. | SDR registers                                                                           | 29  |

| Table 14. | Status Data Register                                                                    | 39  |

| Table 15. | Mapping between the input pins and the outputs in Fail Mode                             | 42  |

| Table 16. | Events leading to Fail Mode                                                             | 42  |

| Table 17. | Control registers in Fail Mode                                                          | 42  |

| Table 18. | Absolute maximum rating                                                                 |     |

| Table 19. | Temperature warning and thermal shutdown                                                | 46  |

| Table 20. | Thermal data                                                                            | 46  |

| Table 21. | Digital timings                                                                         | 46  |

| Table 22. | Electrical characteristics (logic + inputs)                                             |     |

| Table 23. | Dynamic characteristics (SPI)                                                           | 48  |

| Table 24. | Switching (V <sub>S</sub> = 12 V; T <sub>i</sub> = 25°C)                                | 49  |

| Table 25. | Electrical characteristics (OUT1 - OUT8)                                                |     |

| Table 26. | Electrical transient requirements (part 1/3)                                            | 51  |

| Table 27. | Electrical transient requirements (part 2/3)                                            | 51  |

| Table 28. | Electrical transient requirements (part 3/3)                                            | 52  |

| Table 29. | PowerSSO-36™ mechanical data                                                            | 57  |

| Table 30  | Document revision history                                                               | 50  |

4/60 DocID023902 Rev 4

L99CL01XP List of figures

# **List of figures**

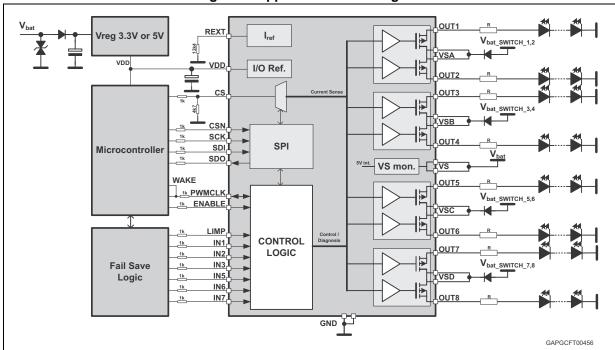

| Figure 1.  | Application block diagram                                                               | 6  |

|------------|-----------------------------------------------------------------------------------------|----|

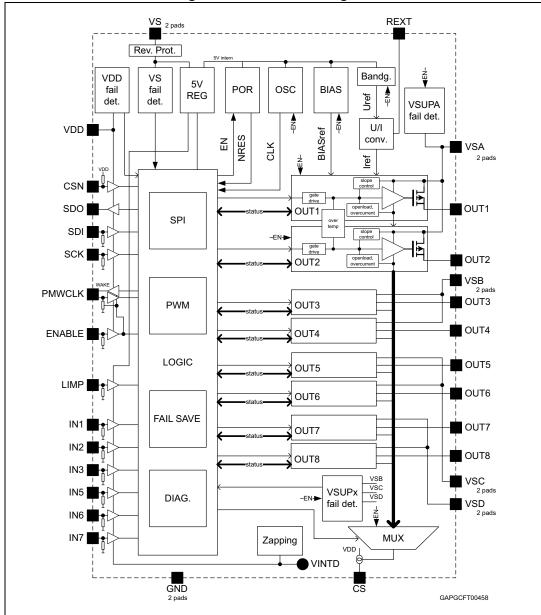

| Figure 2.  | Device block diagram                                                                    | 7  |

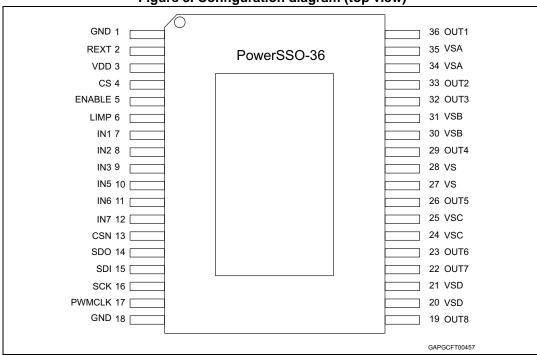

| Figure 3.  | Configuration diagram (top view)                                                        | 8  |

| Figure 4.  | State diagram                                                                           | 40 |

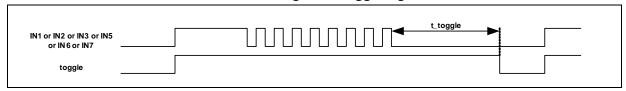

| Figure 5.  | Toggle signal                                                                           | 41 |

| Figure 6.  | Fail mode status diagram                                                                | 44 |

| Figure 7.  | Reset mode                                                                              | 44 |

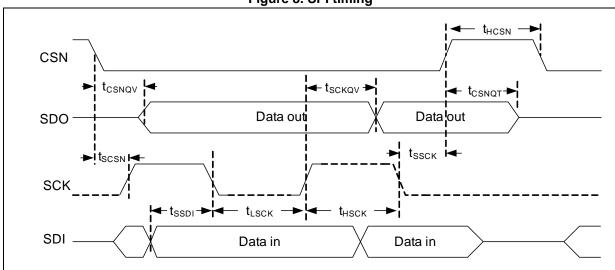

| Figure 8.  | SPI timing                                                                              | 49 |

| Figure 9.  | PowerSSO-36 PC board                                                                    | 53 |

| Figure 10. | R <sub>thi-amb</sub> vs PCB copper area in open box free air condition (one channel ON) | 54 |

| Figure 11. | PowerSSO-36™ package dimensions                                                         |    |

| Figure 12. | PowerSSO-36 tube shipment (no suffix)                                                   |    |

| Figure 13. | PowerSSO-36 tape and reel shipment (suffix "TR")                                        |    |

# 1 Block diagram and pin description

Figure 1. Application block diagram

Figure 2. Device block diagram

Figure 3. Configuration diagram (top view)

**Table 2. Pin function**

| Pin                    | Symbol                             | Function                                                                                                                                                                                                                                                                                            |

|------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,18                   | GND                                | Ground: This terminal is the ground for the logic and analogue circuitry of the device.                                                                                                                                                                                                             |

| 2                      | REXT                               | External Resistor: The Resistor is used to improve internal current precision.                                                                                                                                                                                                                      |

| 3                      | VDD                                | Logic supply voltage: SPI and logic I/O structure power supply.                                                                                                                                                                                                                                     |

| 4                      | CS                                 | Current sense output: This terminal is used to supply a current proportional to the output current in the power output stages. The selection of the output is SPI programmable.                                                                                                                     |

| 5                      | ENABLE                             | Enable (active high): This input enables the device. After wakeup the internal configuration is in default state. The terminal has an internal pull down resistor.                                                                                                                                  |

| 6                      | LIMP                               | Limp home input (active high): The fail mode of the component can be activated by logic [1] at this input. The LIMP state is internally filtered by a 10ms digital filter. This terminal has an internal pull down resistor.                                                                        |

| 7,8,<br>9,10,<br>11,12 | IN1, IN2,<br>IN3, IN5,<br>IN6, IN7 | Direct Drive input 1,2,3,5,6,7: These inputs enable the device and are used to control the corresponding power outputs 1,2,3,5,6,7 in case of fail mode (direct drive). During normal mode the control of the outputs is SPI programmable. All input terminals have an internal pull down resistor. |

**Table 2. Pin function (continued)**

| Pin                                     | Symbol         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|-----------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 13                                      | CSN            | SPI chip select input (active low): When this digital signal is logical [1], SPI signals are ignored. Asserting this terminal [0] an SPI transaction starts. The transaction is indicated as complete when this signal returns to [1]. This terminal has an internal pull up resistor.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 14                                      | SDO            | SPI data-out: SPI data is sent to the microcontroller by this terminal. This data output changes on the positive edge of SCLK. When CSN is [1], this terminal is at high impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 15                                      | SDI            | SPI data-in: This data input is sampled on the negative edge of the SCK. The terminal has an internal pull down resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 16                                      | SCK            | SPI clock input: This digital input terminal is connected to the controller providing the clock (up to 4MHz) for SPI communication. The terminal has an internal pull down resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 17                                      | PWMCLK         | PWM clock input, (WAKE output if ENABLE low): This clock defines the frequency of the internal generated PWM. The terminal has an internal pull down resistor. If ENABLE is low, this pin is used as a WAKE output. This output indicates if another wakeup source, beside ENABLED, is active.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 19, 22,<br>23, 26,<br>29, 32,<br>33, 36 | OUT1 ~<br>OUT8 | Power output 1~8: Fully protected high-side switches with individually programmable R <sub>DSON</sub> and over current shutdown threshold. The output current is up to 1A per channel. However the total current of the device is limited due to the max power dissipation of the component and the total thermal resistance/capacitances of the PCB. The outputs OUT1~OUT3 and OUT5~OUT7 are controlled by the corresponding inputs IN1, IN2, IN3, IN5, IN6, IN7 during fail mode (OUT4 and OUT8 are off). During normal mode the outputs are controlled by the internal PWM generator or the selected direct drive input. |  |  |  |  |  |

| 20, 21                                  | VSD            | Supply voltage pins for outputs 7 and 8. Pins must be tied together on PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 24, 25                                  | VSC            | Supply voltage pins for outputs 5 and 6. Pins must be tied together on PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 27, 28                                  | VS             | Battery supply voltage: Power supply terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 30, 31                                  | VSB            | Supply voltage pins for outputs 3 and 4. Pins must be tied together on PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 34, 35                                  | VSA            | Supply voltage pins for outputs 1 and 2. Pins must be tied together on PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

Note: The Heat Slug is internally connected to GND.

# 1.1 Power supply (VS, GND)

The VS terminal is the power supply pin of the device and it is also used to supply the internal logic of the device. This pin is protected against reverse battery conditions without any external components, down to -24 V.

Overvoltage and undervoltage events on the VS pin are reported by the OVF, respectively the UVF status bits (refer to Device Status #2). Once one of these events has occurred, the corresponding status bit is latched.

The GND is the signal ground and power ground terminal of the device.

# 1.2 VDD (logic interface supply voltage)

The VDD is the logic interface supply voltage terminal, used to supply the SPI communication interface and logic I/Os of the device.

The VDD is monitored by an internal circuitry. In case an under voltage condition is detected, the L99CL01XP enters the Fail Mode after the filter time t<sub>VDD LIV</sub>.

# 1.3 ENABLE (active high)

The ENABLE is used to enable the device by the microcontroller (normal mode). When the ENABLE input is

- logic [0] the device is in standby mode (WAKE output enabled)

- logic [1] the device is in active mode (PWMCLK input enabled)

ENABLE has an internal pull down resistor.

Please check for other wakeup sources the Section 2.4: Control inputs (IN1, IN2, IN3, IN5, IN6, IN7).

# 2 Functional description

# 2.1 Switch supply terminals (VSA, VSB, VSC and VSD)

The device has four groups of output supplies in order to achieve flexible application fuse assignment. The VSA terminal is the drain (power supply pin) of the output switches 1 and 2, while VSB is the supply of switches 3 and 4, VSC is the supply of switches 5 and 6 and VSD is the supply of switches 7 and 8. The supply pins belonging to the same supply group must be connected together in order to ensure proper current capability for PowerMOS devices.

Overvoltage and undervoltage events on the VSX pins are reported by the corresponding OVF\_X, respectively the UVF\_X status bits (refer to Device Status #3). Once one of these events has occurred, the corresponding status bit is latched, the corresponding outputs are latched off and the OUTENx (see control register OUT enable, #10) is set to 0.

The device is fully protected against loss of any supply terminal.

# 2.2 Power Outputs [OUT1 ~ OUT8]

The power outputs are used to control LED arrays with either integrated current source or series resistors.

Each output offers a fully protected p-channel MOSFET (programmable Ron) driver with digital switch diagnosis and analogue current sense circuitry. Paralleling of two or more outputs is possible in order to reduce power dissipation without restriction in performance.

The outputs are protected against:

- output over load and short circuit (incl. very low resistive short circuit and shorts with line inductance)

- overtemperature

- overvoltage/undervoltage

The digital switch diagnosis by SPI communication (see *Section 3.1.6: Status Data Registers*) contains reporting of

- overcurrent shutdown status

- overtemperature shutdown status incl. over temperature warning status

- undervoltage/overvoltage status

In case of undervoltage, thermal shutdown or overcurrent the corresponding OUT is switched off with edge shaping to reduce internal power dissipation in case of hard short.

In normal mode, after a thermal shutdown, an overcurrent, an undervoltage or overvoltage at VSA, VSB, VSC or VSD, the corresponding outputs are latched off until a read and clear command of the corresponding status register is sent.

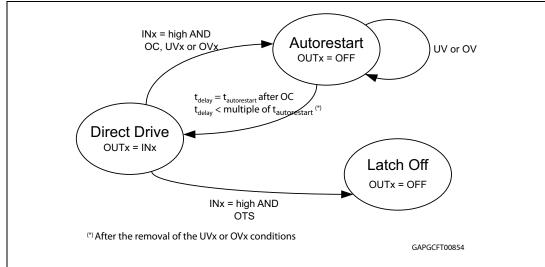

In fail mode, an overtemperature of an output leads to a latch off, whereas, an auto restart strategy is implemented after an overcurrent, an undervoltage or overvoltage at VSA, VSB, VSC or VSD.

# 2.3 Current Sense (CS) – analog diagnosis

The current sense terminal delivers a current which is proportional to the output current. Depending on the programmed  $R_{DSON}$  [#9] (see Section 3.1.5: Control Data Registers (CDR)) the ratio is defined to  $I_{OUT}/1000$  for 1  $\Omega$  and  $I_{OUT}/2000$  for  $600m\Omega$ .

The MUX[2:0] bits select which output channel is connected to the CS pin [#0:D7~D4] (see Section 3.1.5: Control Data Registers (CDR)).

Fast output settling is provided in order to enable processing with synchronous sampling and peak detector as well as diagnosis at very small duty cycle.

# 2.4 Control inputs (IN1, IN2, IN3, IN5, IN6, IN7)

The control inputs are used to

- provide wakeup capability (see Section 3.2.2: Wake up and operating modes).

- directly control the corresponding outputs during fail mode (see Section 3.2.5: Fail Mode).

- control the outputs during normal mode, when the output control is enabled by SPI register [#11, #12 and #13]. By default, the Control Inputs (INx) are disabled. For more detail see Section 2.7.2: PWM module.

The inputs have internal pull down resistors.

# 2.5 PWMCLK input / wake output pin

# 2.5.1 PWMCLK input

When the device is enabled with the ENABLE pin to logic '1', the pin acts as an input with which the PWM frequency is generated from PWMCLK terminal by the integrated PWM module (see Section 2.7.2: PWM module).

The clock input frequency is the factor 256 of the PWM switching frequency. (f<sub>PWM</sub>=100Hz...400Hz=>f<sub>CLK</sub>=25.6kHz...102.4kHz). Therefore the internal PWM module provides an 8-bit resolution PWM.

The PWM module is disabled in case of PWMCLK failure and the outputs are set according to the OUTxEN control bits (control register #10). The status bit PCLKF is set (Status register #3, bit3). This bit is latched until a Read and Clear command is sent to this register.

A PWMCLK failure is detected when the frequency at the PWMCLK input is lower than 5kHz  $(t_{pos\_lock\_edge} + 1 - t_{pos\_lock\_edge} > 1/5kHz => failure)$ . This failure is reported in the SPI register [#1:D3] (see Section 3.1.6: Status Data Registers).

The input terminal has an internal pull down resistor.

# 2.5.2 WAKE output

When the device is not enabled via the ENABLE, this pin is used as an output to indicate the wake state of the device which is related to the INx pins.

- [0] no wakeup source detected

- [1] INx wakeup source detected or 2sec wake timer running

### 2.6 Limp input

The fail mode (limp home mode) of the component is activated by this digital input port in addition to the internal fail mode detection circuit of the device (see *Section 3.2.5: Fail Mode*).

The limp home mode is activated by a logic [1] signal at the input. During limp home mode the outputs are directly controlled by the inputs IN1, IN2, IN3, IN5, IN6, IN7. and the PWM module is disabled.

The limp input has an internal pull down resistor.

# 2.7 Control, protection and diagnosis

#### 2.7.1 Smart switches and gate drivers

The smart switches are controlled by dedicated gate driver including:

- Output pulse shaping

- Overload protection incl. protection against low resistive short circuit and shorts with line inductance

- Over temperature protection incl. over temperature warning signals

The outputs are switched with active pulse shaping to provide an excellent EMC performance of the system.

Therefore the output current of each driver is monitored by a feedback loop in order to control the switching speed of the output. Thereby a compromise between edge shaping and propagation delay of the switch is necessary to achieve low duty cycle values (3% < dc < 97% @ 250Hz).

#### 2.7.2 PWM module

#### **PWM** control

In order to minimize the microcontroller's work load, a synchronous PWM module is integrated. The frequency and timing is derived from the PWMclock input (see Section 2.5.1: PWMCLK input), the control of the PWM module is provided by SPI and INx (see Section: PWM control)

The smart switches can be controlled in the range of 0%...100% with a resolution of 1/256%. The value 00h in the Individual and Global PWM registers refers to OFF state, the value FFh refers to 255/256 ON state of the switches. The PWM timing includes 4 programmable switching phases (0°, 90°, 180° and 270°). The phase can be controlled individually for each channel depending on the channel control registers [#1~#8 D10~D9]

The synchronization of the switching phases between different devices is provided by the PWMsync bit in Initialisation register [#0:D8].

To guarantee a proper generation and smooth PWM duty cycle change via SPI the duty cycle start point is defined by the internal PWM counter zero crossing. Therefore every SPI programmed duty cycle change and duty cycle source change will not take effect till the PWM counter zero crossing is reached (this strategy is also known as buffered PWM). Setting the output to OFF or 100% ON, the setting will occur immediately and independently from PWM counter.

For generation of output duty cycles close to 100% the pulse skipping feature is integrated (see *Pulse skipping feature*).

The PWM module is disabled in case of

- fail mode (direct drive)

- clock input signal failure (controlled by PWMxEN register)

#### PWM module in normal mode with OUTENx bit = 1

This section describes the PWM control modes for OUT1-8, provided that the corresponding OUTENx bit is set (OUTx is enabled).

If OUTENx bit = 0, the corresponding output is disabled.

#### PWM control modes in normal mode for OUTx (x = 1, 2, 3, 5, 6 or 7)

In normal mode, the state of the OUTx, x=1,2,3,5,6 or 7 is determined by the combinations between INSELx[1:0], PWMSELx[1:0] and the state of INx, provided that OUTENx bit is set to 1.

3 cases must be considered:

- Case 1: direct input INx is disabled (INSELx[1:0] = [0,0])

- Case 2: direct input INx is enabled (INSELx[1:0] ≠ [0,0]) and INx = Low

- Case 3: direct input INx is enabled (INSELx[1:0] ≠ [0,0]) and INx = High

Case 1: INx is disabled: The output behaves according to the *Table 3*.

Table 3. PWM mode selection for OUTx (x = 1, 2, 3, 5, 6 or 7) when INx is disabled

| OUTENx | INx              | INSELx1 | INSELx0 | PWMSELx1 | PWMSELx0 | State of OUTx<br>x = 1, 2, 3, 5, 6 or 7 |

|--------|------------------|---------|---------|----------|----------|-----------------------------------------|

| 1      | X <sup>(1)</sup> | 0       | 0       | 0        | 0        | Individual PWM                          |

| 1      | Х                | 0       | 0       | 0        | 1        | GPWM1                                   |

| 1      | Х                | 0       | 0       | 1        | 0        | GPWM2                                   |

| 1      | Х                | 0       | 0       | 1        | 1        | 100% ON                                 |

<sup>1.</sup> X: do not care.

#### Individual PWM selected:

In this mode the PWM control of the channels is provided individually for each channel by the corresponding channel control register [#1~#8:D7~D0].

GPWM1 selected:

in this mode the PWM control of the switches is provided by the global PWM1 value [#14:D7~D0].

GPWM2 selected:

in this mode the PWM control of the switches is provided by the global PWM2 value [#15:D7~D0].

100% ON selected:

In this mode the output is fully on.

OFF selected:

In this mode the output is OFF.

Case 2: direct input INx is enabled (INSELx[1:0] ≠ [0,0]) and INx = Low

In this case, the state of the output is independent from the settings of PWMSELx[1:0]. It is determined only by setting of INSELx[1:0] according to the *Table 4*.

Table 4. PWM mode selection for OUTx (x = 1, 2, 3, 5, 6 or 7) when INx is enabled and INx = 0

| INx | INSELx1 | INSELx0 | PWMSELx1         | PWMSELx0 | State of OUTx<br>x = 1, 2, 3, 5, 6 or 7 |

|-----|---------|---------|------------------|----------|-----------------------------------------|

| Low | 0       | 1       | X <sup>(1)</sup> | X        | GPWM1                                   |

| Low | 1       | 0       | X                | X        | GPWM2                                   |

| Low | 1       | 1       | X                | X        | OFF                                     |

<sup>1.</sup> X: do not care.

Case 3: direct input INx is enabled (INSELx[1:0]  $\neq$  [0,0]) and INx = High

If the direct input INx is High, the state of the output is independent from the settings of INSELx[1:0]. It is determined only by the setting of PWMSELx[1:0] according to the *Table 5*.

Table 5. PWM mode selection for OUTx (x = 1, 2, 3, 5, 6 or 7) when INx is enabled and INx = 1

| OUTxEN | INx  | INSELx1          | INSELx0 | PWMSELx1 | PWMSELx0 | State of OUTx<br>x = 1, 2, 3, 5, 6 or 7 |

|--------|------|------------------|---------|----------|----------|-----------------------------------------|

| 1      | High | X <sup>(1)</sup> | X       | 0        | 0        | Individual PWM                          |

| 1      | High | Х                | Х       | 0        | 1        | GPWM1                                   |

| 1      | High | Х                | Х       | 1        | 0        | GPWM2                                   |

| 1      | High | Х                | Х       | 1        | 1        | 100% ON                                 |

<sup>1.</sup> X: do not care, provided that INSELx[1:0] is different from [0,0]

Table 6 and Table 7 show some examples of SPI settings resulting in states of OUTx, which are independent (Table 6) or dependent (Table 7) from the levels at INx. Other settings are possible.

Table 6. Examples of settings for INSELx[1:0] and PWMSELx[1:0] resulting in OUTx states, which are independent from INx

| OUTXEN | INx              | INSELx1 | INSELx0 | PWMSELx1 | PWMSELx0 | State of OUTx<br>x = 1, 2, 3, 5, 6 or 7 |

|--------|------------------|---------|---------|----------|----------|-----------------------------------------|

| 0      | X <sup>(1)</sup> | X       | Х       | Х        | Х        | OFF                                     |

| 1      | Х                | 0       | 0       | 1        | 1        | 100% ON                                 |

| 1      | Х                | 0       | 0       | 0        | 0        | Individual PWM                          |

| 1      | Х                | 0       | 1       | 0        | 1        | GPWM1                                   |

| 1      | Х                | 1       | 0       | 1        | 0        | GPWM2                                   |

<sup>1.</sup> X: do not care.

Table 7. Examples of settings for INSELx[1:0] and PWMSELx[1:0] resulting in OUTx states, which are dependent from INx.

| OUTXEN | INSELx1 | INSELx0 | PWMSELx1 | PWMSELx0 | State of OUTx<br>x = 1, 2, 3, 5, 6 or 7 |

|--------|---------|---------|----------|----------|-----------------------------------------|

| 1      | 1       | 1       | 0        | 0        | (Individual PWM) AND (INx)              |

| 1      | 1       | 1       | 0        | 1        | (GPWM1) AND (INx)                       |

| 1      | 1       | 1       | 1        | 0        | (GPWM2) AND (INx)                       |

| 1      | 1       | 1       | 1        | 1        | According to INx                        |

#### PWM control modes in normal mode for OUTx, x = 4 or 8, if OUTENx = 1

OUT4 and OUT8 do not have any direct input or INSELx[1:0] control bits. In normal mode, their behaviour is only determined by the control registers PWMSEL4[1:0] and PWMSEL8[1:0], according to the following table:

Table 8. PWM mode selection for OUT4 and OUT8

| PWMSELx1 | PWMSELx0 | State of OUTx<br>x = 4 or 8 |

|----------|----------|-----------------------------|

| 0        | 0        | Individual PWM              |

| 0        | 1        | GPWM1                       |

| 1        | 0        | GPWM2                       |

| 1        | 1        | 100% ON                     |

#### Pulse skipping feature

Due to the output pulse shaping feature and the thereof resulting propagation delay time of the smart switches, the duty cycle range close to 100% can not be generated by the device. Therefore the pulse skipping feature (PSF) is integrated to generate this output duty cycle range in normal mode.

The pulse skipping consists of fixed duty cycle patterns with 8 PWM cycles.

When the corresponding PSF bit [#1~#8:D8] is set, the PWM values 97.25%...99.61% (C3h...C7h) are generated individually for each channel by modulation of the duty cycle in discrete steps by the pulse skipping logic according to the following table:

Table 9. Duty cycle selection (PSF enabled)

| Duty Cycle<br>(%) | HEX<br>(9bit) | #1  | #2  | #3  | #4  | #5  | #6  | #7  | #8  |

|-------------------|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

| 100.00%           | 0x100         | 256 | 256 | 256 | 256 | 256 | 256 | 256 | 256 |

| 99.61%            | 0x0FF         | 248 | 256 | 256 | 256 | 256 | 256 | 256 | 256 |

| 99.22%            | 0x0FE         | 248 | 256 | 256 | 256 | 248 | 256 | 256 | 256 |

| 98.82%            | 0x0FD         | 248 | 248 | 256 | 256 | 256 | 248 | 256 | 256 |

| 98.43%            | 0x0FC         | 248 | 248 | 256 | 256 | 248 | 248 | 256 | 256 |

| 98.04%            | 0x0FB         | 248 | 248 | 248 | 256 | 256 | 248 | 248 | 256 |

16/60 DocID023902 Rev 4

|                   |               |     |     | •   |     | , , |     |     |     |

|-------------------|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Duty Cycle<br>(%) | HEX<br>(9bit) | #1  | #2  | #3  | #4  | #5  | #6  | #7  | #8  |

| 97.65%            | 0x0FA         | 248 | 248 | 248 | 256 | 248 | 248 | 248 | 256 |

| 97,25%            | 0x0F9         | 248 | 248 | 248 | 248 | 248 | 248 | 248 | 256 |

Table 9. Duty cycle selection (PSF enabled) (continued)

The PSF is started with the next PWM cycle after SPI communication. The start step number can not be guaranteed. In reset condition PSFx = [0], the pulse skipping feature is disabled.

The PSF is not available in Fail Mode.

#### 2.7.3 Overcurrent detection

The over current shutdown threshold (I<sub>OC</sub>) combined with the R<sub>DSON</sub> can be programmed individually for each switch in two different levels by SPI command Mode Control [#9: D7~D0] (see Section 3.1.5: Control Data Registers (CDR)):

- when RON bit is [0] the over current shutdown threshold is 1.5 A and the  $R_{DSON}$  is  $600~\text{m}\Omega$

- when RON bit is [1] the over current shutdown threshold is 750 mA and the R<sub>DSON</sub> is 1  $\Omega$

The setting of the RON bits can be monitored by SDO register Mode Control [#9:D7~D0] (see Section 3.1.6: Status Data Registers).

In case of overcurrent failure the corresponding OUTxEN bit is automatically reset and the corresponding OCx status bit is set. This bit is latched once an OC event is detected.

To reset the diagnosis register, the condition has to be removed and an SPI read and clear operation of the corresponding register has to be performed.

#### 2.7.4 External resistor

To achieve the precise internal slope control and timings, an accurate external resistor is needed.

The resistance has to be 12.4 k $\Omega$  (1% tolerance) connected to GND.

If the resistor is removed or shorted, an RFAIL failure is reported via SPI [#1:D2] (see Section 3.1.6: Status Data Registers).

### 2.7.5 Channel voltage level comparator

In addition to the digital diagnosis a multiplexed channel OUT voltage comparator is implemented. The compared threshold is 5 V.

The channel is selected via the MUXEN and the MUX2:1 bits in the Control Data Register [#0:D7:4]. The OUTL bit can be found in the Status Data Registers [#5,#6,#7,#8:D7].

#### 2.7.6 Device protection

A protection strategy enables light functionality even in case of failures inside the component of the light module.

Therefore the component is protected against

- loss of any supply line

- loss of communication interface and PWMCLK fail

#### Reverse polarity protection

VS has an integrated active reverse polarity protection. VSA, VSB, VSC and VSD have to be protected against reverse polarity by using external protection devices (i.e. series diodes) in the battery supply lines.

#### Loss of supply lines

The device is protected against loss of any supply line.

During loss of

- VS: the device can not drive any loads, and no communication via SPI is possible. The

Device is in Power Down Mode (refer to Figure 4: State diagram). When a valid VS

voltage is applied again, the content of the registers are set to their default value. This

event is reflected in the Reset bit, at the first SPI access.

- VSA, VSB, VSC or VSD: the device can not drive the corresponding load group, but sends UVF\_A / UVF\_B / UVF\_C or UVF\_D flag via SPI to the microcontroller.

- VDD: if the condition VDD < VDDUV is present for more than t<sub>VDDUV</sub>, the device enters in Fail Mode. The refreshing of the WD is disabled as long as VDD < VDDUV.</li>

All I/O lines have to be protected by external series resistors.

#### Loss of communication interface

The following failures are considered as a loss of SPI communication: loss of SCK or CSN, or CSN is stuck to High or Low. These failures are detected by the monitoring of the WD bit. In case of WD time-out, the device enters Fail Mode and the failure is reported by the status bit WDCERR (#1,bit 1).

Note:

A short circuit of CSN to Low for a duration exceeding CSN time-out, additionally causes SDO to go in tri-state, in order to avoid a blocking of the whole SPI bus.

If SDI stuck to High of Low, or if the number of SCK cycles is not a multiple of 16, during a SPI transaction, the device directly enters Fail Mode. Moreover the status register SPIF is set (#1, bit 5).

#### **Logic Input supervision**

The logic inputs are supervised by the device with different check strategies and consequential failures:

Input/Output Signal check strategy System failure reaction No PWM feature **PWM Clock** frequency too low a PWMCLK Fail is reported SPI WD bit time-out Fail Mode SPI SDI, SCK, CSN stuck at High or Low Fail Mode SPI SCK fail Fail Mode

Table 10. Error handling

# 3 SPI interface

A 16 bit SPI interface ( $f_{max} = 2 \text{ MHz}$ ) is used for control and diagnosis of the component.

The SPI offers daisy-chain-capability to provide high data rate, minimum circuit overheads and overall synchronization of multiple PWM modules.

During each SPI cycle a 16 bit word is transferred into the control register of each device and a 16 bit word is received from each device.

The data includes the toggling of a watchdog bit, which indicates the proper operation of the SPI interface. The watchdog bit has to be toggled by every SPI access starting after reset with '0'.

#### 3.1 SPI communication

### 3.1.1 CSN (chip select (active low))

The CSN terminal enables the SPI communication with the microcontroller:

- the SDO output driver is enabled

- the device status data is latched to the output shift registers on the falling edge of the CSN

- the input shift register data is latched into the addressed registers on the rising edge of CSN

CSN has an internal pull up resistor and a CSN timeout is implemented. If CSN is kept low for a duration, which is longer than  $t_{\text{CSN}}$  time-out, the incoming frame is considered as invalid and the SDO goes to tri-state. The CSN time-out avoids that a short circuit of CSN to GND blocks the SPI bus.

### 3.1.2 SCK (serial input clock)

The SCK terminal clocks the internal shift registers of the device.

The SDI terminal accepts data into the input shift register on the falling edge of the SCK signal, while the SDO terminal shifts output data to the SDO line driver on the rising edge of the SCK signal (MCU setting: CPHA = 1; CPOL = 0).

The SCK terminal has to be in logic [0] state whenever CSN makes any transition.

When CSN is logic [1] state, signals at the SCK and SDI inputs are ignored and SDO driver output is in tri-state condition (high impedance). The L99CL01XP requires a number of SCK cycles, which is a multiple of 16, during an SPI transaction. If this condition is not met, the device enters Fail Mode.

SCK has an internal pull down resistor.

#### 3.1.3 SDI (serial data input)

The SDI pin is the data input terminal of the SPI communication interface.

The input has an internal pull down resistor. Writing all [0] or all [1] to SDI within one SPI frame will generate an SPI fail (stuck @ error).

The implemented SPI requires a 16 bit stream of serial data, starting with D15 and ending with D0.

### 3.1.4 SDO (serial data output)

The SDO pin is the data output terminal of the SPI communication interface.

The SDO terminal is in tri-state condition unless CSN input is in logic [0] state. When CSN is in logic [0] state, the data from the output shift registers is sent via the SDO pin.

The SDO terminal changes the state at the rising edge of the SCK input and reads out on the falling edge of SCLK.

### 3.1.5 Control Data Registers (CDR)

The data sent to the device will be latched into the internal Control Registers with the rising edge of CSN after a valid SPI cycle is performed.

The written data can be read back by setting the RAMREAD bit D9 in the Initialization register #0. After Reset all registers are by default [0] (except SDOA0 is [1]).

CDR base address = 0x00h

The CDR register are shown in Table 11: CDR registers

Table 11. CDR registers

| Register                                   | Address offset | Reset value |

|--------------------------------------------|----------------|-------------|

| Initialization Register                    | 0x00h          | 0x0001h     |

| Address #1-#8 CHx control                  |                |             |

| Address #1 CHx control                     | 0x01h          | 0x1000h     |

| Address #2 CHx control                     | 0x02h          | 0x2000h     |

| Address #3 CHx control                     | 0x03h          | 0x3000h     |

| Address #4 CHx control                     | 0x04h          | 0x4000h     |

| Address #5 CHx control                     | 0x05h          | 0x5000h     |

| Address #6 CHx control                     | 0x06h          | 0x6000h     |

| Address #7 CHx control                     | 0x07h          | 0x7000h     |

| Address #8 CHx control                     | 0x08h          | 0x8000h     |

| Address #9 mode control                    | 0x09h          | 0x9000h     |

| Address #10 OUT enable                     | 0x0Ah          | 0xA001h     |

| Address #11 PWMSEL / INSEL CH1 + CH2       | 0x0Bh          | 0xB000h     |

| Address #12 PWMSEL / INSEL CH3 + CH4 + CH5 | 0x0Ch          | 0xC001h     |

| Address #13 PWMSEL / INSEL CH6 + CH7 + CH8 | 0x0Dh          | 0xD000h     |

| Address #14 Global PWM1                    | 0x0Eh          | 0xE000h     |

| Address #15 Global PWM2                    | 0x0Fh          | 0xF000h     |

#### **Initialization Register**

| 15 | 14  | 13   | 12 | 11  | 10       | 9        | 8       | 7     | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----|-----|------|----|-----|----------|----------|---------|-------|------|------|------|------|------|------|------|

|    | Add | ress |    | WD  | NO CLEAR | RAM READ | PWMsync | MUXEN | MUX2 | MUX1 | MUX0 | SOA3 | SOA2 | SOA1 | SOA0 |

|    | F   | 3    |    | R/W | R/W      | R/W      | R/W     | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

Address: Base address + 0x00h

**Type:** R, R/W **Reset:** 0x0001h

Note: Writing all [0] to this register will generate a SPI fail (stuck @ '0').

Bit 15:12 Address

Bit 11 WD: Watchdog toggle bit (75ms, start with [0] after Reset, toggled with every SPI access)

Bit 10 NOCLEAR: With this bit set to:

0: every read access clears the read out status bits

1: any reported status from the read and clear flags are not cleared by a read The clear of the read and clear flags will be re-enabled by writing a [0] to this bit.

Bit 9 READRAM: With this bit set to:

0: the addressed status data register (see Section 3.1.4: SDO (serial data output)) is sent back via SDO

1: the addressed control data register is sent back via SDO. This is to verify the written data in the device.

Note: The read back of the Status Data Registers will be re-enabled by writing a [0] to this bit.

Bit 8 PWMsync: internal PWM counter reset. Writing a '1' to this Register will reset the internal PWM counter after valid SPI command and CSN high. This bit is automatically reset after synchronization.

Bit 7 MUXEN: Enable current sense output and the OUT voltage level comparator

0: CS pin disabled / OUT voltage comparator disabled (default)

1: CS pin enable / OUT voltage comparator enabled (see MUX[2:0]) setting

Bit 6:4 MUX[2:0]: Binary decoded selection of current sense output and the OUT voltage level comparator

000: Channel 1 selected (default

001: Channel 2 selected

010: Channel 3 selected

011: Channel 4 selected

100: Channel 5 selected

101: Channel 6 selected

110: Channel 7 selected

111: Channel 8 selected

Bit 3:0 SDOA[3:0]: Address of next SDO data word (also see READRAM bit)

0000: READRAM = 0: Address #1 selected, else Address #0

0001: Address #1 selected (default)

0010: Address #2 selected

0011: Address #3 selected

0100: Address #4 selected

0101: Address #5 selected

0110: Address #6 selected

0111: Address #7 selected

1000: Address #8 selected

1001: Address #9 selected

1010: Address #10 selected

1011: Address #11 selected

1100: Address #12 selected

1101: Address #13 selected

1110: Address #14 selected

1111: Address #15 selected

#### Address #1-#8 CHx control

| 15 | 14   | 13  | 12 | 11  | 10   | 9    | 8    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----|------|-----|----|-----|------|------|------|-------|-------|-------|-------|-------|-------|-------|-------|

|    | Addı | ess |    | WD  | PHx1 | PHx0 | PSFx | IxDC7 | IxDC6 | IxDC5 | IxDC4 | IxDC3 | IxDC2 | IxDC1 | IxDC0 |

|    | F    | }   |    | R/W | R/W  | R/W  | R/W  | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

**Address:** Base address + 0x0Yh (Y = 0x01h to 0x08h)

Type: R, R/W

Reset: 0xY000h

Bit 15:12 Address

Bit 11 WD: Watchdog toggle bit (75ms, start with [0] after Reset, toggled with every SPI access)

Bit 10:9 PHx[1:0]: Binary decoded PWM phase shift selection (0°, 90°, 180°, 270°)

00: 0° Phase (default)

01: 90° Phase 10: 180° Phase 11: 270° Phase

Bit 8 PSFx: Pulse skipping enable

0: disabled1: enabled

Bit 7:0 DCx7:0: Channel individual duty cycle programmable from 0x00 to 0xFF

DutyCycle value in % DC[%] = value\*100/256

0x00h: 0% 0x01h: 0.39% 0x02h: 0.78%

....

0xFFh: 99.61%

#### Address #9 mode control

|   | 15 | 14  | 13   | 12 | 11  | 10  | 9 | 8     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---|----|-----|------|----|-----|-----|---|-------|------|------|------|------|------|------|------|------|

|   |    | Add | ress |    | WD  | res | 0 | OCBLN | RON8 | RON7 | RON6 | RON5 | RON4 | RON3 | RON2 | RON1 |

| , |    | F   | 3    |    | R/W | R   | R | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

**Address:** Base address + 0x09h

Type: R, R/W

Reset: 0x9000h

Bit 15:12 Address

Bit 11 WD: Watchdog toggle bit (75ms, start with [0] after Reset, toggled with every SPI access)

Bit 10 Reserved bits have to be written with 0

Bit 9 0

Bit 8 OCBLN: OC Blanking disable

0: OC blanking = 150us blanking after OUTx on enabled (default)

1: OC blanking = 150us blanking after OUTx on disabled

Bit 7:0 RON8:1: Defines over current threshold and R<sub>DSON</sub> value

0: OC threshold = 1.5A and  $R_{DSON}$  = 600m $\Omega$  (OL high threshold) (default)

1: OC threshold = 750mA and  $R_{\mbox{\footnotesize DSON}}$  =  $1\Omega$  (OL low threshold)

#### Address #10 OUT enable

| 15 | 14  | 13   | 12 | 11  | 10  | 9   | 8   | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|----|-----|------|----|-----|-----|-----|-----|--------|--------|--------|--------|--------|--------|--------|--------|

|    | Add | ress |    | WD  | res | res | res | OUTBEN | OUT7EN | OUTGEN | OUTSEN | OUT4EN | OUT3EN | OUT2EN | OUT1EN |

|    | -   | 2    |    | R/W | B   | R   | R   | R/W    | B/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

Address: Base address + 0x0Ah

Type: R, R/W

Reset: 0xA001h

Bit 15:12 Address

Bit 11 WD: Watchdog toggle bit (75ms, start with [0] after Reset, toggled with every SPI access)

Bit 10:8 Reserved bits have to be written with 0

Bit 7:0 OUTEN8:1: Enables the Output in Normal Mode. In case of OVx, UVx, TSDx or OCx the corresponding bits are cleared and therefore the OUTx is switched off.

0: disabled (default)

1: enabled (OUT corresponding INSELx, PWMSELx and INx)

#### Address #11 PWMSEL / INSEL CH1 + CH2

| 15 | 14  | 13   | 12 | 11  | 10  | 9   | 8   | 7       | 6       | 5        | 4        | 3       | 2       | 1        | 0        |  |

|----|-----|------|----|-----|-----|-----|-----|---------|---------|----------|----------|---------|---------|----------|----------|--|

|    | Add | ress |    | WD  | res | res | res | INSEL21 | INSEL20 | PWMSEL21 | PWMSEL20 | INSEL11 | INSEL10 | PWMSEL11 | PWMSEL10 |  |

|    | F   | 3    |    | R/W | R   | R   | R   | R/W     | R/W     | R/W      | R/W      | R/W     | R/W     | R/W      | R/W      |  |

Address: Base address + 0x0Bh

Type: R, R/W

Reset: 0xB000h

Bit 15:12 Address

Bit 11 WD: Watchdog toggle bit (75ms, start with [0] after Reset, toggled with every SPI access)

Bit 10:8 Reserved bits have to be written with 0

Bit 7:6 - Bit 3:2 INSELx[1:0]: INx function selector see Section 2.7.2: PWM module

Bit 5:4 - Bit 1:0 PWMSELx[1:0]: PWM function selector see Section 2.7.2: PWM module

#### Address #12 PWMSEL / INSEL CH3 + CH4 + CH5

| 15 | 14  | 13   | 12 | 11  | 10  | 9       | 8       | 7        | 6        | 5        | 4        | 3       | 2       | 1        | 0        |

|----|-----|------|----|-----|-----|---------|---------|----------|----------|----------|----------|---------|---------|----------|----------|

|    | Add | ress |    | WD  | res | INSEL51 | INSEL50 | PWMSEL51 | PWMSEL50 | PWMSEL41 | PWMSEL40 | INSEL31 | INSEL30 | PWMSEL31 | PWMSEL30 |

|    | -   | ,    |    | D/M | В   | D/M     | D AA/   | D AA/    | D/M      | D/M      | D AAA    | D/M     | D/M     | D/M      | D/M      |

Address: Base address + 0x0Ch

Type: R, R/W

Reset: 0xC001h

Bit 15:12 Address

Bit 11 WD: Watchdog toggle bit (75ms, start with [0] after Reset, toggled with every SPI access)

Bit 10 Reserved bits have to be written with 0

Bit 9:8 - Bit 3:2 INSELx[1:0]: INx function selector see Section 2.7.2: PWM module

Bit 7:4 - Bit 1:0 PWMSELx[1:0]: PWM function selector see Section 2.7.2: PWM module

#### Address #13 PWMSEL / INSEL CH6 + CH7 + CH8

| 15 | 14  | 13   | 12 | 11  | 10  | 9        | 8        | 7       | 6       | 5        | 4        | 3       | 2       | 1        | 0        |

|----|-----|------|----|-----|-----|----------|----------|---------|---------|----------|----------|---------|---------|----------|----------|

|    | Add | ress |    | WD  | res | PWMSEL81 | PWMSEL80 | INSEL71 | INSEL70 | PWMSEL71 | PWMSEL70 | INSEL61 | INSEL60 | PWMSEL61 | PWMSEL60 |

|    | F   | 3    |    | R/W | R   | R/W      | R/W      | R/W     | R/W     | R/W      | R/W      | R/W     | R/W     | R/W      | R/W      |

**Address:** Base address + 0x0Dh

Type: R, R/W

Reset: 0xD000h

Bit 15:12 Address

Bit 11 WD: Watchdog toggle bit (75ms, start with [0] after Reset, toggled with every SPI access)

Bit 10 Reserved bits have to be written with 0

Bit 7:6 - Bit 3:2 See Section 2.7.2: PWM module

Bit 5:4 - Bit 1:0 See Section 2.7.2: PWM module

#### Address #14 Global PWM1

| 15 | 14  | 13   | 12 | 11  | 10 | 9 | 8 | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----|-----|------|----|-----|----|---|---|-------|-------|-------|-------|-------|-------|-------|-------|

|    | Add | ress |    | WD  | 0  | 0 | 0 | G1DC7 | G1DC6 | G1DC5 | G1DC4 | G1DC3 | G1DC2 | G1DC1 | G1DC0 |

|    | F   | 3    |    | R/W | R  | R | R | R/W   |

Address: Base address + 0x0Eh

Type: R, R/W Reset: 0xE000h

Bit 15:12 Address

Bit 11 Watchdog toggle bit (75ms, start with [0] after Reset, toggled with every SPI access)

Bit 10:8 0

G1DCx: Global 1 duty cycle programmable from 0x00 to 0xFF:

DutyCycle value in %; DC[%] = value \* 100/256

0x00h: 0%

Bit 7:0 0x01h: 0.39%

0x02h: 0.78%

....

0xFFh: 99.61%

#### Address #15 Global PWM2

| 15 | 14   | 13   | 12 | 11  | 10 | 9 | 8 | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----|------|------|----|-----|----|---|---|-------|-------|-------|-------|-------|-------|-------|-------|

|    | Addı | ress |    | WD  | 0  | 0 | 0 | G2DC7 | G2DC6 | G2DC5 | G2DC4 | G2DC3 | G2DC2 | G2DC1 | G2DC0 |

|    | F    | 3    |    | R/W | R  | R | R | R/W   |

Note: Writing all [1] to this register will generate a SPI fail (stuck @ '1').

Address: Base address + 0x0Fh

Type: R, R/W

Reset: 0xF000h

Bit 15:12 Address

Bit 11 WD: Watchdog toggle bit (75ms, start with [0] after Reset, toggled with every SPI access)

Bit 10:8 0

Bit 7:0 G2DCx: Global 2 duty cycle programmable from 0x00 to 0xFF

DutyCycle value in %; DC[%] = value \* 100/256

0x00h: 0% 0x01h: 0.39% 0x02h: 0.78%

...

0xFFh: 99.61%

All SDI input data values, are latched into the registers at the rising edge of CSN if the communication is valid (multiple of 16 SCKs and data consistency check).

Table 12. Control Data Register

| Dogistor                          |    |     | Addre | SS  |     |     |          |          |          |              | C            | Control data |              |         |         |          |          |

|-----------------------------------|----|-----|-------|-----|-----|-----|----------|----------|----------|--------------|--------------|--------------|--------------|---------|---------|----------|----------|

| Register                          | #  | D15 | D14   | D13 | D12 | D11 | D10      | D9       | D8       | D7           | D6           | D5           | D4           | D3      | D2      | D1       | D0       |

| Initialization                    | 0  | 0   | 0     | 0   | 0   | WD  | NO CLEAR | RAM READ | PWMsync  | MUXEN        | MUX2         | MUX1         | MUX0         | SOA3    | SOA2    | SOA1     | SOA0     |

| CH1 control                       | 1  | 0   | 0     | 0   | 1   | WD  | PH11     | PH10     | PSF1     | I1DC7        | I1DC6        | I1DC5        | I1DC4        | I1DC3   | I1DC2   | I1DC1    | I1DC0    |

| CH2 control                       | 2  | 0   | 0     | 1   | 0   | WD  | PH21     | PH20     | PSF2     | I2DC7        | I2DC6        | I2DC5        | I2DC4        | I2DC3   | I2DC2   | I2DC1    | I2DC0    |

| CH3 control                       | 3  | 0   | 0     | 1   | 1   | WD  | PH31     | PH30     | PSF3     | I3DC7        | I3DC6        | I3DC5        | I3DC4        | I3DC3   | I3DC2   | I3DC1    | I3DC0    |

| CH4 control                       | 4  | 0   | 1     | 0   | 0   | WD  | PH41     | PH40     | PSF4     | I4DC7        | I4DC6        | I4DC5        | I4DC4        | I4DC3   | I4DC2   | I4DC1    | I4DC0    |

| CH5 control                       | 5  | 0   | 1     | 0   | 1   | WD  | PH51     | PH50     | PSF5     | I5DC7        | I5DC6        | I5DC5        | I5DC4        | I5DC3   | I5DC2   | I5DC1    | I5DC0    |

| CH6 control                       | 6  | 0   | 1     | 1   | 0   | WD  | PH61     | PH60     | PSF6     | I6DC7        | I6DC6        | I6DC5        | I6DC4        | I6DC3   | I6DC2   | I6DC1    | I6DC0    |

| CH7 control                       | 7  | 0   | 1     | 1   | 1   | WD  | PH71     | PH70     | PSF7     | I7DC7        | I7DC6        | I7DC5        | I7DC4        | I7DC3   | I7DC2   | I7DC1    | I7DC0    |

| CH8 control                       | 8  | 1   | 0     | 0   | 0   | WD  | PH81     | PH80     | PSF8     | I8DC7        | I8DC6        | I8DC5        | I8DC4        | I8DC3   | I8DC2   | I8DC1    | I8DC0    |

| Mode control                      | 9  | 1   | 0     | 0   | 1   | WD  | res      | 0        | OCBLN    | RON8         | RON7         | RON6         | RON5         | RON4    | RON3    | RON2     | RON1     |

| OUT enable                        | 10 | 1   | 0     | 1   | 0   | WD  | res      | res      | res      | OUT8EN       | OUT7EN       | OUT6EN       | OUT5EN       | OUT4EN  | OUT3EN  | OUT2EN   | OUT1EN   |

| PWMSEL / INSEL<br>CH1 + CH2       | 11 | 1   | 0     | 1   | 1   | WD  | res      | res      | res      | INSEL21      | INSEL20      | PWMSEL21     | PWM<br>SEL20 | INSEL11 | INSEL10 | PWMSEL11 | PWMSEL10 |

| PWMSEL / INSEL<br>CH3 + CH4 + CH5 | 12 | 1   | 1     | 0   | 0   | WD  | res      | INSEL51  | INSEL50  | PWM<br>SEL51 | PWM<br>SEL50 | PWMSEL41     | PWMSEL40     | INSEL31 | INSEL30 | PWMSEL31 | PWMSEL30 |

| PWMSEL / INSEL<br>CH6 + CH7 + CH8 | 13 | 1   | 1     | 0   | 1   | WD  | res      | PWMSEL81 | PWMSEL80 | INSEL71      | INSEL70      | PWMSEL71     | PWMSEL70     | INSEL61 | INSEL60 | PWMSEL61 | PWMSEL60 |

| Global PWM1                       | 14 | 1   | 1     | 1   | 0   | WD  | 0        | 0        | 0        | G1DC7        | G1DC6        | G1DC5        | G1DC4        | G1DC3   | G1DC2   | G1DC1    | G1DC0    |

| Global PWM2                       | 15 | 1   | 1     | 1   | 1   | WD  | 0        | 0        | 0        | G2DC7        | G2DC6        | G2DC5        | G2DC4        | G2DC3   | G2DC2   | G2DC1    | G2DC0    |

DocID023902 Rev 4

#### 3.1.6 **Status Data Registers**

By accessing the Status Registers, the read and clear flags are cleared after rising CSN edge. All read and clear flags are latched and keep the status till read out. All other flags report the actual status and are therefore not clearable. By setting the NOCLEAR flag D10 in Initialisation register #0, this automatic clear is prohibited.

If a flag is set during read out phase the flag is latched and will be reported with the next read.

The SPI output delivers the data set programmed by the bits D9 (READRAM option) and D3:0 (SDOA3:0) inside the control data register [#0] of the SPI:

SDR base address = 0x00h

The SDR register are shown in *Table 13: SDR registers*

Table 13. SDR registers

| Register                     | Address offset | Reset value |

|------------------------------|----------------|-------------|

| Address #0                   | 0x00h          | 0x00h       |

| Address #1 Device Status 1   | 0x01h          | 0x00h       |

| Address #2 Device Status 2   | 0x02h          | 0x00h       |

| Address #3 Device Status 3   | 0x03h          | 0x00h       |

| Address #4 Quick Status      | 0x04h          | 0x00h       |

| Address #5-#8 Status CHx+CHy |                |             |

| Address #5 Status CH1+CH2    | 0x05h          | 0x00h       |

| Address #6 Status CH31+CH4   | 0x06h          | 0x00h       |

| Address #7 Status CH5+CH6    | 0x07h          | 0x00h       |

| Address #8 Status CH7+CH8    | 0x08h          | 0x00h       |

| Address #9 Mode Control      | 0x09h          | 0x00h       |

| Address #10 OUT enable       | 0x0Ah          | 0x00h       |

| Address #11 INx Status       | 0x0Bh          | 0x00h       |

| Address #12 Silicon Version  | 0x0Ch          | 0x01h       |

#### Address #0

A read access to Status Register #0 is not allowed. It is interpreted as SDO is shorted to "0" and lead the device to enter Fail Mode

#### Address #1 Device Status 1

| • | 15 | 14  | 13   | 12 | 11       | 10  | 9                | 8   | 7          | 6    | 5    | 4    | 3     | 2     | 1      | 0    |

|---|----|-----|------|----|----------|-----|------------------|-----|------------|------|------|------|-------|-------|--------|------|

|   |    | Add | ress |    | FAILSAFE | SVF | X <sup>(1)</sup> | DSF | CHIP RESET | VDDF | SPIF | LIMP | PCLKF | RFAIL | WDCERR | WDC0 |

|   | R  |     |      |    | R/W      | R/W | R/W              | R/W | R/W        | R/W  | R/W  | R/W  | R/W   | R/W   | R/W    | R/W  |

1. X: do not care

Address: Base address + 0x01h

**Type:** R, R/W **Reset:** 0x00h

Bit 15:12 Address

Bit 11 FAILSAFE:

0: Device is in Normal Mode

1: Device is in Fail Mode (DirectDrive enabled)

Bit 10 SVF: logical OR combination of all OV, UV, OVx, UVx

0: supply voltage in operating range

1: supply voltage failure

Bit 9 X: do not care

Bit 8 DSF: logical OR combination of VDDF or SPIF or LIMP or PCLKF or RFAIL or WDCERR

0: no fail detected

1: fail detected

Bit 7 CHIP RESET: indicates if all registers are previously reset, cleared with the first SPI read (by default #1)

0: device has not been previously reset

1: all registers are in reset state (cleared with first valid SPI command after reset)

Bit 6 VDDF: VDD fail occurred

0: no VDD fail detected

1: VDD fail detected

Bit 5 SPIF: SPI clock fail or SDI stuck @ detected

0: no SPI fail detected

1: SPI fail detected (SPI clock cycles during a transaction is not a multiple of 16, stuck @

0 or 1 at SDI detected)

Bit 4 LIMP: LIMP pin high detected

0: no LIMP high detected

1: LIMP high detected

Bit 3 PCLKF: PWMCLK fail detected

0: no PWMCLK fail detected

1: PWMCLK fail detected

Bit 2 RFAIL: External R failure detected

0: R external connected correctly

1: R external fail detected

Bit 1 WDCERR: WDC time-out or WD toggle bit fail detected

0: no watchdog failure

1: watchdog fail detected

Bit 0 WDC0: WDC 50% flag

0: watchdog 50% time-out not reached

1: watchdog 50% time-out reached

30/60 DocID023902 Rev 4

#### Address #2 Device Status 2

| 15 | 14   | 13   | 12 | 11       | 10  | 9                | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----|------|------|----|----------|-----|------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|    | Addı | ress |    | FAILSAFE | SVF | X <sup>(1)</sup> | DSF | 0   | 0   | 0   | 0   | TSD | TW  | OVF | UVF |

| R  |      |      |    | R/W      | R/W | R                | R/W |

1. X: do not care

Address: Base address + 0x02h

**Type:** R, R/W **Reset:** 0x00h

Bit 15:12 Address

Bit 11 FAILSAFE:

0: Device is in Normal Mode

1: Device is in Fail Mode (DirectDrive enabled)

Bit 10 SVF: Logical OR combination of all OV, UV, OVx, UVx

0: supply voltage in operating range

1: supply voltage failure

Bit 9 X: do not care

Bit 8 DSF: Logical OR combination of VDDF or SPIF or LIMP or PCLKF or RFAIL or

**WDCERR**

0: no fail detected

1: fail detected

Bit 7:4 0

Bit 2 TW: Logical OR combination of all TWx

0: no thermal warning detected

1: thermal warning detected

Bit 1 OVF: OverVoltage at VS detected

0: no over voltage detected

1: over voltage detected (OVF is latched once an overvoltage on VS is detected)

Bit 0 UVF: UnderVoltage at VS detected

0: no under voltage detected

1: under voltage detected (UVF is latched once an undervoltage on VS is detected)

#### Address #3 Device Status 3

| 15 | 14  | 13   | 12 | 11       | 10  | 9                | 8   | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----|-----|------|----|----------|-----|------------------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

|    | Add | ress |    | FAILSAFE | SVF | X <sup>(1)</sup> | DSF | OVF_A | UVF_A | OVF_B | UVF_B | OVF_C | UVF_C | OVF_D | UVF_D |

| R  |     |      |    | R/W      | R/W | R                | R/W | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

1. X: do not care

Address: Base address + 0x03h

**Type:** R, R/W **Reset:** 0x00h

Bit 15:12 Address

Bit 11 FAILSAFE:

0: Device is in Normal Mode

1: Device is in Fail Mode (DirectDrive enabled)

Bit 10 SVF: Logical OR combination of all OVx, UVx

0: supply voltage in operating range

1: supply voltage failure

Bit 9 X: do not care

Bit 8 DSF: Logical OR combination of VDDF or SPIF or LIMP or PCLKF or RFAIL or WDCERR

0: no fail detected

1: fail detected

Bit 7 OVF\_A<sup>(1)</sup>: OverVoltage at VSA detected

0: no over voltage detected

1: over voltage detected, OUT1EN and OUT2EN are cleared automatically (channel OFF)

Bit 6 UVF\_A<sup>(1)</sup>: UnderVoltage at VSA detected

0: no under voltage detected

1: under voltage detected, OUT1EN and OUT2EN are cleared automatically (channel OFF)

Bit 5 OVF\_B<sup>(1)</sup>: OverVoltage at VSB detected

0: no over voltage detected

1: over voltage detected, OUT3EN and OUT4EN are cleared automatically (channel OFF)

Bit 4 UVF\_B<sup>(1)</sup>: UnderVoltage at VSB detected

0: no under voltage detected

1: under voltage detected, OUT3EN and OUT4EN are cleared automatically (channel OFF)

Bit 3 OVF\_C<sup>(1)</sup>: OverVoltage at VSC detected

0: no over voltage detected

1: over voltage detected, OUT5EN and OUT6EN are cleared automatically (channel OFF)

32/60 DocID023902 Rev 4

Bit 2 UVF\_C<sup>(1)</sup>: UnderVoltage at VSC detected

0: no under voltage detected

1: under voltage detected, OUT5EN and OUT6EN are cleared automatically (channel OFF)

Bit 1 OVF\_D<sup>(1)</sup>: OverVoltage at VSD detected

0: no over voltage detected

1: over voltage detected, OUT7EN and OUT8EN are cleared automatically (channel OFF)

Bit 0 UVF\_D<sup>(1)</sup>: UnderVoltage at VSD detected

0: no under voltage detected

1: under voltage detected, OUT7EN and OUT8EN are cleared automatically (channel OFF)

1. OVF\_X and UVF\_X are latched, once an overvoltage, respectively, and undervoltage is detected on VS\_X.

#### Address #4 Quick Status

| 15 | 14   | 13   | 12 | 11       | 10  | 9                | 8   | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----|------|------|----|----------|-----|------------------|-----|------|------|------|------|------|------|------|------|

|    | Addı | ress |    | FAILSAFE | SVF | X <sup>(1)</sup> | DSF | QSF8 | QSF7 | QSF6 | QSF5 | QSF4 | QSF3 | QSF2 | QSF1 |

|    |      |      |    | R/W      | R/W | R                | R/W | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

1. X: do not care

Address: Base address + 0x04h

**Type:** R, R/W **Reset:** 0x00h

Bit 15:12 Address

Bit 11 FAILSAFE:

0: Device is in Normal Mode

1: Device is in Fail Mode (DirectDrive enabled)

Bit 10 SVF: Logical OR combination of all OVx, UVx

0: supply voltage in operating range

1: supply voltage failure

Bit 9 X: do not care

Bit 8 DSF: logical OR combination of VDDF or SPIF or LIMP or PCLKF or RFAIL or WDCERR

0: no fail detected

1: fail detected

Bit 7:0 QSFx[7:0]: channel specific logical OR combination of TSDx or TWx\_th2 or TWx\_th1 or OCx or OLx

0: no fail detected

1: fail detected

#### Address #5-#8 Status CHx+CHy

| 15 | 14  | 13   | 12 | 11       | 10  | 9                | 8   | 7    | 6     | 5       | 4       | 3   | 2                | 1   | 0                |

|----|-----|------|----|----------|-----|------------------|-----|------|-------|---------|---------|-----|------------------|-----|------------------|

|    | Add | ress |    | FAILSAFE | SVF | X <sup>(1)</sup> | DSF | OUTL | TSDxy | TWxyth2 | TWxyth1 | ОСу | X <sup>(1)</sup> | OCx | X <sup>(1)</sup> |

|    | R   |      |    | R/W      | R/W | В                | R/W | В/W  | R/W   | R/W     | В/W     | R/W | R/W              | R/W | R/M              |

1. X: do not care

**Address:** Base address + 0x0Yh (Y = 0x05 to 0x08h)

**Type:** R, R/W **Reset:** 0x00h

Bit 15:12 Address

Bit 11 FAILSAFE:

0: Device is in Normal Mode

1: Device is in Fail Mode (DirectDrive enabled)

Bit 10 SVF: Logical OR combination of all OVx, UVx

0: supply voltage in operating range

1: supply voltage failure

Bit 9 X: do not care

Bit 8 DSF: logical OR combination of VDDF or SPIF or LIMP or PCLKF or RFAIL or WDCERR

0: no fail detected

1: fail detected

Bit 7 OUTL: logical read back value of selected [#0:D7~D4] OUTx channel. This information can be used to distinguish between open load and short to VSx in OFF state.

0: OUTx is low

1: OUTx is high