### **General Description**

The DS8007A multiprotocol dual smart card interface is an automotive grade, low-cost, dual smart card reader interface supporting all ISO 7816, EMV™, and GSM11-11 requirements. Through its 8-bit parallel bus and dedicated address selects (AD3-AD0), the DS8007A can easily and directly connect to the nonmultiplexed bytewide bus of a Maxim secure microcontroller. Optionally, the parallel bus can be multiplexed to allow direct access to the multiplexed bus of an 80C51-compatible microcontroller through MOVX memory addressing.

One integrated UART is multiplexed among the interfaces to allow high-speed automatic smart card processing with each card-possessing, independent, variable, baud-rate capability. The card interface is controlled by internal sequencers that support automatic activation and deactivation sequencing, handling all actions required for T = 0, T = 1, and synchronous protocols. Emergency deactivation is also supported in case of supply dropout. A third card is supported through the auxiliary I/O. The same set of I/O can optionally be used as additional serial interface for the UART.

The DS8007A provides all electrical signals necessary to interface with two smart cards. The integrated voltage converter ensures full cross-compatibility between 1.8V/3V/5V cards and a 1.8V/3V/5V environment, and allows operation within a 2.7V to 6V supply voltage range. The standard DS8007 revision is available for nonautomotive applications.

### **Applications**

Banking Applications (Point-of-Sale Terminals, Debit/Credit Payment Terminals, PIN Pads, Automated Teller Machines)

Telecommunications

Pay Television

Access Control

### **Ordering Information**

| PART         | TEMP RANGE      | SMART<br>CARDS<br>SUPPORTED | PIN-<br>PACKAGE |

|--------------|-----------------|-----------------------------|-----------------|

| DS8007A-EAG+ | -40°C to +125°C | 2 + auxiliary               | 48 LQFP         |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant device.

EMV is a trademark owned by EMVCo LLC.

#### **Features**

- Complete Interface/Control for Two Separate **Smart Card Devices**

- ♦ 8kV (min) ESD Protection on Card Interfaces

- ♦ Internal IC Card Supply Voltage Generation 5.0V ±5%, 65mA (max)  $3.0V \pm 8\%$ , 50mA (max)1.8V ±10%, 30mA (max)

- ♦ Automatic Card Activation, Deactivation, and Data **Communication Controlled by Dedicated Internal** Sequencer

- ♦ Host Interface Through an 8-Bit Parallel Bus (User-Selectable Multiplexed or Nonmultiplexed Modes)

- **Chip Select and Three-State Bus Allow Multiple Devices (Card Readers and Memories) on Bus**

- ♦ 8-Character Receive FIFO with Optional **Programmable Depth/Threshold**

- ♦ I/O Interface Pin to External ISO 7816 UART

- **♦** Separate Card Clock Generation (Up to 10MHz) with 2x Frequency Doubling

- ♦ Selectable Card Clock Stop High, Stop Low, or Internally Generated 1.25MHz (for Card Power-Down)

- **♦** EMV-Certified Reference Design and Evaluation Kit Available (DS8007-KIT)

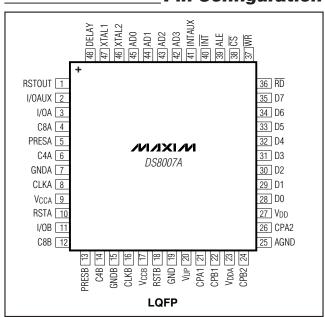

### Pin Configuration

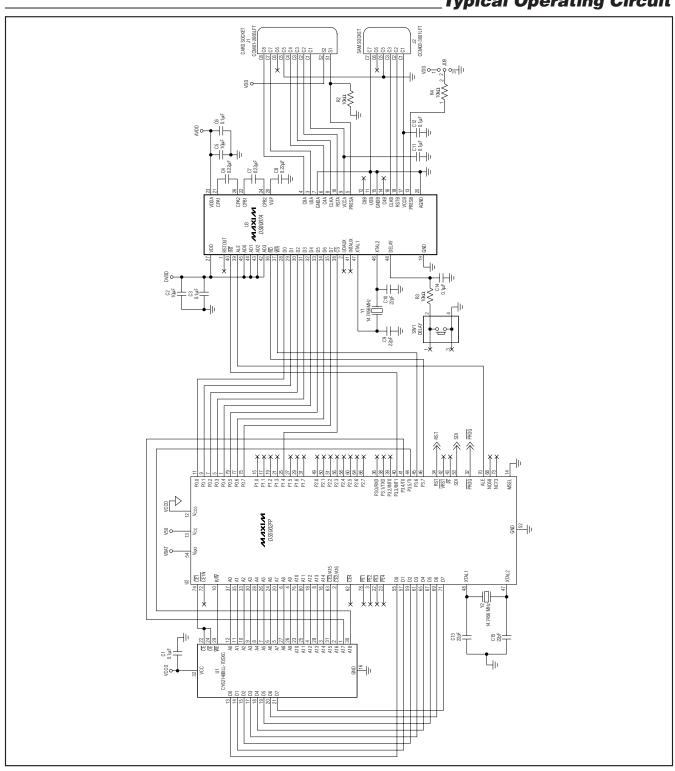

Typical Operating Circuit appears at end of data sheet.

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: www.maxim-ic.com/errata.

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on V <sub>DD</sub> Relative to Ground0.5V to +6.5V  | Maximum Junction Temperature+150°C                      |

|-------------------------------------------------------------------|---------------------------------------------------------|

| Voltage Range on V <sub>DDA</sub> Relative to Ground0.5V to +6.5V | Maximum Power Dissipation (T <sub>A</sub> = -25°C)900mW |

| Voltage Range on Any Pin Relative to Ground                       | Storage Temperature Range55°C to +150°C                 |

| Pins CPA1, CPA2, CPB1, CPB2, and V <sub>UP</sub> 0.5V to +7.5V    | Soldering TemperatureRefer to the IPC/JEDEC             |

| All Other Pins0.5V to (V <sub>DD</sub> + 0.5V)                    | J-STD-020 Specification                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(V<sub>DD</sub> = +3.3V, V<sub>DDA</sub> = +3.3V, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                   |                                            | SYMBOL                  | CONDITIONS                                                                                                                                                | MIN                      | TYP  | MAX                   | UNITS  |

|---------------------------------------------|--------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-----------------------|--------|

| Digital Supply                              | Digital Supply Voltage                     |                         |                                                                                                                                                           | 2.7                      |      | 6.0                   | V      |

| Step-Up Conve<br>Voltage                    | Step-Up Converter Supply<br>Voltage        |                         |                                                                                                                                                           | V <sub>DD</sub>          |      | 6.0                   | V      |

| Power-Down                                  | Cards Inactive                             | - I <sub>PD</sub>       | f <sub>XTAL</sub> = 0MHz                                                                                                                                  |                          |      | 0.9                   | mA     |

| V <sub>DD</sub> Current                     | Cards Active                               | IPD                     | $f_{XTAL} = 0MHz, f_{CLK} = 0MHz, V_{CCX} = 5V$                                                                                                           |                          |      | 2.2                   | IIIA   |

| Sleep Mode V <sub>E</sub><br>(Cards Active) | DD Current                                 | ISTOP                   | f <sub>CLK</sub> = 0MHz, V <sub>CCx</sub> = 5V                                                                                                            |                          |      | 24                    | mA     |

| Active V <sub>DD</sub> Cu<br>5V Cards       | rrent                                      | I <sub>DD</sub>         | 3x V <sub>DD</sub> step-up:<br>I <sub>CCA</sub> + I <sub>CCB</sub> = 80mA, V <sub>DD</sub> = 2.7V,<br>f <sub>XTAL</sub> = 20MHz, f <sub>CLK</sub> = 10MHz |                          |      | 325                   | mA     |

| Active V <sub>DD</sub> Cu                   | rrent                                      | I <sub>DD</sub>         | 2x V <sub>DD</sub> step-up:<br>I <sub>CCA</sub> + I <sub>CCB</sub> = 80mA, f <sub>XTAL</sub> = 20MHz,<br>f <sub>CLK</sub> = 10MHz, V <sub>DD</sub> = 2.7V |                          |      | 225                   | mA.    |

| 3V Cards                                    |                                            |                         | No step-up:<br>I <sub>CCA</sub> + I <sub>CCB</sub> = 80mA, f <sub>XTAL</sub> = 20MHz,<br>f <sub>CLK</sub> = 10MHz, V <sub>DD</sub> = 5V                   |                          |      | 120                   | 1 IIIA |

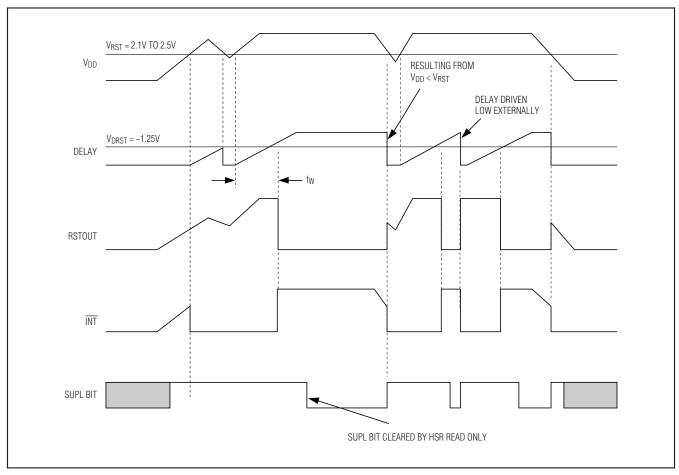

| Power-Fail Res                              | oct Voltago                                | V <sub>RST</sub>        | Threshold voltage (falling)                                                                                                                               | 2.1                      |      | 2.5                   | V      |

| Fower-rail nes                              | set voltage                                | V <sub>H</sub> YS       | Hysteresis                                                                                                                                                | 50                       |      | 170                   | mV     |

|                                             | Reset<br>Threshold                         | V <sub>DRST</sub>       |                                                                                                                                                           |                          | 1.25 |                       | V      |

| Delay Pin                                   | Output Voltage                             | V <sub>DO</sub>         |                                                                                                                                                           |                          |      | V <sub>DD</sub> + 0.3 | v      |

| Delay I III                                 | Output Current I <sub>DO</sub> VDELAY = 0V | V <sub>DELAY</sub> = 0V |                                                                                                                                                           | -2                       |      | μΑ                    |        |

|                                             | Output Ourient                             | 100                     | VDELAY = VDD                                                                                                                                              |                          | +2   |                       | mA     |

|                                             | Output<br>Capacitance                      | C <sub>DO</sub>         |                                                                                                                                                           | 1                        |      |                       | nF     |

| RSTOUT PIN                                  |                                            |                         |                                                                                                                                                           |                          |      |                       |        |

| Output High Voltage                         |                                            | Vohrsto                 | I <sub>OH</sub> = -1mA                                                                                                                                    | 0.8 x<br>V <sub>DD</sub> |      | V <sub>DD</sub> + 0.3 | V      |

| Output Low Vo                               | Itage                                      | Volrsto                 | I <sub>OL</sub> = 2mA                                                                                                                                     | -0.3                     |      | +0.4                  | V      |

| Leakage Curre                               | nt                                         | IL                      | V <sub>OL</sub> = 0V, V <sub>OH</sub> = 5V                                                                                                                | -10                      |      | +10                   | μA     |

|                                             |                                            |                         | -                                                                                                                                                         |                          |      |                       |        |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3.3V, V_{DDA} = +3.3V, T_A = +25$ °C, unless otherwise noted.) (Note 1)

| PARAMETER        |                          | SYMBOL                                | CONDITIONS             | MIN                            | TYP                    | MAX  | UNITS            |        |  |

|------------------|--------------------------|---------------------------------------|------------------------|--------------------------------|------------------------|------|------------------|--------|--|

| Alarm            | Pulse Wid                | th                                    | tw                     | C <sub>DELAY</sub> = 22nF      |                        | 10   |                  | ms     |  |

| Eytorn           | External Clock Frequency |                                       | form                   | External crystal               | 4                      |      | 20               | MHz    |  |

| Extern           |                          |                                       | fxtal                  | External oscillator            | 0                      |      | 20               | IVIMZ  |  |

| Interna          | al Oscillato             | or                                    | fINT                   |                                | 1.6                    | 2.5  | 3.7              | MHz    |  |

| Voltag           | e on V <sub>UP</sub> F   | Pin .                                 | V <sub>UP</sub>        | 3x step-up                     |                        | 5.7  |                  | V      |  |

| Voltag           | C 011 VUP 1              | 111                                   | VUP                    | 2x step-up                     |                        | 4.1  |                  | V      |  |

| Voltag<br>3x Ste |                          | n of $V_{DDA}$ for $2x$ ,             | V <sub>DET</sub>       |                                | 3.25                   | 3.50 | 3.60             | V      |  |

| Shutdo           | own Tempe                | erature                               | T <sub>SD</sub>        |                                |                        | +150 |                  | °C     |  |

|                  | Card<br>Inactive         | Output Low<br>Voltage                 | Volrst                 | I <sub>OLRST</sub> = 1mA       | 0                      |      | 0.3              | V      |  |

|                  | Mode                     | Output Current                        | IOLRST                 | V <sub>OLRST</sub> = 0V        | 0                      |      | -1               | mA     |  |

|                  |                          | Output Low<br>Voltage                 | Volrstl                | I <sub>OLRST</sub> = +200μA    | 0                      |      | 0.3              | V      |  |

| RSTx<br>Pins     | Card<br>Active<br>Mode   | Output High<br>Voltage                | Vohrsth                | IOHRST = -200μA                | V <sub>CCx</sub> - 0.5 |      | V <sub>CCx</sub> | V      |  |

| 1 1113           |                          | Rise Time                             | trrst                  | $C_L = 30pF$                   |                        |      | 0.1              | 0      |  |

|                  |                          | Fall Time                             | tfrst                  | C <sub>L</sub> = 30pF          |                        |      | 0.1              | μs     |  |

|                  |                          | Shutdown<br>Current                   | I <sub>RST(SD)</sub>   |                                |                        | -25  |                  | m ^    |  |

|                  |                          | Current<br>Limitation                 | IRST(LIMIT)            |                                | -30                    |      | +30              | · mA   |  |

|                  | Card<br>Inactive         | Output Low<br>Voltage                 | Volclk                 | IOLCLK = 1mA                   | 0                      |      | 0.3              | V      |  |

|                  | Mode                     | Output Current                        | lolclk                 | V <sub>OLCLK</sub> = 0V        | 0                      |      | -1               | mA     |  |

|                  |                          | Output Low<br>Voltage                 | V <sub>OLCLK</sub>     | I <sub>OLCLK</sub> = +200μA    | 0                      |      | 0.3              | V      |  |

| CLKx<br>Pins     | 1 0 0.0                  | Voltage VOHCLK TOHCLK = -200µA 0.     | V <sub>CCx</sub> - 0.5 |                                | V <sub>CCx</sub>       | V    |                  |        |  |

| PINS             | Active<br>Mode           | Rise Time                             | trclk                  | C <sub>L</sub> = 30pF (Note 2) |                        |      | 8                |        |  |

|                  |                          | Fall Time                             | tFCLK                  | C <sub>L</sub> = 30pF (Note 2) |                        |      | 8                | ns     |  |

|                  |                          | Current<br>Limitation                 | ICLK(LIMIT)            |                                | -90                    |      | +90              | mA     |  |

|                  | Clock Fr                 | · · · · · · · · · · · · · · · · · · · | form                   | Idle configuration (1MHz)      | 1                      |      | 1.85             | NALJ → |  |

|                  | Clock Fre                | equency                               | I TOLK H               | Operational                    | 0                      |      | 10               | MHz    |  |

|                  | Duty Fac                 | tor                                   | δ                      | $C_L = 30pF$                   | 45                     |      | 55               | %      |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3.3V, V_{DDA} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$  (Note 1)

|                  | PARAMETER        |                              | SYMBOL                 | CONDITIONS                                                             | MIN                  | TYP  | MAX       | UNITS |

|------------------|------------------|------------------------------|------------------------|------------------------------------------------------------------------|----------------------|------|-----------|-------|

|                  | Card<br>Inactive | Output Low<br>Voltage        | V <sub>CCx</sub>       | ICC = 1mA                                                              | 0                    |      | 0.3       | V     |

|                  | Mode             | Output Current               | Icc                    | V <sub>CCx</sub> = 0V                                                  | 0                    |      | -1        | mA    |

|                  |                  |                              |                        | I <sub>CC(5V)</sub> < 65mA                                             | 4.72                 | 5.00 | 5.25      |       |

|                  |                  |                              |                        | I <sub>CC(3V)</sub> < 50mA                                             | 2.75                 | 3.00 | 3.22      |       |

|                  |                  |                              |                        | ICC(1.8V) < 30mA                                                       | 1.62                 | 1.80 | 1.95      |       |

|                  |                  | Output Low<br>Voltage        | V <sub>CCx</sub>       | 5V card, current pulses of 40nC with I < 200mA, t < 400ns, f < 20MHz   | 4.6                  |      | 5.4       | V     |

| V <sub>CCx</sub> |                  |                              |                        | 3V card, current pulses of 24nC with I < 200mA, t < 400ns, f < 20MHz   | 2.75                 |      | 3.25      |       |

| Pins             | Card<br>Active   |                              |                        | 1.8V card, current pulses of 12nC with I < 200mA, t < 400ns, f < 20MHz | 1.62                 |      | 1.98      |       |

|                  | Mode             |                              |                        | $V_{CCx(5V)} = 0 \text{ to } 5V$                                       |                      |      | -65       |       |

|                  |                  | Output Current               | Icc                    | $V_{CCx(3V)} = 0 \text{ to } 3V$                                       |                      |      | -50       |       |

|                  |                  |                              |                        | $V_{CCx(1.8V)} = 0 \text{ to } 1.8V$                                   |                      |      | -30       |       |

|                  |                  | Total Current<br>(Two Cards) | ICC(A+B)               |                                                                        |                      |      | -80       | mA    |

|                  |                  | Shutdown<br>Current          | ICC(SD)                |                                                                        |                      | -100 |           |       |

|                  |                  | Slew Rate                    | Vccsr                  | Up/down, C < 300nF (Note 3)                                            | 0.05                 | 0.16 | 0.5       | V/µs  |

|                  | Card             | Output Low<br>Voltage        | V <sub>OLIO</sub>      | I <sub>OLIO</sub> = 1mA                                                | 0                    |      | 0.3       | V     |

|                  | Inactive         | Output Current               | lolio                  | V <sub>OLIO</sub> = 0V                                                 | 0                    |      | -1        | mA    |

|                  | Mode             | Internal Pullup<br>Resistor  | RPULLUP                | To V <sub>CCx</sub>                                                    | 9                    | 14   | 19        | kΩ    |

|                  |                  | Output Low<br>Voltage        | Volio                  | I <sub>OLIO</sub> = 1mA                                                | 0                    |      | 0.3       | .,    |

|                  |                  | Output High                  | V <sub>OHIO</sub>      | I <sub>OHIO</sub> ≤ -20μA                                              | 0.8 x V <sub>C</sub> | Cx   | $V_{CCx}$ | V     |

|                  |                  | Voltage                      | VOHIO                  | I <sub>OHIO</sub> ≤ -40μA (3V/5V)                                      | 0.75 x V             | CCx  | VCCx      |       |

| I/Ox             |                  | Output<br>Rise/Fall Time     | tOT                    | C <sub>L</sub> = 30pF                                                  |                      |      | 0.1       | μs    |

| Pins             | Card             | Input Low<br>Voltage         | V <sub>ILIO</sub>      |                                                                        | -0.3                 |      | +0.8      | V     |

|                  | Active<br>Mode   | Input High<br>Voltage        | VIHIO                  |                                                                        | 1.5                  |      | VCC       | V     |

|                  |                  | Input Low<br>Current         | I <sub>ILIO</sub>      | V <sub>ILIO</sub> = 0V                                                 |                      |      | 700       |       |

|                  |                  | Input High<br>Current        | Іню                    | V <sub>IHIO</sub> = V <sub>CCx</sub>                                   |                      |      | 20        | μΑ    |

|                  |                  | Input Rise/Fall<br>Time      | tı⊤                    | C <sub>L</sub> = 30pF                                                  |                      |      | 1.2       | μs    |

|                  |                  | Current<br>Limitation        | I <sub>IO(LIMIT)</sub> |                                                                        | -25                  |      | +25       | mA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3.3V, V_{DDA} = +3.3V, T_A = +25$ °C, unless otherwise noted.) (Note 1)

|             | PARAI                  | METER                       | SYMBOL             | CONDITIONS                            | MIN                   | TYP | MAX                  | UNITS |

|-------------|------------------------|-----------------------------|--------------------|---------------------------------------|-----------------------|-----|----------------------|-------|

|             | Card                   | Output Low<br>Voltage       | V <sub>OLC48</sub> | IOLC48 = 1mA                          | 0                     |     | 0.3                  | V     |

|             | Inactive<br>Mode       | Output Current              | I <sub>OLC48</sub> | V <sub>OLC48</sub> = 0V               | 0                     |     | -1                   | mA    |

|             |                        | Internal Pullup<br>Resistor | RPULLUP            | Between C4 or C8 and V <sub>CCx</sub> | 6                     | 10  | 14                   | kΩ    |

|             |                        | Output Low<br>Voltage       | V <sub>OLC48</sub> | I <sub>OLC48</sub> = 1mA              | 0                     |     | 0.35                 |       |

|             |                        | Output High                 | V2.12.12           | I <sub>OHC48</sub> ≤ -20μA            | 0.8 x V <sub>C</sub>  | x   | V <sub>CCx</sub>     | - V   |

|             |                        | Voltage                     | V <sub>OHC48</sub> | I <sub>OHC48</sub> ≤ -40µA (3V/5V)    | 0.75 x Vc             | Cx  | V <sub>CCx</sub>     |       |

|             |                        | Output<br>Rise/Fall Time    | tor                | C <sub>L</sub> = 30pF                 |                       |     | 0.1                  | μs    |

| C4x,<br>C8x |                        | Input Low<br>Voltage        | V <sub>ILC48</sub> |                                       | -0.3                  |     | +0.8                 | M     |

| Pins        | Card<br>Active<br>Mode | Input High<br>Voltage       | VIHC48             |                                       | 1.5                   |     | V <sub>CCx</sub>     | V     |

|             |                        | Input Low<br>Current        | IILC48             | V <sub>ILIO</sub> = 0V                |                       |     | 850                  | ^     |

|             |                        | Input High<br>Current       | I <sub>IHC48</sub> | VIHIO = VCCx                          |                       |     | 20                   | μΑ    |

|             |                        | Input Rise/Fall<br>Time     | t <sub>IT</sub>    | C <sub>L</sub> = 30pF                 |                       |     | 1.2                  | μs    |

|             |                        | Pullup Pulse<br>Width       | twpu               | Active pullup                         |                       | 200 |                      | ns    |

|             |                        | Operating<br>Frequency      | f <sub>MAX</sub>   | On card contact pins                  |                       |     | 1                    | MHz   |

| TIMIN       | G                      |                             |                    |                                       |                       |     |                      |       |

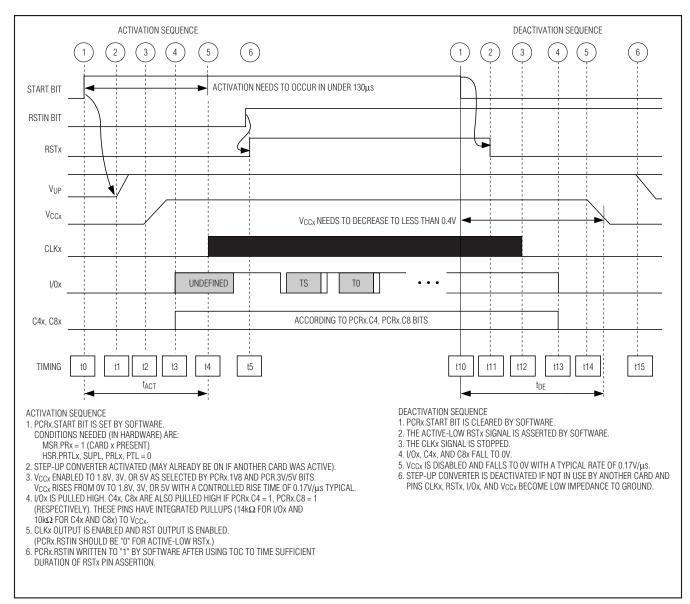

|             |                        | ence Duration               | tACT               | See Figure 9                          |                       |     | 130                  | μs    |

| Deact       | vation Sec             | quence Duration             | tDE                | See Figure 9                          |                       |     | 150                  | μs    |

|             | A/PRESB                |                             | ı                  |                                       |                       |     |                      |       |

|             | _ow Voltag             |                             | VILPRES            |                                       |                       |     | 25 x V <sub>DD</sub> | V     |

|             | High Voltag            |                             | VIHPRES            |                                       | 0.7 x V <sub>DE</sub> | )   | 10                   | V     |

|             | _ow Curren             |                             | lilpres            | VILPRES = 0V                          |                       |     | 40                   | μA    |

| Input I     | High Curre             | าเ                          | IHPRES             | VIHPRES = VDD                         |                       |     | 40                   | μΑ    |

|             | al Pullup R            | <br>esistor                 | Rpullup            | Between I/OAUX and VDD                | 9                     | 14  | 19                   | kΩ    |

|             | t Low Volta            |                             | VOLAUX             | I <sub>OLAUX</sub> = 1mA              |                       | 17  | 0.3                  | V V   |

|             | t High Volta           |                             | VOLAUX             | Ι <sub>ΟΗΑUX</sub> = 40μΑ (3V/5V)     | 0.75 x V <sub>C</sub> | חר  | V <sub>DD</sub>      | V     |

|             | t Rise/Fall            |                             | tor                | C <sub>L</sub> = 30pF                 | 3 3 VL                |     | 0.1                  | μs    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3.3V, V_{DDA} = +3.3V, T_A = +25$ °C, unless otherwise noted.) (Note 1)

| PARAMETER                   | SYMBOL             | CONDITIONS              | MIN TY                   | P MAX                    | UNITS |

|-----------------------------|--------------------|-------------------------|--------------------------|--------------------------|-------|

| Input Low Voltage           | VILAUX             |                         | -0.3                     | 0.3 x<br>V <sub>DD</sub> | V     |

| Input High Voltage          | V <sub>IHAUX</sub> |                         | 0.7 x<br>V <sub>DD</sub> | $V_{DD}$                 | V     |

| Input Low Current           | IILAUX             | V <sub>ILAUX</sub> = 0V |                          | 700                      | μA    |

| Input High Current          | IIHAUX             | VIHAUX = VDD            | -20                      | +20                      | μA    |

| Input Rise/Fall Time        | tıT                | $C_L = 30pF$            |                          | 1.2                      | μs    |

| INTERRUPT PIN               |                    |                         |                          |                          |       |

| Output Low Voltage          | VOLINT             | I <sub>OH</sub> = 2mA   |                          | 0.3                      | V     |

| Input High Leakage Current  | ILIHINT            |                         |                          | 10                       | μA    |

| D7 TO D0, ALL OTHER LOGIC I | PINS               |                         |                          |                          |       |

| Output Low Voltage          | V <sub>OLD</sub>   | I <sub>OLD</sub> = +5mA |                          | 0.2 x<br>V <sub>DD</sub> | V     |

| Output High Voltage         | Vohd               | I <sub>OHD</sub> = -5mA | 0.8 x<br>V <sub>DD</sub> | V <sub>DD</sub>          | V     |

| Output Rise/Fall Time       | toT                | C <sub>L</sub> = 50pF   |                          | 25                       | ns    |

| Input Low Voltage           | V <sub>ILD</sub>   |                         |                          | 0.3 x<br>V <sub>DD</sub> | V     |

| Input High Voltage          | VIHD               |                         | 0.7 x<br>V <sub>DD</sub> |                          | V     |

| Input Low Current           | l <sub>ILD</sub>   |                         | -20                      | +20                      | μA    |

| Input High Current          | lihd               |                         | -20                      | +20                      | μΑ    |

| Load Capacitance            | C <sub>LD</sub>    |                         |                          | 10                       | pF    |

**Note 1:** Operation guaranteed at -40°C but not tested.

Note 2: Parameters are guaranteed to meet all ISO 7816, GSM11-11, and EMV 2000 requirements. For the 1.8V card, the maximum rise and fall time is 10ns.

**Note 3:** Parameter is guaranteed to meet all ISO 7816, GSM11-11, and EMV 2000 requirements. For the 1.8V card, the minimum slew rate is 0.05V/µs and the maximum slew rate is 0.5V/µs.

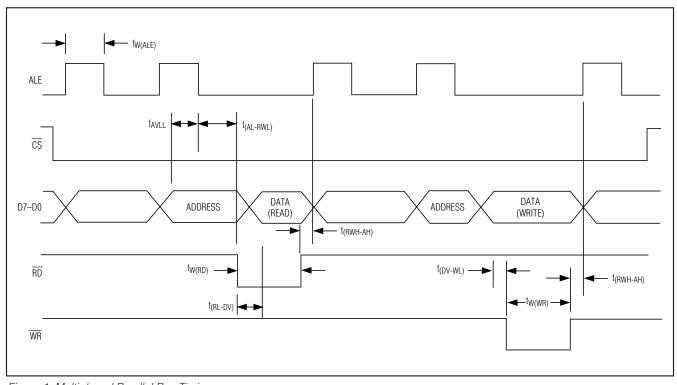

# AC ELECTRICAL SPECIFICATIONS—TIMING PARAMETERS FOR MULTIPLEXED PARALLEL BUS

$(V_{DD} = 3.3V, V_{DDA} = 3.3V, T_{A} = +25^{\circ}C, unless otherwise noted.)$  (Figure 1)

| PARAMETER                  | SYMBOL              | CONDITIONS      | MIN TY        | P MAX | UNITS |

|----------------------------|---------------------|-----------------|---------------|-------|-------|

| XTAL1 Cycle Time           | tCY(XTAL1)          |                 | 50            |       | ns    |

| ALE Pulse Width            | t <sub>W(ALE)</sub> |                 | 20            |       | ns    |

| Address Valid to ALE Low   | tavll               |                 | 10            |       | ns    |

| ALE Low to RD or WR Low    | t(AL-RWL)           |                 | 10            |       | ns    |

| RD Pulse Width             | turn                | Register URR    | 2 x tcy(xtal- | 1)    | 200   |

| ND Pulse Width             | tw(RD)              | Other registers | 10            |       | ns    |

| RD Low to Data Read Valid  | t(RL-DV)            |                 |               | 50    | ns    |

| WR/RD High to ALE High     | t(RWH-AH)           |                 | 10            |       | ns    |

| WR Pulse Width             | tw(wr)              |                 | 10            |       | ns    |

| Data Write Valid to WR Low | t(DV-WL)            |                 | 10            |       | ns    |

Figure 1. Multiplexed Parallel Bus Timing

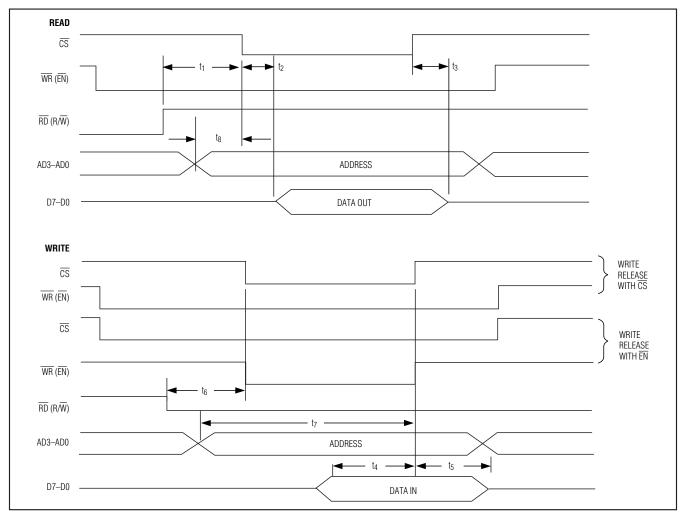

# AC ELECTRICAL SPECIFICATIONS—TIMING PARAMETERS FOR NONMULTIPLEXED PARALLEL BUS (READ AND WRITE)

$(V_{DD} = 3.3V, V_{DDA} = 3.3V, T_{A} = +25$ °C, unless otherwise noted.) (See Figure 2.)

| PARAMETER                            | SYMBOL         | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------------------------------------|----------------|------------|-----|-----|-----|-------|

| RD High to CS Low                    | t <sub>1</sub> |            | 10  |     |     | ns    |

| Access Time CS Low to Data Out Valid | t <sub>2</sub> |            |     |     | 50  | ns    |

| CS High to Data Out High Impedance   | t3             |            |     |     | 10  | ns    |

| Data Valid to End of Write           | t <sub>4</sub> |            | 10  |     |     | ns    |

| Data Hold Time                       | t <sub>5</sub> |            | 10  |     |     | ns    |

| RD Low to CS or WR Low               | t <sub>6</sub> |            | 10  |     |     | ns    |

| Address Stable to CS or WR High      | t <sub>7</sub> |            | 10  |     |     | ns    |

| Address to CS Low                    | t <sub>8</sub> |            | 10  |     |     | ns    |

Figure 2. Nonmultiplexed Parallel Bus Timing (Read and Write)

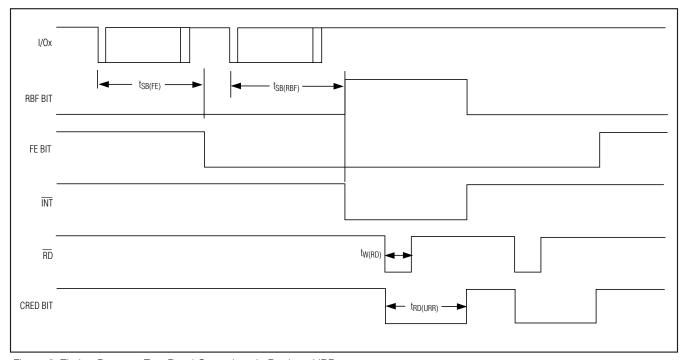

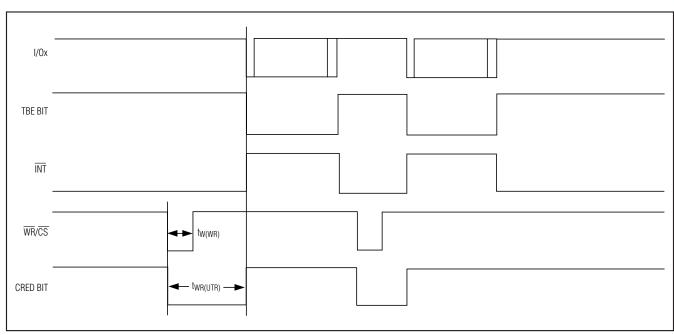

# AC ELECTRICAL SPECIFICATIONS—TIMING PARAMETERS FOR CONSECUTIVE READ/WRITE TO URR/UTR/TOC

$(V_{DD} = 3.3V, V_{DDA} = 3.3V, T_{A} = +25^{\circ}C, unless otherwise noted.)$

| PARAMETER                  | SYMBOL               | CONDITIONS      | MIN                   | TYP MAX               | UNITS |

|----------------------------|----------------------|-----------------|-----------------------|-----------------------|-------|

| SEE FIGURE 3               |                      |                 |                       |                       |       |

| RD Pulse Width             | tw(RD)               |                 | 10                    |                       | ns    |

| RD Low to Bit CRED = 1     | t <sub>RD(URR)</sub> |                 | tw(RD) +<br>2tcy(CLK) | tw(RD) +<br>3tcy(CLK) | ns    |

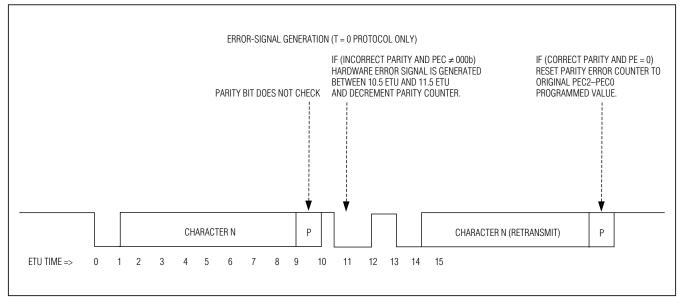

| Set Time Bit FE            | t <sub>SB(FE)</sub>  |                 | 10.5                  |                       | ETU   |

| Set Time Bit RBF           | tsb(RBF)             |                 | 10.5                  |                       | ETU   |

| SEE FIGURE 4               |                      |                 |                       |                       |       |

| WR/CS Pulse Width          | tw(wr)               | (Note 4)        | 10                    |                       | ns    |

| WR/CS Low to I/Ox Low      | twr(utr)             |                 | tw(wr) +<br>2tcy(clk) | tw(wr) +<br>3tcy(clk) | ns    |

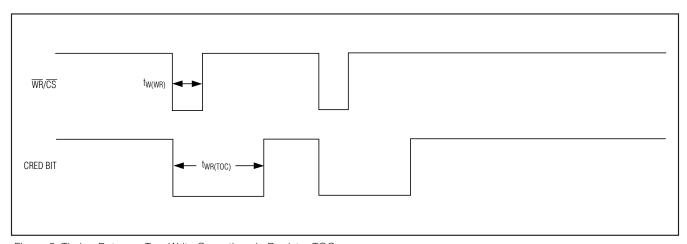

| SEE FIGURE 5               |                      |                 |                       |                       |       |

| WR/CS Pulse Width          | tw(wr)               |                 | 10                    |                       | ns    |

| WR/CS High to Bit CRED = 1 | twr(toc)             | (Notes 4 and 5) | 1 / PSC               | 2/PSC                 | ETU   |

Note 4: Depends on the leading edge of WR or CS (whichever is deasserted first). Reference this specification to the rising edge of CS/WR instead of the falling edge.

Note 5: PSC is the programmed prescaler value (31 or 32).

Figure 3. Timing Between Two Read Operations in Register URR

Figure 4. Timing Between Two Write Operations in Register UTR

Figure 5. Timing Between Two Write Operations in Register TOC

### \_\_\_\_Pin Description

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                    |

|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RSTOUT           | Reset Output. This active-high output is provided for resetting external devices. The RSTOUT pin is driven high until the DELAY pin reaches V <sub>DRST</sub> . Once the DELAY pin reaches V <sub>DRST</sub> , the RSTOUT pin is tri-stated so it can externally be pulled down. The SUPL bit is set for each RSTOUT pulse. |

| 2   | I/OAUX           | Auxiliary I/O. This I/O pin allows connection to an auxiliary smart card interface.                                                                                                                                                                                                                                         |

| 3   | I/OA             | Smart Card A I/O Data Line. This is the I/O data line associated with smart card A. This is also referred to as the ISO C7 contact.                                                                                                                                                                                         |

| 4   | C8A              | Smart Card A Auxiliary I/O. This is an auxiliary I/O associated with smart card A. This is also referred to as the ISO C8 contact. This can be associated with synchronous cards.                                                                                                                                           |

| 5   | PRESA            | Smart Card A Presence Contact. This is the active-high presence contact associated with smart card A.                                                                                                                                                                                                                       |

| 6   | C4A              | Smart Card A Auxiliary I/O. This is an auxiliary I/O associated with smart card A. This is also referred to as the ISO C4 contact. This can be associated with synchronous cards.                                                                                                                                           |

| 7   | GNDA             | Smart Card A Ground. This must be connected to GND.                                                                                                                                                                                                                                                                         |

| 8   | CLKA             | Smart Card A Clock Output. This is the clock output associated with smart card A. This is also referred to as the ISO C3 contact.                                                                                                                                                                                           |

| 9   | VCCA             | Smart Card A Supply Voltage. This is the supply voltage output associated with smart card A. This is also referred to as the ISO C1 contact.                                                                                                                                                                                |

| 10  | RSTA             | Smart Card A Reset. This is the reset output associated with smart card A. This is also referred to as the ISO C2 contact.                                                                                                                                                                                                  |

| 11  | I/OB             | Smart Card B I/O Data Line. This is the I/O data line associated with smart card B. This is also referred to as the ISO C7 contact.                                                                                                                                                                                         |

| 12  | C8B              | Smart Card B Auxiliary I/O. This is an auxiliary I/O associated with smart card B. This is also referred to as the ISO C8 contact. This can be associated with synchronous cards.                                                                                                                                           |

| 13  | PRESB            | Smart Card B Presence Contact. This is the active-high presence contact associated with smart card B.                                                                                                                                                                                                                       |

| 14  | C4B              | Smart Card B Auxiliary I/O. This is an auxiliary I/O associated with smart card B. This is also referred to as the ISO C4 contact. This can be associated with synchronous cards.                                                                                                                                           |

| 15  | GNDB             | Smart Card B Ground. This must be connected to GND.                                                                                                                                                                                                                                                                         |

| 16  | CLKB             | Smart Card B Clock Output. This is the clock output associated with smart card B. This is also referred to as the ISO C3 contact.                                                                                                                                                                                           |

| 17  | V <sub>CCB</sub> | Smart Card B Supply Voltage. This is the supply voltage output associated with smart card B. This is also referred to as the ISO C1 contact.                                                                                                                                                                                |

| 18  | RSTB             | Smart Card B Reset. This is the reset output associated with smart card B. This is also referred to as the ISO C2 contact.                                                                                                                                                                                                  |

| 19  | GND              | Ground                                                                                                                                                                                                                                                                                                                      |

| 20  | V <sub>UP</sub>  | Step-Up Converter Connection. Connect a low-ESR capacitor of 220nF between this pin and ground.                                                                                                                                                                                                                             |

### \_\_\_\_\_Pin Description (continued)

| PIN    | NAME                                                                                                                                                                                            | FUNCTION                                                                                                                                                                                                                                                                                                                                |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21     | CPA1                                                                                                                                                                                            | Step-Up Converter Contact 1. Connect a low-ESR capacitor of 220nF between CPA1 and CPA2.                                                                                                                                                                                                                                                |

| 22     | CPB1                                                                                                                                                                                            | Step-Up Converter Contact 3. Connect a low-ESR capacitor of 220nF between CPB1 and CPB2.                                                                                                                                                                                                                                                |

| 23     | Analog Supply Voltage. Positive analog-supply voltage for the step-up converter; can be higher lower than V <sub>DD</sub> . This pin should be decoupled to AGND with a good quality capacitor. |                                                                                                                                                                                                                                                                                                                                         |

| 24     | CPB2                                                                                                                                                                                            | Step-Up Converter Contact 4. Connect a low-ESR capacitor of 220nF between CPB1 and CPB2.                                                                                                                                                                                                                                                |

| 25     | AGND                                                                                                                                                                                            | Analog Ground                                                                                                                                                                                                                                                                                                                           |

| 26     | CPA2                                                                                                                                                                                            | Step-Up Converter Contact 2. Connect a low-ESR capacitor of 220nF between CPA1 and CPA2.                                                                                                                                                                                                                                                |

| 27     | $V_{DD}$                                                                                                                                                                                        | Digital Supply Voltage. This pin should be decoupled to GND with a good quality capacitor.                                                                                                                                                                                                                                              |

| 28–35  | D0-D7                                                                                                                                                                                           | 8-Bit Digital I/O. This port functions as the data or address/data communication lines between the host controller and the DS8007A for the nonmultiplexed and multiplexed operating modes, respectively.                                                                                                                                |

| 36     | RD                                                                                                                                                                                              | Active-Low Parallel Bus Read Strobe Input. In multiplexed mode, this input indicates when the host processor is reading information from the DS8007A. In nonmultiplexed mode, this pin signals the current operation is a read $(\overline{RD} = 1)$ or a write $(\overline{RD} = 0)$ when $\overline{CS}$ and $\overline{WR}$ are low. |

| 37     | WR                                                                                                                                                                                              | Active-Low Parallel Bus Write Strobe Input. In multiplexed mode, this input indicates when the host processor is writing information to the DS8007A. In nonmultiplexed mode, a low on this pin signals the bus is engaged in a read or write operation.                                                                                 |

| 38     | CS                                                                                                                                                                                              | Active-Low Chip-Select Input. This input indicates when the DS8007A is active on the parallel bus.                                                                                                                                                                                                                                      |

| 39     | ALE                                                                                                                                                                                             | Address Latch Enable Input. This signal monitors the ALE signal when the host processor bus is operating in multiplexed mode. Connect this signal to VDD when operating in nonmultiplexed mode.                                                                                                                                         |

| 40     | ĪNT                                                                                                                                                                                             | Active-Low Interrupt. This output indicates an interrupt is active.                                                                                                                                                                                                                                                                     |

| 41     | INTAUX                                                                                                                                                                                          | Auxiliary Interrupt Input. This pin serves as an auxiliary interrupt.                                                                                                                                                                                                                                                                   |

| 42–45  | AD3-AD0                                                                                                                                                                                         | Register Selection Address Inputs. These pins function as the address input lines for the nonmultiplexed configuration and should be connected to ground or V <sub>DD</sub> in the multiplexed configuration.                                                                                                                           |

| 46, 47 | XTAL2,<br>XTAL1                                                                                                                                                                                 | Crystal Oscillators. Place a crystal with appropriate load capacitors between these pins if that is the desired clock source. XTAL1 also acts as an input if there is an external clock source in place of a crystal.                                                                                                                   |

| 48     | DELAY                                                                                                                                                                                           | External Delay Capacitor Connection. Connect a capacitor from this pin to ground to set the power-on reset delay.                                                                                                                                                                                                                       |

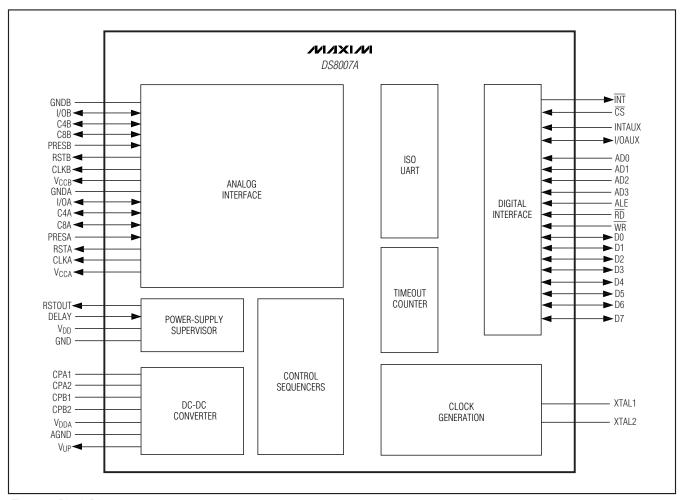

### **Detailed Description**

The following describes the major functional features of the device. Use of this document requires the reader have a basic understanding of ISO 7816 terminology.

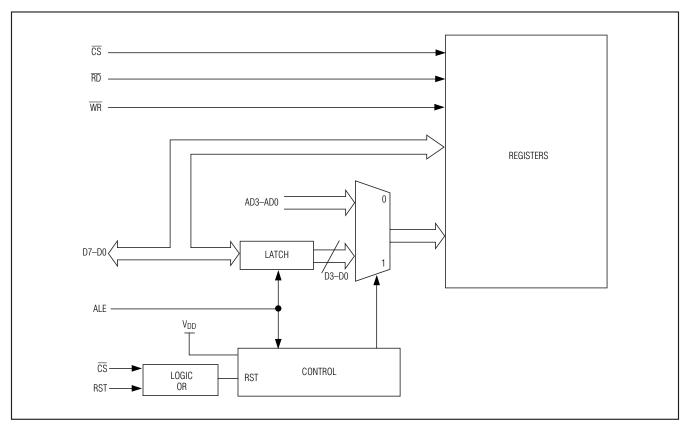

### **Parallel Bus Interface**

The device interfaces to a host computer/processor through a multiplexed or demultiplexed, parallel, 8-bit data bus (D0-D7). The parallel bus interface monitors the ALE signal and automatically detects whether a multiplexed or nonmultiplexed external bus interface is intended. The nonmultiplexed external bus interface is the default configuration and is maintained so long as

no edge (activity) is detected on the ALE pin. Once a rising edge is detected on the ALE pin, the DS8007A is placed into the multiplexed mode of operation. Once in the multiplexed mode of operation, a reset/power cycle or the deassertion of  $\overline{\text{CS}}$  forces the device to the nonmultiplexed mode. Connecting the ALE pin to  $V_{DD}$  or ground forces the device into nonmultiplexed parallel bus mode. Figure 7 shows that the bus recognition dictates whether the external address lines (AD3–AD0) can be used directly or whether the external data lines (D7–D0) must be latched according to the ALE input signal. In the multiplexed mode of operation, a new address is latched irrespective of the state of  $\overline{\text{CS}}$ .

Figure 6. Block Diagram

Figure 7. Parallel Bus Interface

#### **Multiplexed Mode**

In the multiplexed mode of operation, the D7–D0 signals are multiplexed between address and data. The falling edge of the address latch enable (ALE) signal from the host microcontroller latches the address (D3–D0), and the  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  strobe input signals are used to enable a read or write operation, respectively, if the DS8007A is selected (i.e.,  $\overline{\text{CS}} = 0$ ). See the AC timing for the multiplexed parallel bus mode found earlier in this data sheet.

### **Nomultiplexed Mode**

In the nonmultiplexed mode of operation, the address is always provided on the AD3–AD0 signals, and the data is always transacted on the D7–D0 signals. The  $\overline{\text{RD}}$  input signal is used as a read/write (R/W) operation select. The  $\overline{\text{WR}}$  and  $\overline{\text{CS}}$  input signals serve as active-low enables, and must be asserted for the read or write operation to take place. See the AC timing for the nonmultiplexed parallel bus mode found earlier in this data sheet.

### **Control Registers**

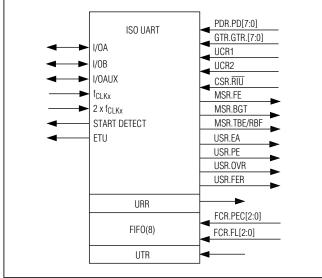

Special control registers that the host computer/micro-controller accesses through the parallel bus manage most DS8007A features. Many of the registers, although only mentioned once in the listing, are duplicated for each card interface. The PDR, GTR, UCR1, UCR2, and CCR registers exist separately for each of the three card interfaces. The PCR register is provided only for card interface A and card interface B.

The specific register to be accessed is controlled by the current setting of the SC3-SC1 bits in the Card Select Register. For example, there are three instances of the UART Control Register 1 (UCR1) at address 06h. If the SC3-SC1 bits are configured so that card A is selected, then all reads and writes to address 06h only affect card A. If SC3-SC1 are changed to select card B, then all reads and writes to address 06h only affect card B, etc.

In addition, some registers have different functions based on whether the register is being read from or written to. An example of this are the UART Receive (URR)/UART Transmit (UTR) registers located at address 0Dh. Although they share the same address, during read operations the receive register is read, and write operations go to a separate transmit register. This selection requires no extra configuration by the software.

**Table 1. Special Function Register Map**

| ADDRESS<br>(HEX) | REGISTER<br>NAME | R/W | BIT 7 | BIT 6          | BIT 5  | BIT 4 | BIT 3 | BIT 2 | BIT 1   | BIT 0       | RESET     | RIU = 0*  |

|------------------|------------------|-----|-------|----------------|--------|-------|-------|-------|---------|-------------|-----------|-----------|

| 00               | CSR              | R/W | CSR7  | CSR6           | CSR5   | CSR4  | RIU   | SC3   | SC2     | SC1         | 0011 0000 | 0011 0uuu |

| 01               | CCR              | R/W | _     | _              | SHL    | CST   | SC    | AC2   | AC1     | AC0         | 0000 0000 | 00uu uuuu |

| 02               | PDR              | R/W | PD7   | PD6            | PD5    | PD4   | PD3   | PD2   | PD1     | PD0         | 0000 0000 | uuuu uuuu |

| 03               | UCR2             | R/W | _     | DISTBE/<br>RBF | DISAUX | PDWN  | SAN   | AUTOC | CKU     | PSC         | 0000 0000 | uuuu uuuu |

| 05               | GTR              | R/W | GTR.7 | GTR.6          | GTR.5  | GTR.4 | GTR.3 | GTR.2 | GTR.1   | GTR.0       | 0000 0000 | uuuu uuuu |

| 06               | UCR1             | R/W | FTE0  | FIP            | _      | PROT  | T/R   | LCT   | SS      | CONV        | 0000 0000 | Ouuu OOuu |

| 07               | PCR              | R/W | _     | _              | C8     | C4    | 1V8   | RSTIN | 3V/5V   | START       | 0011 0000 | 0011 uuuu |

| 08               | TOC              | R/W | TOC7  | TOC6           | TOC5   | TOC4  | TOC3  | TOC2  | TOC1    | TOC0        | 0000 0000 | 0000 0000 |

| 09               | TOR1             | W   | TOL7  | TOL6           | TOL5   | TOL4  | TOL3  | TOL2  | TOL1    | TOL0        | 0000 0000 | uuuu uuuu |

| 0A               | TOR2             | W   | TOL15 | TOL14          | TOL13  | TOL12 | TOL11 | TOL10 | TOL9    | TOL8        | 0000 0000 | uuuu uuuu |

| 0B               | TOR3             | W   | TOL23 | TOL22          | TOL21  | TOL20 | TOL19 | TOL18 | TOL17   | TOL16       | 0000 0000 | uuuu uuuu |

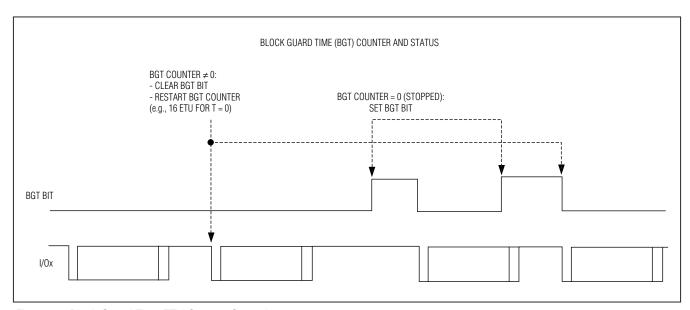

| 0C               | MSR              | R   | CLKSW | FE             | BGT    | CRED  | PRB   | PRA   | INTAUX  | TBE/<br>RBF | 0101 0000 | u1u1 uuu0 |

| 0C               | FCR              | W   | _     | PEC2           | PEC1   | PEC0  | FTE1  | FL2   | FL1     | FL0         | 0000 0000 | Ouuu Ouuu |

| 0D               | URR              | R   | UR7   | UR6            | UR5    | UR4   | UR3   | UR2   | UR1     | UR0         | 0000 0000 | 0000 0000 |

| 0D               | UTR              | W   | UT7   | UT6            | UT5    | UT4   | UT3   | UT2   | UT1     | UT0         | 0000 0000 | 0000 0000 |

| 0E               | USR              | R   | TO3   | TO2            | TO1    | EA    | PE    | OVR   | FER     | TBE/<br>RBF | 0000 0000 | 0000 0000 |

| 0F               | HSR              | R   | _     | PRTLB          | PRTLA  | SUPL  | PRLB  | PRLA  | INTAUXL | PTL         | 0001 0000 | Ouuu xxxu |

<sup>\*</sup>u = unchanged, x = always reflects state of external device pin, even when  $\overline{RIU}$  = 0.

Note: Writes to unimplemented bits have no effect. Reads of unimplemented bits return 0.

### Card Select Register (CSR)

| _           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------|------|------|------|------|------|------|------|------|

| Address 00h | CSR7 | CSR6 | CSR5 | CSR4 | RIU  | SC3  | SC2  | SC1  |

| _           | R-0  | R-0  | R-1  | R-1  | RW-0 | RW-0 | RW-0 | RW-0 |

R = unrestricted read, W = unrestricted write, -n = value after reset. This register is reset to 00110uuub on  $\overline{RIU} = 0$ .

**Bits 7 to 4: Identification Bits (CSR7 to CSR4).** These bits provide a method for software to identify the device as follows:

0011 = DS8007A revision Ax

Bit 3: Reset ISO UART (RIU). When this bit is cleared (0), most of the ISO UART registers are reset to their initial values. This bit must be cleared for at least 10ns prior to initiating an activation sequence. This bit must be set (1) by software before any action on the UART can take place.

**Bits 2 to 0: Select Card Bits (SC3 to SC1).** These bits determine which IC card interface is active as shown below. Only one bit should be active at any time, and no card is selected after reset (i.e., SC3–SC1 = 000b). Other combinations are invalid.

000 = No card is selected.

001 = Card A is selected.

010 = Card B is selected.

100 = AUX card interface is selected.

### **Clock Configuration Register (CCR)**

|             | 7   | 6   | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------|-----|-----|------|------|------|------|------|------|

| Address 01h | _   | _   | SHL  | CST  | SC   | AC2  | AC1  | AC0  |

| _           | R-0 | R-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 |

$R = unrestricted read, W = unrestricted write, -n = value after reset. This register is reset to 00uuuuuub on <math>\overline{RIU} = 0$ .

#### Bits 7 and 6: Reserved.

**Bit 5: Stop High or Low (SHL).** This bit determines if the card clock stops in the low or high state when the CST bit is active. It forces the clock to stop in a low state when SHL = 0 or in a high state when SHL = 1.

**Bit 4: Clock Stop (CST).** For an asynchronous card, this bit allows the clock to the selected card to be stopped. When this bit is set (1), the card clock is stopped in the state determined by the SHL bit. When this bit is cleared (0), the card clock operation is defined by CCR bits AC2–AC0.

Bit 3: Synchronous Clock (SC). For a synchronous card, the card clock is controlled by software manipulation of this SC, and the contact CLKx is the copy of the value in this bit. In synchronous transmit mode, a write to the UTR results in the least significant bit (LSb) of the data written to the UTR being driven out on the

I/Ox pin. In synchronous receive mode, the state of the I/Ox pin can be read from the LSb of the URR.

Bits 2 to 0: Alternating Clock Select (AC2 to AC0). These bits select the frequency of the clock provided to the active card interface and to the UART for the elementary time unit (ETU) generation as shown below. All frequency changes are synchronous so that there are no spikes or unwanted pulse widths during transitions. fint is the frequency of the internal oscillator.

AC2-AC0

$000 = f_{XTAL}$

$001 = f_{XTAL} / 2$

$010 = f_{XTAL} / 4$

$011 = f_{XTAL} / 8$

$1xx = f_{INT} / 2$

### **Programmable Divider Register (PDR)**

| _           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------|------|------|------|------|------|------|------|------|

| Address 02h | PD7  | PD6  | PD5  | PD4  | PD3  | PD2  | PD1  | PD0  |

| _           | RW-0 |

R = unrestricted read, W = unrestricted write, -n = value after reset; all bits unaffected by  $\overline{RIU} = 0$ .

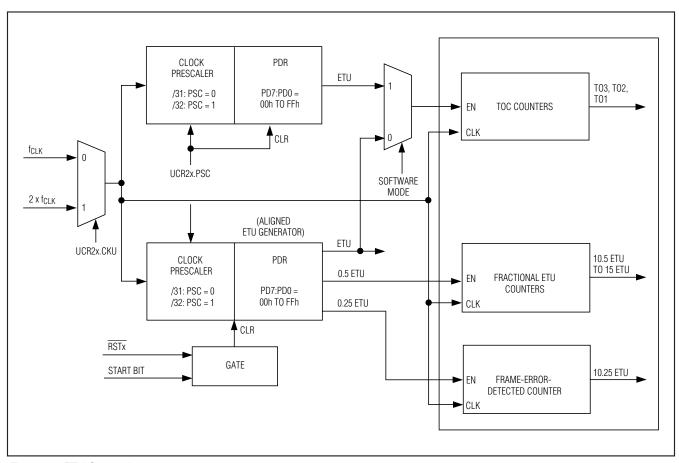

Bits 7 to 0: Programmable ETU Divider Register Bits 7 to 0 (PD7 to PD0). These bits, in conjunction with the defined UART input clock (based upon CKU, AC2–AC0) and the prescaler selection (PSC bit), are used to define the ETU for the UART when interfaced to the associated card interface. The output of the prescaler block is further divided according to the PD7–PD0 bits as follows:

- ETU = Prescaler output / (PD7-PD0), when PD7-PD0 = 02h-FFh

- ETU = Prescaler output / 1, when PD7-PD0 = 00h-01h

- Prescaler output / 256 is not supported

### **UART Control Register 2 (UCR2)**

|             | 7   | 6          | 5      | 4    | 3    | 2     | 1    | 0    |

|-------------|-----|------------|--------|------|------|-------|------|------|

| Address 03h | _   | DISTBE/RBF | DISAUX | PDWN | SAN  | AUTOC | CKU  | PSC  |

| _           | R-0 | RW-0       | RW-0   | RW-0 | RW-0 | RW-0  | RW-0 | RW-0 |

$R = unrestricted read, W = unrestricted write, -n = value after reset; all bits unaffected by <math>\overline{RIU} = 0$ .

#### Bit 7: Reserved.

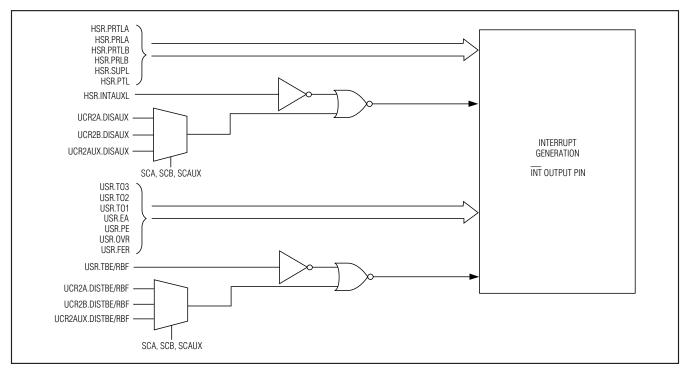

Bit 6: Disable TBE/RBF Interrupt (DISTBE/RBF). This bit controls whether the TBE/RBF flag can generate an interrupt on the INT pin. When this bit is cleared to 0, an interrupt is signaled on the INT pin in response to the TBE/RBF flag getting set. When DISTBE/RBF is set to 1, interrupts are not generated in response to the TBE/RBF flag. Disabling the TBE/RBF interrupt can allow faster communication speed with the card, but requires that a copy of TBE/RBF in register MSR be polled to not lose priority interrupts that can occur in register USR.

Bit 5: Disable Auxiliary Interrupt (DISAUX). This bit controls whether the external INTAUX pin can generate an interrupt on the INT output pin. When this bit is cleared to 0, a change on the INTAUX input pin results in assertion of the INT output pin. When DISAUX is set to 1, a change on INTAUX does not result in assertion of the INT output pin. The INTAUXL bit is set by a change on the INTAUX pin independent of the DISAUX bit state. Since the INTAUX bit is set independent of the DISAUX bit, it is advisable to read HSR (thus clearing INTAUX) prior to clearing DISAUX to avoid an interrupt on the INT pin. To avoid an interrupt when selecting a different card, the DISAUX bit should be set to 1 in all UCR2 registers.

Bit 4: Power-Down Mode Enable (PDWN). This bit controls entry into the power-down mode. Power-down mode can only be entered if the SUPL bit has been cleared. When PDWN is set to 1, the XTAL1 and XTAL2 crystal oscillator is stopped, and basic functions such as the sequencers are supported by the internal ring oscillator. The UART is put in a suspended state, and the clocks to the UART, the ETU unit, and the timeout counter are gated off. During the power-down mode, it is not possible to select a card other than the one currently selected (advisory to the programmer, selecting another card during power-down mode is not recommended). There are five ways of exiting the power-down mode:

- Insertion of card A or card B (detected by PRLA or PRLB).

- Withdrawal of card A or card B (detected by PRLA or PRLB).

- Reassertion of the CS pin to select the DS8007A (CS must be deasserted after setting PDWN = 1 for this event to exit from power-down).

- INTAUXL bit is set due to change in INTAUX (INTAUXL bit must be cleared first).

- Clearing of PDWN bit by software (if CS pin is always tied to 0).

Except in the case of a read operation of register HSR, the  $\overline{\text{INT}}$  pin remains asserted in the active-low state. The host device can read the status registers after the oscillator warmup time, and the  $\overline{\text{INT}}$  signal returns to the high state.

**Bit 3: Synchronous/Asynchronous Card Select** (SAN). This bit selects whether a synchronous or asynchronous card interface is enabled. When this bit is cleared to 0, an asynchronous card interface is expected. When this bit is set to 1, a synchronous interface is expected. In synchronous mode, the UART is bypassed; the SC bit controls the CLK, and I/O is transacted in the LSb of UTR/URR. Card interface AUX cannot operate in the true synchronous mode since it does not have a CLK signal to accompany I/OAUX. However, the SAN bit invokes the same control of I/OAUX through UTR/URR as is given for card interfaces A and B.

**Bit 2: Auto Convention Disable (AUTOC).** This active-low bit controls whether the decoding convention should automatically be detected during the first received character in answer-to-reset (ATR). If AUTOC = 0, the character decoding convention is automatically detected (while SS = 1) and the UCR1.CONV bit is written accordingly by hardware. If AUTOC = 1, the UCR1.CONV bit must be set by software to assign the character decoding convention. The AUTOC bit must not be changed during a card session.

Bit 1: Clock UART Doubler Enable (CKU). This bit enables the effective ETU defined for the UART to last half the number of clock cycles defined by the AC2–AC0 and PD7–PD0 configuration (except in the case when AC2–AC0 = 000b, where  $f_{CLK} = f_{XTAL}$ ). When CKU is cleared to 0, the AC2–AC0 defined  $f_{CLK}$  is used for ETU timing generation. When CKU is set to 1, a clock frequency of 2 x  $f_{CLK}$  is used for ETU generation.

Bit 0: Prescaler Select (PSC). When PSC = 0, the prescaler value is 31. When PSC = 1, the prescaler value is 32.

### **Guard Time Register (GTR)**

|             | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address 05h | GTR.7 | GTR.6 | GTR.5 | GTR.4 | GTR.3 | GTR.2 | GTR.1 | GTR.0 |

| _           | RW-0  |

$R = unrestricted read, W = unrestricted write, -n = value after reset; all bits unaffected by <math>\overline{RIU} = 0$ .

Bits 7 to 0: Guard Time Register Bits 7 to 0 (GTR.7 to GTR.0). These bits are used for storing the number of guard time units (ETU) requested during ATR. When

transmitting, the DS8007A UART delays these numbers of extra guard time ETU before transmitting a character written to UTR.

### **UART Control Register 1 (UCR1)**

|             | 7    | 6    | 5   | 4    | 3    | 2    | 1    | 0    |

|-------------|------|------|-----|------|------|------|------|------|

| Address 06h | FTE0 | FIP  | _   | PROT | T/R  | LCT  | SS   | CONV |

| _           | R-0  | RW-0 | R-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 |

R = unrestricted read, W = unrestricted write, -n = value after reset. This register is reset to 0uuu00uub on RIU = 0.

**Bit 7: FIFO Threshold Enable 0 (FTE0).** When this bit and the FTE1 (FCR.3) bit are set, the programmable FIFO threshold feature is enabled. This bit always reads 0 for compatibility.

**Bit 6: Force Inverse Parity (FIP).** When this bit is configured to 0, the correct parity is transmitted with each character, and receive characters are checked for the correct parity. When FIP = 1, an inverse parity bit is transmitted with each character and correctly received characters are NAK'd.

**Bit 5: Reserved.** This bit must be left 0. Setting this bit to 1 causes improper device operation.

**Bit 4: Protocol Select (PROT).** This bit is set to 1 by software to select the asynchronous T = 1 protocol and is cleared to 0 to select the T = 0 protocol.

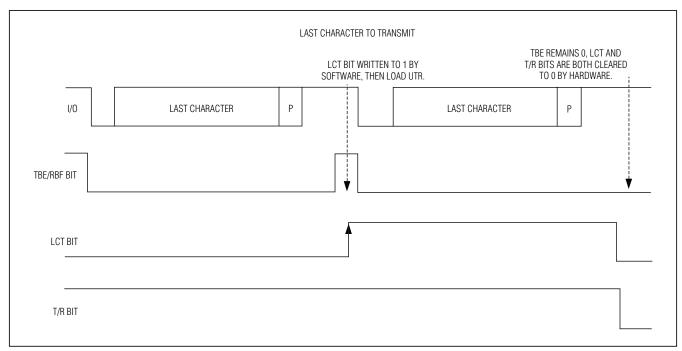

Bit 3: Transmit/Receive (T/R). This bit should be set by software to operate the UART in transmit mode. When this bit is changed from 0 to 1 (UART changed from receive to transmit mode), hardware sets the USR.RBF/TBE bit, indicating an empty transmit buffer. The T/R bit is automatically cleared to 0 following successful transmission if UCR1.LCT is configured to 1 prior to the transmission. This bit cannot be written to when  $\overline{RIU} = 0$  (holding in reset).

Bit 2: Last Character to Transmit (LCT). This bit is optionally set by software prior to writing the last character to be transmitted to the UART transmit register (UTR). If LCT is set to 1 prior to writing to UTR, hardware resets the LCT, T/R, and TBE/RBF bits following a successful transmission. Setting this bit to 1 allows automatic change to the reception mode after the last character is sent. This bit can be set during and before the transmission. This bit cannot be written to when  $\overline{RIU} = 0$  (holding in reset).

**Bit 1: Software Convention Setting (SS).** This bit should be set by software prior to ATR to allow automatic convention detection. Hardware automatically resets the SS bit at 10.5 ETU after the detection of the start bit of the first character of the ATR.

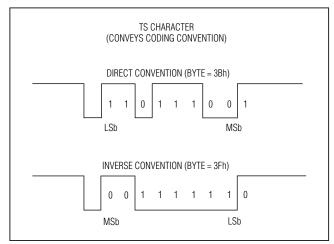

**Bit 0: Convention (CONV).** This bit defines the character decoding convention of the ISO UART. If CONV = 1, the convention is direct. If CONV = 0, the convention is inverted. If automatic convention detection is enabled  $(\overline{AUTOC} = 0)$ , hardware detects the character convention and configures the CONV bit appropriately at 10.5 ETU. Otherwise  $(\overline{AUTOC} = 1)$ , software must configure the CONV bit.

### Power Control Register (PCR)

|             | 7   | 6   | 5    | 4    | 3    | 2     | 1     | 0     |

|-------------|-----|-----|------|------|------|-------|-------|-------|

| Address 07h | _   | _   | C8   | C4   | 1V8  | RSTIN | 3V/5V | START |

| _           | R-0 | R-0 | RW-1 | RW-1 | RW-0 | RW-0  | RW-0  | RW-0  |

R = unrestricted read, W = unrestricted write, -n = value after reset. This register is reset to 0011uuuub on  $\overline{RIU} = 0$ .

**Note:** The AUX card interface does not have register PCR. C4 and C8 are external ports that are internally pulled up ( $10k\Omega$  to  $V_{CCX}$ ), writing a 1 to C4, C8 configures the weak pullup. Reads are made of the pin state to a different physical bit. Writing a 0 to C4, C8 configures the pulldown. C4 and C8 bits can be written irrespective of the state of the T/R bit.

#### Bits 7 and 6: Reserved.

**Bit 5: Contact 8 (C8).** Writes to this register bit are output on the C8 pin of the card interface. Reads of this register bit reflect the value on the C8 pin.

**Bit 4: Contact 4 (C4).** Writes to this register bit are output on the C4 pin of the card interface. Reads of this register bit reflect the value on the C4 pin.

Bit 3: 1.8V Card Select (1V8). If this bit is set to 1, the  $V_{CCX}$  supplied to the card interface is 1.8V. This bit overrides the 3V/5V bit.

**Bit 2: Reset Bit (RSTIN).** When a card interface is activated, the RSTx pin is driven according to the value contained in this register bit.

**Bit 1: 3V/5V Card Select (3V/5V).** This bit determines the  $V_{CCx}$  level for the card interface. When this bit is set to 1,  $V_{CCx}$  is defined as 3V. When this bit is cleared to 0,  $V_{CCx}$  is defined as 5V. When the 1V8 and 3V/5V bits are set to 1, priority is given to 1V8.