# **Audio, Dual-Matched NPN Transistor**

SSM2212

#### **FEATURES**

Very low voltage noise: 1 nV/√Hz maximum @ 100 Hz Excellent current gain match: 0.5% Low offset voltage (Vos): 200 µV maximum Outstanding offset voltage drift: 0.03 µV/°C High gain bandwidth product: 200 MHz

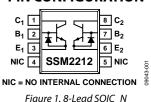

#### PIN CONFIGURATION

#### **GENERAL DESCRIPTION**

The SSM2212 is a dual, NPN-matched transistor pair that is specifically designed to meet the requirements of ultralow noise audio systems.

With its extremely low input base spreading resistance (rbb' is typically 28  $\Omega$ ) and high current gain (h<sub>FE</sub> typically exceeds 600 at I<sub>C</sub> = 1 mA), the SSM2212 can achieve outstanding signal-tonoise ratios. The high current gain results in superior performance compared to systems incorporating commercially available monolithic amplifiers.

Excellent matching of the current gain ( $\Delta h_{FE}$ ) to about 0.5% and low  $V_{OS}$  of less than 10  $\mu V$  typical make the SSM2212 ideal for symmetrically balanced designs, which reduce high-order amplifier harmonic distortion.

Stability of the matching parameters is guaranteed by protection diodes across the base-emitter junction. These diodes prevent degradation of beta and matching characteristics due to reverse biasing of the base-emitter junction.

The SSM2212 is also an ideal choice for accurate and reliable current biasing and mirroring circuits. Furthermore, because a current mirror's accuracy degrades exponentially with mismatches of V<sub>BE</sub> between transistor pairs, the low V<sub>OS</sub> of the SSM2212 does not need offset trimming in most circuit applications.

The SSM2212 performance and characteristics are guaranteed over the extended temperature range of -40°C to +85°C.

©2010 Analog Devices, Inc. All rights reserved.

# **TABLE OF CONTENTS**

6/10—Revision 0: Initial Version

| reatures                                                            | 1 |

|---------------------------------------------------------------------|---|

| Pin Configuration                                                   | 1 |

| General Description                                                 | 1 |

| Revision History                                                    | 2 |

| Specifications                                                      | 3 |

| Electrical Characteristics                                          | 3 |

| Absolute Maximum Ratings                                            | 4 |

| REVISION HISTORY                                                    |   |

| 7/ <b>10—Rev. A to Rev. B</b> Changes to Figure 1                   | 1 |

| 5/10—Rev. 0 to Rev. A Changes to Fast Logarithmic Amplifier Section | 8 |

| Thermal Resistance                  | 4 |

|-------------------------------------|---|

| ESD Caution                         | 4 |

| Typical Performance Characteristics | 5 |

| Applications Information            | 8 |

| Fast Logarithmic Amplifier          | 8 |

| Outline Dimensions                  | 9 |

| Ordering Guide                      | 9 |

|                                     |   |

## **SPECIFICATIONS**

#### **ELECTRICAL CHARACTERISTICS**

$V_{CB}$  = 15 V,  $I_O$  = 10  $\mu A$ ,  $T_A$  = 25°C, unless otherwise specified.

Table 1.

| Parameter                                 | Symbol                        | Text Conditions/Comments                                                                  | Min | Тур  | Max | Unit   |

|-------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------|-----|------|-----|--------|

| DC AND AC CHARACTERISTICS                 |                               |                                                                                           |     |      |     |        |

| Current Gain <sup>1</sup>                 | h <sub>FE</sub>               |                                                                                           |     |      |     |        |

|                                           |                               | $I_C = 1 \text{ mA}$                                                                      | 300 | 605  |     |        |

|                                           |                               | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$                     | 300 |      |     |        |

|                                           |                               | $I_C = 10 \mu A$                                                                          | 200 | 550  |     |        |

|                                           |                               | $-40$ °C $\leq T_A \leq +85$ °C                                                           | 200 |      |     |        |

| Current Gain Match <sup>2</sup>           | $\Delta h_{	extsf{FE}}$       | $10 \mu A \le I_C \le 1 mA$                                                               |     | 0.5  | 5   | %      |

| Noise Voltage Density <sup>3</sup>        | e <sub>N</sub>                | $I_C = 1 \text{ mA, } V_{CB} = 0 \text{ V}$                                               |     |      |     |        |

|                                           |                               | $f_0 = 10 \text{ Hz}$                                                                     |     | 1.6  | 2   | nV/√Hz |

|                                           |                               | $f_0 = 100 \text{ Hz}$                                                                    |     | 0.9  | 1   | nV/√Hz |

|                                           |                               | $f_0 = 1 \text{ kHz}$                                                                     |     | 0.85 | 1   | nV/√Hz |

|                                           |                               | $f_0 = 10 \text{ kHz}$                                                                    |     | 0.85 | 1   | nV/√Hz |

| Low Frequency Noise (0.1 Hz to 10 Hz)     | e <sub>N</sub> p-p            | $I_C = 1 \text{ mA}$                                                                      |     | 0.4  |     | μV p-p |

| Offset Voltage                            | Vos                           | $V_{CB} = 0 \text{ V, } I_{C} = 1 \text{ mA}$                                             |     | 10   | 200 | μV     |

|                                           |                               | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$                     |     |      | 220 | μV     |

| Offset Voltage Change vs. V <sub>CB</sub> | $\Delta V_{OS}/\Delta V_{CB}$ | $0 \text{ V} \le V_{CB} \le V_{MAX}^4, 1  \mu A \le I_C \le 1  mA^5$                      |     | 10   | 50  | μV     |

| Offset Voltage Change vs. Ic              | $\Delta V_{OS}/\Delta I_{C}$  | $1 \mu A \le I_C \le 1 mA^5, V_{CB} = 0 V$                                                |     | 5    | 70  | μV     |

| Offset Voltage Drift                      | $\Delta V_{OS}/\Delta T$      | $-40$ °C $\leq T_A \leq +85$ °C                                                           |     | 0.08 | 1   | μV/°C  |

|                                           |                               | $-40^{\circ}\text{C} \le T_A \le +85^{\circ}\text{C}$ , $V_{OS}$ trimmed to $0 \text{ V}$ |     | 0.03 | 0.3 | μV/°C  |

| Breakdown Voltage                         | $BV_CEO$                      |                                                                                           | 40  |      |     | V      |

| Gain Bandwidth Product                    | f⊤                            | $I_C = 100 \text{ mA}, V_{CE} = 10 \text{ V}$                                             |     | 200  |     | MHz    |

| Collector-to-Base Leakage Current         | I <sub>CBO</sub>              | $V_{CB} = V_{MAX}$                                                                        |     | 25   | 500 | рА     |

| -                                         |                               | $-40^{\circ}\text{C} \le \text{T}_{A} \le +85^{\circ}\text{C}$                            |     | 3    |     | nA     |

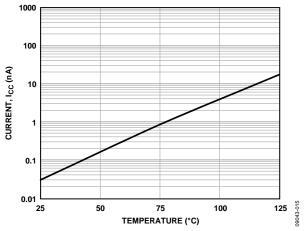

| Collector-to-Collector Leakage Current    | I <sub>CC</sub>               | $V_{CC} = V_{MAX}^{6,7}$                                                                  |     | 35   | 500 | рА     |

| _                                         |                               | $-40^{\circ}\text{C} \le \text{T}_{A} \le +85^{\circ}\text{C}$                            |     | 4    |     | nA     |

| Collector-to-Emitter Leakage Current      | I <sub>CES</sub>              | $V_{CE} = V_{MAX}, V_{BE} = 0 V^{6,7}$                                                    |     | 35   | 500 | рА     |

| _                                         |                               | $-40^{\circ}\text{C} \le \text{T}_{A} \le +85^{\circ}\text{C}$                            |     | 4    |     | nA     |

| Input Bias Current                        | I <sub>B</sub>                | $I_C = 10 \mu A$                                                                          |     |      | 50  | nA     |

| ·                                         |                               | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$                     |     |      | 50  | nA     |

| Input Offset Current                      | los                           | $I_C = 10 \mu A$                                                                          |     |      | 6.2 | nA     |

| ·                                         |                               | -40°C ≤ T <sub>A</sub> ≤ +85°C                                                            |     |      | 13  | nA     |

| Input Offset Current Drift                | ΔΙος/ΔΤ                       | $I_C = 10 \mu A^6, -40^{\circ}C \le T_A \le +85^{\circ}C$                                 |     | 40   | 150 | pA/°C  |

| Collector Saturation Voltage              | V <sub>CE (SAT)</sub>         | $I_C = 1 \text{ mA}, I_B = 100 \mu\text{A}$                                               |     | 0.05 | 0.2 | V      |

| Output Capacitance                        | Сов                           | $V_{CB} = 15 \text{ V}, I_E = 0 \mu\text{A}$                                              |     | 23   |     | pF     |

| Bulk Resistance                           | R <sub>BE</sub>               | $10 \mu\text{A} \le I_{\text{C}} \le 10 \text{mA}^{6}$                                    |     | 0.3  | 1.6 | Ω      |

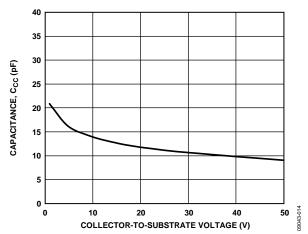

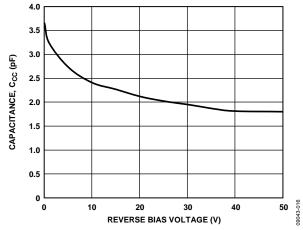

| Collector-to-Collector Capacitance        | Ccc                           | V <sub>CC</sub> = 0 V                                                                     |     | 35   |     | pF     |

$<sup>^1</sup>$  Current gain is guaranteed with collector-to-base voltage (V\_CB) swept from 0 V to V\_MAX at the indicated collector currents.  $^2$  Current gain match ( $\Delta h_{FE}$ ) is defined as follows:  $\Delta h_{FE} = (100(\Delta l_B)(h_{FE\,min})/l_C)$ .

<sup>&</sup>lt;sup>3</sup> Noise voltage density is guaranteed, but not 100% tested.

$<sup>^4</sup>$  This is the maximum change in  $V_{OS}$  as  $V_{CB}$  is swept from 0 V to 40 V.

$<sup>^5</sup>$  Measured at  $I_C$  = 10  $\mu A$  and guaranteed by design over the specified range of  $I_C$

<sup>6</sup> Guaranteed by design.

7 I<sub>CC</sub> and I<sub>CES</sub> are verified by measurement of I<sub>CBO</sub>.

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                                              | Rating          |

|------------------------------------------------------------------------|-----------------|

| Breakdown Voltage of Collector-to-Base Voltage (BV <sub>CBO</sub> )    | 40 V            |

| Breakdown Voltage of Collector-to-Emitter Voltage (BV <sub>CEO</sub> ) | 40 V            |

| Breakdown Voltage of Collector-to-Collector Voltage (BVcc)             | 40 V            |

| Breakdown Voltage of Emitter-to-Emitter Voltage (BV <sub>EE</sub> )    | 40 V            |

| Collector Current (Ic)                                                 | 20 mA           |

| Emitter Current (I <sub>E</sub> )                                      | 20 mA           |

| Storage Temperature Range                                              | −65°C to +150°C |

| Operating Temperature Range                                            | -40°C to +85°C  |

| Junction Temperature Range                                             | −65°C to +150°C |

| Lead Temperature (Soldering, 60 sec)                                   | 300°C           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Table 3. Thermal Resistance

| Package Type      | θја | θις | Unit |

|-------------------|-----|-----|------|

| 8-Lead SOIC (R-8) | 120 | 45  | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## TYPICAL PERFORMANCE CHARACTERISTICS

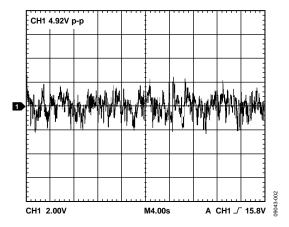

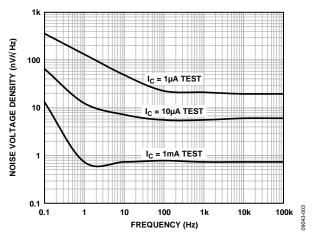

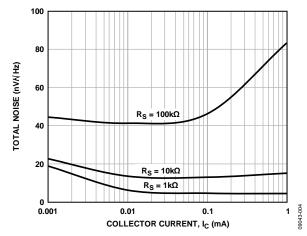

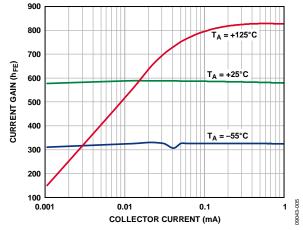

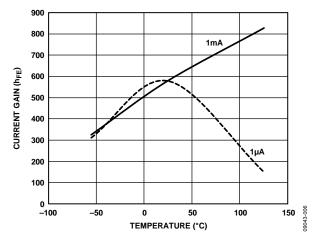

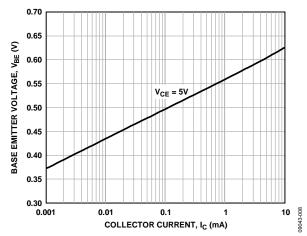

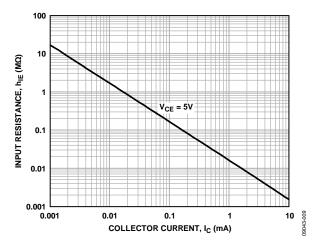

$T_A = 25$ °C,  $V_{CE} = 5$  V, unless otherwise specified.

Figure 2. Low Frequency Noise (0.1 Hz to 10 Hz),  $I_c = 1$  mA, Gain = 10,000,000

Figure 3. Noise Voltage Density vs. Frequency

Figure 4. Total Noise vs. Collector Current, f = 1 kHz

Figure 5. Current Gain vs. Collector Current ( $V_{CB} = 0 V$ )

Figure 6. Current Gain vs. Temperature (Excludes ICBO)

Figure 7. Base Emitter Voltage vs. Collector Current

Figure 8. Small Signal Input Resistance vs. Collector Current

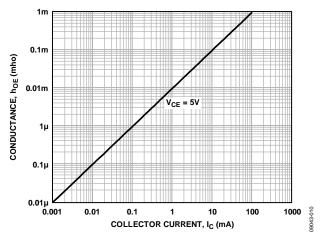

Figure 9. Small Signal Output Conductance vs. Collector Current

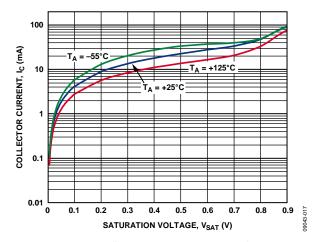

Figure 10. Collector Current vs. Saturation Voltage

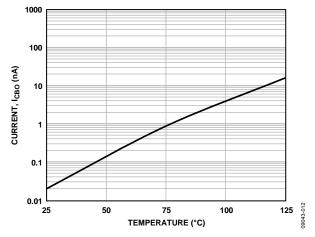

Figure 11. Collector-to-Base Leakage Current vs. Temperature

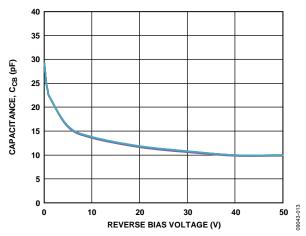

Figure 12. Collector-to-Base Capacitance vs. Reverse Bias Voltage

Figure 13. Collector-to-Collector Capacitance vs. Collector-to-Substrate Voltage

Figure 14. Collector-to-Collector Leakage Current vs. Temperature

Figure 15. Collector-to-Collector Capacitance vs. Reverse Bias Voltage

## APPLICATIONS INFORMATION

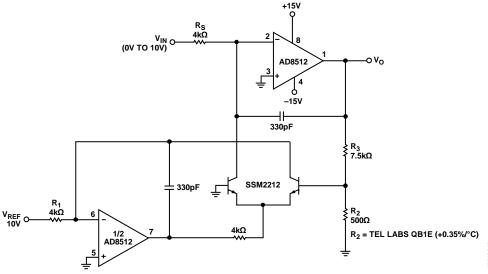

#### **FAST LOGARITHMIC AMPLIFIER**

The circuit of Figure 16 is a modification of a standard logarithmic amplifier configuration. Running the SSM2212 at 2.5 mA per side (full-scale) allows for a fast response with a wide dynamic range. The circuit has a 7 decade current range and a 5 decade voltage range, and it is capable of 2.5  $\mu s$  settling time to 1% with a 1 V to 10 V step. The output follows the equation:

$$V_{O} = \frac{R3 + R2}{R2} \frac{kT}{q} \ln \frac{V_{REF}}{V_{IN}}$$

To compensate for the temperature dependence of the kT/q term, a resistor with a positive 0.35%/°C temperature coefficient is chosen for  $R_2$ . The output is inverted with respect to the input and is nominally -1 V/decade using the component values indicated.

Figure 16. Fast Logarithmic Amplifier

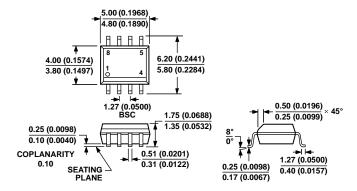

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 17. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                            | Package Option |

|--------------------|-------------------|------------------------------------------------|----------------|

| SSM2212RZ          | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| SSM2212RZ-R7       | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| SSM2212RZ-RL       | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

**NOTES**

# **NOTES**

NOTES

# AMEYA360 Components Supply Platform

## **Authorized Distribution Brand:**

## Website:

Welcome to visit www.ameya360.com

## Contact Us:

## > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

## > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

## Customer Service :

Email service@ameya360.com

## Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com