# SLRC400

## **ICODE** reader IC

Rev. 3.3 — 23 March 2010 054333

Product data sheet PUBLIC

### 1. Introduction

This data sheet describes the functionality of the SLRC400 Integrated Circuit (IC). It includes the functional and electrical specifications and from a system and hardware viewpoint gives detailed information on how to design-in the device.

## 2. General description

The SLRC400 is a member of a new family of highly integrated reader ICs for contactless communication at 13.56 MHz. This family of reader ICs provide:

- outstanding modulation and demodulation for passive contactless communication

- a wide range of methods and protocols

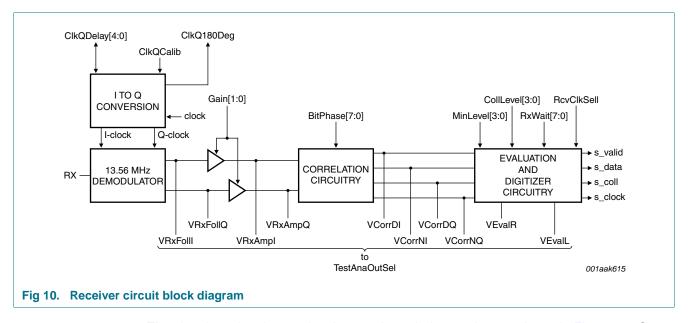

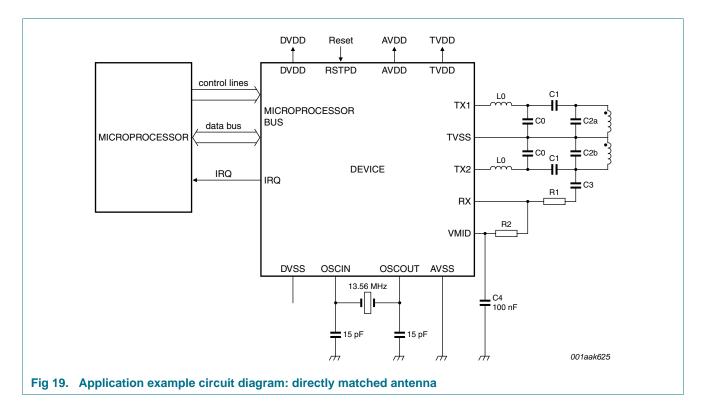

The transmitter module <u>Section 8.9 on page 24</u> can directly drive an antenna designed for proximity operating distance up to 100 mm without additional active circuitry. The receiver module provides a robust and efficient demodulation/decoding circuitry implementation for compatible transponder signals (see <u>Section 8.10 on page 28</u>).

All layers of the ICODE1 and ISO/IEC 15693 protocols are supported. The receiver module provides a robust and efficient demodulation/decoding circuitry implementation for ICODE1 and ISO/IEC 15693 compatible transponder signals. The digital module manages ICODE1 and ISO/IEC 15693 framing and error detection (CRC).

A parallel interface can be directly connected to any 8-bit microprocessor to ensure reader/terminal design flexibility.

## 3. Features and benefits

#### 3.1 General

- Highly integrated analog circuitry for demodulating and decoding label response

- Buffered output drivers enable antenna connection using the minimum of external components

- Proximity operating distance up to 100 mm

- Supports both ICODE1 and ISO/IEC 15693 protocols

- Parallel microprocessor interface with internal address latch and IRQ line

- Flexible interrupt handling

- Automatic detection of parallel microprocessor interface type

- 64-byte send and receive FIFO buffer

- Hard reset with low power function

- Software controlled Power-down mode

- Programmable timer

- Unique serial number

- User programmable start-up configuration

- Bit-oriented and byte oriented framing

- Independent power supply pins for analog, digital and transmitter modules

- Internal oscillator buffer optimized for low phase jitter enables 13.56 MHz quartz connection

- Clock frequency filtering

- 3.3 V operation for transmitter (antenna driver) in short range and proximity applications

## 4. Applications

- Electronic payment systems

- Identification systems

- Access control systems

- Subscriber services

- Banking systems

- Digital content systems

## 5. Ordering information

Table 1. Ordering information

| Type number    | Package |                                                            |          |  |  |  |  |

|----------------|---------|------------------------------------------------------------|----------|--|--|--|--|

|                | Name    | Description                                                | Version  |  |  |  |  |

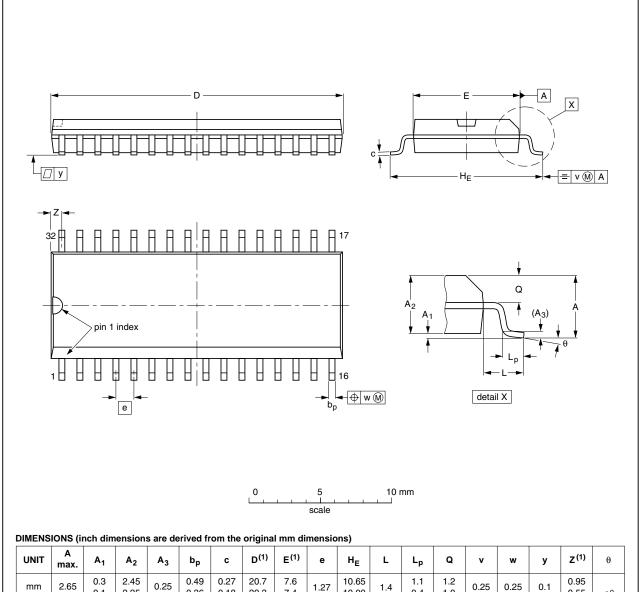

| SLRC40001T/0FE | SO32    | plastic small outline package; 32 leads; body width 7.5 mm | SOT287-1 |  |  |  |  |

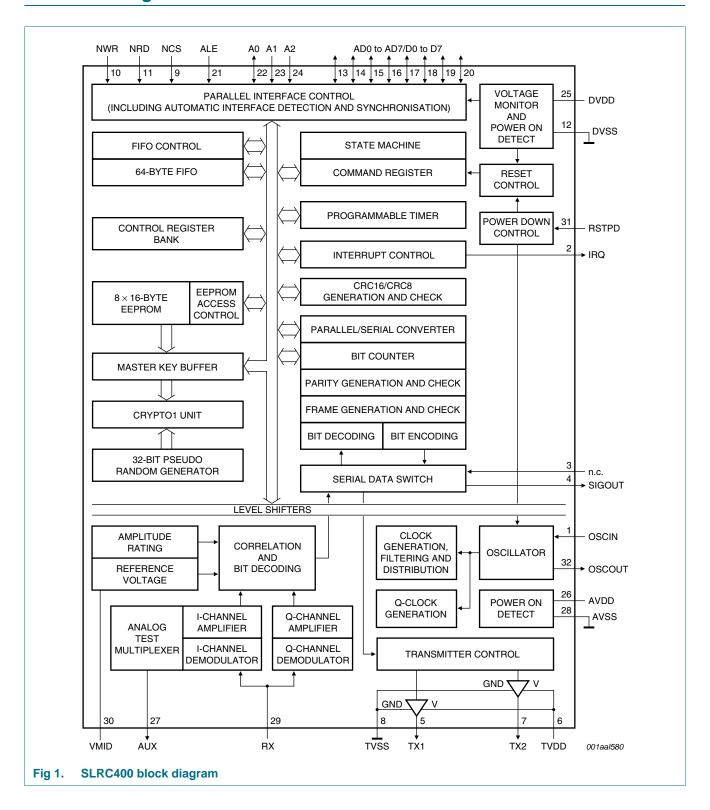

## 6. Block diagram

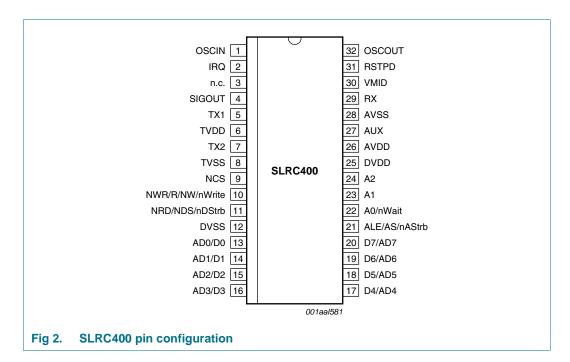

## 7. Pinning information

## 7.1 Pin description

Table 2. Pin description

| Pin   | Symbol | Type <sup>[1]</sup> | Description                                                                                            |

|-------|--------|---------------------|--------------------------------------------------------------------------------------------------------|

| 1     | OSCIN  | I                   | oscillator or clock input:                                                                             |

|       |        |                     | crystal oscillator input to the oscillator's inverting amplifier                                       |

|       |        |                     | externally generated clock input; $f_{osc} = 13.56 \text{ MHz}$                                        |

| 2     | IRQ    | 0                   | interrupt request output signals an interrupt event                                                    |

| 3     | n.c.   | I                   | connect this pin to ground                                                                             |

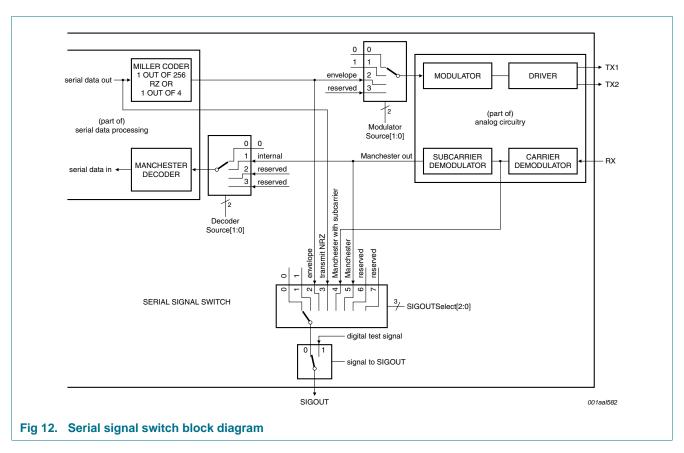

| 4     | SIGOUT | 0                   | ICODE interface serial data output based on ICODE1 and ISO/IEC 15693                                   |

| 5     | TX1    | 0                   | transmitter 1 modulated carrier output; 13.56 MHz                                                      |

| 6     | TVDD   | Р                   | power supply for transmitter output stage pins TX1 and TX2                                             |

| 7     | TX2    | 0                   | transmitter 2 modulated carrier output; 13.56 MHz                                                      |

| 8     | TVSS   | G                   | transmitter ground for the TX1 and TX2 output stages                                                   |

| 9     | NCS    | I                   | not chip select input selects and activates the SLRC400's microprocessor interface                     |

| 10[2] | NWR    | I                   | not write input strobe signal for writing data to the SLRC400 registers when applied to pins D0 to D7  |

|       | R/NW   | I                   | read not write input indicates that a read or a write cycle must be performed                          |

|       | nWrite | I                   | not write input indicates that a read or a write cycle must be performed                               |

| 11[2] | NRD    | I                   | not read input strobe signal for reading data from the SLRC400 registers when applied to pins D0 to D7 |

|       | NDS    | I                   | not data strobe input strobe signal for read and write cycles                                          |

|       | nDStrb | I                   | not data strobe input strobe signal for read and write cycles                                          |

SLRC400\_33

All information provided in this document is subject to legal disclaimers.

Table 2. Pin description ...continued

| 10010 21                | accompact  |                     |                                                                                                                               |

|-------------------------|------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Pin                     | Symbol     | Type <sup>[1]</sup> | Description                                                                                                                   |

| 12                      | DVSS       | G                   | digital ground                                                                                                                |

| 13 to 20 <sup>[2]</sup> | D0 to D7   | I/O                 | 8-bit bidirectional data bus input/output on pins D0 to D7                                                                    |

|                         | AD0 to AD7 | I/O                 | 8-bit bidirectional address and data bus input/output on pins AD0 to AD7                                                      |

| 21[2]                   | ALE        | I                   | address latch enable input for pins AD0 to AD5; HIGH latches the internal address                                             |

|                         | AS         | I                   | address strobe input for pins AD0 to AD5; HIGH latches the internal address                                                   |

|                         | nAStrb     | I                   | not address strobe input for pins AD0 to AD5; LOW latches the internal address                                                |

| 22[2]                   | A0         | I                   | address line 0 is the address register bit 0 input                                                                            |

|                         | nWait      | 0                   | not wait output:                                                                                                              |

|                         |            |                     | LOW starts an access cycle                                                                                                    |

|                         |            |                     | HIGH ends an access cycle                                                                                                     |

| 23                      | A1         | I                   | address line 1 is the address register bit 1 input                                                                            |

| 24                      | A2         | I                   | address line 2 is the address register bit 2 input                                                                            |

| 25                      | DVDD       | Р                   | digital power supply                                                                                                          |

| 26                      | AVDD       | Р                   | analog power supply for pins OSCIN, AUX, RX, VMID and OSCOUT                                                                  |

| 27                      | AUX        | 0                   | auxiliary analog test signal output. The output signal is selected using the TestAnaSelect register's TestAnaOutSel[4:0] bits |

| 28                      | AVSS       | G                   | analog ground                                                                                                                 |

| 29                      | RX         | I                   | receiver input for the label response. The carrier is load modulated at 13.56 MHz, taken from the antenna circuit             |

| 30                      | VMID       | Р                   | internal reference voltage: provides the internal reference voltage as a supply                                               |

|                         |            |                     | Remark: It must be connected to ground using a 100 nF block capacitor.                                                        |

| 31                      | RSTPD      | I                   | reset and power-down input:                                                                                                   |

|                         |            |                     | HIGH: switches off the internal current sinks, inhibits the oscillator and disconnects the input pads                         |

|                         |            |                     | LOW (negative edge): starts the internal reset phase                                                                          |

| 32                      | OSCOUT     | 0                   | crystal oscillator output for the oscillator's inverting amplifier                                                            |

|                         |            |                     |                                                                                                                               |

<sup>[1]</sup> Pin types: I = Input, O = Output, I/O = Input/Output, P = Power and G = Ground.

<sup>[2]</sup> These pins provide different functionality depending on the selected microprocessor interface type (see <u>Section 8.1 on page 6</u> for detailed information).

## 8. Functional description

## 8.1 Digital interface

## 8.1.1 Overview of supported microprocessor interfaces

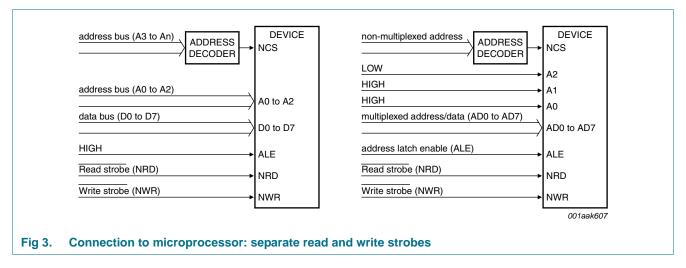

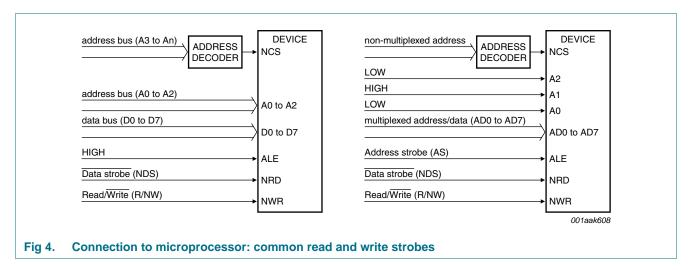

The SLRC400 supports direct interfacing to various 8-bit microprocessors. Alternatively, the SLRC400 can be connected to a PC's Enhanced Parallel Port (EPP). <u>Table 3</u> shows the parallel interface signals supported by the SLRC400.

Table 3. Supported microprocessor and EPP interface signals

|                                             |         |                                | 3                                |

|---------------------------------------------|---------|--------------------------------|----------------------------------|

| Bus control signals                         | Bus     | Separated address and data bus | Multiplexed address and data bus |

| Separated read and write strobes            | control | NRD, NWR, NCS                  | NRD, NWR, NCS, ALE               |

|                                             | address | A0, A1, A2                     | AD0, AD1, AD2, AD3, AD4, AD5     |

|                                             | data    | D0 to D7                       | AD0 to AD7                       |

| Common read and write strobe                | control | R/NW, NDS, NCS                 | R/NW, NDS, NCS, AS               |

|                                             | address | A0, A1, A2                     | AD0, AD1, AD2, AD3, AD4, AD5     |

|                                             | data    | D0 to D7                       | AD0 to AD7                       |

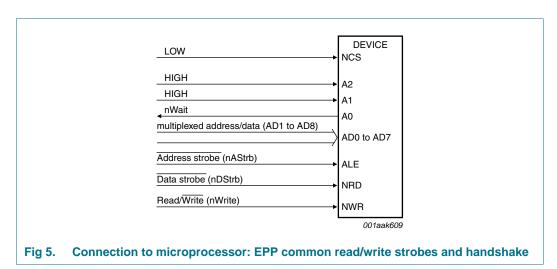

| Common read and write strobe with handshake | control | -                              | nWrite, nDStrb, nAStrb, nWait    |

| (EPP)                                       | address | -                              | AD0, AD1, AD2, AD3, AD4, AD5     |

|                                             | data    | -                              | AD0 to AD7                       |

## 8.1.2 Automatic microprocessor interface detection

After a Power-On or Hard reset, the SLRC400 resets parallel microprocessor interface mode and detects the microprocessor interface type.

The SLRC400 identifies the microprocessor interface using the logic levels on the control pins after the reset phase. This is performed using a combination of fixed pin connections and the dedicated Initialization routine (see Section 8.7.4 on page 23).

## 8.1.3 Connection to different microprocessor types

The connection to various microprocessor types is shown in Table 4.

Table 4. Connection scheme for detecting the parallel interface type

| SLRC400  | Parallel interface type and signals |                         |                          |                         |                                        |  |  |  |  |  |

|----------|-------------------------------------|-------------------------|--------------------------|-------------------------|----------------------------------------|--|--|--|--|--|

| pins     | Separated read                      | /write strobe           | Common read/write strobe |                         |                                        |  |  |  |  |  |

|          | Dedicated address bus               | Multiplexed address bus | Dedicated address bus    | Multiplexed address bus | Multiplexed address bus with handshake |  |  |  |  |  |

| ALE      | HIGH                                | ALE                     | HIGH                     | AS                      | nAStrb                                 |  |  |  |  |  |

| A2       | A2                                  | LOW                     | A2                       | LOW                     | HIGH                                   |  |  |  |  |  |

| A1       | A1                                  | HIGH                    | A1                       | HIGH                    | HIGH                                   |  |  |  |  |  |

| A0       | A0                                  | HIGH                    | A0                       | LOW                     | nWait                                  |  |  |  |  |  |

| NRD      | NRD                                 | NRD                     | NDS                      | NDS                     | nDStrb                                 |  |  |  |  |  |

| NWR      | NWR                                 | NWR                     | R/NW                     | R/NW                    | nWrite                                 |  |  |  |  |  |

| NCS      | NCS                                 | NCS                     | NCS                      | NCS                     | LOW                                    |  |  |  |  |  |

| D7 to D0 | D7 to D0                            | AD7 to AD0              | D7 to D0                 | AD7 to AD0              | AD7 to AD0                             |  |  |  |  |  |

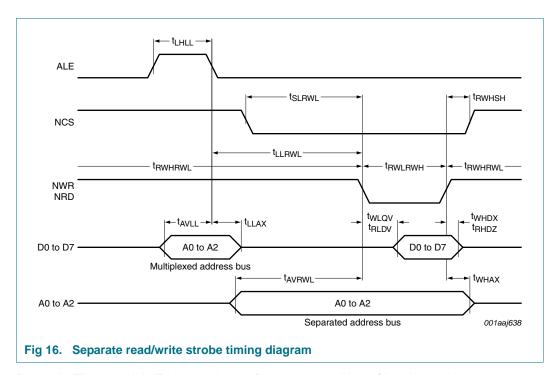

## 8.1.3.1 Separate read and write strobe

Refer to Section 12.4.1 on page 80 for timing specification.

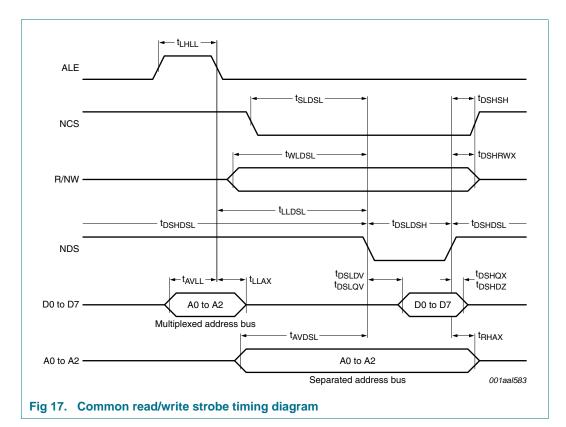

#### 8.1.3.2 Common read and write strobe

Refer to Section 12.4.2 on page 81 for timing specification.

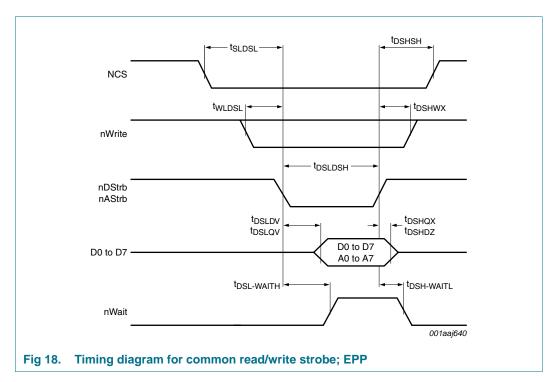

#### 8.1.3.3 Common read and write strobe: EPP with handshake

Refer to Section 12.4.3 on page 82 for timing specification.

**Remark:** In the EPP standard a chip select signal is not defined. To cover this situation, the status of the NCS pin can be used to inhibit the nDStrb signal. If this inhibitor is not used, it is mandatory that pin NCS is connected to pin DVSS.

**Remark:** After each Power-On or Hard reset, the nWait signal on pin A0 is high-impedance. nWait is defined as the first negative edge applied to the nAStrb pin after the reset phase. The SLRC400 does not support Read Address Cycle.

## 8.2 Memory organization of the EEPROM

Table 5. EEPROM memory organization diagram

| Block    |         | Byte       | Access | Memory content                                                             | Refer to                          |  |  |

|----------|---------|------------|--------|----------------------------------------------------------------------------|-----------------------------------|--|--|

| Position | Address | address    |        |                                                                            |                                   |  |  |

| 0        | 0       | 00h to 0Fh | R      | product information field                                                  | Section 8.2.1 on page 9           |  |  |

| 1        | 1       | 10h to 1Fh | R/W    | StartUp register                                                           | Section 8.2.2.1 on page 10        |  |  |

| 2        | 2       | 20h to 2Fh | R/W    | initialization file                                                        |                                   |  |  |

| 3        | 3       | 30h to 3Fh | R/W    | register                                                                   | Section 8.2.2.3 "Register         |  |  |

| 4        | 4       | 40h to 4Fh | R/W    | initialization file initialization file (reconstruction on page 12) second | initialization file (read/write)" |  |  |

| 5        | 5       | 50h to 5Fh | R/W    |                                                                            | on page 12                        |  |  |

| 6        | 6       | 60h to 6Fh | R/W    | initialization                                                             |                                   |  |  |

| 7        | 7       | 70h to 7Fh | R/W    |                                                                            |                                   |  |  |

Remark: It is recommend to use only the above EEPROM address area.

## 8.2.1 Product information field (read only)

Table 6. Product information field byte allocation

| Byte   | 15  | 14     | 13   | 12   | 11   | 10       | 9       | 8    | 7 | 6      | 5  | 4   | 3       | 2       | 1         | 0  |

|--------|-----|--------|------|------|------|----------|---------|------|---|--------|----|-----|---------|---------|-----------|----|

| Symbol | CRC | RsMaxP | Inte | rnal | Prod | duct Ser | ial Nun | nber | R | eserve | ed | Pro | duct Ty | pe Ider | ntificati | on |

| Access | R   | R      | F    | ₹    |      | F        | }       |      |   | R      |    |     |         | R       |           |    |

Table 7. Product information field

| Table 1. | i roduct imormation neid    |        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-----------------------------|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Byte     | Symbol                      | Access | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15       | CRC                         | R      | -     | the content of the product information field is secured using a CRC byte which is checked during start-up                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14       | RsMaxP                      | R      | -     | maximum source resistance for the p-channel driver transistor on pins TX1 and TX2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |                             |        |       | The source resistance of the p-channel driver transistors of pin TX1 and TX2 can be adjusted using the value GsCfgCW[5:0] in the CwConductance register (see Section 8.9.3 on page 25). The mean value of the maximum adjustable source resistance for pins TX1 and TX2 is stored as an integer value in $\Omega$ in this byte. Typical values for RsMaxP are between 60 $\Omega$ to 140 $\Omega$ . This value is denoted as maximum adjustable source resistance $R_{S(ref)maxP}$ and is measured by setting the CwConductance register's GsCfgCW[5:0] bits to 01h. |

| 13 to 12 | Internal                    | R      | -     | two bytes for internal trimming parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11 to 8  | Product Serial Number       | R      | -     | a unique four byte serial number for the device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7 to 5   | reserved                    | R      | -     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4 to 0   | Product Type Identification | R      | -     | the SLRC400 is a member of a new family of highly integrated reader ICs. Each member of the product family has a unique product type identification. The value of the product type identification is shown in <u>Table 8</u> .                                                                                                                                                                                                                                                                                                                                       |

Table 8. Product type identification definition

| Definition | Product type identification bytes |     |     |     |              |  |  |  |

|------------|-----------------------------------|-----|-----|-----|--------------|--|--|--|

| Byte       | 0                                 | 1   | 2   | 3   | 4 <u>[1]</u> |  |  |  |

| Value      | 30h                               | 33h | F1h | 00h | XXh          |  |  |  |

<sup>[1]</sup> Byte 4 contains the current version number.

### 8.2.2 Register initialization file (read/write)

Register initialization from address 10h to address 2Fh is performed automatically during the initializing phase (see <u>Section 8.7.3 on page 23</u>) using the StartUp register initialization file.

In addition, the SLRC400 registers can be initialized using values from the StartUp register initialization file when the LoadConfig command is executed (see <u>Section 10.4.1</u> on page 75).

**Remark:** The following points apply to initialization:

- the Page register (addressed using 10h, 18h, 20h, 28h) is skipped and not initialized.

- make sure that all PreSetxx registers are not changed.

- make sure that all register bits that are reserved are set to logic 0.

### 8.2.2.1 StartUp register initialization file (read/write)

The EEPROM memory block address 1 and 2 contents are used to automatically set the register subaddresses 10h to 2Fh during the initialization phase. The default values stored in the EEPROM during production are shown in <a href="Section 8.2.2.2">Section 8.2.2.2</a> "Factory default StartUp register initialization file".

The byte assignment is shown in Table 9.

Table 9. Byte assignment for register initialization at start-up

| EEPROM byte address    | Register address | Remark  |

|------------------------|------------------|---------|

| 10h (block 1, byte 0)  | 10h              | skipped |

| 11h                    | 11h              | copied  |

|                        |                  |         |

| 2Fh (block 2, byte 15) | 2Fh              | copied  |

### 8.2.2.2 Factory default StartUp register initialization file

During the production tests, the StartUp register initialization file is initialized using the default values shown in <u>Table 10</u>. During each power-up and initialization phase, these values are written to the SLRC400's registers.

Table 10. Shipment content of StartUp register initialization file

| Table 10.                 | Silipilieni      | Content | t or Startop register in | itialization nie                                                                                                             |

|---------------------------|------------------|---------|--------------------------|------------------------------------------------------------------------------------------------------------------------------|

| EEPROM<br>byte<br>address | Register address | Value   | Symbol                   | Description                                                                                                                  |

| 10h                       | 10h              | 00h     | Page                     | free for user                                                                                                                |

| 11h                       | 11h              | 58h     | TxControl                | transmitter pins TX1 and TX2 are switched off, bridge driver configuration, modulator driven from internal digital circuitry |

| 12h                       | 12h              | 3Fh     | CwConductance            | source resistance of TX1 and TX2 is set to minimum                                                                           |

| 13h                       | 13h              | 05h     | ModGsCfg                 | source resistance of TX1 and TX2 at modulation to determine the modulation index                                             |

| 14h                       | 14h              | 2Ch     | CoderControl             | selects the bit coding mode and framing during transmission                                                                  |

| 15h                       | 15h              | 3Fh     | ModWidth                 | pulse width for used code (1 out of 256 RZ or 1 out of 4); pulse coding is set to standard configuration                     |

| 16h                       | 16h              | 3Fh     | ModWidthSOF              | pulse width of Start Of Frame (SOF)                                                                                          |

| 17h                       | 17h              | 00h     | PreSet17                 | -                                                                                                                            |

| 18h                       | 18h              | 00h     | Page                     | free for user                                                                                                                |

| 19h                       | 19h              | 8Bh     | RxControl1               | internal amplifier gain is maximum                                                                                           |

| 1Ah                       | 1Ah              | 00h     | DecoderControl           | bit-collisions always evaluate to HIGH in the data bit stream                                                                |

| 1Bh                       | 1Bh              | 54h     | BitPhase                 | BitPhase[7:0] is set to standard configuration                                                                               |

| 1Ch                       | 1Ch              | 68h     | RxThreshold              | MinLevel[3:0] and CollLevel[3:0] are set to maximum                                                                          |

| 1Dh                       | 1Dh              | 00h     | PreSet1D                 | -                                                                                                                            |

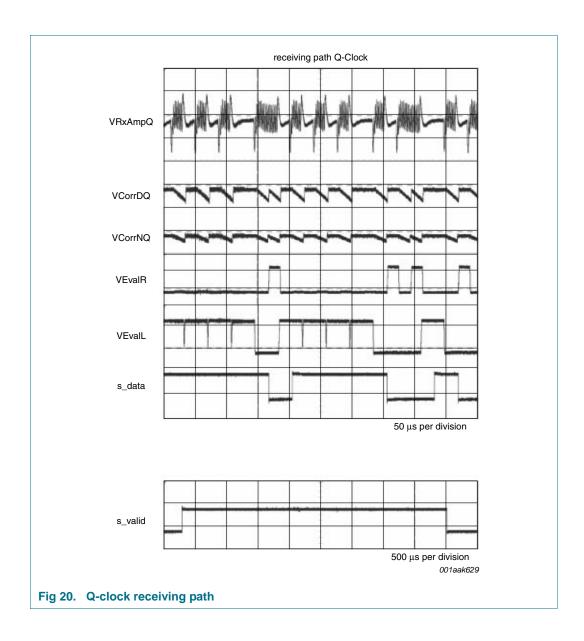

| 1Eh                       | 1Eh              | 41h     | RxControl2               | use Q-clock for the receiver, automatic receiver off is switched on, decoder is driven from internal analog circuitry        |

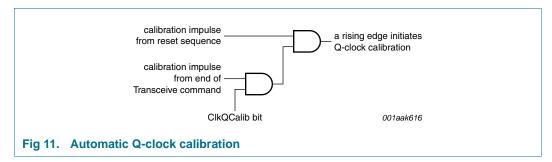

| 1Fh                       | 1Fh              | 00h     | ClockQControl            | automatic Q-clock calibration is switched on                                                                                 |

| 20h                       | 20h              | 00h     | Page                     | free for user                                                                                                                |

| 21h                       | 21h              | 08h     | RxWait                   | frame guard time is set to eight bit-clocks                                                                                  |

| 22h                       | 22h              | 0Ch     | ChannelRedundancy        | channel redundancy is set in accordance with ICODE1                                                                          |

| 23h                       | 23h              | FEh     | CRCPresetLSB             | CRC preset value is set in accordance with ICODE1                                                                            |

| 24h                       | 24h              | FFh     | CRCPresetMSB             | CRC preset value is set in accordance with ICODE1                                                                            |

| 25h                       | 25h              | 00h     | PreSet25                 | -                                                                                                                            |

| 26h                       | 26h              | 00h     | SIGOUTSelect             | pin SIGOUT is set LOW                                                                                                        |

| 27h                       | 27h              | 00h     | PreSet27                 | -                                                                                                                            |

| 28h                       | 28h              | 00h     | Page                     | free for user                                                                                                                |

| 29h                       | 29h              | 3Eh     | FIFOLevel                | WaterLevel[5:0] FIFO buffer warning level is set to standard configuration                                                   |

| 2Ah                       | 2Ah              | 0Bh     | TimerClock               | TPreScaler[4:0] is set to standard configuration, timer unit restart function is switched off                                |

| 2Bh                       | 2Bh              | 02h     | TimerControl             | Timer is started at the end of transmission, stopped at the beginning of reception                                           |

| 2Ch                       | 2Ch              | 00h     | TimerReload              | TReloadValue[7:0]: the timer unit preset value is set to standard configuration                                              |

| 2Dh                       | 2Dh              | 02h     | IRQPinConfig             | pin IRQ is set to high-impedance                                                                                             |

| 2Eh                       | 2Eh              | 00h     | PreSet2E                 | -                                                                                                                            |

| 2Fh                       | 2Fh              | 00h     | PreSet2F                 | -                                                                                                                            |

|                           |                  |         |                          |                                                                                                                              |

#### 8.2.2.3 Register initialization file (read/write)

The EEPROM memory content from block address 3 to 7 can initialize register sub addresses 10h to 2Fh when the LoadConfig command is executed (see <u>Section 10.4.1 on page 75</u>). This command requires the EEPROM starting byte address as a two byte argument for the initialization procedure.

The byte assignment is shown in Table 11.

Table 11. Byte assignment for register initialization at StartUp

| EEPROM byte address               | Register address | Remark  |

|-----------------------------------|------------------|---------|

| EEPROM starting byte address      | 10h              | skipped |

| EEPROM + 1 starting byte address  | 11h              | copied  |

|                                   |                  |         |

| EEPROM + 31 starting byte address | 2Fh              | copied  |

The register initialization file is large enough to hold values for two initialization sets and up to one block (16-byte) of user data.

**Remark:** The register initialization file can be read/written by users and these bytes can be used to store other user data.

## 8.3 FIFO buffer

An  $8 \times 64$  bit FIFO buffer is used in the SLRC400 to act as a parallel-to-parallel converter. It buffers both the input and output data streams between the microprocessor and the internal circuitry of the SLRC400. This makes it possible to manage data streams up to 64 bytes long without needing to take timing constraints into account.

#### 8.3.1 Accessing the FIFO buffer

#### 8.3.1.1 Access rules

The FIFO buffer input and output data bus is connected to the FIFOData register. Writing to this register stores one byte in the FIFO buffer and increments the FIFO buffer write pointer. Reading from this register shows the FIFO buffer contents stored at the FIFO buffer read pointer and increments the FIFO buffer read pointer. The distance between the write and read pointer can be obtained by reading the FIFOLength register.

When the microprocessor starts a command, the SLRC400 can still access the FIFO buffer while the command is running. Only one FIFO buffer has been implemented which is used for input and output. Therefore, the microprocessor must ensure that there are no inadvertent FIFO buffer accesses. <u>Table 12</u> gives an overview of FIFO buffer access during command processing.

Table 12. FIFO buffer access

|          | FIFO buffer |     | Remark |

|----------|-------------|-----|--------|

|          |             |     |        |

| StartUp  | -           | -   |        |

| Idle     | -           | -   |        |

| Transmit | yes         | -   |        |

| Receive  | -           | yes |        |

SLRC400\_33

All information provided in this document is subject to legal disclaimers.

Table 12. FIFO buffer access ... continued

| Active     | FIFO buffe       | er              | Remark                                                                              |  |  |

|------------|------------------|-----------------|-------------------------------------------------------------------------------------|--|--|

| command    | μ <b>P Write</b> | μ <b>P Read</b> |                                                                                     |  |  |

| Transceive | yes              | yes             | the microprocessor has to know the state of the command (transmitting or receiving) |  |  |

| WriteE2    | yes              | -               |                                                                                     |  |  |

| ReadE2     | yes              | yes             | the microprocessor has to prepare the arguments, afterwards only reading is allowed |  |  |

| LoadConfig | yes              | -               |                                                                                     |  |  |

| CalcCRC    | yes              | -               |                                                                                     |  |  |

## 8.3.2 Controlling the FIFO buffer

In addition to writing to and reading from the FIFO buffer, the FIFO buffer pointers can be reset using the FlushFIFO bit. This changes the FIFOLength[6:0] value to zero, bit FIFOOvfl is cleared and the stored bytes are no longer accessible. This enables the FIFO buffer to be written with another 64 bytes of data.

#### 8.3.3 FIFO buffer status information

The microprocessor can get the following FIFO buffer status data:

- the number of bytes stored in the FIFO buffer: bits FIFOLength[6:0]

- the FIFO buffer full warning: bit HiAlert

- the FIFO buffer empty warning: bit LoAlert

- the FIFO buffer overflow warning: bit FIFOOvfl.

Remark: Setting the FlushFIFO bit clears the FIFOOvfl bit.

The SLRC400 can generate an interrupt signal when:

- bit LoAlertIRq is set to logic 1 and bit LoAlert = logic 1, pin IRQ is activated.

- bit HiAlertIRq is set to logic 1 and bit HiAlert = logic 1, pin IRQ activated.

The HiAlert flag bit is set to logic 1 only when the WaterLevel[5:0] bits or less can be stored in the FIFO buffer. The trigger is generated by Equation 1:

$$HiAlert = (64 - FIFOLength) \le WaterLevel$$

(1)

The LoAlert flag bit is set to logic 1 when the FIFOLevel register's WaterLevel[5:0] bits or less are stored in the FIFO buffer. The trigger is generated by Equation 2:

$$LoAlert = FIFOLength \le WaterLevel \tag{2}$$

## 8.3.4 FIFO buffer registers and flags

Table 13 shows the related FIFO buffer flags in alphabetical order.

Table 13. Associated FIFO buffer registers and flags

| Flags           | Register name | Bit    | Register address |

|-----------------|---------------|--------|------------------|

| FIFOLength[6:0] | FIFOLength    | 6 to 0 | 04h              |

| FIFOOvfl        | ErrorFlag     | 4      | 0Ah              |

| FlushFIFO       | Control       | 0      | 09h              |

| HiAlert         | PrimaryStatus | 1      | 03h              |

| HiAlertIEn      | InterruptEn   | 1      | 06h              |

| HiAlertIRq      | InterruptRq   | 1      | 07h              |

| LoAlert         | PrimaryStatus | 0      | 03h              |

| LoAlertIEn      | InterruptEn   | 0      | 06h              |

| LoAlertIRq      | InterruptRq   | 0      | 07h              |

| WaterLevel[5:0] | FIFOLevel     | 5 to 0 | 29h              |

## 8.4 Interrupt request system

The SLRC400 indicates interrupt events by setting the PrimaryStatus register bit IRq (see Section 9.5.1.4 "PrimaryStatus register" on page 41) and activating pin IRQ. The signal on pin IRQ can be used to interrupt the microprocessor using its interrupt handling capabilities ensuring efficient microprocessor software.

#### 8.4.1 Interrupt sources overview

Table 14 shows the integrated interrupt flags, related source and setting condition. The interrupt TimerIRq flag bit indicates an interrupt set by the timer unit. Bit TimerIRq is set when the timer decrements from one down to zero (bit TAutoRestart disabled) or from one to the TReLoadValue[7:0] with bit TAutoRestart enabled.

Bit TxIRq indicates interrupts from different sources and is set as follows:

- the transmitter automatically sets the bit TxIRq interrupt when it is active and its state changes from sending data to transmitting the end of frame pattern

- the CRC coprocessor sets the bit TxIRq after all data from the FIFO buffer has been processed indicated by bit CRCReady = logic 1

- when EEPROM programming is finished, the bit TxIRq is set and is indicated by bit E2Ready = logic 1

The RxIRq flag bit indicates an interrupt when the end of the received data is detected. The IdleIRq flag bit is set when a command finishes and the content of the Command register changes to Idle.

When the FIFO buffer reaches the HIGH-level indicated by the WaterLevel[5:0] value (see Section 8.3.3 on page 13) and bit HiAlert = logic 1, then the HiAlertIRq flag bit is set to logic 1.

When the FIFO buffer reaches the LOW-level indicated by the WaterLevel[5:0] value (see Section 8.3.3 on page 13) and bit LoAlert = logic 1, then LoAlertIRq flag bit is set to logic 1.

Table 14. Interrupt sources

| Interrupt flag | Interrupt source | Trigger action                                   |

|----------------|------------------|--------------------------------------------------|

| TimerIRq       | timer unit       | timer counts from 1 to 0                         |

| TxIRq          | transmitter      | a data stream, transmitted to the label, ends    |

|                | CRC coprocessor  | all data from the FIFO buffer has been processed |

| RxIRq          | receiver         | a data stream, received from the label, ends     |

| IdleIRq        | Command register | command execution finishes                       |

| HiAlertIRq     | FIFO buffer      | FIFO buffer is full                              |

| LoAlertIRq     | FIFO buffer      | FIFO buffer is empty                             |

|                |                  |                                                  |

### 8.4.2 Interrupt request handling

#### 8.4.2.1 Controlling interrupts and getting their status

The SLRC400 informs the microprocessor about the interrupt request source by setting the relevant bit in the InterruptRq register. The relevance of each interrupt request bit as source for an interrupt can be masked by the InterruptEn register interrupt enable bits.

Table 15. Interrupt control registers

| Register    | Bit 7  | Bit 6    | Bit 5    | Bit 4 | Bit 3 | Bit 2   | Bit 1      | Bit 0      |

|-------------|--------|----------|----------|-------|-------|---------|------------|------------|

| InterruptEn | SetlEn | reserved | TimerIEn | TxIEn | RxIEn | IdleIEn | HiAlertIEn | LoAlertIEn |

| InterruptRq | SetIRq | reserved | TimerIRq | TxIRq | RxIRq | IdleIRq | HiAlertIRq | LoAlertIRq |

If any interrupt request flag is set to logic 1 (showing that an interrupt request is pending) and the corresponding interrupt enable flag is set, the PrimaryStatus register IRq flag bit is set to logic 1. Different interrupt sources can activate simultaneously because all interrupt request bits are ORed, coupled to the IRq flag and then forwarded to pin IRQ.

#### 8.4.2.2 Accessing the interrupt registers

The interrupt request bits are automatically set by the SLRC400's internal state machines. In addition, the microprocessor can also set or clear the interrupt request bits as required.

A special implementation of the InterruptRq and InterruptEn registers enables changing an individual bit status without influencing any other bits. If an interrupt register is set to logic 1, bit Setlxx and the specific bit must both be set to logic 1 at the same time. Vice versa, if a specific interrupt flag is cleared, zero must be written to the Setlxx and the interrupt register address must be set to logic 1 at the same time.

If a content bit is not changed during the setting or clearing phase, zero must be written to the specific bit location.

**Example:** Writing 3Fh to the InterruptRq register clears all bits. SetIRq is set to logic 0 while all other bits are set to logic 1. Writing 81h to the InterruptRq register sets LoAlertIRq to logic 1 and leaves all other bits unchanged.

#### 8.4.3 Configuration of pin IRQ

The logic level of the IRq flag bit is visible on pin IRQ. The signal on pin IRQ can also be controlled using the following IRQPinConfig register bits.

• bit IRQInv: the signal on pin IRQ is equal to the logic level of bit IRq when this bit is set to logic 0. When set to logic 1, the signal on pin IRQ is inverted with respect to bit IRq.

SLRC400\_33

All information provided in this document is subject to legal disclaimers

• bit IRQPushPull: when set to logic 1, pin IRQ has CMOS output characteristics. When it is set to logic 0, it is an open-drain output which requires an external resistor to achieve a HIGH-level at pin IRQ.

**Remark:** During the reset phase (see Section 8.7.2 on page 23) bit IRQInv is set to logic 1 and bit IRQPushPull is set to logic 0. This results in a high-impedance on pin IRQ.

## 8.4.4 Register overview interrupt request system

Table 16 shows the related interrupt request system flags in alphabetical order.

Table 16. Associated Interrupt request system registers and flags

|             | apt request eyetem registere an | 90  |                  |

|-------------|---------------------------------|-----|------------------|

| Flags       | Register name                   | Bit | Register address |

| HiAlertIEn  | InterruptEn                     | 1   | 06h              |

| HiAlertIRq  | InterruptRq                     | 1   | 07h              |

| IdleIEn     | InterruptEn                     | 2   | 06h              |

| IdleIRq     | InterruptRq                     | 2   | 07h              |

| IRq         | PrimaryStatus                   | 3   | 03h              |

| IRQInv      | IRQPinConfig                    | 1   | 07h              |

| IRQPushPull | IRQPinConfig                    | 0   | 07h              |

| LoAlertIEn  | InterruptEn                     | 0   | 06h              |

| LoAlertIRq  | InterruptRq                     | 0   | 07h              |

| RxIEn       | InterruptEn                     | 3   | 06h              |

| RxIRq       | InterruptRq                     | 3   | 07h              |

| SetlEn      | InterruptEn                     | 7   | 06h              |

| SetIRq      | InterruptRq                     | 7   | 07h              |

| TimerlEn    | InterruptEn                     | 5   | 06h              |

| TimerIRq    | InterruptRq                     | 5   | 07h              |

| TxIEn       | InterruptEn                     | 4   | 06h              |

| TxlRq       | InterruptRq                     | 4   | 07h              |

|             |                                 |     |                  |

## 8.5 Timer unit

The timer derives its clock from the 13.56 MHz on-board chip clock. The microprocessor can use this timer to manage timing-relevant tasks.

The timer unit may be used in one of the following configurations:

- Timeout counter

- WatchDog counter

- Stopwatch

- Programmable one shot

- Periodical trigger

The timer unit can be used to measure the time interval between two events or to indicate that a specific timed event occurred. The timer is triggered by events but does not influence any event (e.g. a time-out during data receiving does not automatically influence the receiving process). Several timer related flags can be set and these flags can be used to generate an interrupt.

SLRC400\_33

All information provided in this document is subject to legal disclaimers.

### 8.5.1 Timer unit implementation

#### 8.5.1.1 Timer unit block diagram

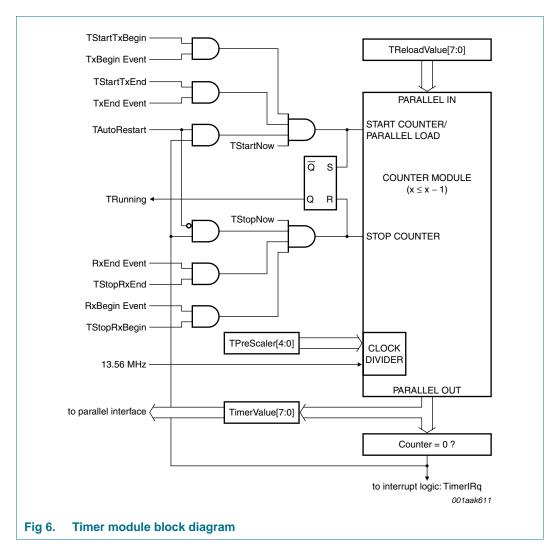

Figure 6 shows the block diagram of the timer module.

The timer unit is designed, so that events when combined with enabling flags start or stop the counter. For example, setting bit TStartTxBegin = logic 1 enables control of received data with the timer unit. In addition, the first received bit is indicated by the TxBegin event. This combination starts the counter at the defined TReloadValue[7:0].

The timer stops automatically when the counter value is equal to zero or if a defined stop event happens (TautoRestart not enabled).

#### 8.5.1.2 Controlling the timer unit

The main part of the timer unit is a down-counter. As long as the down-counter value is not zero, it decrements its value with each timer clock cycle.

If the TAutoRestart flag is enabled, the timer does not decrement down to zero. On reaching value 1, the timer reloads the next clock function with the TReloadValue[7:0].

SLRC400\_33

All information provided in this document is subject to legal disclaimers

The timer is started immediately by loading a value from the TimerReload register into the counter module.

This is activated by one of the following events:

- transmission of the first bit to the label (TxBegin event) with bit TStartTxBegin = logic 1

- transmission of the last bit to the label (TxEnd event) with bit TStartTxEnd = logic 1

- bit TStartNow is set to logic 1 by the microprocessor

**Remark:** Every start event reloads the timer from the TimerReload register. Thus, the timer unit is re-triggered.

The timer can be configured to stop on one of the following events:

- receipt of the first valid bit from the label (RxBegin event) with bit TStopRxBegin = logic 1

- receipt of the last bit from the label (RxEnd event) with bit TStopRxEnd = logic 1

- the counter module has decremented down to zero and bit TAutoRestart = logic 0

- bit TStopNow is set to logic 1 by the microprocessor.

Loading a new value, e.g. zero, into the TimerReload register or changing the timer unit while it is counting will not immediately influence the counter. In both cases, this is because this register only affects the counter content after a start event. Thus, the TimerReload register may be changed even if the timer unit is already counting. The consequence of changing the TimerReload register will be visible after the next start event.

If the counter is stopped when bit TStopNow is set, no TimerIRq is flagged.

#### 8.5.1.3 Timer unit clock and period

The timer unit clock is derived from the 13.56 MHz on-board chip clock using the programmable divider. Clock selection is made using the TimerClock register TPreScaler[4:0] bits based on Equation 3:

$$f_{TimerClock} = \frac{1}{T_{TimerClock}} = \frac{2^{TPreScaler}}{13.56} [MHz]$$

(3)

The values for the TPreScaler[4:0] bits are between 0 and 21 which results in a minimum periodic time ( $T_{TimerClock}$ ) of between 74 ns and 150 ms.

The time period elapsed since the last start event is calculated using Equation 4:

$$t_{Timer} = \frac{TReLoadValue - TimerValue}{f_{TimerClock}}[s] \tag{4}$$

This results in a minimum time period (t<sub>Timer</sub>) of between 74 ns and 40 s.

#### 8.5.1.4 Timer unit status

The SecondaryStatus register's TRunning bit shows the timer's status. Configured start events start the timer at the TReloadValue[7:0] and changes the status flag TRunning to logic 1. Conversely, configured stop events stop the timer and sets the TRunning status flag to logic 0. As long as status flag TRunning is set to logic 1, the TimerValue register changes on the next timer unit clock cycle.

The TimerValue[7:0] bits can be read directly from the TimerValue register.

#### 8.5.1.5 Time-slot period

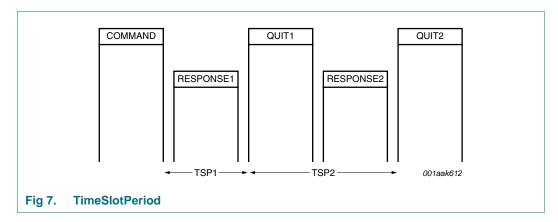

When sending ICODE1 Quit frames, it is necessary to generate the exact chronological relationship to the start of the command frame.

If at the end of command execution TimeSlotPeriod > 0, the TimeSlotPeriod starts. If the FIFO buffer contains data when the end of TimeSlotPeriod is reached, the data is sent. If the FIFO buffer is empty nothing happens. As long as the TimeSlotPeriod is > 0, the TimeSlotPeriod counter automatically starts on reaching the end.

This forms the exact time relationship between the start and finish of the command frame used to generate and send ICODE1 Quit frames.

When the TimeSlotPeriod > 0, the next Frame starts with exactly the same interval TimeSlotPeriod/CoderRate delayed after each previous send frame. CoderRate defines the clock frequency of the encoder. If TimeSlotPeriod[7:0] = 0, the send function is not automatically triggered.

The content of the TimeSlotPeriod register can be changed while it is running but the change is only effective after the next TimeSlotPeriod restart.

#### Example:

- CoderRate = 0 × 0.5 (~52.97 kHz)

- The interval should be 8.458 ms for ICODE1 standard mode

TimeSlotPeriod = CoderRate  $\times$  Interval = 52.97 kHz  $\times$  8.458 ms -1 = 447 = 1BFh

Remark: The TimeSlotPeriod MSB bit is contained in the SIGOUTSelect register.

SLRC400\_33

**ICODE** reader IC

Table 17. TimeSlotPeriod

| ICODE1 mode   | TimeSlotPeriod for TSP1 | TimeSlotPeriod for TSP2 |

|---------------|-------------------------|-------------------------|

| standard mode | BFh                     | 1BFh                    |

| fast mode     | 5Fh                     | 67h                     |

**Remark:** Set bit TxCRCEn to logic 0 before the Quit frame is sent. If TxCRCEn is not set to logic 0, the Quit frame is sent with a calculated CRC value. Use the CRC8 algorithm to calculate the Quit value.

#### 8.5.2 Using the timer unit functions

#### 8.5.2.1 Time-out and WatchDog counters

After starting the timer using TReloadValue[7:0], the timer unit decrements the TimerValue register beginning with a given start event. If a given stop event occurs, such as a bit being received from the label, the timer unit stops without generating an interrupt.

If a stop event does not occur, such as the label not answering within the expected time, the timer unit decrements down to zero and generates a timer interrupt request. This signals to the microprocessor the expected event has not occurred within the given time  $(t_{\text{Timer}})$ .

#### 8.5.2.2 Stopwatch

The time  $(t_{\text{Timer}})$  between a start and stop event is measured by the microprocessor using the timer unit. Setting the TimerReload register triggers the timer which in turn, starts to decrement. If the defined stop event occurs, the timer stops. The time between start and stop is calculated by the microprocessor using <u>Equation 5</u>, when the timer does not decrement down to zero.

$$\Delta t = (TReLoad_{value} - TimerValue) \times t_{Timer}$$

(5)

#### 8.5.2.3 Programmable one shot timer and periodic trigger

**Programmable one shot timer:** The microprocessor starts the timer unit and waits for the timer interrupt. The interrupt occurs after the time specified by  $t_{Timer}$  (TAutoRestart bit = logic 0).

**Periodic trigger:** If the microprocessor sets the TAutoRestart bit, and TReloadValue is not equal to zero, it generates an interrupt request after every t<sub>Timer</sub> cycle.

#### 8.5.3 Timer unit registers

Table 18 shows the related flags of the timer unit in alphabetical order.

Table 18. Associated timer unit registers and flags

| Flags             | Register name   | Bit    | Register address |

|-------------------|-----------------|--------|------------------|

| TAutoRestart      | TimerClock      | 5      | 2Ah              |

| TimerValue[7:0]   | TimerValue      | 7 to 0 | 0Ch              |

| TReloadValue[7:0] | TimerReload     | 7 to 0 | 2Ch              |

| TPreScaler[4:0]   | TimerClock      | 4 to 0 | 2Ah              |

| TRunning          | SecondaryStatus | 7      | 05h              |

| TStartNow         | Control         | 1      | 09h              |

SLRC400\_33

All information provided in this document is subject to legal disclaimers

Table 18. Associated timer unit registers and flags ...continued

| Flags         | Register name | Bit | Register address |

|---------------|---------------|-----|------------------|

| TStartTxBegin | TimerControl  | 0   | 2Bh              |

| TStartTxEnd   | TimerControl  | 1   | 2Bh              |

| TStopNow      | Control       | 2   | 09h              |

| TStopRxBegin  | TimerControl  | 2   | 2Bh              |

| TStopRxEnd    | TimerControl  | 3   | 2Bh              |

## 8.6 Power reduction modes

## 8.6.1 Hard power-down

Hard power-down is enabled when pin RSTPD is HIGH. This turns off all internal current sinks including the oscillator. All digital input buffers are separated from the input pads and defined internally (except pin RSTPD itself). The output pins are frozen at a given value. The status of all pins during a hard power-down is shown in Table 19.

Table 19. Signal on pins during Hard power-down

| Symbol   | Pin      | Туре | Description                              |

|----------|----------|------|------------------------------------------|

| OSCIN    | 1        | I    | not separated from input, pulled to AVSS |

| IRQ      | 2        | 0    | high-impedance                           |

| n.c.     | 3        | I    | separated from input                     |

| SIGOUT   | 4        | 0    | LOW                                      |

| TX1      | 5        | 0    | HIGH                                     |

| TX2      | 7        | 0    | LOW                                      |

| NCS      | 9        | I    | separated from input                     |

| NWR      | 10       | I    | separated from input                     |

| NRD      | 11       | I    | separated from input                     |

| D0 to D7 | 13 to 20 | I/O  | separated from input                     |

| ALE      | 21       | I    | separated from input                     |

| A0       | 22       | I/O  | separated from input                     |

| A1       | 23       | I    | separated from input                     |

| A2       | 24       | I    | separated from input                     |

| AUX      | 27       | 0    | high-impedance                           |

| RX       | 29       | I    | not changed                              |

| VMID     | 30       | Α    | pulled to V <sub>DDA</sub>               |

| RSTPD    | 31       | I    | not changed                              |

| OSCOUT   | 32       | 0    | HIGH                                     |

|          |          |      |                                          |

### 8.6.2 Soft power-down mode

Soft power-down mode is entered immediately using the Control register bit PowerDown. All internal current sinks, including the oscillator buffer, are switched off. The digital input buffers are not separated from the input pads and keep their functionality. In addition, the digital output pins do not change their state.

After resetting the Control register bit PowerDown, the bit indicating Soft power-down mode is only cleared after 512 clock cycles. Resetting it does not immediately clear it. The PowerDown bit is automatically cleared when the Soft power-down mode is exited.

**Remark:** When the internal oscillator is used, time ( $t_{osc}$ ) is required for the oscillator to become stable. This is because the internal oscillator is supplied by  $V_{DDA}$  and any clock cycles will not be detected by the internal logic until  $V_{DDA}$  is stable.

### 8.6.3 Standby mode

The Standby mode is immediately entered when the Control register Standby bit is set. All internal current sinks, including the internal digital clock buffer are switched off. However, the oscillator buffer is not switched off.

The digital input buffers are not separated by the input pads, keeping their functionality and the digital output pins do not change their state. In addition, the oscillator does not need time to wake-up.

After resetting the Control register StandBy bit, it takes four clock cycles on pin OSCIN for Standby mode to exit. Resetting bit StandBy does not immediately clear it. It is automatically cleared when the Standby mode is exited.

### 8.6.4 Automatic receiver power-down

It is a power saving feature to switch off the receiver circuit when it is not needed. Setting bit RxAutoPD = logic 1, automatically powers down the receiver when it is not in use. Setting bit RxAutoPD = logic 0, keeps the receiver continuously powered up.

## 8.7 StartUp phase

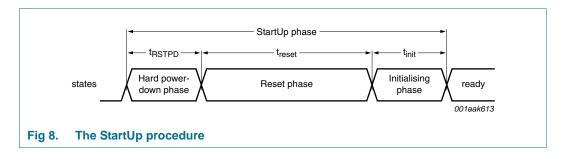

The events executed during the StartUp phase are shown in Figure 8.

#### 8.7.1 Hard power-down phase

The hard power-down phase is active during the following cases:

- a Power-On Reset (POR) caused by power-up on pins DVDD activated when V<sub>DDD</sub> is below the digital reset threshold.

- a Power-On Reset (POR) caused by power-up on pins AVDD activated when V<sub>DDA</sub> is below the analog reset threshold.

- a HIGH-level on pin RSTPD which is active while pin RSTPD is HIGH. The HIGH level period on pin RSTPD must be at least 100  $\mu$ s ( $t_{PD} \ge 100~\mu$ s). Shorter phases will not necessarily result in the reset phase ( $t_{reset}$ ). The rising or falling edge slew rate on pin RSTPD is not critical because pin RSTPD is a Schmitt trigger input.

SLRC400\_33

### 8.7.2 Reset phase

The reset phase automatically follows the Hard power-down. Once the oscillator is running stably, the reset phase takes 512 clock cycles. During the reset phase, some register bits are preset by hardware. The respective reset values are given in the description of each register (see Section 9.5 on page 40).

**Remark:** When the internal oscillator is used, time  $(t_{osc})$  is required for the oscillator to become stable. This is because the internal oscillator is supplied by  $V_{DDA}$  and any clock cycles will not be detected by the internal logic until  $V_{DDA}$  is stable.

#### 8.7.3 Initialization phase

The initialization phase automatically follows the reset phase and takes 128 clock cycles. During the initializing phase the content of the EEPROM blocks 1 and 2 is copied into the register subaddresses 10h to 2Fh (see Section 8.2.2 on page 10).

**Remark:** During the production test, the SLRC400 is initialized with default configuration values. This reduces the microprocessor's configuration time to a minimum.

#### 8.7.4 Initializing the parallel interface type

A different initialization sequence is used for each microprocessor. This enables detection of the correct microprocessor interface type and synchronization of the microprocessor's and the SLRC400's start-up. See <u>Section 8.1.3 on page 7</u> for detailed information on the different connections for each microprocessor interface type.

During StartUp phase, the command value is set to 3Fh once the oscillator attains clock frequency stability at an amplitude of > 90 % of the nominal 13.56 MHz clock frequency. At the end of the initialization phase, the SLRC400 automatically switches to idle and the command value changes to 00h.

To ensure correct detection of the microprocessor interface, the following sequence is executed:

- the Command register is read until the 6-bit register value is 00h. On reading the 00h value, the internal initialization phase is complete and the SLRC400 is ready to be controlled

- write 80h to the Page register to initialize the microprocessor interface

- read the Command register. If it returns a value of 00h, the microprocessor interface was successfully initialized

- write 00h to the Page registers to activate linear addressing mode.

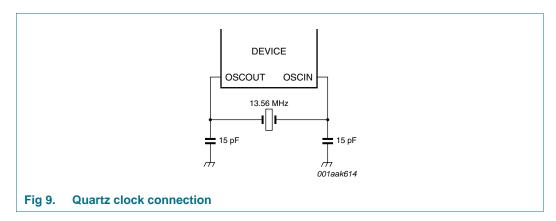

#### 8.8 Oscillator circuit

The clock applied to the SLRC400 acts as a time basis for the synchronous system encoder and decoder. The stability of the clock frequency is an important factor for correct operation. To obtain highest performance, clock jitter must be as small as possible. This is best achieved by using the internal oscillator buffer with the recommended circuitry.

If an external clock source is used, the clock signal must be applied to pin OSCIN. In this case, be very careful in optimizing clock duty cycle and clock jitter. Ensure the clock quality has been verified. It must meet the specifications described in <a href="Section 12.4.4">Section 12.4.4</a> on page 84.

Remark: We do not recommend using an external clock source.

## 8.9 Transmitter pins TX1 and TX2

The signal on pins TX1 and TX2 is the 13.56 MHz carrier modulated by an envelope signal. It can be used to drive an antenna directly, using minimal passive components for matching and filtering (see Section 14.1 on page 85). To enable this, the output circuitry is designed with a very low-impedance source resistance. The TxControl register is used to control the TX1 and TX2 signals.

## 8.9.1 Configuring pins TX1 and TX2

TX1 pin configurations are described in Table 20.

Table 20. Pin TX1 configurations

| Envelope | TX1 signal                    |

|----------|-------------------------------|

|          |                               |

| X        | LOW (GND)                     |

| 0        | 13.56 MHz modulated carrier   |

| 1        | 13.56 MHz unmodulated carrier |

|          | •                             |

TX2 pin configurations are described in Table 21.

Table 21. Pin TX2 configurations

| TxControl register configuration |       | Envelope | TX2 signal |                                                                         |

|----------------------------------|-------|----------|------------|-------------------------------------------------------------------------|

| TX2RFEn                          | TX2Cw | TX2Inv   |            |                                                                         |

| 0                                | Χ     | Χ        | Χ          | LOW (GND)                                                               |

| 1                                | 0     | 0        | 0          | 13.56 MHz modulated carrier                                             |

| 1                                | 0     | 0        | 1          | 13.56 MHz unmodulated carrier                                           |

| 1                                | 0     | 1        | 0          | 13.56 MHz modulated carrier frequency, 180° phase-shift relative to TX1 |

| 1                                | 0     | 1        | 1          | 13.56 MHz unmodulated carrier, 180° phase-shift relative to TX1         |

| 1                                | 1     | 0        | Χ          | 13.56 MHz unmodulated carrier                                           |

| 1                                | 1     | 1        | X          | 13.56 MHz unmodulated carrier, 180° phase-shift relative to TX1         |

## 8.9.2 Antenna operating distance versus power consumption

Using different antenna matching circuits (by varying the supply voltage on the antenna driver supply pin TVDD), it is possible to find the trade-off between maximum effective operating distance and power consumption. Different antenna matching circuits are described in the Application note Ref. 1.

### 8.9.3 Antenna driver output source resistance

The output source conductance of pins TX1 and TX2 for driving a HIGH level can be adjusted between 1  $\Omega$  and 100  $\Omega$  using the CwConductance register GsCfgCW[5:0] bits.

The values are relative to the reference source resistance ( $R_{S(ref)}$ ) which is measured during the production test and stored in the SLRC400 EEPROM. It can be read from the product information field (see <u>Section 8.2.1 on page 9</u>). The electrical specification can be found in <u>Section 12.3.3 on page 79</u>.

#### 8.9.3.1 Source resistance table

Table 22. TX1 and TX2 source resistance of n-channel driver transistor against GsCfgCW MANT = Mantissa; EXP = Exponent.

| GsCfgCW (decimal) | EXP <sub>GsCfgCW</sub> (decimal) | MANT <sub>GsCfgCW</sub><br>(decimal) | $R_{S(ref)}$ $(\Omega)$ | GsCfgCW (decimal) | EXP <sub>GsCfgCW</sub><br>(decimal) | MANT <sub>GsCfgCW</sub><br>(decimal) | $R_{S(ref)}$ $(\Omega)$ |

|-------------------|----------------------------------|--------------------------------------|-------------------------|-------------------|-------------------------------------|--------------------------------------|-------------------------|

| 0                 | 0                                | 0                                    | œ                       | 24                | 1                                   | 8                                    | 0.0652                  |

| 16                | 1                                | 0                                    | œ                       | 25                | 1                                   | 9                                    | 0.0580                  |

| 32                | 2                                | 0                                    | œ                       | 37                | 2                                   | 5                                    | 0.0541                  |

| 48                | 3                                | 0                                    | œ                       | 26                | 1                                   | 10                                   | 0.0522                  |

| 1                 | 0                                | 1                                    | 1.0000                  | 27                | 1                                   | 11                                   | 0.0474                  |

| 17                | 1                                | 1                                    | 0.5217                  | 51                | 3                                   | 3                                    | 0.0467                  |

| 2                 | 0                                | 2                                    | 0.5000                  | 38                | 2                                   | 6                                    | 0.0450                  |

| 3                 | 0                                | 3                                    | 0.3333                  | 28                | 1                                   | 12                                   | 0.0435                  |

| 33                | 2                                | 1                                    | 0.2703                  | 29                | 1                                   | 13                                   | 0.0401                  |

| 18                | 1                                | 2                                    | 0.2609                  | 39                | 2                                   | 7                                    | 0.0386                  |

| 4                 | 0                                | 4                                    | 0.2500                  | 30                | 1                                   | 14                                   | 0.0373                  |

| 5                 | 0                                | 5                                    | 0.2000                  | 52                | 3                                   | 4                                    | 0.0350                  |

| 19                | 1                                | 3                                    | 0.1739                  | 31                | 1                                   | 15                                   | 0.0348                  |

| 6                 | 0                                | 6                                    | 0.1667                  | 40                | 2                                   | 8                                    | 0.0338                  |

| 7                 | 0                                | 7                                    | 0.1429                  | 41                | 2                                   | 9                                    | 0.0300                  |

| 49                | 3                                | 1                                    | 0.1402                  | 53                | 3                                   | 5                                    | 0.0280                  |

| 34                | 2                                | 2                                    | 0.1351                  | 42                | 2                                   | 10                                   | 0.0270                  |

| 20                | 1                                | 4                                    | 0.1304                  | 43                | 2                                   | 11                                   | 0.0246                  |

| 8                 | 0                                | 8                                    | 0.1250                  | 54                | 3                                   | 6                                    | 0.0234                  |

| 9                 | 0                                | 9                                    | 0.1111                  | 44                | 2                                   | 12                                   | 0.0225                  |

| 21                | 1                                | 5                                    | 0.1043                  | 45                | 2                                   | 13                                   | 0.0208                  |

| 10                | 0                                | 10                                   | 0.1000                  | 55                | 3                                   | 7                                    | 0.0200                  |

| 11                | 0                                | 11                                   | 0.0909                  | 46                | 2                                   | 14                                   | 0.0193                  |

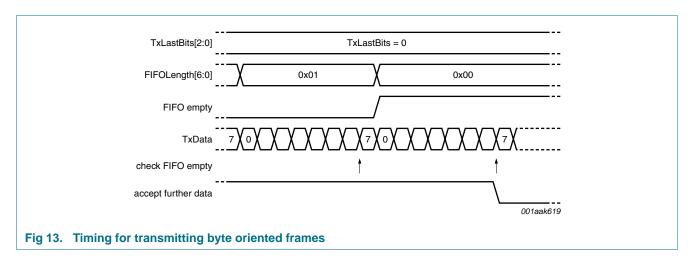

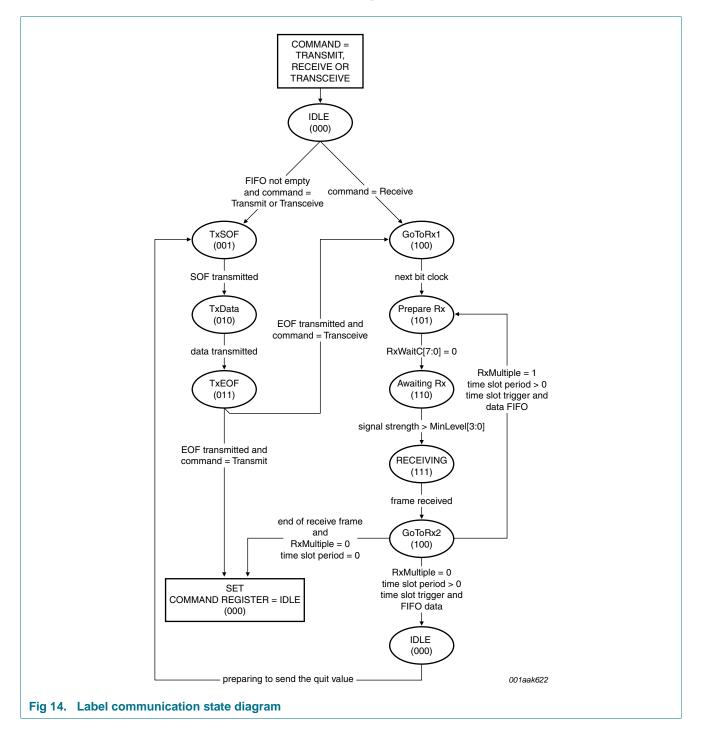

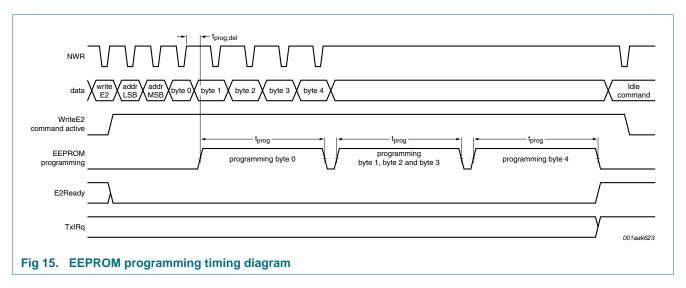

| 35                | 2                                | 3                                    | 0.0901                  | 47                | 2                                   | 15                                   | 0.0180                  |