# CS44800

# 8-Channel Digital Amplifier Controller

## Features

- ♦ > 100 dB Dynamic Range System Level

- ◆ < 0.03% THD+N @ 1 W System Level

- ♦ 32 kHz to 192 kHz Sample Rates

- Internal Oscillator Circuit Supports 24.576 MHz to 54 MHz Crystals

- Integrated Sample Rate Converter (SRC)

- Eliminates Clock Jitter Effects

- Input Sample Rate Independent Operation

- Power Supply Rejection Realtime Feedback

- Spread Spectrum Modulation Reduces EMI

- ♦ PWM Popguard<sup>®</sup> for Single-Ended Mode

- Eliminates AM Frequency Interference

- Programmable Load Compensation Filters

- Support for up to 40 kHz Audio Bandwidth

- Digital Volume Control with Soft Ramp

+24 to -127 dB in 0.25 dB Steps

- Per Channel Programmable Peak Detect and Limiter

- SPI<sup>™</sup> and I<sup>2</sup>C<sup>®</sup> Host Control Interfaces

- Separate 2.5 V to 5.0 V Serial Port and Host Control Port Supplies

#### **General Description**

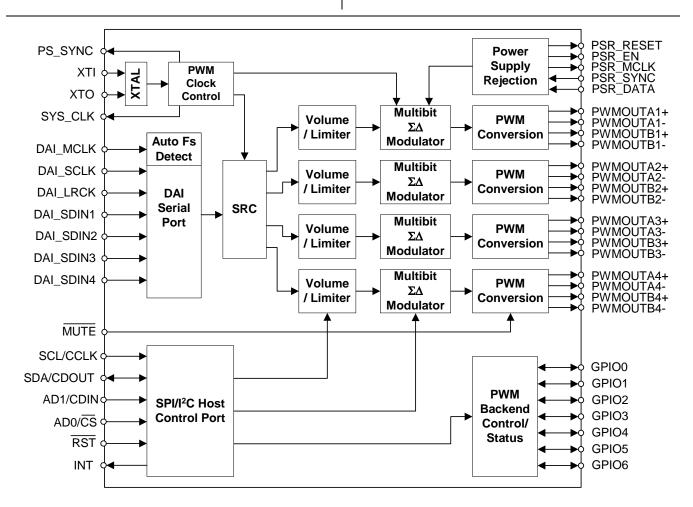

The CS44800 is a multi-channel digital-to-PWM Class D audio system controller including interpolation, sample rate conversion, half- and full-bridge PWM driver outputs, and power supply rejection feedback in a 64-pin LQFP pack-age. The architecture uses a direct-to-digital approach that maintains digital signal integrity to the final output filter, minimizing analog interference effects which negatively affect system performance.

The CS44800 integrates on-chip digital volume control, peak detect with limiter, de-emphasis, and 7 GPIO's, allowing easy interfacing to many commonly available power stages. The PWM amplifier can achieve greater than 90% efficiency. This efficiency provides for smaller device package, less heat sink requirements, and smaller power supplies.

The CS44800 is ideal for audio systems requiring wide dynamic range, negligible distortion and low noise, such as A/V receivers, DVD receivers, digital speaker and automotive audio systems.

# TABLE OF CONTENTS

| 1. CHARACTERISTICS AND SPECIFICATIONS                              | 8  |

|--------------------------------------------------------------------|----|

| SPECIFIED OPERATING CONDITIONS                                     |    |

| ABSOLUTE MAXIMUM RATINGS                                           | 8  |

| DC ELECTRICAL CHARACTERISTICS                                      | 9  |

| DIGITAL INTERFACE CHARACTERISTICS                                  | 9  |

| PWM OUTPUT PERFORMANCE CHARACTERISTICS                             | 10 |

| PWM FILTER CHARACTERISTICS                                         |    |

| SWITCHING CHARACTERISTICS - XTI                                    |    |

| SWITCHING CHARACTERISTICS - SYS_CLK                                |    |

| SWITCHING CHARACTERISTICS - PWMOUTA1-B4                            |    |

| SWITCHING CHARACTERISTICS - PS_SYNC                                |    |

| SWITCHING CHARACTERISTICS - DAI INTERFACE                          |    |

| SWITCHING CHARACTERISTICS - CONTROL PORT - I <sup>2</sup> C FORMAT |    |

| SWITCHING CHARACTERISTICS - CONTROL PORT - SPI FORMAT              | 15 |

| 2. PIN DESCRIPTIONS                                                |    |

| 2.1 I/O Pin Characteristics                                        |    |

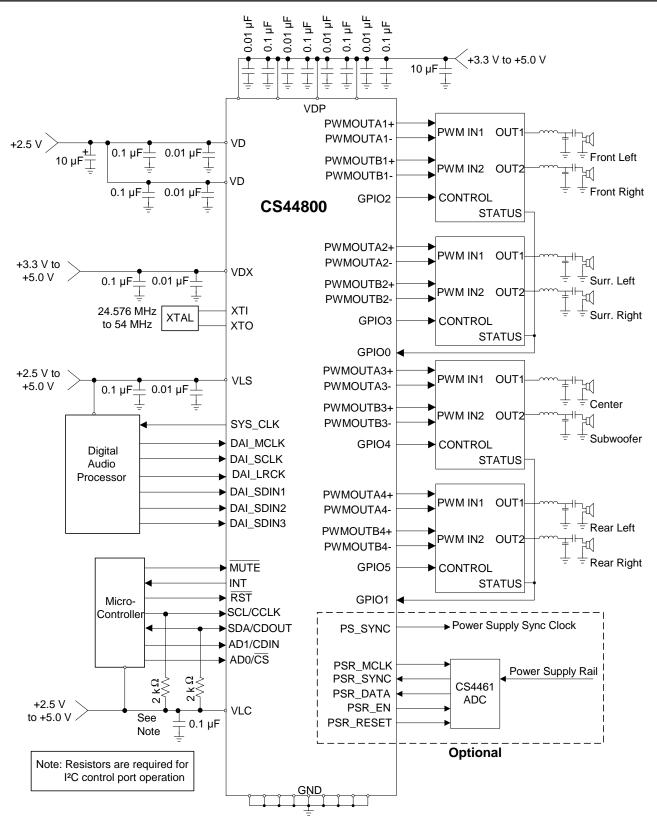

| 3. TYPICAL CONNECTION DIAGRAMS                                     | 21 |

| 4. APPLICATIONS                                                    |    |

| 4.1 Overview                                                       |    |

| 4.2 Feature Set Summary                                            |    |

| 4.3 Clock Generation                                               |    |

| 4.3.1 FsIn Domain Clocking                                         |    |

| 4.3.2 FsOut Domain Clocking                                        |    |

| 4.4 FsIn Clock Domain Modules                                      |    |

| 4.4.1 Digital Audio Input Port                                     |    |

| 4.4.2 Auto Rate Detect                                             |    |

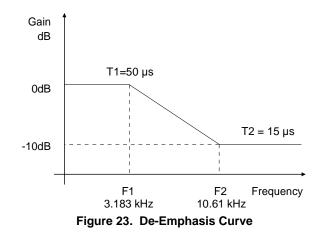

| 4.4.3 De-Emphasis                                                  |    |

| 4.5 FsOut Clock Domain Modules                                     |    |

| 4.5.1 Sample Rate Converter                                        |    |

| 4.5.2 Load Compensation Filter                                     |    |

| 4.5.3 Digital Volume and Mute Control                              |    |

| 4.5.4 Peak Detect / Limiter                                        |    |

| 4.5.5 PWM Engines                                                  |    |

| 4.5.6 Interpolation Filter                                         |    |

| 4.5.7 Quantizer                                                    |    |

| 4.5.8 Modulator                                                    |    |

| 4.5.9 PWM Outputs                                                  | 34 |

| 4.5.10 Power Supply Rejection (PSR) Real-Time Feedback             |    |

| 4.6.1 SPI Mode                                                     |    |

| 4.6.2 I <sup>2</sup> C Mode                                        |    |

| 4.6.3 GPIOs                                                        |    |

| 4.6.4 Host Interrupt                                               |    |

| 5. POWER SUPPLY, GROUNDING, AND PCB LAYOUT                         |    |

| 5.1 Reset and Power-Up                                             |    |

| 5.1.1 PWM PopGuard® Transient Control                              |    |

| 5.1.2 Recommended Power-Up Sequence                                |    |

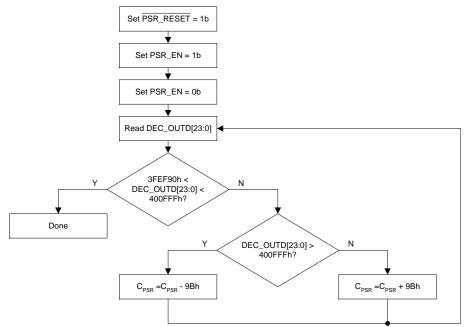

| 5.1.3 Recommended PSR Calibration Sequence                         |    |

| 5.1.4 Recommended Power-Down Sequence                              |    |

| 6. REGISTER QUICK REFERENCE                                        |    |

| 7. REGISTER DESCRIPTION                                            |    |

| 7.1 Memory Address Pointer (MAP)                                   | 50 |

|                                                                    |    |

# CS44800

| 7.1.1 Increment (INCR)                                                                                      | 50 |

|-------------------------------------------------------------------------------------------------------------|----|

| 7.1.2 Memory Address Pointer (MAPx)                                                                         |    |

| 7.2 CS44800 I.D. and Revision Register (address 01h) (Read Only)                                            |    |

| 7.2.1 Chip I.D. (Chip_IDx)                                                                                  |    |

| 7.2.2 Chip Revision (Rev_IDx)                                                                               |    |

| 7.3 Clock Configuration and Power Control (address 02h)                                                     |    |

| 7.3.1 Enable SYS_CLK Output (EN_SYS_CLK)                                                                    |    |

| 7.3.2 SYS_CLK Clock Divider Settings (SYS_CLK_DIV[1:0])                                                     |    |

| 7.3.3 PWM Master Clock Divider Settings (PWM_MCLK_DIV[1:0])                                                 |    |

| 7.3.4 Power Down XTAL (PDN_XTAL)                                                                            |    |

| 7.3.5 Power Down Output Mode (PDN_OUTPUT_MODE)                                                              | 52 |

| 7.3.6 Power Down (PDN)                                                                                      |    |

| 7.4 PWM Channel Power Down Control (address 03h)                                                            |    |

| 7.4.1 Power Down PWM Channels (PDN_PWMB4:PDN_PWMA1)                                                         |    |

| 7.5 Misc. Configuration (address 04h)                                                                       |    |

| 7.5.1 Digital Interface Format (DIFX)                                                                       |    |

| 7.5.2 AM Frequency Hopping (AM_FREQ_HOP)                                                                    |    |

| 7.5.3 Freeze Controls (FREEZE)                                                                              |    |

| 7.5.4 De-Emphasis Control (DEM[1:0])                                                                        |    |

| 7.6 Ramp Configuration (address 05h)                                                                        | 54 |

| 7.6.1 Ramp-Up/Down Setting (RAMP[1:0])                                                                      | 54 |

| 7.6.2 Ramp Speed (RAMP_SPD[1:0])                                                                            |    |

| 7.7 Volume Control Configuration (address 06h)                                                              | 55 |

| 7.7.1 Single Volume Control (SNGVOL)                                                                        |    |

| 7.7.2 Soft Ramp and Zero Cross Control (SZC[1:0])                                                           |    |

| 7.7.3 Enable 50% Duty Cycle for Mute Condition (MUTE_50/50)                                                 |    |

| 7.7.4 Soft Ramp-Down on Interface Error (SRD_ERR)                                                           |    |

| 7.7.4 Soft Ramp-Up on Recovered Interface Error (SRU_ERR)                                                   |    |

| 7.7.6 Auto-Mute (AMUTE)                                                                                     |    |

| 7.8 Master Volume Control - Integer (address 07h)                                                           |    |

| 7.8 Master Volume Control - Integer (Address 071)<br>7.8.1 Master Volume Control - Integer (MSTR_IVOL[7:0]) |    |

| 7.9 Master Volume Control - Fraction (address 08h)                                                          | 57 |

| 7.9 Master Volume Control - Fraction (MSTR_FVOL[1:0])                                                       |    |

| 7.9.1 Master Volume Control - Fraction (MSTR_FVOL[1.0])                                                     |    |

| 7.10 Channel Volume Control - Integer (addresses 091 - 101)                                                 |    |

| 7.10 Channel XX Volume Control1 - Fraction (address 11h)                                                    |    |

|                                                                                                             |    |

| 7.12 Channel XX Volume Control2 - Fraction (address 12h)                                                    |    |

| 7.12.1 Channel Volume Control - Fraction (CHXX_FVOL[1:0])                                                   |    |

| 7.13 Channel Mute (address 13h)                                                                             | 60 |

| 7.13.1 Independent Channel Mute (CHXX_MUTE)                                                                 |    |

| 7.14 Channel Invert (address 14h)                                                                           | 60 |

| 7.14.1 Invert Signal Polarity (CHXX_INV)                                                                    |    |

| 7.15 Peak Limiter Control Register (address 15h)                                                            |    |

| 7.15.1 Peak Signal Limit All Channels (LIMIT_ALL)                                                           |    |

| 7.15.2 Peak Signal Limiter Enable (LIMIT_EN)                                                                |    |

| 7.16 Limiter Attack Rate (address 16h)                                                                      |    |

| 7.16.1 Attack Rate (ARATE[7:0])                                                                             |    |

| 7.17 Limiter Release Rate (address 17h)                                                                     |    |

| 7.17.1 Release Rate (RRATE[7:0])                                                                            | 62 |

| 7.18 Chnl XX Load Compensation Filter - Coarse Adjust                                                       | 00 |

| (addresses 18h, 1Ah, 1Ch, 1Eh, 20h, 22h, 24h, 26h)                                                          |    |

| 7.18.1 Channel Compensation Filter - Coarse Adjust (CHXX_CORS[5:0])                                         | 62 |

| 7.19 Chnl XX Load Compensation Filter - Fine Adjust                                                         |    |

| (addresses 19h, 1Bh, 1Dh, 1Fh, 21h, 23h, 25h, 27h)                                                          | 63 |

|                                                                    | _  |

|--------------------------------------------------------------------|----|

| 7.19.1 Channel Compensation Filter - Fine Adjust (CHXX_FINE[5:0])  |    |

| 7.20 Interrupt Mode Control (address 28h)                          | 63 |

| 7.20.1 Interrupt Pin Control (INT1/INT0)                           |    |

| 7.20.2 Overflow Level/Edge Select (OVFL_L/E)                       |    |

| 7.21 Interrupt Mask (address 29h)                                  |    |

| 7.22 Interrupt Status (address 2Ah) (Read Only)                    |    |

| 7.22.1 SRC Unlock Interrupt (SRC_UNLOCK)                           |    |

| 7.22.2 SRC Lock Interrupt (SRC_LOCK)                               |    |

| 7.22.3 Ramp-Up Complete Interrupt (RMPUP_DONE)                     |    |

| 7.22.4 Ramp-Down Complete Interrupt (RMPDN_DONE)                   |    |

| 7.22.5 Mute Complete Interrupt (Mute_DONE)                         | 65 |

| 7.22.6 Channel Over Flow Interrupt (OVFL_INT)                      |    |

| 7.22.7 GPIO Interrupt Condition (GPIO_INT)                         | 65 |

| 7.23 Channel Over Flow Status (address 2Bh) (Read Only)            |    |

| 7.23.1 ChXX_OVFL                                                   |    |

| 7.24 GPIO Pin In/Out (address 2Ch)                                 |    |

| 7.24.1 GPIO In/Out Selection (GPIOX_I/O)                           |    |

| 7.25 GPIO Pin Polarity/Type (address 2Dh)                          | 66 |

| 7.25.1 GPIO Polarity/Type Selection (GPIOX_P/T)                    | 66 |

| 7.26 GPIO Pin Level/Edge Trigger (address 2Eh)                     | 67 |

| 7.26.1 GPIO Level/Edge Input Sensitive (GPIOX_L/E)                 | 67 |

| 7.27 GPIO Status Register (address 2Fh)                            | 67 |

| 7.27.1 GPIO Pin Status (GPIOX_STATUS)                              |    |

| 7.28 GPIO Interrupt Mask Register (address 30h)                    |    |

| 7.28.1 GPIO Pin Interrupt Mask (M_GPIOX)                           |    |

| 7.29 PWM Configuration Register (address 31h)                      |    |

| 7.29.1 Over Sample Rate Selection (OSRATE)                         |    |

| 7.29.2 Channels A1 and B1 Output Configuration (A1/B1_OUT_CNFG)    |    |

| 7.29.3 Channels A2 and B2 Output Configuration (A2/B2_OUT_CNFG)    |    |

| 7.29.4 Channel A3 Output Configuration (A3_OUT_CNFG)               |    |

| 7.29.5 Channel B3 Output Configuration (B3_OUT_CNFG)               | 69 |

| 7.29.6 Channels A4 and B4 Output Configuration (A4/B4_OUT_CNFG)    | 69 |

| 7.30 PWM Minimum Pulse Width Register (address 32h)                |    |

| 7.30.1 Disable PWMOUTXX - Signal (DISABLE_PWMOUTXX-)               |    |

| 7.30.2 Minimum PWM Output Pulse Settings (MIN_PULSE[4:0])          |    |

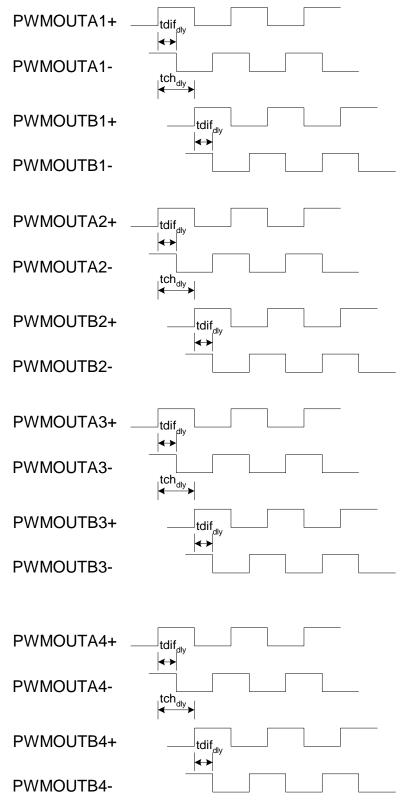

| 7.31 PWMOUT Delay Register (address 33h)                           |    |

| 7.31.1 Differential Signal Delay (DIFF_DLY[2:0])                   |    |

| 7.31.2 Channel Delay Settings (CHNL_DLY[4:0])                      |    |

| 7.32 PSR and Power Supply Configuration (address 34h)              |    |

| 7.32.1 Power Supply Rejection Enable (PSR_EN)                      |    |

| 7.32.2 Power Supply Rejection Reset (PSR_RESET)                    |    |

| 7.32.3 Power Supply Rejection Feedback Enable (FEEDBACK_EN)        |    |

| 7.32.4 Power Supply Sync Clock Divider Settings (PS_SYNC_DIV[2:0]) |    |

| 7.33 Decimator Shift/Scale (addresses 35h, 36h, 37h)               |    |

| 7.33.1 Decimator Shift (DEC_SHIFT[2:0])                            |    |

| 7.33.2 Decimator Scale (DEC_SCALE[18:0])                           |    |

| 7.34 Decimator Outd (addresses 3Bh, 3Ch, 3Dh)                      |    |

| 7.34.1 Decimator Outd (DEC_OUTD[23:0])                             |    |

| 8. PARAMETER DEFINITIONS                                           |    |

| 9. REFERENCES                                                      |    |

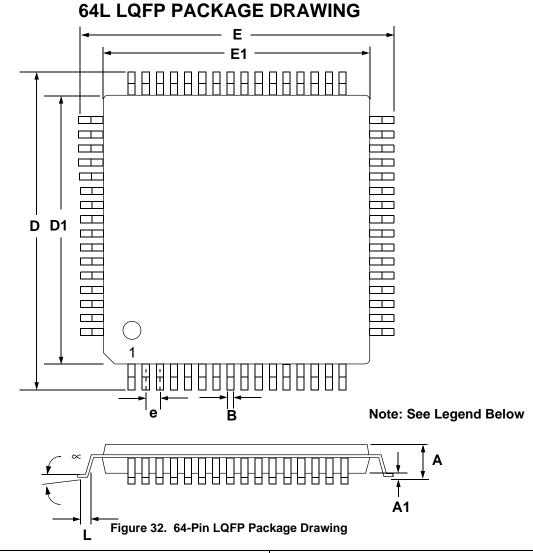

| 10. PACKAGE DIMENSIONS                                             |    |

| 11. THERMAL CHARACTERISTICS                                        |    |

| 12. ORDERING INFORMATION                                           |    |

| 13. REVISION HISTORY                                               | 79 |

# LIST OF FIGURES

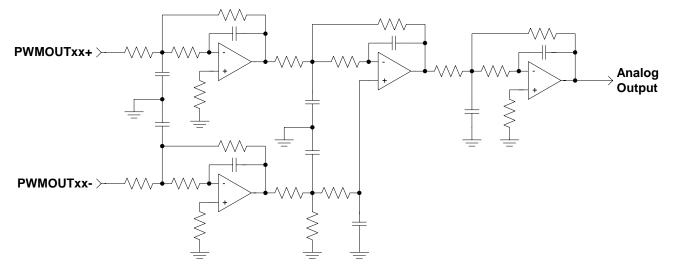

| Figure 1.Performance Characteristics Evaluation Active Filter Circuit | 10 |

|-----------------------------------------------------------------------|----|

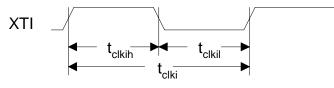

| Figure 2.XTI Timings                                                  |    |

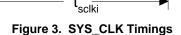

| Figure 3.SYS_CLK Timings                                              | 12 |

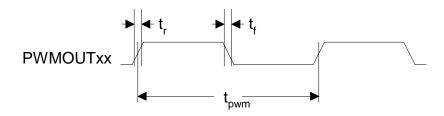

| Figure 4.PWMOUTxx Timings                                             | 12 |

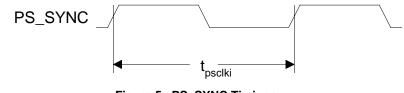

| Figure 5.PS_SYNC Timings                                              |    |

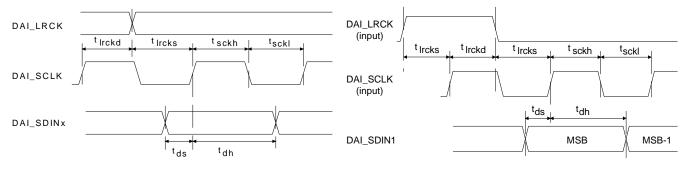

| Figure 6.Serial Audio Interface Timing                                |    |

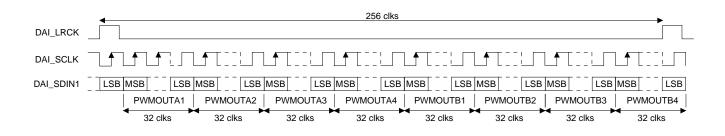

| Figure 7.Serial Audio Interface Timing - TDM Mode                     | 13 |

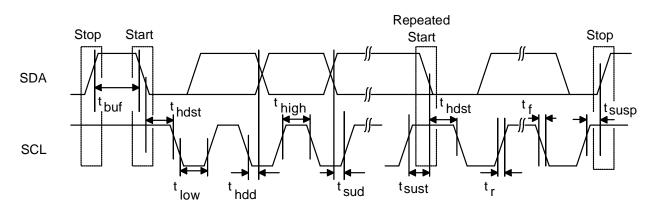

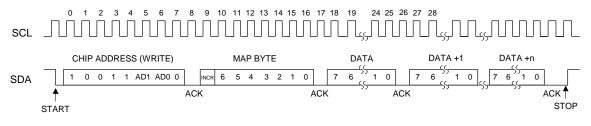

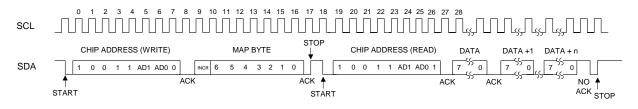

| Figure 8.Control Port Timing - I <sup>2</sup> C Format                |    |

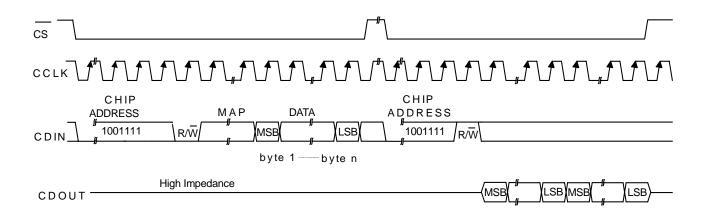

| Figure 9.Control Port Timing - SPI Format                             | 15 |

| Figure 10.CS44800 Pinout Diagram                                      |    |

| Figure 11. Typical Full-Bridge Connection Diagram                     |    |

| Figure 12. Typical Half-Bridge Connection Diagram                     |    |

| Figure 13.CS44800 Data Flow Diagram (Single Channel Shown)            |    |

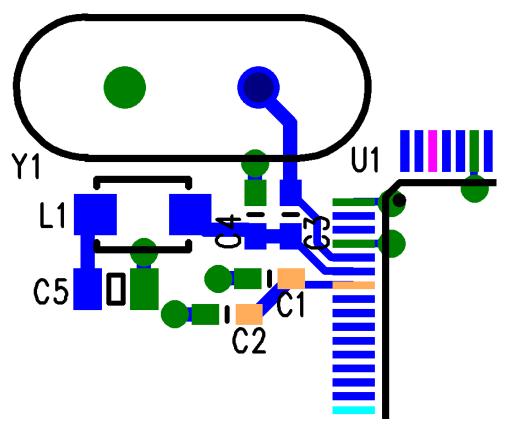

| Figure 14. Fundamental Mode Crystal Configuration                     | 25 |

| Figure 15.3rd Overtone Crystal Configuration                          | 26 |

| Figure 16.CS44800 Internal Clock Generation                           |    |

| Figure 17.I <sup>2</sup> S Serial Audio Formats                       |    |

| Figure 18.Left-Justified Serial Audio Formats                         |    |

| Figure 19.Right-Justified Serial Audio Formats                        | 29 |

| Figure 20.One Line Mode #1 Serial Audio Format                        | 29 |

| Figure 21.One Line Mode #2 Serial Audio Format                        | 30 |

| Figure 22.TDM Mode Serial Audio Format                                |    |

| Figure 23.De-Emphasis Curve                                           |    |

| Figure 24.Control Port Timing in SPI Mode                             |    |

| Figure 25.Control Port Timing, I <sup>2</sup> C Slave Mode Write      |    |

| Figure 26.Control Port Timing, I <sup>2</sup> C Slave Mode Read       |    |

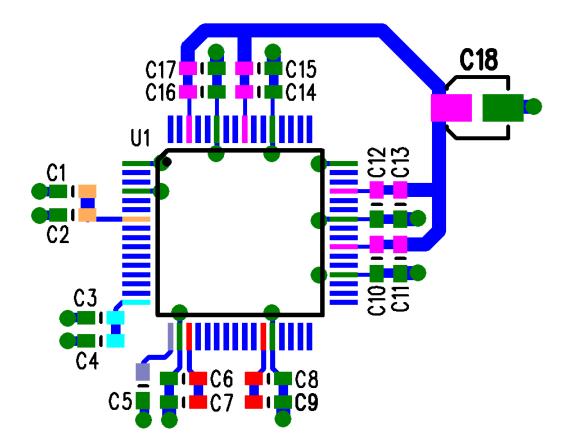

| Figure 27.Recommended CS44800 Power Supply Decoupling Layout          | 39 |

| Figure 28.Recommended CS44800 Crystal Circuit Layout                  |    |

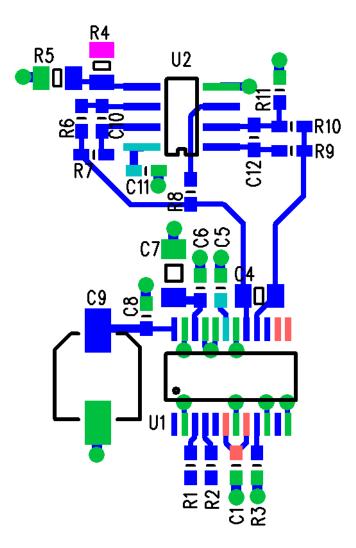

| Figure 29.Recommended PSR Circuit Layout                              |    |

| Figure 30.PSR Calibration Sequence                                    |    |

| Figure 31.PWM Output Delay                                            |    |

| Figure 32.64-Pin LQFP Package Drawing                                 | 78 |

# LIST OF TABLES

| Table 1. Common DAI_MCLK Frequencies                             | . 25 |

|------------------------------------------------------------------|------|

| Table 2. DAI Serial Audio Port Channel Allocations               | . 27 |

| Table 3. Load Compensation Example Settings                      | . 32 |

| Table 4. Typical PWM Switch Rate Settings                        | . 34 |

| Table 5. Digital Audio Interface Formats                         | . 53 |

| Table 6. Master Integer Volume Settings                          | . 57 |

| Table 7. Master Fractional Volume Settings                       |      |

| Table 8. Channel Integer Volume Settings                         | . 59 |

| Table 9. Channel Fractional Volume Settings                      | . 60 |

| Table 10. Limiter Attack Rate Settings                           | . 62 |

| Table 11. Limiter Release Rate Settings                          | . 62 |

| Table 12. Channel Load Compensation Filter Coarse Adjust         | . 63 |

| Table 13. Channel Load Compensation Filter Fine Adjust           | . 63 |

| Table 14. PWM Minimum Pulse Width Settings                       | . 70 |

| Table 15. Differential Signal Delay Settings                     |      |

| Table 16. Channel Delay Settings                                 |      |

| Table 17. Power Supply Sync Clock Divider Settings               | . 74 |

| Table 18. Decimator Shift/Scale Coefficient Calculation Examples |      |

# **1. CHARACTERISTICS AND SPECIFICATIONS**

(All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical performance characteristics and specifications are derived from measurements taken at nominal supply voltages and  $T_A = 25^{\circ}$ C.)

# SPECIFIED OPERATING CONDITIONS

(GND = 0 V, all voltages with respect to ground)

| Parameter                     |       | Symbol         | Min  | Тур | Max  | Units |

|-------------------------------|-------|----------------|------|-----|------|-------|

| DC Power Supply               |       |                |      |     |      |       |

| Digital                       | 2.5 V | VD             | 2.37 | 2.5 | 2.63 | V     |

| XTAL (Note 1)                 | 2.5 V | VDX            | 2.37 | 2.5 | 2.63 | V     |

|                               | 3.3 V |                | 3.14 | 3.3 | 3.47 | V     |

|                               | 5.0 V |                | 4.75 | 5.0 | 5.25 | V     |

| PWM Interface                 | 3.3 V | VDP            | 3.14 | 3.3 | 3.47 | V     |

|                               | 5.0 V |                | 4.75 | 5.0 | 5.25 | V     |

| Serial Audio Interface        | 2.5 V | VLS            | 2.37 | 2.5 | 2.63 | V     |

|                               | 3.3 V |                | 3.14 | 3.3 | 3.47 | V     |

|                               | 5.0 V |                | 4.75 | 5.0 | 5.25 | V     |

| Control Interface             | 2.5 V | VLC            | 2.37 | 2.5 | 2.63 | V     |

|                               | 3.3 V |                | 3.14 | 3.3 | 3.47 | V     |

|                               | 5.0 V |                | 4.75 | 5.0 | 5.25 | V     |

| Ambient Operating Temperature |       |                |      |     |      |       |

| Commercial                    | -CQZ  | Τ <sub>Α</sub> | -10  | -   | +70  | °C    |

| Automotive                    | -DQZ  |                | -40  | -   | +85  | °C    |

#### Notes:

1. When using external crystal, VDX = 3.14 V(min). When using clock signal input, VDX = 2.37 V(min).

# **ABSOLUTE MAXIMUM RATINGS**

(GND = 0 V; all voltages with respect to ground.)

| Parameters                    |                        | Symbol               | Min  | Max     | Units |

|-------------------------------|------------------------|----------------------|------|---------|-------|

| DC Power Supply               | Digital                | VD                   | -0.3 | 3.5     | V     |

|                               | XTAL                   | VDX                  | -0.3 | 6.0     | V     |

|                               | PWM Interface          | VDP                  | -0.3 | 6.0     | V     |

|                               | Serial Audio Interface | VLS                  | -0.3 | 6.0     | V     |

|                               | Control Interface      | VLC                  | -0.3 | 6.0     | V     |

| Input Current                 | (Note 2)               | l <sub>in</sub>      | -    | ±10     | mA    |

| Digital Input Voltage         | PWM Interface          | V <sub>IND-PWM</sub> | -0.3 | VDP+0.4 | V     |

| (Note 3)                      | Serial Audio Interface | V <sub>IND-S</sub>   | -0.3 | VLS+0.4 | V     |

|                               | Control Interface      | V <sub>IND-C</sub>   | -0.3 | VLC+0.4 | V     |

| Ambient Operating Temperature | -CQ                    | T <sub>A</sub>       | -20  | +85     | °C    |

| (power applied)               | -DQ                    |                      | -50  | +95     | °C    |

| Storage Temperature           |                        | T <sub>stg</sub>     | -65  | +150    | °C    |

**WARNING:** Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

- 2. Any pin except supplies. Transient currents of up to ±100 mA on the input pins will not cause SCR latch-up.

- 3. The maximum over/under voltage is limited by the input current.

# DC ELECTRICAL CHARACTERISTICS

(GND = 0 V, all voltages with respect to ground; DAI\_MCLK = 12.288 MHz, XTAL = 24.576 MHz, PWM Switch Rate = 384 kHz unless otherwise specified.)

| Para                            | Symbol                           | Min             | Тур | Max | Units |         |

|---------------------------------|----------------------------------|-----------------|-----|-----|-------|---------|

| Normal Operation (Note 4)       |                                  | •               |     |     | •     |         |

| Power Supply Current (Note 5)   | VD = 2.5 V                       | I <sub>D</sub>  | -   | 150 | -     | mA      |

|                                 | VDX = 3.3 V                      | I <sub>DX</sub> | -   | 2   | -     | mA      |

| VDP = 3.                        |                                  | I <sub>DP</sub> | -   | 1.2 | -     | mA      |

| VLS = 3.3 V                     |                                  | I <sub>LS</sub> | -   | 150 | -     | μA      |

|                                 | VLC = 3.3 V (Note 6)             | I <sub>LC</sub> | -   | 250 | -     | μA      |

| Power Dissipation VD=2.5 V, V   | VDX = VDP = VLS = VLC = 3.3 V    |                 | -   | 387 | 500   | mW      |

| Power Supply Rejection Ratio (N | ote 7) (1 kHz)                   | PSRR            | -   | 15  | -     | dB      |

| (60 Hz)                         |                                  |                 | -   | 40  | -     | dB      |

| Power-Down Mode (Note 8)        |                                  |                 |     |     |       | <u></u> |

| Power Supply Current            | All Supplies except VDX (Note 9) | I <sub>pd</sub> | -   | 80  | -     | μA      |

- 4. Normal operation is defined as  $\overline{RST}$  = HI with a 997 Hz, 0 dBFS input.

- 5. Current consumption increases with increasing XTAL clock rates and PWM switch rates. Variance between DAI clock rates is negligible.

- 6.  $I_{LC}$  measured with no external loading on the SDA pin.

- 7. Valid with PSRR function enabled and the recommended external ADC (CS4461) and filtering.

- 8. Power down mode is defined as  $\overline{RST}$  pin = LOW with all clock and data lines held static.

- 9. When  $\overline{RST}$  pin = LOW, the internal oscillator is active to provide a valid clock for the SYS\_CLK output.

# **DIGITAL INTERFACE CHARACTERISTICS**

(GND = 0 V, all voltages with respect to ground)

| Parameters (Note 1                                  | 0)                     | Symbol          | Min     | Тур | Max     | Units |

|-----------------------------------------------------|------------------------|-----------------|---------|-----|---------|-------|

| High-Level Input Voltage                            | XTAL                   |                 | 0.7xVDX | -   | -       | V     |

|                                                     | PWM Interface          | VIH             | 0.7xVDP | -   | -       | V     |

|                                                     | Serial Audio Interface |                 | 0.7xVLS | -   | -       | V     |

|                                                     | Control Interface      |                 | 0.7xVLC | -   | -       | V     |

| Low-Level Input Voltage                             | XTAL                   |                 | -       | -   | 0.2xVDX | V     |

|                                                     | PWM Interface          | VIL             | -       | -   | 0.2xVDP | V     |

|                                                     | Serial Audio Interface |                 | -       | -   | 0.2xVLS | V     |

|                                                     | Control Interface      |                 | -       | -   | 0.2xVLC | V     |

| High-Level Output Voltage at I <sub>o</sub> = -2 mA | PWM Interface          |                 | VDP-1.0 | -   | -       | V     |

|                                                     | Serial Audio Interface | V <sub>OH</sub> | VLS-1.0 | -   | -       | V     |

|                                                     | Control Interface      |                 | VLC-1.0 | -   | -       | V     |

| Low-Level Output Voltage at I <sub>o</sub> = 2 mA   | PWM Interface          |                 | -       | -   | 0.45    | V     |

|                                                     | Serial Audio Interface | V <sub>OL</sub> | -       | -   | 0.45    | V     |

|                                                     | Control Interface      |                 | -       | -   | 0.45    | V     |

| Input Leakage Current                               |                        | l <sub>in</sub> | -       | -   | ±10     | μA    |

| Input Capacitance                                   |                        |                 | -       | -   | 8       | pF    |

10. Serial Port signals include: SYS\_CLK, DAI\_MCLK, DAI\_SCLK, DAI\_LRCK, DAI\_SDIN1-4 Control Port signals include: SCL/CCLK, SDA/CDOUT, AD0/CS, AD1/CDIN, INT, RST, MUTE PWM signals include: PWMOUTA1-B4, PSR\_MCLK, PSR\_SYNC, PSR\_DATA, PS\_SYNC, GPI0[6:0]

## **PWM OUTPUT PERFORMANCE CHARACTERISTICS**

(Logic "0" = GND = 0 V; Logic "1" = VLS = VLC; VD = 2.5 V; DAI\_MCLK = 12.288 MHz; XTAL= 24.576 MHz; PWM Switch Rate = 384 kHz; Fs = 32 kHz to 192 kHz; Measurement bandwidth is 10 Hz to 20 kHz unless otherwise specified; Performance measurements taken with a full-scale 997 Hz.)

| Parameter                                  |            | Symbol | Min | Тур | Max | Unit |

|--------------------------------------------|------------|--------|-----|-----|-----|------|

| Dynamic Performance (Note 11)              |            |        |     |     |     |      |

| 24-Bits                                    | A-Weighted |        | 102 | 108 | -   | dB   |

|                                            | unweighted |        | 99  | 105 | -   | dB   |

| 16-Bits                                    | unweighted |        | -   | 96  | -   | dB   |

| Total Harmonic Distortion + Noise (Note 1  | 1)         |        |     |     |     |      |

| 24-Bits                                    | 0 dB       | THD+N  | -   | -90 | -85 | dB   |

|                                            | -20 dB     |        | -   | -77 | -   | dB   |

|                                            | -60 dB     |        | -   | -45 | -   | dB   |

| Idle Channel Noise / Signal-to-Noise Ratio |            |        | -   | 110 | -   | dB   |

| Interchannel Isolation                     | (1 kHz)    |        | -   | 100 | -   | dB   |

#### 11. Performance characteristics measured using filter shown in Figure 1.

Figure 1. Performance Characteristics Evaluation Active Filter Circuit

# **PWM FILTER CHARACTERISTICS**

(Logic "0" = GND = 0 V; Logic "1" = VLS = VLC; VD = 2.5 V; DAI\_MCLK = 12.288 MHz; XTAL = 24.576 MHz; PWM Switch Rate = 384 kHz; Fs = 32 kHz to 192 kHz; Measurement bandwidth is 10 Hz to 20 kHz unless otherwise specified.)

| Paramete                          | er                 | Min  | Тур       | Max   | Unit |

|-----------------------------------|--------------------|------|-----------|-------|------|

| Digital Filter Response (Note 12) |                    |      |           |       |      |

| Passband                          |                    |      |           |       |      |

| OSRATE = 0b                       | to -0.01 dB corner | 0    | -         | 1.6   | kHz  |

|                                   | to -3 dB corner    | 0    | -         | 24.0  | kHz  |

| OSRATE = 1b (Note 13)             | to -0.01 dB corner | 0    | -         | 3.3   | kHz  |

|                                   | to -3 dB corner    | 0    | -         | 44.5  | kHz  |

|                                   | Frequency Response |      |           |       |      |

| OSRATE = 0b                       | 10 Hz to 20 kHz    | -0.8 | -         | +0.02 | dB   |

| OSRATE = 1b (Note 13)             | 10 Hz to 40 kHz    | -1.2 | -         | +0.02 | dB   |

| Group Delay                       |                    |      | (Note 14) |       | ms   |

| De-emphasis Error                 | Fs = 32 kHz        | -    | -         | ±0.23 | dB   |

| (Relative to 1 kHz)               | Fs = 44.1 kHz      | -    | -         | ±0.14 | dB   |

|                                   | Fs = 48 kHz        | -    | -         | ±0.09 | dB   |

12. Filter response is not production tested but is characterized and guaranteed by design.

- 13. XTAL = 49.152 MHz; PWM Switch Rate = 768 kHz; Fs = 96 kHz to 192 kHz.

- 14. The equation for the group delay through the sample rate converter with OSRATE = 0b is (8.5 / Fsi) + (10 / Fso) ± (4.5 / Fsi). The equation for the group delay through the sample rate converter with OSRATE = 1b is (8.5 / Fsi) + (20 / Fso) ± (4.5 / Fsi).

# **SWITCHING CHARACTERISTICS - XTI**

(VD = 2.5 V, VDP = VLC = VLS = 3.3 V, VDX = 2.5 V to 5.0 V; Inputs: Logic 0 = GND, Logic 1 = VDX)

| Parameter                            | Symbol             | Min    | Тур | Max   | Unit |

|--------------------------------------|--------------------|--------|-----|-------|------|

| XTI period                           | t <sub>clki</sub>  | 18.518 |     | 40.69 | ns   |

| XTI high time                        | t <sub>clkih</sub> | 8.34   |     | 22.38 | ns   |

| XTI low time                         | t <sub>clkil</sub> | 8.34   |     | 22.38 | ns   |

| XTI Duty Cycle                       |                    | 45     | 50  | 55    | %    |

| External Crystal operating frequency |                    | 24.576 |     | 54    | MHz  |

Figure 2. XTI Timings

# SWITCHING CHARACTERISTICS - SYS\_CLK

(VD = 2.5 V, VDP = VLC = VDX = 3.3 V, VLS = 2.5 V to 5.0 V, Cload = 50 pF)

| Parameter          | Symbol             | Min    | Тур | Max | Unit |

|--------------------|--------------------|--------|-----|-----|------|

| SYS_CLK Period     | t <sub>sclki</sub> | 18.518 |     |     | ns   |

| SYS_CLK Duty Cycle |                    | 45     | 50  | 55  | %    |

| SYS_CLK _          |                    |        |     |     |      |

# **SWITCHING CHARACTERISTICS - PWMOUTA1-B4**

(VD = 2.5 V, VLS = VLC = VDX = 3.3 V, VDP = 3.3 V to 5.0 V unless otherwise specified, Cload = 10 pF)

| Parameter             |                            | Symbol           | Min  | Тур        | Max  | Unit     |

|-----------------------|----------------------------|------------------|------|------------|------|----------|

| PWMOUTxx Period       |                            | t <sub>pwm</sub> | 2.60 | -          | 1.18 | μs       |

| Rise Time of PWMOUTxx | VDP = 5.0 V<br>VDP = 3.3 V |                  | -    | 1.6<br>2.1 | -    | ns<br>ns |

| Fall Time of PWMOUTxx | VDP = 5.0 V<br>VDP = 3.3 V |                  | -    | 1.1<br>1.4 | -    | ns<br>ns |

Figure 4. PWMOUTxx Timings

# SWITCHING CHARACTERISTICS - PS\_SYNC

(VD = 2.5 V, VLS = VLC = VDX = 3.3 V, VDP = 3.3 V to 5.0 V, Cload = 20 pF)

| Parameter          | Symbol              | Min     | Тур | Max | Unit |

|--------------------|---------------------|---------|-----|-----|------|

| PS_SYNC Period     | t <sub>psclki</sub> | 592.576 |     |     | ns   |

| PS_SYNC Duty Cycle |                     | 45      | 50  | 55  | %    |

Figure 5. PS\_SYNC Timings

## **SWITCHING CHARACTERISTICS - DAI INTERFACE**

(VD = 2.5 V, VDX = VDP = VLC = 3.3 V, VLS = 2.5 V to 5.0 V; Inputs: Logic 0 = GND, Logic 1 = VLS.)

| Parameters                                      |           | Symbol             | Min | Max | Units |

|-------------------------------------------------|-----------|--------------------|-----|-----|-------|

| RST pin Low Pulse Width                         | (Note 15) |                    | 1   | -   | ms    |

| DAI_MCLK Duty Cycle                             | (Note 16) |                    | 40  | 60  | %     |

| DAI_SCLK Duty Cycle                             |           |                    | 45  | 55  | %     |

| DAI_LRCK Duty Cycle                             |           |                    | 45  | 55  | %     |

| DAI Sample Rate                                 | (Note 17) | Fs                 | 32  | 192 | kHz   |

| DAI_SDIN Setup Time Before DAI_SCLK Rising Edge |           | t <sub>ds</sub>    | 10  | -   | ns    |

| DAI_SDIN Hold Time After DAI_SCLK Rising Edge   |           | t <sub>dh</sub>    | 10  | -   | ns    |

| DAI_SCLK High Time                              |           | t <sub>sckh</sub>  | 20  | -   | ns    |

| DAI_SCLK Low Time                               |           | t <sub>sckl</sub>  | 20  | -   | ns    |

| DAI_LRCK Setup Time Before DAI_SCLK Rising Edge |           | t <sub>lrcks</sub> | 25  | -   | ns    |

| DAI_SCLK Rising Edge Before DAI_LRCK Edge       |           | t <sub>lrckd</sub> | 25  | -   | ns    |

15. After powering up, the CS44800, RST should be held low until after the power supplies and clocks are settled.

- 16. See Table 1 on page 26 for suggested MCLK frequencies.

- 17. Max DAI sample rate is 96 kHz for One Line and TDM modes of operation.

Figure 6. Serial Audio Interface Timing

Figure 7. Serial Audio Interface Timing - TDM Mode

# SWITCHING CHARACTERISTICS - CONTROL PORT - I<sup>2</sup>C FORMAT

(VD = 2.5 V, VDX = VDP = VLS = 3.3 V; VLC = 2.5 V to 5.0 V; Inputs: Logic 0 = GND, Logic 1 = VLC, C<sub>L</sub> = 30 pF)

| Parameter                                              | Symbol            | Min | Max  | Unit |

|--------------------------------------------------------|-------------------|-----|------|------|

| SCL Clock Frequency                                    | f <sub>scl</sub>  | -   | 100  | kHz  |

| Bus Free Time between Transmissions                    | t <sub>buf</sub>  | 4.7 | -    | μs   |

| Start Condition Hold Time (prior to first clock pulse) | t <sub>hdst</sub> | 4.0 | -    | μs   |

| Clock Low time                                         | t <sub>low</sub>  | 4.7 | -    | μs   |

| Clock High Time                                        | t <sub>high</sub> | 4.0 | -    | μs   |

| Setup Time for Repeated Start Condition                | t <sub>sust</sub> | 4.7 | -    | μs   |

| SDA Hold Time from SCL Falling (Note 18)               | t <sub>hdd</sub>  | 10  | -    | ns   |

| SDA Setup time to SCL Rising                           | t <sub>sud</sub>  | 250 | -    | ns   |

| Rise Time of SCL and SDA                               | t <sub>r</sub>    | -   | 1000 | ns   |

| Fall Time SCL and SDA                                  | t <sub>f</sub>    | -   | 300  | ns   |

| Setup Time for Stop Condition                          | t <sub>susp</sub> | 4.7 | -    | μs   |

18. Data must be held for sufficient time to bridge the transition time,  $t_{f}$ , of SCL.

Figure 8. Control Port Timing - I<sup>2</sup>C Format

# SWITCHING CHARACTERISTICS - CONTROL PORT - SPI FORMAT

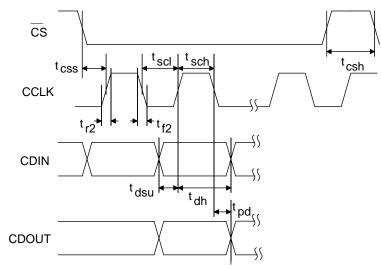

(VD = 2.5 V, VDP = VLS = 3.3 V; VLC = 2.5 V to 5.0 V; Inputs: Logic 0 = GND, Logic 1 = VLC,  $C_L$  = 30 pF)

| Parameter                               | Symbol           | Min | Тур | Max | Units |

|-----------------------------------------|------------------|-----|-----|-----|-------|

| CCLK Clock Frequency                    | f <sub>sck</sub> | 0   | -   | 6.0 | MHz   |

| CS High Time between Transmissions      | t <sub>csh</sub> | 1.0 | -   | -   | μs    |

| CS Falling to CCLK Edge                 | t <sub>css</sub> | 20  | -   | -   | ns    |

| CCLK Low Time                           | t <sub>scl</sub> | 66  | -   | -   | ns    |

| CCLK High Time                          | t <sub>sch</sub> | 66  | -   | -   | ns    |

| CDIN to CCLK Rising Setup Time          | t <sub>dsu</sub> | 40  | -   | -   | ns    |

| CCLK Rising to DATA Hold Time (Note 19) | t <sub>dh</sub>  | 15  | -   | -   | ns    |

| CCLK Falling to CDOUT Stable            | t <sub>pd</sub>  | -   | -   | 50  | ns    |

| Rise Time of CDOUT                      | t <sub>r1</sub>  | -   | -   | 25  | ns    |

| Fall Time of CDOUT                      | t <sub>f1</sub>  | -   | -   | 25  | ns    |

| Rise Time of CCLK and CDIN (Note 20)    | t <sub>r2</sub>  | -   | -   | 100 | ns    |

| Fall Time of CCLK and CDIN (Note 20)    | t <sub>f2</sub>  | -   | -   | 100 | ns    |

19. Data must be held for sufficient time to bridge the transition time of CCLK.

20. For f<sub>sck</sub> <1 MHz.

Figure 9. Control Port Timing - SPI Format

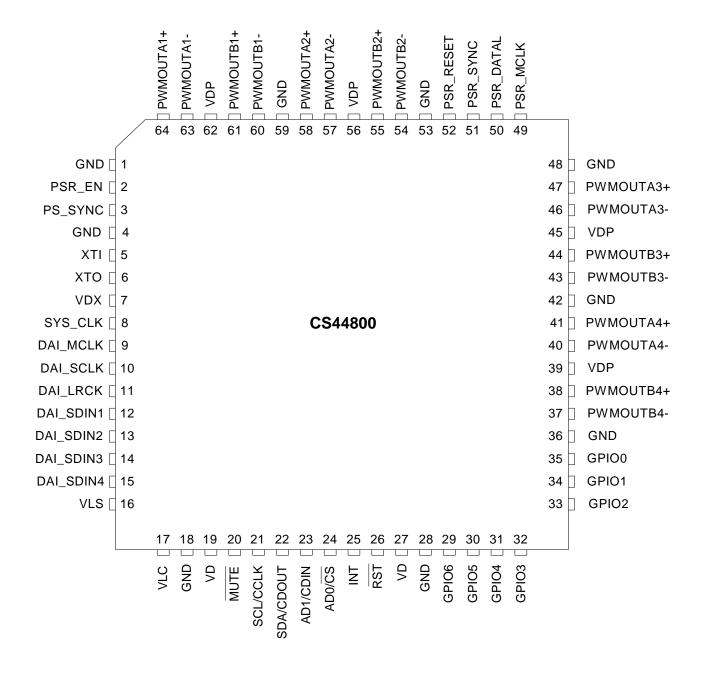

# 2. PIN DESCRIPTIONS

Figure 10. CS44800 Pinout Diagram

Pin Name Pin #

Pin Description

CS44800

#

| PS_SYNC                                          | 3                    | <b>Power Supply Synchronization Clock</b> ( <i>Output</i> ) - The PWM synchronized clock to the switch mode power supply.                                                                                                                                                                             |

|--------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ХТІ                                              | 5                    | <b>Crystal Oscillator Input</b> ( <i>Input</i> ) - Crystal Oscillator input or accepts an external clock input signal that is used to drive the internal PWM core logic.                                                                                                                              |

| ХТО                                              | 6                    | Crystal Oscillator Output (Output) - Crystal Oscillator output.                                                                                                                                                                                                                                       |

| SYS_CLK                                          | 8                    | <b>External System Clock</b> ( <i>Output</i> ) - Clock output. This pin provides a divided down clock derived from the XTI input.                                                                                                                                                                     |

| DAI_MCLK                                         | 9                    | Digital Audio Input Master Clock (Input) - Master audio clock.                                                                                                                                                                                                                                        |

| DAI_SCLK                                         | 10                   | <b>Digital Audio Input Serial Clock</b> <i>(Input)</i> - Serial clock for the Digital Audio Input Inter-<br>face. The clock frequency is a multiple of the Left/Right Clock running at Fs.                                                                                                            |

| DAI_LRCK                                         | 11                   | <b>Digital Audio Input Left/Right Clock</b> ( <i>Input</i> ) - Determines which channel, Left or Right, is currently active on the serial audio data line. The rate is determined by the sampling frequency Fs.                                                                                       |

| DAI_SDIN1<br>DAI_SDIN2<br>DAI_SDIN3<br>DAI_SDIN4 | 12<br>13<br>14<br>15 | Digital Audio Input Serial Data (Input) - Input for two's complement serial audio data.                                                                                                                                                                                                               |

| MUTE                                             | 20                   | <b>Mute</b> ( <i>Input</i> ) - The device will perform a hard mute on all channels. All internal registers are not reset to their default settings.                                                                                                                                                   |

| SCL/CCLK                                         | 21                   | <b>Serial Control Port Clock</b> ( <i>Input</i> ) - Serial clock for the serial control port. Requires an external pull-up resistor to the logic interface voltage in I <sup>2</sup> C mode as shown in the Typical Connection Diagram.                                                               |

| SDA/CDOUT                                        | 22                   | <b>Serial Control Data</b> ( <i>Input/Output</i> ) - SDA is a data I/O line in I <sup>2</sup> C mode and requires an external pull-up resistor to the logic interface voltage, as shown in the Typical Connection Diagram.; CDOUT is the output data line for the control port interface in SPI mode. |

| AD1/CDIN                                         | 23                   | Address Bit 1 (I <sup>2</sup> C)/Serial Control Data (SPI) ( <i>Input</i> ) - AD1 is a chip address pin in I <sup>2</sup> C mode.;CDIN is the input data line for the control port interface in SPI mode.                                                                                             |

| AD0/CS                                           | 24                   | Address Bit 0 (I <sup>2</sup> C)/Control Port Chip Select (SPI) ( <i>Input</i> ) - AD0 is a chip address pin in I <sup>2</sup> C mode; CS is the chip select signal in SPI mode.                                                                                                                      |

| INT                                              | 25                   | <b>Interrupt Request</b> ( <i>Output</i> ) - CMOS or open-drain interrupt request output. This pin is driven to the configured active state to indicate that the PWM Controller has status data that should be read by the host.                                                                      |

| RST                                              | 26                   | <b>Reset</b> ( <i>Input</i> ) - The device enters a low power mode and all internal registers are reset to their default settings when low.                                                                                                                                                           |

| GPIO6                                            | 29                   | <b>General Purpose Input, Output</b> ( <i>Input/Output</i> ) - This pin is configured as an input following a RST condition. It can be configured as a general purpose input or output which can be individually controlled by the Host Controller.                                                   |

| GPIO5                                            | 30                   | <b>General Purpose Input, Output</b> ( <i>Input/Output</i> ) - This pin is configured as an input following a RST condition. It can be configured as a general purpose input or output which can be individually controlled by the Host Controller.                                                   |

| GPIO4                                            | 31                   | <b>General Purpose Input, Output</b> ( <i>Input/Output</i> ) - This pin is configured as an input following a RST condition. It can be configured as a general purpose input or output which can be individually controlled by the Host Controller.                                                   |

| GPIO3                                            | 32                   | <b>General Purpose Input, Output</b> ( <i>Input/Output</i> ) - This pin is configured as an input following a RST condition. It can be configured as a general purpose input or output which can be individually controlled by the Host Controller.                                                   |

| GPIO2     | 33     | <b>General Purpose Input, Output</b> ( <i>Input/Output</i> ) - This pin is configured as an input following a RST condition. It can be configured as a general purpose input or output which can be individually controlled by the Host Controller. |

|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO1     | 34     | <b>General Purpose Input, Output</b> ( <i>Input/Output</i> ) - This pin is configured as an input following a RST condition. It can be configured as a general purpose input or output which can be individually controlled by the Host Controller. |

| GPIO0     | 35     | <b>General Purpose Input, Output</b> ( <i>Input/Output</i> ) - This pin is configured as an input following a RST condition. It can be configured as a general purpose input or output which can be individually controlled by the Host Controller. |

| PSR_MCLK  | 49     | <b>Power Supply Rejection Master Clock</b> ( <i>Output</i> ) - Master audio clock for external PSR ADC (CS4461).                                                                                                                                    |

| PSR_DATAL | 50     | <b>Power Supply Rejection Input Serial Data</b> ( <i>Input</i> ) - Input for serial audio data from external PSR ADC (CS4461).                                                                                                                      |

| PSR_SYNC  | 51     | <b>Power Supply Rejection Sync Clock</b> <i>(Input)</i> - Synchronization signal for external PSR ADC (CS4461).                                                                                                                                     |

| PSR_RESET | 52     | <b>Power Supply Rejection Reset</b> ( <i>Output</i> ) - The reset pin for the external Power Supply Rejection circuitry.                                                                                                                            |

| PSR_EN    | 2      | <b>Power Supply Rejection Enable</b> ( <i>Output</i> ) - The enable pin for the external Power Supply Rejection circuitry.                                                                                                                          |

| PWMOUTA1+ | 64     |                                                                                                                                                                                                                                                     |

| PWMOUTA1- | 63     |                                                                                                                                                                                                                                                     |

| PWMOUTB1+ | 61     |                                                                                                                                                                                                                                                     |

| PWMOUTB1- | 60     |                                                                                                                                                                                                                                                     |

| PWMOUTA2+ | 58     |                                                                                                                                                                                                                                                     |

| PWMOUTA2- | 57     |                                                                                                                                                                                                                                                     |

| PWMOUTB2+ | 55     |                                                                                                                                                                                                                                                     |

| PWMOUTB2- | 54     | <b>PWM Output</b> ( <i>Output</i> ) - PWM control signals for the Class D amplifier backend.                                                                                                                                                        |

| PWMOUTA3+ | 47     |                                                                                                                                                                                                                                                     |

| PWMOUTA3- | 46     |                                                                                                                                                                                                                                                     |

| PWMOUTB3+ | 44     |                                                                                                                                                                                                                                                     |

| PWMOUTB3- | 43     |                                                                                                                                                                                                                                                     |

| PWMOUTA4+ | 41     |                                                                                                                                                                                                                                                     |

| PWMOUTA4- | 40     |                                                                                                                                                                                                                                                     |

| PWMOUTB4+ | 38     |                                                                                                                                                                                                                                                     |

| PWMOUTB4- | 37     |                                                                                                                                                                                                                                                     |

| VDX       | 7      | Crystal Power ( <i>Input</i> ) - Positive power supply for the Crystal section.                                                                                                                                                                     |

| VD        | 19, 27 | <b>Digital Power</b> ( <i>Input</i> ) - Positive power supply for the digital section.                                                                                                                                                              |

| VLC       | 17     | <b>Host Interface Power</b> ( <i>Input</i> ) - Determines the required signal level for the digital input/output signals for the host interface.                                                                                                    |

| VLS       | 16     | <b>Digital Audio Interface Power</b> ( <i>Input</i> ) - Determines the required signal level for the digital input signals for the digital audio interface.                                                                                         |

| VDP       |        | <b>PWM Interface Power</b> ( <i>Input</i> ) - Determines the required signal level for the digital input/output signals for the PWM and GPIO interface.                                                                                             |

|     | 1, 4,<br>18, 28,                                                                        |

|-----|-----------------------------------------------------------------------------------------|

| GND | 36, 42, <b>Digital Ground</b> ( <i>Input</i> ) - Ground reference for digital circuits. |

|     | 48, 53,                                                                                 |

|     | 59                                                                                      |

## 2.1 I/O Pin Characteristics

| Signal Name | Power<br>Rail | I/O               | Driver                        | Receiver                                                |

|-------------|---------------|-------------------|-------------------------------|---------------------------------------------------------|

| RST         | VLC           | Input             | -                             | 2.5 V and 3.3/5.0 V TTL Compatible.                     |

| SCL/CCLK    | VLC           | Input             | -                             | 2.5 V and 3.3/5.0 V TTL Compatible, with Hysteresis.    |

| SDA/CDOUT   | VLC           | Input /<br>Output | 2.5-5.0 V,<br>CMOS/Open Drain | 2.5 V and 3.3/5.0 V TTL Compatible, with Hysteresis.    |

| AD0/CS      | VLC           | Input             | -                             | 2.5 V and 3.3/5.0 V TTL Compatible, Internal pull-up.   |

| AD1/CDIN    | VLC           | Input             | -                             | 2.5 V and 3.3/5.0 V TTL Compatible, Internal pull-up.   |

| INT         | VLC           | Output            | 2.5-5.0 V,<br>CMOS/Open Drain | -                                                       |

| MUTE        | VLC           | Input             | -                             | 2.5 V and 3.3/5.0 V TTL Compatible.                     |

| DAI_SDINx   | VLS           | Input             | -                             | 2.5 V and 3.3/5.0 V TTL Compatible.                     |

| DAI_SCLK    | VLS           | Input             | -                             | 2.5 V and 3.3/5.0 V TTL Compatible.                     |

| DAI_LRCK    | VLS           | Input             | -                             | 2.5 V and 3.3/5.0 V TTL Compatible.                     |

| DAI_MCLK    | VLS           | Input             | -                             | 2.5 V and 3.3/5.0 V TTL Compatible.                     |

| SYS_CLK     | VLS           | Output            | 2.5-5.0 V, CMOS               | -                                                       |

| ХТІ         | VDX           | Input             | -                             | 2.5 V and 3.3/5.0 V TTL Compatible, Internal pull-down. |

| хто         | VDX           | Output            | -                             | -                                                       |

| GPIOx       | VDP           | Input /<br>Output | 3.3/5.0 V,<br>CMOS/Open Drain | 3.3/5.0 V TTL Compatible.                               |

| PWMOUTAx+/- | VDP           | Output            | 3.3/5.0 V, CMOS               | -                                                       |

| PWMOUTBx+/- | VDP           | Output            | 3.3/5.0 V, CMOS               | -                                                       |

| PSR_MCLK    | VDP           | Output            | 3.3/5.0 V, CMOS               | -                                                       |

| PSR_SYNC    | VDP           | Input             | -                             | 3.3/5.0 V TTL Compatible, Internal pull-up.             |

| PSR_DATA    | VDP           | Input             | -                             | 3.3/5.0 V TTL Compatible, Internal pull-up.             |

| PSR_EN      | VDP           | Output            | 3.3/5.0 V, CMOS               | -                                                       |

| PSR_RESET   | VDP           | Output            | 3.3/5.0 V, CMOS               | -                                                       |

| PS_SYNC     | VDP           | Output            | 3.3/5.0 V, CMOS               | -                                                       |

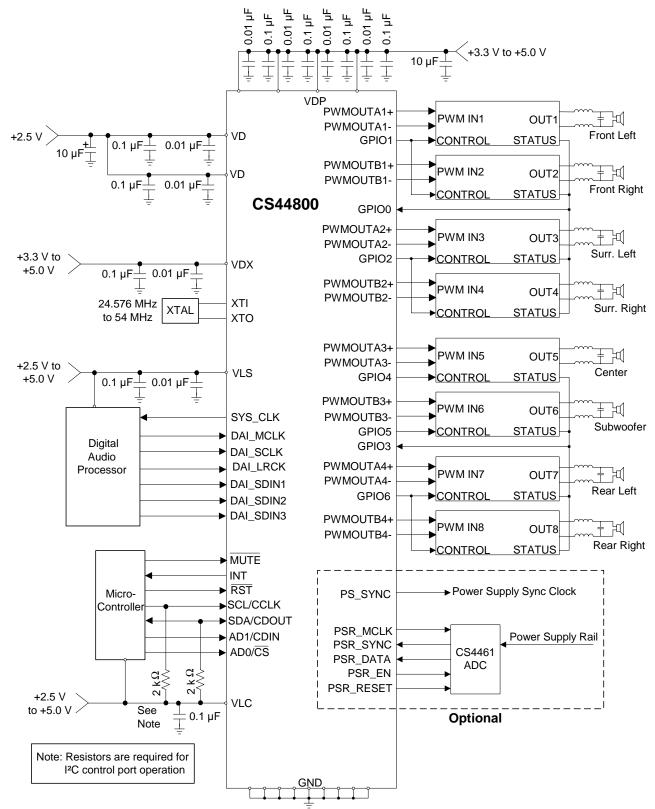

## 3. TYPICAL CONNECTION DIAGRAMS

Figure 12. Typical Half-Bridge Connection Diagram

# 4. APPLICATIONS

#### 4.1 Overview

The CS44800 is a multi-channel digital-to-PWM Class D audio system controller including interpolation, sample rate conversion, half- and full-bridge PWM driver outputs, and power supply rejection feedback in a 64-pin LQFP package. The architecture uses a direct-to-digital approach that maintains digital signal integrity to the final output filter, minimizing analog interference effects which negatively affect system performance.

The CS44800 integrates on-chip sample rate conversion, digital volume control, peak detect with volume limiter, de-emphasis, programmable interrupt conditions, and the ability to change the PWM switch rate to eliminate AM frequency interference. The CS44800 also has a programmable load compensation filter, which allows the speaker load to vary while the output filter remains fixed, maintaining a flat frequency response. For single-ended half-bridge applications PWM Popguard<sup>®</sup> reduces the transient pops and clicks and realtime power supply feedback reduces noise coupling from the power supply. The PWM amplifier can achieve greater than 90% efficiency. This efficiency provides for a smaller device package, less heat sink requirements, and smaller power supplies.

The CS44800 is ideal for audio systems requiring wide dynamic range, negligible distortion, and low noise such as A/V receivers, DVD receivers, digital speaker, and automotive audio systems.

#### 4.2 Feature Set Summary

#### **Core Features**

- 2.5 V digital core voltage, VD.

- VLC voltage pin for host interface logic levels between 2.5 V and 5.0 V.

- VLS voltage pin for digital audio interface logic levels between 2.5 V and 5.0 V.

- VDP voltage pin for PWM backend interface logic levels between 3.3 V and 5.0 V.

- VDX voltage pin for clock input signals between 2.5 V and 5.0 V.

#### Clocking

- Minimum of 128Fs DAI\_MCLK for DAI serial interface.

- DAI interface uses automatic detection of LRCK/MCLK ratio to configure internal DAI/SRC clocks.

- All PWM Processing clocks generated internally via:

- An external crystal 24.576 MHz to 54 MHz, or

- XTI input pin capable of supporting a clock signal at the VDX voltage level.

- Programmable divide of XTI by 1, 2, 4, 8 for SYS\_CLK output.

- Programmable divide of XTI by 32, 64, 128, 256 for PS\_SYNC (power supply synchronization signal).

#### **Digital Audio Playback**

- Supports 32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz, 176.4 kHz and 192 kHz sample frequencies.

- High performance sample rate converter.

- 16, 20 and 24 bit audio sample lengths.

- De-emphasis for 32 kHz, 44.1 kHz, 48 kHz.

- Digital volume control with soft ramp.

- Individual channel volume gain, attenuation and mute capability; +24 to -127 dB in 0.25 dB steps.

- Master volume attenuation; +24 to -127 dB in 0.25 dB steps.

- Peak Detect and Volume Limiter with programmable attack and release rates.

- Signal-clipping interrupt indicator.

#### **Additional Features**

- Contains a two-stage digital output filter for speaker impedance compensation.

- Provides 7 programmable GPIO pins with interrupt generation for easily interfacing to a variety of commonly available power state parts. Interrupts can be masked.

- Selectable over-sample rate for increased audio bandwidth.

- Power supply clock output, PS\_SYNC, with programmable divider

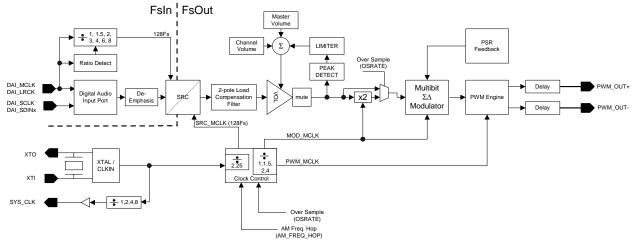

Figure 13. CS44800 Data Flow Diagram (Single Channel Shown)

#### 4.3 Clock Generation

The sources for internal clock generation for the PWM processing are as follows:

- FsIn Domain:

- DAI\_MCLK, minimum 128Fs

- FsOut Domain:

- XTI/XTO (Fundamental or 3<sup>rd</sup> overtone crystal), or

- Clock signal on XTI (VDX is used to set logic voltage level)

#### 4.3.1 FsIn Domain Clocking

| Mode<br>(sample-rate range) | Sample<br>Rate<br>(kHz) | DAI_MCLK (MHz) |         |         |         |         |  |

|-----------------------------|-------------------------|----------------|---------|---------|---------|---------|--|

| DAI_MCLK/LRCK               | K Ratio ->              | 256x           | 384x    | 512x    | 768x    | 1024x   |  |

| Single Speed                | 32                      | 8.1920         | 12.2880 | 16.3840 | 24.5760 | 32.7680 |  |

| (4 to 50 kHz)               | 44.1                    | 11.2896        | 16.9344 | 22.5792 | 33.8688 | 45.1584 |  |

|                             | 48                      | 12.2880        | 18.4320 | 24.5760 | 36.8640 | 49.1520 |  |

| DAI_MCLK/LRCK               | K Ratio ->              | 128x           | 192x    | 256x    | 384x    | 512x    |  |

| Double Speed                | 64                      | 8.1920         | 12.2880 | 16.3840 | 24.5760 | 32.7680 |  |

| (50 to 100 kHz)             | 88.2                    | 11.2896        | 16.9344 | 22.5792 | 33.8688 | 45.1584 |  |

|                             | 96                      | 12.2880        | 18.4320 | 24.5760 | 36.8640 | 49.1520 |  |

| DAI_MCLK/LRCK               | K Ratio ->              | 64x            | 96x     | 128x    | 192x    | 256x    |  |

| Quad Speed                  | 176.4                   | n/a            | n/a     | 22.5792 | 33.8688 | 45.1584 |  |

| (100 to 200 kHz)            | 192                     | n/a            | n/a     | 24.5760 | 36.8640 | 49.1520 |  |

Common DAI\_MCLK frequencies and sample rates are shown in Table 1.

Table 1. Common DAI\_MCLK Frequencies

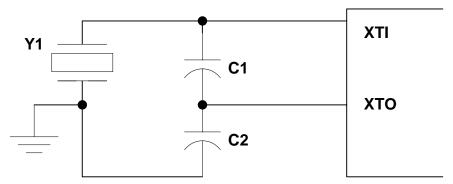

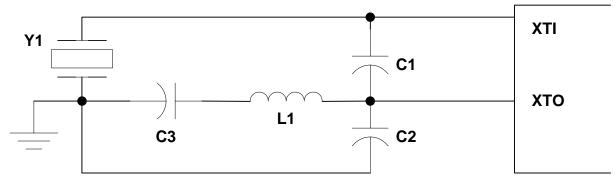

#### 4.3.2 FsOut Domain Clocking

To ensure the highest quality conversion of PWM signals, the CS44800 is capable of operating from a fundamental mode or 3<sup>rd</sup> overtone crystal, or a clock signal attached to XTI, at a frequency of 24.576 MHz to 54 MHz. If XTI is being directly driven by a clock signal, XTO can be left floating or tied to ground through a pull-down resistor and the internal oscillator should be powered down using the PDN\_XTAL bit in register 02h.

Figure 14. Fundamental Mode Crystal Configuration

Figure 15. 3<sup>rd</sup> Overtone Crystal Configuration

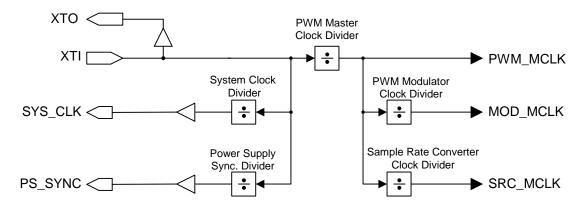

Appropriate clock dividers for each functional block and a programmable divider to support an output for switched-mode power supply synchronization are provided. The clock generation for the CS44800 is shown in the Figure 16.

Figure 16. CS44800 Internal Clock Generation

#### 4.4 FsIn Clock Domain Modules

#### 4.4.1 Digital Audio Input Port

The CS44800 interfaces to an external Digital Audio Processor via the Digital Audio Input serial port, the DAI serial port. The DAI port has 4 stereo data inputs with support for I<sup>2</sup>S, left-justified and right-justified formats. The DAI port operates in slave operation only, where DAI\_LRCK, DAI\_SCLK and DAI\_MCLK are always inputs. The signal DAI\_LRCK must be equal to the sample rate, Fs and must be synchronously derived from the supplied master clock, DAI\_MCLK. The serial bit clock, DAI\_SCLK, is used to sample the data bits and must be synchronously derived from the master clock.

DAI\_SDIN1, DAI\_SDIN2, DAI\_SDIN3, and DAI\_SDIN4 are the serial data input pins supplying the associated internal PWM channel modulators. The serial data interface format selection (left-justified, right-justified, I<sup>2</sup>S, one line mode, or TDM) for the DAI serial port data input pins is configured using the appropriate bits in the register "Misc. Configuration (address 04h)" on page 52. The serial audio data is presented in 2's complement binary form with the MSB first in all formats.

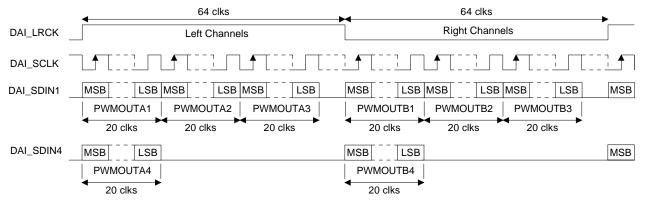

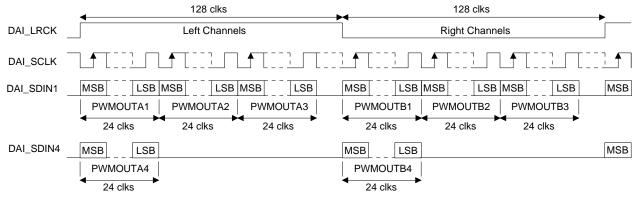

When operated in One Line Data Mode, 6 channels of PWM data are input on DAI\_SDIN1 and two additional PWM channels on DAI\_SDIN4. In TDM mode, all 8 channels are multiplexed onto the DAI\_SDIN1 data line. Table 2 outlines the serial port channel allocations.

| Serial Data Inputs | Data mode                       | Channel Assignments                            |

|--------------------|---------------------------------|------------------------------------------------|

| DAI_SDIN1          | Normal (I <sup>2</sup> S,LJ,RJ) | PWMOUTA1(left channel)/PWMOUTB1(right channel) |

|                    | One Line #1 or #2               | PWMOUTA1/A2/A3/B1/B2/B3                        |

|                    | TDM                             | PWMOUTA1/A2/A3/A4/B1/B2/B3/B4                  |

| DAI_SDIN2          | Normal (I <sup>2</sup> S,LJ,RJ) | PWMOUTA2(left channel)/PWMOUTB2(right channel) |

|                    | One Line #1 or #2               | not used                                       |

|                    | TDM                             | not used                                       |

| DAI_SDIN3          | Normal (I <sup>2</sup> S,LJ,RJ) | PWMOUTA3(left channel)/PWMOUTB3(right channel) |

|                    | One Line #1 or #2               | not used                                       |

|                    | TDM                             | not used                                       |

| DAI_SDIN4          | Normal (I <sup>2</sup> S,LJ,RJ) | PWMOUTA4(left channel)/PWMOUTB4(right channel) |

|                    | One Line #1 or #2               | PWMOUTA4/B4                                    |

|                    | TDM                             | not used                                       |

#### Table 2. DAI Serial Audio Port Channel Allocations

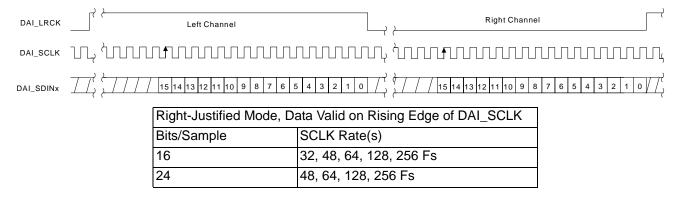

The DAI digital audio serial ports support 6 formats with varying bit depths from 16 to 24 as shown in Figure 17, Figure 18, Figure 19, Figure 20, Figure 21 and Figure 22. These formats are selected using the configuration bits in the "Misc. Configuration (address 04h)" on page 52.

#### 4.4.1.1 I<sup>2</sup>S Data Format

For I<sup>2</sup>S, data is received most significant bit first, one DAI\_SCLK delay after the transition of DAI\_LRCK, and is valid on the rising edge of DAI\_SCLK. For the I<sup>2</sup>S format, the left channel data is presented when DAI\_LRCK is low; the right channel data is presented when DAI\_LRCK is high.

| DAI_LRCK  | Left Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Right Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |