SLWS227A - NOVEMBER 2010 - REVISED MARCH 2011

# **Wideband Transmit-Receive Digital Signal Processors**

Check for Samples: GC6016

## **FEATURES**

- Integrated Transmit and Receive Digital IF Solution

- Up to 4 TX, 8 RX

- TX-Transmit Includes DUC, CFR, TX Equalizer, and Bulk Upconverter

- CFR: 6-dB PAR for WCDMA, 7-db LTE Signals With EVM Meeting 3GPP Specs; Configurable for All Major Wireless Infrastructure Standards

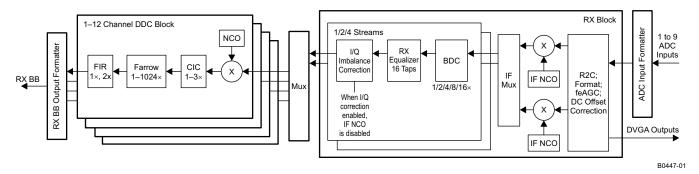

- RX-Receive Includes DC-Offset Cancellation, Front-End and Back-End AGC, Bulk Downconverter, RX Equalizer, I/Q Imbalance Correction, DDC

- 4 DDUCs, 1–12 Channels per DDUC, Each DDUC Can Be Programmed to TX or RX, at a Common Resampler Rate – Multimode Support

- Seamless Interface to TI High-Speed Data Converters

- 4 TX Aggregate Output to DACs up to 930 MSPS Complex

- 8 RX Aggregate Input From ADCs up to 1.24 GSPS Real

- 16-Tap (Complex) RX Equalizers

- Two 4K Complex Word Capture Buffers for Signal Analysis, and Adaptive Filtering

- 1.1-V Core, 3.3-V I/O CMOS, 1.8-V I/O LVDS

- Power Consumption, 3.5 W Typical

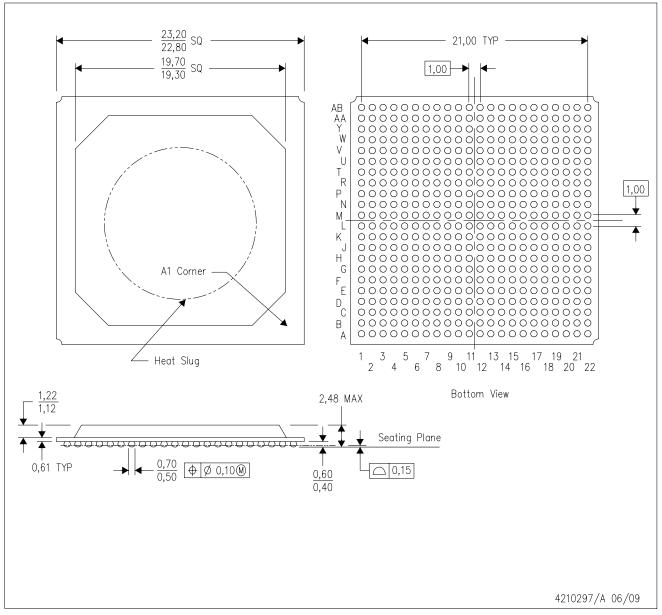

- 484-Ball TE-PBGA Package, 23 mm × 23 mm

## **APPLICATIONS**

- Multi-Standard Base Stations

- 3GPP (LTE, W-CDMA, TDS-CDMA)

- MC-GSM

- WiMAX and WiBro (OFDMA)

- Multi-Carrier Power Amplifiers (MCPAs)

- · Wireless Infrastructure Repeaters

- Digital Radio Instrumentation and Test Equipment

#### DESCRIPTION

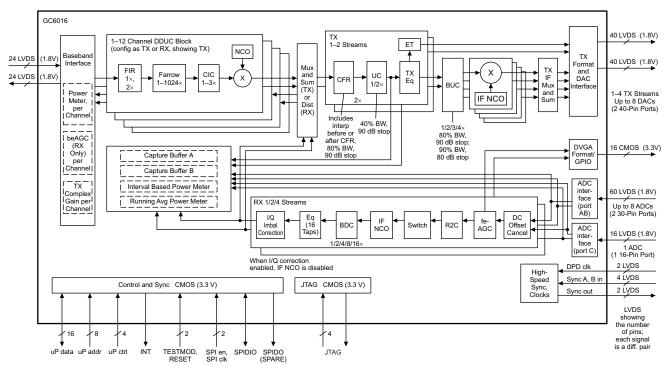

The GC6016 is a wideband transmit and receive signal processor that includes digital downconverter / upconverter (DDUC), transmit, receive, and capture buffer blocks. The transmit path includes crest factor reduction (CFR), complex equalization, and bulk upconversion.

The GC6016 is a related product to the GC5330, with the DPD block not functional. The GC6016 has an identical package and footprint with the GC5330. The receive path includes wideband and narrowband automatic gain control (AGC), bulk downconversion, complex equalization, and I/Q imbalance correction.

The DDUC section consists of four identical DDUC blocks, each supporting up to 12 channels. Each channel has independent fractional resamplers and NCOs to enable flexible carrier configurations. Multi-mode/multi-standard operation can be supported by configuring the individual DDUC blocks to different filtering and oversampling scenarios.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **DESCRIPTION (Continued)**

The CFR block reduces the peak-to-average ratio (PAR) of the digital transmit signals, such as those used in third-generation (3G) code division multiple access (CDMA) and orthogonal frequency-division multiple-access (OFDMA) applications.

By reducing the PAR of the digital signal and the PA nonlinearity, the operational efficiency of follow-on power amplifiers can be substantially improved.

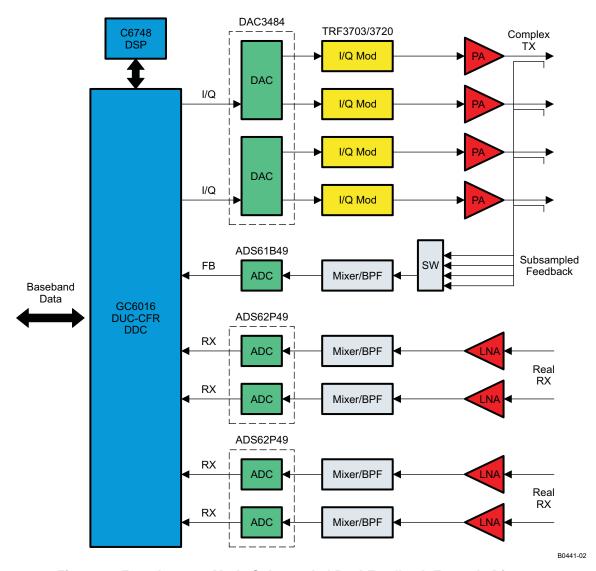

In Table 1, feedback is normally associated with a DPD system. The GC6016 can use the feedback input as a calibration antenna input to the capture buffer. Several architectures that provide performance and cost optimization are listed in Table 1

|          | ·          |                                            |                                                                   |  |  |  |  |  |  |

|----------|------------|--------------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|--|

| Figure   | TX Antenna | Other                                      |                                                                   |  |  |  |  |  |  |

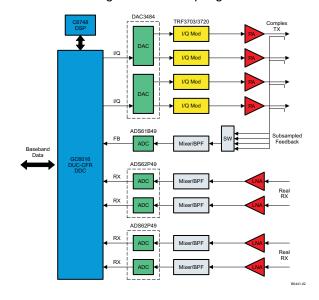

| Figure 1 | 2-62 MHz   | 2 typical at 250 Msps, up to 4 at 250 Msps | Lower-cost 2-antenna solution                                     |  |  |  |  |  |  |

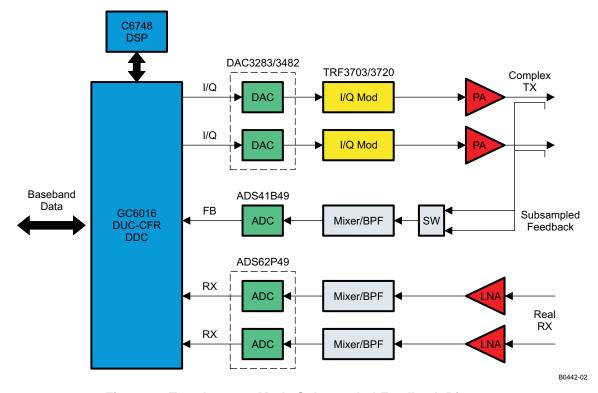

| Figure 2 | 2-62 MHz   | 2 at 250Msps, 4 with lower-rate RX ADC     | 2-antenna solution with full-rate real feedback                   |  |  |  |  |  |  |

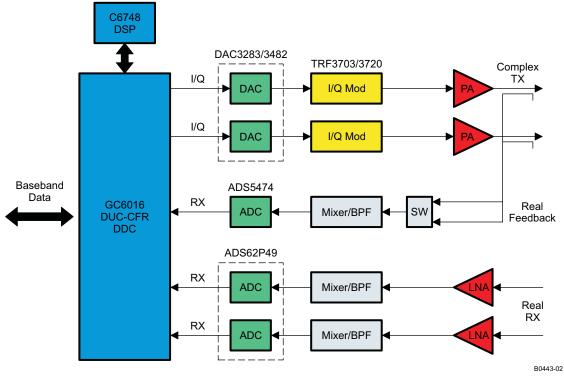

| Figure 3 | 2-62 MHz   | 2 at 250Msps, 4 with lower-rate RX ADC     | 2-antenna solution with complex feedback, lower subsampling ratio |  |  |  |  |  |  |

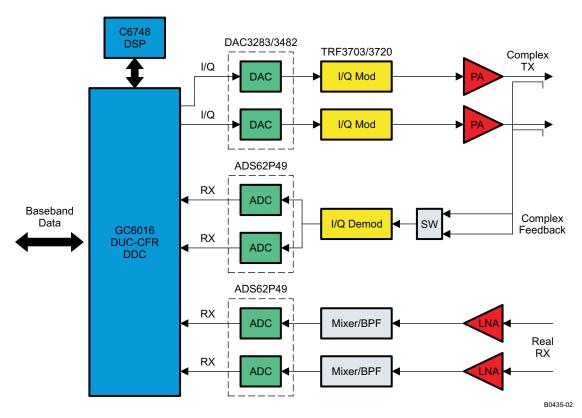

| Figure 4 | 4-31 MHz   | 4 at 250Msps, 8 with lower-rate RX ADC     | Lower-cost 4 antenna solution                                     |  |  |  |  |  |  |

Table 1. Sample Configurations for GC6016

#### ANTENNA MODE EXAMPLE DIAGRAMS

Figure 1. Two-Antenna-Mode Subsampled-Feedback Diagram

**INSTRUMENTS**

SLWS227A - NOVEMBER 2010 - REVISED MARCH 2011

Figure 2. Two-Antenna-Mode Full-Rate Real-Feedback Diagram

Figure 3. Two-Antenna-Mode Complex-Feedback Diagram

Figure 4. Four-Antenna-Mode Subsampled Real-Feedback Example Diagram

## **GENERAL DESCRIPTION**

processor GC6016 is а wideband transmit and receive signal that includes digital downconverter/upconverter (DDUC), transmit, receive, and capture buffer blocks. The transmit path includes crest factor reduction (CFR), complex equalization, and bulk upconversion. The receive path includes wideband and narrowband automatic gain control (AGC), bulk downconversion, complex equalization, and I/Q imbalance correction.

The architecture supports different RX, TX, and feedback modes of operation. This provides for many configurations to optimize performance and cost.

- RX real or complex input

- TX real, complex, complex with envelope tracking

The RX path can be configured for one or two multichannel ADC input ports. The RX block provides each ADC channel with a front-end AGC, IQ demodulation correction, real-to-complex conversion, complex mixing, decimation, and complex equalization. The RX block output is input to the DDUC block. The output of the DDUC block goes through gain and back-end AGC and is formatted for the baseband output.

INSTRUMENTS

There are four DDUC blocks. Each can be used for the RX DDC downconversion or TX DUC upconversion, one at a time. The DDUC has a complex mixer, cascade integrator comb filter, resampler, and a programmable FIR filter. Each DDUC can support 1 to 12 channels.

The TX path can be configured for one, two, or four antenna streams. In addition, with one or two antenna streams, an envelope modulator output is available. The DAC and envelope modulator share the same output ports. The TX input is from the baseband input, through the DDUC to create complex antenna streams. The CFR block provides for gain adjustment, peak reduction, and peak limiting. Additional interpolation stages after CFR expand the antenna stream bandwidth.

Specialized capture logic collects the RX input, feedback input, RX output, CFR output, and DPD output for the DSP processor to support built-in test. The capture logic can also be used for performance monitoring and power measurement.

#### **AVAILABLE OPTIONS**

| PART NUMBER | T <sub>C</sub> | PACKAGE                     | THERMAL PROPERTIES                |  |  |

|-------------|----------------|-----------------------------|-----------------------------------|--|--|

| GC6016IZEV  | –40°C to 85°C  | 484 ball 23-mm × 23-mm PBGA | Heat transfer through package top |  |  |

B0445-02

NOTE: UC1 and UC2 are for CFR interpolation; UC2 can only be used if UC1 is also used.

Figure 5. GC6016 Block Diagram

#### GC6016 Introduction

The GC6016 is a flexible transmit and receive digital signal processor that includes receiver and transmitter blocks, digital downconverter / upconverter (DDUC) blocks, crest factor reduction (CFR) engine, flexible LVDS data converter and baseband interfaces, and capture buffers for adaptive filtering algorithms.

Each of the four DDUC blocks can be configured as either a digital downconverter (DDC) or a digital upconverter (DUC). Typically, a system can be implemented as both TX and RX, with both DDC and DUC functions. The DDUC blocks provide programmable FIR filters with flexible numbers of taps, depending on signal bandwidth and number of channels, as well as fractional resamplers, CIC filters, and complex mixers. The DDUC complex mixers support static or hopping tuning functions.

www.ti.com

beAGC after the DDC is part of the baseband interface. Static gain is applied in the BB block for both the DDC output and DUC input.

The receiver block provides dc offset correction, front-end AGC, real-to-complex conversion, complex mixing, decimating filters, a complex equalizer, and a blind RX IQ imbalance correction function.

The CFR block reduces the peak-to-average ratio (PAR) of complex, arbitrary TX signals. Reducing the PAR of the TX signal allows wireless-infrastructure (WI) base stations and repeaters to use smaller and lower-cost multi-carrier power amplifiers (MCPAs).

In WI applications, the GC6016 meets multi-carrier 3G and 4G performance standards (PCDE, composite EVM, and ACLR) at PAR levels down to 6 dB for WCDMA and 7 dB for LTE. The GC6016 integrates easily into the transmit/receive signal chain between Texas Instruments' high-performance data converters and baseband processors such as the TI TMS320C64xx family. In wireless repeater applications, the GC6016 can provide seamless interfaces to TI data converters, along with receive and transmit filtering, DDC, and DUC functions.

The GC6016 is extremely flexible and can be used in system architectures with different signal types and TX-by-RX antenna configurations such as 2×2, 2×4, 4×4, and 4×8.

The GC6016 EVM system provides an example sector transmit-receive signal chain solution, from the multi-carrier baseband to the RF antenna.

#### **ABSOLUTE MAXIMUM RATINGS**

over recommended operating free-air temperature range (unless otherwise noted)(1)

|                    |                            |                                                                  | MIN  | MAX  | UNIT |

|--------------------|----------------------------|------------------------------------------------------------------|------|------|------|

| $V_{DD}$           | Core supply voltage        |                                                                  | -0.3 | 1.32 | V    |

| $V_{DDA}$          | PLL analog voltage         |                                                                  | -0.3 | 2    | V    |

| $V_{DDS}$          | Digital supply voltage for | TX                                                               | -0.3 | 2    | V    |

| $V_{\text{DDSHV}}$ | Digital supply voltage     |                                                                  | -0.3 | 3.6  | V    |

| $V_{IN}$           | Input voltage (under/ove   | Input voltage (under/overshoot)                                  |      |      |      |

|                    | Clamp current for an inp   | ut/output                                                        | -20  | 20   | mA   |

| T <sub>stg</sub>   | Storage temperature        |                                                                  | -65  | 140  | °C   |

|                    | ESD classification         | Class 2 (2.5 kV HBM, 500 V CDM, 150 V MM)                        |      |      |      |

|                    | Moisture sensitivity       | Moisture sensitivity Class 3 (1 week floor life at 30°C / 60% H) |      |      |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

SLWS227A - NOVEMBER 2010 - REVISED MARCH 2011

#### RECOMMENDED OPERATING CONDITIONS

|                |                                     |                                  | MIN  | TYP | MAX  | TINU |

|----------------|-------------------------------------|----------------------------------|------|-----|------|------|

| $V_{DD}$       | Core supply voltage                 | 310 MHz, 5.7 A max. (1)(2)(3)    | 1.05 | 1.1 | 1.15 | ٧    |

| $V_{DDA}$      | Analog supply for PLLs              | 60 mA max. (each) <sup>(1)</sup> | 1.71 | 1.8 | 1.89 | ٧    |

| $V_{DDS}$      | Digital supply voltage for LVDS I/O | 700 mA max. (1)                  | 1.71 | 1.8 | 1.89 | V    |

| $V_{DDSHV}$    | Digital supply voltage CMOS I/O     | PC board design dependent        | 3.15 | 3.3 | 3.45 | V    |

| T <sub>C</sub> | Case temperature                    |                                  | -40  | 30  | 90   | °C   |

| TJ             | Junction temperature                | See (4)                          |      |     | 105  | °C   |

- (1) Chip specifications are production tested to 90°C case temperature. QA tests are performed at 85°C.

- (2) Production tested hot using checksum at 310 MHz and maximum supplies. Power scales linearly with frequency with a dc consumption around 350 mA typical, 700 mA worst case.

- (3) Power consumption is a strong function of the configuration. A calculator is available to estimate power for a specific configuration.

- (4) Reliability calculations presume junction temperature 105°C or below. Operation above 105°C junction temperature reduces product lifetime.

#### THERMAL INFORMATION

|                  |                                                          | GC6016   |      |

|------------------|----------------------------------------------------------|----------|------|

|                  | THERMAL METRIC                                           | ZEV      | UNIT |

|                  |                                                          | 484 PINS |      |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance <sup>(1)</sup>    | 15.4     | °C/W |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance <sup>(2)</sup> | 2.1      | °C/W |

| $\theta_{JB}$    | Junction-to-board thermal resistance (3)                 | 7.6      | °C/W |

| ΨЈТ              | Junction-to-top characterization parameter (4)           | 0.5      | °C/W |

| ΨЈВ              | Junction-to-board characterization parameter (5)         | 7.5      | °C/W |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance (6)         | N/A      | °C/W |

- (1) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (2) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (3) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (4) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (5) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

Pin Assignment and Descriptions (Top View)

#### www.ti.com

#### 15 NC BRIN5P BRIN4P BRIN3P BRIN1P SPIDENB SPICI K CEB LIPA5 LIPA2 LIPD15 LIPD12 LIPD8 LIPD5 UPD1 VSSA2 SYNCRN TXA1N TXA2P NC BBIN7N BBIN7P BBIN5N BBIN4N BBIN3N BBIN1N SPIDIO INTERRP UPA6 UPA3 WEB UPD13 UPD9 UPD6 UPD2 VDDA2 SYNCBF TXA0N TXA1P TXA2N TXA5N BBIN8P BBIN6P BBIN6N VSSA1 BBIN2P BBIN0P EMIFENA UPA7 UPA4 UPD14 UPD10 UPD7 UPD3 SYNCAPOPDCLKP TXA0P BBIN8N UPA0 TXA3P TXA4P TXA4N TXA5F NC BBIN9N BBIN9P VDDA1 BBIN2N BBIN0N OEB UPA1 VSS UPD11 UPD4 SYNCA DPDCLKN TXA3N TXA6N TXA7N TXA8N TXA9F D BBIN10N BBIN11P BBIN11N NC TXA7P TXA8P TXA9N BBOUT1N BBOUT1P VDDS2 VDDSHV /DDSHV VDDSHV VDDSHV VDDS. TXA10N TXA10P BBOUTON BBOUT2N BBOUT2P NC NC TXA11N TXA11P BBOUT4N BBOUT4P BBOUT3N ввоитзр VDDS2 VSS TXA13N TXA12P TXA12N G VSS VSS VSS TXA17P TXA17N BBOUT8N BBOUT8P BBOUT7N BBOUT7P VSS VSS VSS VSS VSS VSS VSS VSS VSS TXA16N TXA16P BOUT10N BBOUT10F BBOUT9N BBOUT9P VDDS2 VSS VDDS1 TXA19N TXA19P TXA18N TXA18P ĸ RXA14P BBOUT11P BBOUT11 TXB1N RXA13N RXA12P RXA11N RXA11P VDDS2 VSS VDDS1 TXB3F TXB3N TXB2P TXB2N RXA12N RXA10P RXA9N RXA9P VSS TXB5P TXB5N TXB4P TXB4N RXA8P TXB6N RXA5N RXA5P vss VDDS1 TXB8N RXA6P TXB9F TXB9N TXB8P RXA6N RXA4N RXA3N RXA3P RXA2N RXA2P VSS VSS VSS VSS VSS VSS VSS VSS VSS TXB11F TXB11N TXB10P TXB10N VDDS2 TXB12P TXB12N RXA0N NC VDD RXB14N RXB10N RXB10P NC NC VDD NC NC TXB15F TXB15N TXB14N TXB14P RXA1N RXB14P RXB13P RXB6P RXB6N RXB4F RXB2P VSS VSS DVGA6 TDO TMS RXC6N RXC4N NC TXB17P TXB17N TXB16P TXB16N RXB13N RXB12N RXB8N RXB8P RXB4N VDDMON RESETB DVGA13 DVGA10 DVGA7 DVGA3 RXC5N RXC4P TXB19P TXB18N TXB18P RXB1N VSSMON DVGA14 DVGA11 DVGA8 TRSTB RXC7N RXC2P RXB12P RXB11P RXB9P RXB7N RXB5N RXB3P DVGA4 DVGA1 RXC5P RXC3P RXC2N RXC0N NC RXB0N TESTMOD DVGA15 DVGA12 DVGA9 NC RXB11N RXB9N RXB7P NC RXB3N RXB1P RXB0P DVGA5 DVGA2 TCK RXC7P RXC3N RXC1N RXC1P RXC0P NC ΑB 12 = 1.8 V, 3.3 V = 1.1 V= GND

Figure 6. GC6016 Pinout (Top View)

Submit Documentation Feedback

Copyright © 2010–2011, Texas Instruments Incorporated

P0131-01

8

SLWS227A - NOVEMBER 2010 - REVISED MARCH 2011

## **Pin Functions**

| NAME          | NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TYPE | DESCRIPTION                                   |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------|

| POWER AND BI  | ASING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                                               |

| VDD           | E6, E7, E8, E9, E10, E11, E12, E13, E14, E15, E16, F9, F11, F13, F15, F18, G18, H5, J5, J18, L18, N5, N18, P18, R5, T18, U5, U8, U10, U12, U14, U15, U18, V7, V8, V9, V10, V11, V12, V13, V14, V15, V16                                                                                                                                                                                                                                                                                                                                                                                                       | PWR  | 1.1-V power supply                            |

| VDDSHV2       | U9, U11, U13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PWR  | 3.3-V power supply for CMOS I/O               |

| VDDSHV1       | F8, F10, F12, F14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PWR  | 3.3-V power supply for CMOS I/O               |

| VDDS1         | F16, H18, K18, M18, R18, U16,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PWR  | 1.8-V power supply for LVDS I/O               |

| VDDS2         | F7, G5, K5, M5, U7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PWR  | 1.8-V power supply for LVDS I/O               |

| VPP           | W8, W10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PWR  | 1.1-V E-fuse supply, connect to VDD           |

| VDDMON        | Y8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NC   | Do not connect, internal monitor point        |

| VSSMON        | AA8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NC   | Do not connect, internal monitor point        |

| VDDA2         | B17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PWR  | 1.8-V power for PLL (requires filtering)      |

| VDDA1         | D5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PWR  | 1.8-V power for PLL (requires filtering)      |

| VSSA2         | A16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PWR  | Ground for PLL (requires filtering)           |

| VSSA1         | C5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PWR  | Ground for PLL (requires filtering)           |

| VSS           | D8, D10, D12, D14, G6, G7. G8, G9, G10, G11, G12, G13, G14, G15, G16, G17, H6, H7, H8, H9, H10, H11, H12, H13, H14, H15, H16, H17, J6, J7, J8, J9,J10, J11, J12, J13, J14, J15, J16, J17, K6, K7, K8, K9, K10, K11, K12, K13, K14, K15, K16, K17, L6, L7, L8, L9, L10, L11, L12, L13, L14, L15, L16, L17, M6, M7, M8, M9, M10, M11, M12, M13, M14, M15, M16, M17, N6, N7, N8, N9, N10, N11, N12, N13, N14, N15, N16, N17, P6, P7, P8, P9, P10, P11, P12, P13, P14, P15, P16, P17, R6, R7, R8, R9, R10, R11, R12, R13, R14, R15, R16, R17, T6, T7, T8, T9, T10, T11, T12, T13, T14, T15, T16, T17,W9, W11, W13 | PWR  | Ground                                        |

| NC            | E17, E18, F6, F17, U6, U17, V5, V6, V17, V18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | NC   | No connection. Recommend connecting to ground |

| NC            | A1, A22, D1, D4, W3, W18, AA22, AB1, AB5, AB22,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | NC   | No connection                                 |

| BASEBAND INP  | UT/OUTPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                               |

| BBIN[11:0]P   | E4, E2, D3, C2, B2, C3, A2, A3, A4, C6, A5, C7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I    | Baseband input – LVDS positive                |

| BBIN[11:0]N   | E5, E3, D2, C1, B1, C4, B3, B4, B5, D6, B6, D7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I    | Baseband input – LVDS negative                |

| BBOUT[11:0]P  | L4, K2, K4, J2, J4, H2, H4, G2, G4, F3, F5, E1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0    | Baseband output – LVDS positive               |

| BBOUT[11:0]N  | L5, K1, K3, J1, J3, H1, H3, G1, G3, F2, F4, F1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0    | Baseband output – LVDS negative               |

| TX DAC INTERF | ACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                               |

| TXA[19:0]P    | K20, K22, J19, J22, H19, H22, G19, G21, F20, F22, D22, E21, E20, E19, C22, C20, C19, A21, B20, C18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0    | DAC TX port A – LVDS positive                 |

| TXA[19:0]N    | K19, K21, J20, J21, H20, H21, G20, G22, F19, F21, E22, D21, D20, D19, B22, C21, D18, B21, A20, B19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0    | DAC TX port A – LVDS negative                 |

| TXB[19:0]P    | Y20, Y22, W19, W21, V19, V22, U19, U21, T19, T21, R19, R21, P19, P21, N19, N21, M19, M21, L19, L21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0    | DAC TX port B – LVDS positive                 |

| TXB[19:0]N    | Y19, Y21, W20, W22, V20, V21, U20, U22, T20, T22, R20, R22, P20, P22, N20, N22, M20, M22, L20, L22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0    | DAC TX port B – LVDS negative                 |

| RX and FB ADC | INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                               |

| RXA[14:0]P    | L3, L1, M2, M4, N2, N4, P3, P5, R2, R4, U1, T3, T5, U2, U4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I    | ADC receive port A – LVDS positive            |

| RXA[14:0]N    | L2, M1, N1, M3, P1, N3, P2, P4, R1, R3, T1, T2, T4, V1, U3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I    | ADC receive port A – LVDS negative            |

| RXB[14:0]P    | W1, W2, AA1, AA2, V4, AA3, Y4, AB4, W4, Y5, W6, AA6, W7, AB7, AB8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I    | ADC receive port B – LVDS positive            |

| RXB[14:0]N    | V2, Y1, Y2, AB2, V3, AB3, Y3, AA4, W5, AA5, Y6, AB6, Y7, AA7, AB9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I    | ADC receive port B – LVDS negative            |

| RXC[7:0]P     | AB17, Y16, AA17, Y18, AA18, AA20, AB20, AB21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I    | ADC receive port C – LVDS positive            |

| RXC[7:0]N     | AA16, W16, Y17, W17, AB18, AA19, AB19, AA21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I    | ADC receive port C – LVDS negative            |

## Pin Functions (continued)

| NAME          | NUMBER                                                                                   | TYPE | DESCRIPTION                                                                                                                                                                                                                              |

|---------------|------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DVGA INTERFA  | CE                                                                                       | 1    | ,                                                                                                                                                                                                                                        |

| DVGA[15:0]    | AB11, AA10, Y10, AB12, AA11, Y11, AB13, AA12, Y12, W12, AB14, AA13, Y13, AB15, AA14, Y14 | 0    |                                                                                                                                                                                                                                          |

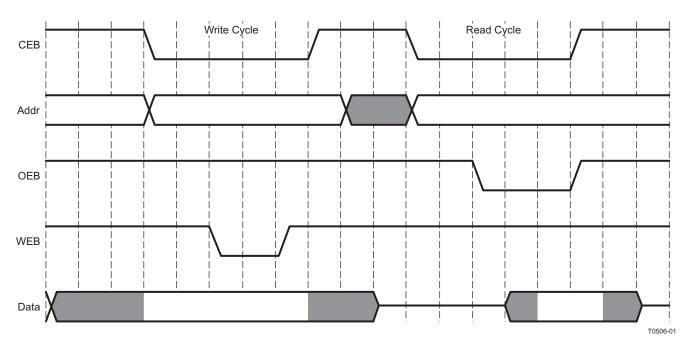

| MPU INTERFAC  | E                                                                                        |      |                                                                                                                                                                                                                                          |

| UPD[15:0]     | A11, C12, B12, A12, D13, C13, B13, A13, C14, B14, A14, D15, C15, B15, A15, B16           | I/O  |                                                                                                                                                                                                                                          |

| UPA[7:0]      | C9, B9, A9, C10, B10, A10, D11, C11                                                      | 1    |                                                                                                                                                                                                                                          |

| WEB           | B11                                                                                      | 1    | Write enable, active-low                                                                                                                                                                                                                 |

| EMIFENA       | C8                                                                                       | 1    | EMIFENA switches between address/data μP access and SPI access. Its value may be changed at any time, but both address/data access and SPI access must be idle during the change. Logic 1 = EMIF, logic 0 = SPI pin has internal pullup. |

| OEB           | D9                                                                                       | I    | Read and output enable, active-low                                                                                                                                                                                                       |

| CEB           | A8                                                                                       | I    | Chip enable, active-low                                                                                                                                                                                                                  |

| JTAG INTERFA  | CE                                                                                       |      |                                                                                                                                                                                                                                          |

| TRSTB         | AA15                                                                                     | I    | JTAG reset (active-low); pull down if JTAG is not used.                                                                                                                                                                                  |

| TMS           | W15                                                                                      | I    | JTAG mode select                                                                                                                                                                                                                         |

| TDO           | W14                                                                                      | 0    | JTAG data out                                                                                                                                                                                                                            |

| TDI           | Y15                                                                                      | I    | JTAG data in                                                                                                                                                                                                                             |

| TCK           | AB16                                                                                     | I    | JTAG clock                                                                                                                                                                                                                               |

| SPI INTERFACE |                                                                                          |      |                                                                                                                                                                                                                                          |

| SPIDENB       | A6                                                                                       | 1    | Serial interface enable                                                                                                                                                                                                                  |

| SPICLK        | A7                                                                                       | 1    | Serial interface clock                                                                                                                                                                                                                   |

| SPIDIO        | B7                                                                                       | I/O  | Serial interface data                                                                                                                                                                                                                    |

| SPIDO(SPARE)  | AA9                                                                                      | 0    | Serial interface data out in four-wire SPI mode                                                                                                                                                                                          |

| MISCELLANEO   | JS                                                                                       |      |                                                                                                                                                                                                                                          |

| TESTMOD       | AB10                                                                                     | I    | Test mode for GC6016, typically grounded                                                                                                                                                                                                 |

| RESETB        | Y9                                                                                       | I    | Chip reset – required – active-low                                                                                                                                                                                                       |

| INTERRPT      | B8                                                                                       | 0    | Output interrupt                                                                                                                                                                                                                         |

| DPDCLKP       | C17                                                                                      | I    | DPD CLK input – LVDS positive                                                                                                                                                                                                            |

| DPDCLKN       | D17                                                                                      | 1    | DPD CLK input – LVDS negative                                                                                                                                                                                                            |

| SYNCOUTP      | A19                                                                                      | 0    | Sync output – LVDS positive                                                                                                                                                                                                              |

| SYNCOUTN      | A18                                                                                      | 0    | Sync output – LVDS negative                                                                                                                                                                                                              |

| SYNCAP        | C16                                                                                      | I    | Sync input A – LVDS positive                                                                                                                                                                                                             |

| SYNCAN        | D16                                                                                      | I    | Sync input A – LVDS negative                                                                                                                                                                                                             |

| SYNCBP        | B18                                                                                      | 1    | Sync input B – LVDS positive                                                                                                                                                                                                             |

| SYNCBN        | A17                                                                                      | I    | Sync input B – LVDS negative                                                                                                                                                                                                             |

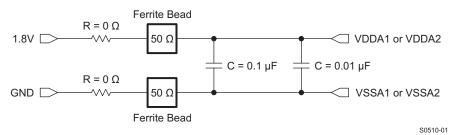

NOTE:  $0-\Omega$  R0603 resistor is used to accommodate series resistor if needed.

Figure 7. GC6016 PLL Filtering

The two GC6016 PLLs require a filtered power supply. The supply can be generated by filtering the digital supply (VDDS1, VSSA1, VDDS2, and VSSA2). A representative filter is shown in Figure 7. The two PLLs should have separate filters that are located as close as is reasonable to their respective pins (especially the bypass capacitors). The ferrite beads should be series 50R (similar to Murata P/N: BLM31P500SPT, Description: IND FB BLM31P500SPT 50R 1206).

## **Sub-Chip Descriptions**

INSTRUMENTS

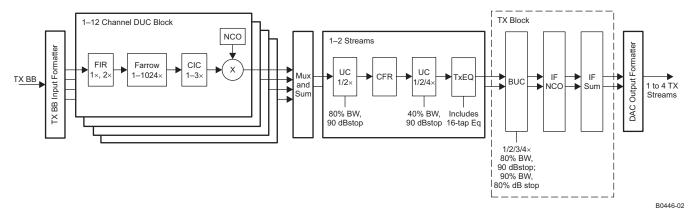

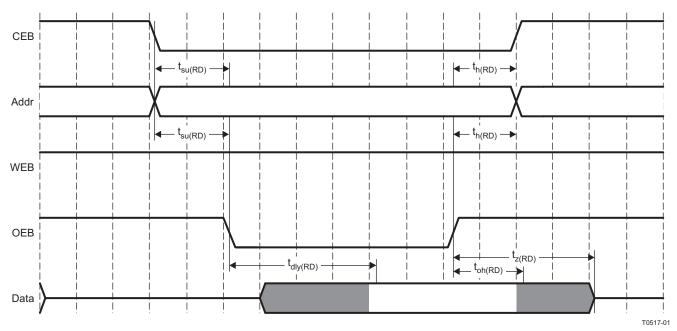

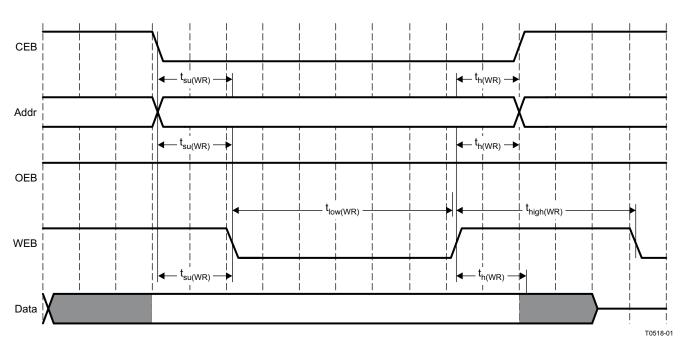

Figure 8 shows the TX functional block diagram, and Figure 9 shows the RX functional block diagram. Note that each figure shows up to four DUC or DDC blocks in the TX or RX paths, and there are a total of four DDUC blocks that may be configured as either DUC or DDC each.

Figure 8. TX Functional Block Diagram

Figure 9. RX Functional Block Diagram

#### TX Baseband Input Formatter

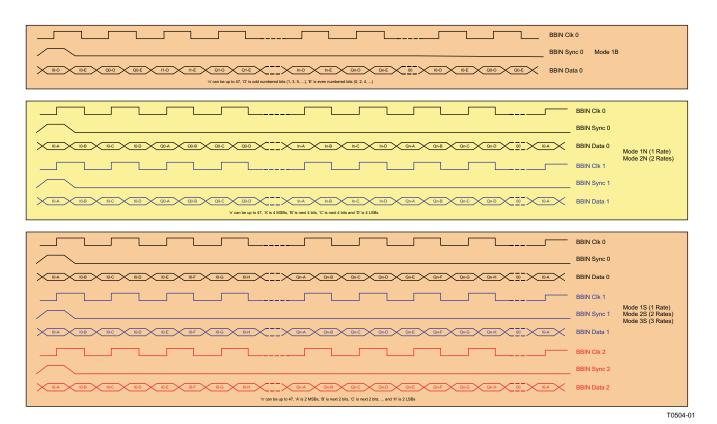

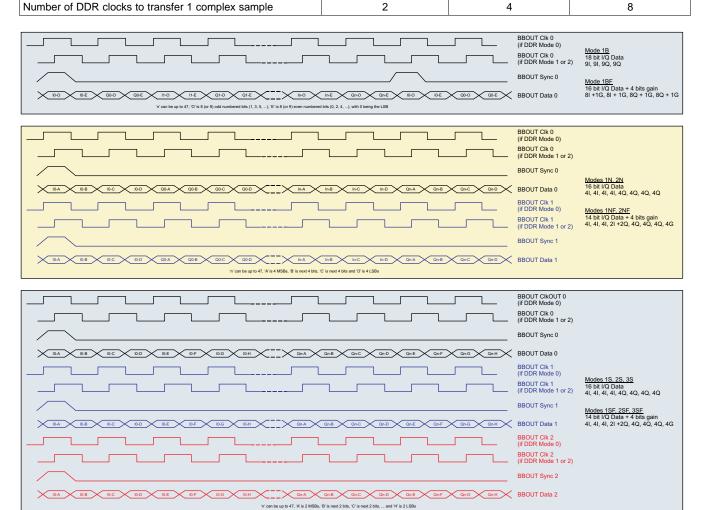

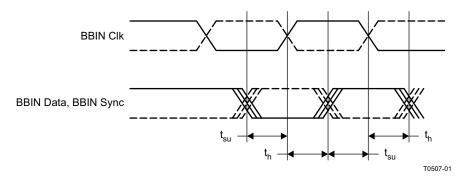

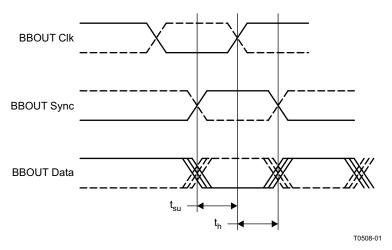

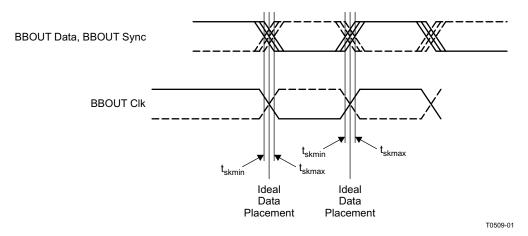

The TX baseband (BB) input-formatter block accepts TX baseband inputs from the FPGA or baseband processor and formats them for the DUC blocks. There are 12 unidirectional LVDS pairs for the TX input formatter, and their function depends on the operational mode. There are three operational modes for the TX BB input formatter: byte mode (B, 8 or 9 bits), nibble mode (N, 4 bits), and serial mode (S, 2 bits) to allow multiple BB input rates. The GC6016 can accept up to three different BB input data rates. Table 2 and Table 3 summarize each mode and the pin assignments. In Table 3, BBIN[X] is the BBIN differential pair (assumed positive and negative connections), and BB0, BB1, and BB2 represent three different TX baseband ports at arbitrary rates.

#### **Table 2. TX BB Formatter Modes**

| MODE   | DESCRIPTION                                                                       | Total Number of Interface Pins                                                       | Maximum Complex Interface Rate per Channel N is the number of channels.                                  |

|--------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 1B     | Byte mode, 1 interface rate                                                       | 10 or 11 = 8 or 9 data + 1 clk + 1 sync                                              | (Clk × 4/4)/N; maximum 192.31 MSPS total (for all channels)                                              |

| 1N     | Nibble mode, 1 interface rate                                                     | 6 = 4 data + 1 clk + 1 sync                                                          | (Clk × 4/8)/N; maximum 125 (Nibble 0), 96.15 (Nibble 1) MSPS total                                       |

| 1S     | Serial mode, 1 interface rate                                                     | 4 = 2 data + 1 clk + 1 sync                                                          | (Clk × 4/16)/N; maximum 48.07 MSPS total                                                                 |

| 2N     | Nibble mode, 2 interface rates                                                    | 12 = 4 data + 1 clk + 1 sync + 4<br>data + 1 clk + 1 sync                            | (Clk × 4/8)/N × 2; maximum 221.15 MSPS total                                                             |

| 2N'(1) | Nibble + byte mode, 2 interface rates, RX-ADC input pins used for byte-mode port. | 16 = 4 data + 1 clk + 1 sync + 8<br>data + 1 clk + 1 sync                            | Nibble port: (Clk × 4/8)/N; maximum 125 MSPS total Byte port: (Clk × 2/4)/N; maximum 125, 250 MSPS total |

| 2S     | Serial mode, 2 interface rates                                                    | 8 = 2 data + 1 clk + 1 sync + 2 data<br>+ 1 clk + 1 sync                             | (Clk × 4/16)/N; maximum 96.15 MSPS total                                                                 |

| 3S     | Serial mode, 3 interface rates                                                    | 12 = 2 data + 1 clk+1 sync + 2 data<br>+ 1 clk + 1 sync + 2 data + 1 clk + 1<br>sync | (Clk × 4/16)/N; maximum 144.23 MSPS total                                                                |

(1) 2N' is the only configuration that allows a special mode to re-use RX input port A as baseband TX inputs

## **Table 3. TX BB Pin Assignments**

| 3          |                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BYTE MODE  | NIBBLE MODE                                                                                                                                                      | SERIAL MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BB0_DATA_0 | BB0_DATA_0                                                                                                                                                       | BB0_DATA_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BB0_DATA_1 | BB0_DATA_1                                                                                                                                                       | BB0_DATA_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BB0_DATA_2 | BB0_SYNC                                                                                                                                                         | BB0_SYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Spare      | BB0_CLOCK                                                                                                                                                        | BB0_CLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BB0_DATA_3 | BB0_DATA_2                                                                                                                                                       | BB1_DATA_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BB0_DATA_4 | BB0_DATA_3                                                                                                                                                       | BB1_DATA_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BB0_SYNC   | BB1_SYNC                                                                                                                                                         | BB1_SYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BB0_CLOCK  | BB1_CLOCK                                                                                                                                                        | BB1_CLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BB0_DATA_5 | BB1_DATA_0                                                                                                                                                       | BB2_DATA_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BB0_DATA_6 | BB1_DATA_1                                                                                                                                                       | BB2_DATA_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BB0_DATA_7 | BB1_DATA_2                                                                                                                                                       | BB2_SYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BB0_DATA_8 | BB1_DATA_3                                                                                                                                                       | BB2_CLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1          | 2                                                                                                                                                                | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2          | 4                                                                                                                                                                | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            | BYTE MODE  BB0_DATA_0  BB0_DATA_1  BB0_DATA_2  Spare  BB0_DATA_3  BB0_DATA_4  BB0_SYNC  BB0_CLOCK  BB0_DATA_5  BB0_DATA_6  BB0_DATA_6  BB0_DATA_7  BB0_DATA_8  1 | BB0_DATA_0         BB0_DATA_0           BB0_DATA_1         BB0_DATA_1           BB0_DATA_2         BB0_SYNC           Spare         BB0_CLOCK           BB0_DATA_3         BB0_DATA_2           BB0_DATA_4         BB0_DATA_3           BB0_SYNC         BB1_SYNC           BB0_CLOCK         BB1_CLOCK           BB0_DATA_5         BB1_DATA_0           BB0_DATA_6         BB1_DATA_1           BB0_DATA_7         BB1_DATA_2           BB0_DATA_8         BB1_DATA_3           1         2 |

The actual data transfer rate in nibble mode is 2 times higher than the byte mode for the same total throughput. If two ports are required (e.g., to support two different sample rates), and a lower speed on the interface is desired, the GC6016 can re-use the RX ADC input port A as a baseband TX input bus. RX ADC port A has 15 pairs of LVDS input pins and supports one set of baseband input data in byte mode. When RX port A is used as a baseband TX input, it cannot be also used as an RX input port.

The baseband interface supports a full-clock or gated-clock format. These formats are shown in Figure 10

The mapping for the RX port A pins when in BB TX input mode is:

RXA14: clock

RXA13: sync

RXA12–5: BB0\_DATA7–0

Submit Documentation Feedback

Copyright © 2010–2011, Texas Instruments Incorporated

Figure 10. TX BB Formats

The TX formatter block includes a per-channel TX gain adjust via a 16-bit complex digital word which can be set to have gain between  $-\infty$  and 9 dB.

## **Digital Down- and Upconverters (DDUCs)**

The GC6016 has four identical and independent DDUC blocks that can be configured as either DDC or DUC. Each DDUC can support up to 12 channels with scalable bandwidth.

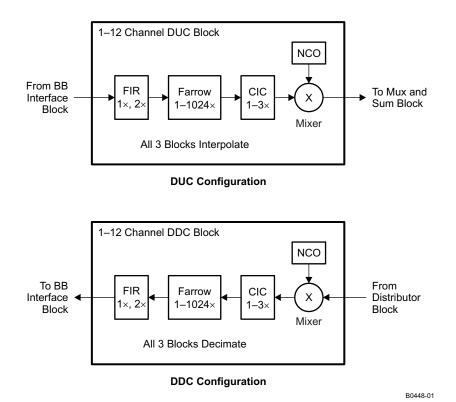

The only difference between the DUC and DDC configurations is the interpolate (DUC) versus decimate (DDC) functions and the data path direction as shown in Figure 11. Both DDC and DUC are described in this section. Note that each DDUC block must be configured statically as a DUC or DDC and cannot switch modes dynamically in TDD applications.

Figure 11. DUC and DDC Functional Block Diagram

In combination with the follow-on mux and sum block, the DUC block interpolates, filters, mixes each carrier, and combines multiple channels into one to four wideband, composite TX signal streams. Any input channel can be mapped to any TX stream in the mux and sum block.

The DDC configuration accepts an RX stream from the distributor block and provides mixing, decimation filtering, fractional resampling, and filtering to RX channels. The RX block outputs are mapped to the mixer CIC stream via the distributor block.

Each DDUC block contains a finite impulse response (FIR) filter, a fractional resampler (Farrow filter), a cascaded integrator-comb (CIC) filter, a complex mixer and NCO for channel placement in the composite stream, and a programmable frequency hopper (see Figure 11).

The number of taps available in the FIR filter depends on various parameters such as the BBclk rate (derived from DPDCLK), input sample rate, interpolate and decimate settings, and number of channels. Different tap values may be used for each channel (however, that reduces the number of filter taps available).

Note that the input sample rate is the input from the TX BB input formatter for the DUC configuration and the input from the distributor block for DDC configuration. The number of taps for various wireless standards and configurations is shown in Table 4.

The Farrow filter supports one real channel or 1–12 complex channels and can be configured for any resampling ratio from 1 to 1024 with 32-bit resolution. A different delay value for each channel is supported. The Farrow filter is used to resample different TX BB input sample rates to a common CFR rate, and it provides 95-dB rejection at  $\pm 0.25$  output  $f_S$  (sample rate), 83-dB rejection at  $\pm 0.375$  output  $f_S$ , and 56-dB rejection at  $\pm 0.4$  output  $f_S$ .

The CIC interpolates or decimates by a factor of 1, 2, or 3. If each DDUC must support more than eight carriers, the CIC must interpolate/decimate by 3. If each DDUC must support between four and eight carriers, the CIC can interpolate/decimate by 2 or 3. If each DDUC must support fewer than four carriers, the CIC can interpolate by 1, 2, or 3.

**NSTRUMENTS**

The NCO contains a 48-bit frequency word and 48-bit accumulator, and operates at the DUC output sample rate. The minimum resolution is the DUC output sample rate or DDC input sample rate divided by  $2^{48}$ , or about 0.2  $\mu$ Hz for a 61.44-MSPS DUC output rate. The mixer and NCO can be used for frequency planning or fine frequency control.

Per-channel phase can be adjusted in the mixer/NCO block with a 16-bit phase word, while per channel fractional delay can be adjusted in the Farrow block.

Table 4. Number of FIR Filter Taps for Example Signal Types

| Name             | BBclk  | Input<br>Sample<br>Rate | Filter Type      | DUC Mode<br>Interp. | DDC Mode<br>Decim. | No. of   | Max. Taps |

|------------------|--------|-------------------------|------------------|---------------------|--------------------|----------|-----------|

|                  | MHz    | MSPS                    | Sym or<br>Un-Sym | 1 or 2              | 1 or 2             | Channels | •         |

| Ite20_1          | 245.76 | 30.72                   | S                | 1                   | 1                  | 1        | 159       |

| Ite20_2          | 245.76 | 30.72                   | S                | 1                   | 1                  | 2        | 79        |

| Ite10_2          | 245.76 | 15.36                   | S                | 1                   | 1                  | 2        | 159       |

| Ite10_3          | 245.76 | 15.36                   | S                | 1                   | 1                  | 3        | 99        |

| Ite10_4          | 245.76 | 15.36                   | S                | 1                   | 1                  | 4        | 79        |

| Ite5_4           | 245.76 | 7.68                    | S                | 1                   | 1                  | 4        | 159       |

| Ite5_8           | 245.76 | 7.68                    | S                | 1                   | 1                  | 8        | 79        |

| wimax20_r3       | 246.4  | 44.8                    | S                | 1                   | 2                  | 3        | 59        |

| wimax20_t3       | 246.4  | 22.4                    | S                | 2                   | 1                  | 3        | 39        |

| wimax20_r2       | 246.4  | 44.8                    | S                | 1                   | 2                  | 2        | 99        |

| wimax20_t2       | 246.4  | 22.4                    | S                | 2                   | 1                  | 2        | 79        |

| wimax20_r1       | 246.4  | 44.8                    | S                | 1                   | 2                  | 1        | 219       |

| wimax20_t1       | 246.4  | 22.4                    | S                | 2                   | 1                  | 1        | 199       |

| wimax10_r2       | 246.4  | 22.4                    | S                | 1                   | 2                  | 2        | 219       |

| wimax10_t2       | 246.4  | 11.2                    | S                | 2                   | 1                  | 2        | 199       |

| wimax10_r3       | 246.4  | 22.4                    | S                | 1                   | 2                  | 3        | 139       |

| wimax10_t3       | 246.4  | 11.2                    | S                | 2                   | 1                  | 3        | 119       |

| wimax10_r4       | 246.4  | 22.4                    | S                | 1                   | 2                  | 4        | 99        |

| wimax10_t4       | 246.4  | 11.2                    | S                | 2                   | 1                  | 4        | 79        |

| wimax5_r4        | 246.4  | 11.2                    | S                | 1                   | 2                  | 4        | 219       |

| wimax5_t4        | 246.4  | 5.6                     | S                | 2                   | 1                  | 4        | 199       |

| wimax5_r8        | 246.4  | 11.2                    | S                | 1                   | 2                  | 8        | 99        |

| wimax5_t8        | 246.4  | 5.6                     | S                | 2                   | 1                  | 8        | 79        |

| wbcdma_r4        | 245.76 | 7.68                    | S                | 1                   | 1                  | 4        | 159       |

| wbcdma_t4        | 245.76 | 3.84                    | S                | 2                   | 1                  | 4        | 319       |

| wbcdma_r8        | 245.76 | 7.68                    | S                | 1                   | 1                  | 8        | 79        |

| wbcdma_t8        | 245.76 | 3.84                    | S                | 2                   | 1                  | 8        | 159       |

| cdma_r12         | 245.76 | 2.4576                  | S                | 1                   | 1                  | 12       | 99        |

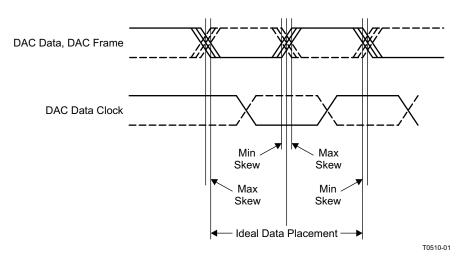

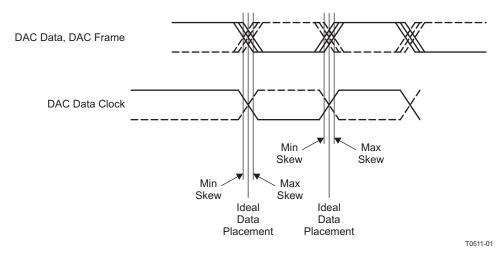

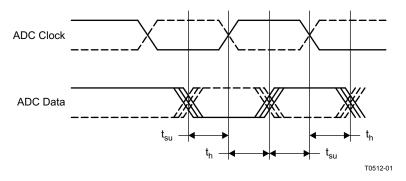

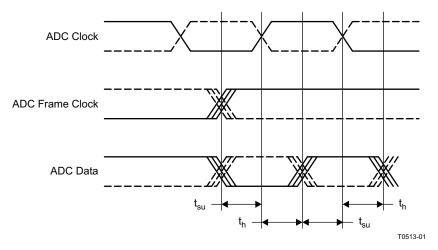

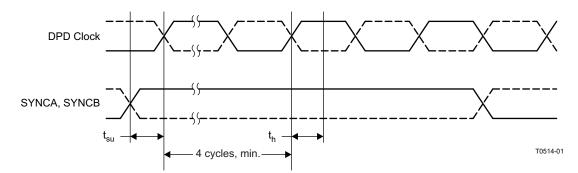

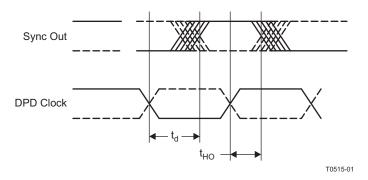

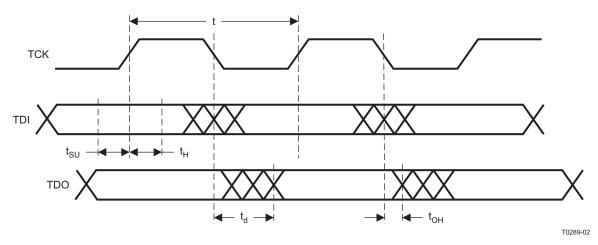

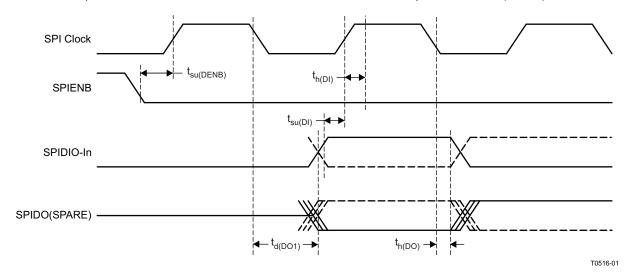

| cdma_t12         | 245.76 | 1.2288                  | U                | 2                   | 1                  | 12       | 100       |