# Fully Integrated, 8-Channel Voltage Controlled Amplifier for Ultrasound with Passive CW Mixer, 0.75 nV/rtHz, 99 mW/CH

Check for Samples: VCA5807

#### **FEATURES**

- 8-Channel Voltage Controlled Amplifier

- LNA, VCAT, PGA, LPF, and CW Mixer

- Programmable Low-Noise Amplifier (LNA)

- 24/18/12 dB Gain

- 0.25/0.5/1 V<sub>PP</sub> Linear Input Range

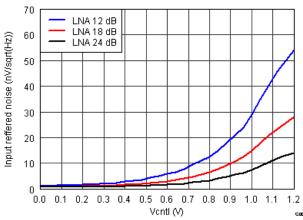

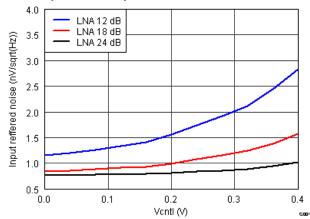

- 0.63/0.7/0.9 nV/rtHz Input Referred Noise

- Programmable Active Termination

- 40 dB Low Noise Voltage Controlled Attenuator (VCAT)

- 24/30 dB Programmable Gain Amplifier (PGA)

- 3<sup>rd</sup> Order Linear Phase Low-Pass Filter (LPF)

- 10, 15, 20, 30 MHz

- Butterworth Characteristics

- Noise/Power Optimizations (Full Chain)

- 99 mW/CH at 0.75 nV/rtHz

- 56 mW/CH at 1.1 nV/rtHz

- 80 mW/CH at CW Mode

- Excellent Device-to-Device Gain Matching

- ±0.5 dB (typical) and ±1.05 dB (max)

- Low Harmonic Distortion

- Fast and Consistent Overload Recovery

- Low Frequency Sonar Signal Processing

- Passive Mixer for Continuous Wave Doppler (CWD)

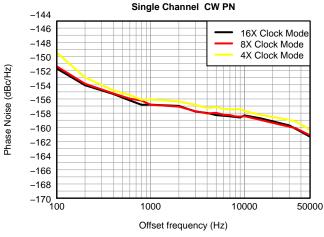

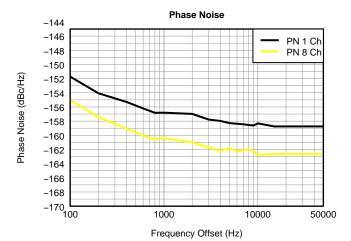

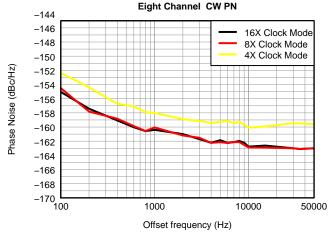

- Low Close-in Phase Noise –156 dBc/Hz at 1 KHz off 2.5 MHz Carrier

- Phase Resolution of 1/16λ

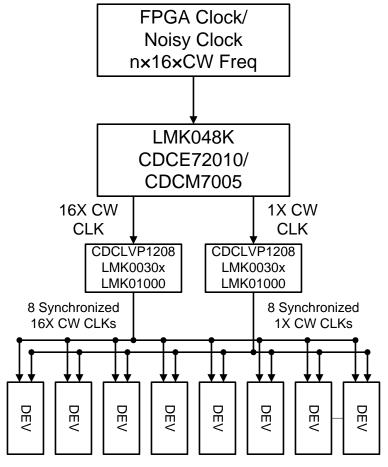

- Support 32X,16X, 8X, 4X and 1X CW Clocks

- 12dB Suppression on 3<sup>rd</sup> and 5<sup>th</sup> Harmonics

- Flexible Input Clocks

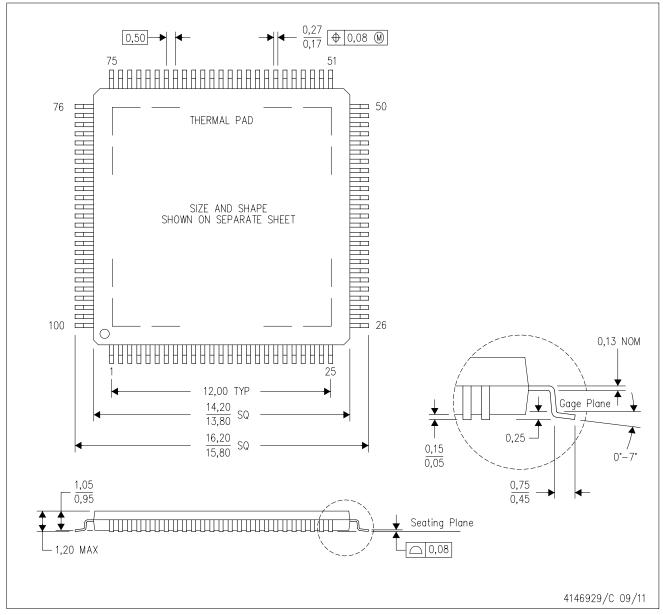

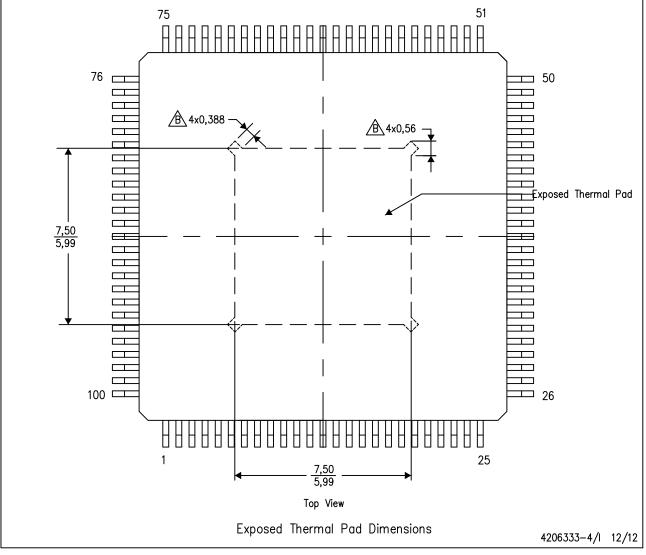

- 14mm x 14mm, 100-pin TQFP

#### **APPLICATIONS**

- Medical Ultrasound Imaging

- Nondestructive Evaluation Equipments

- Sonar Imaging

#### DESCRIPTION

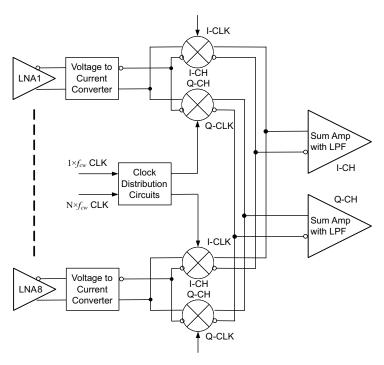

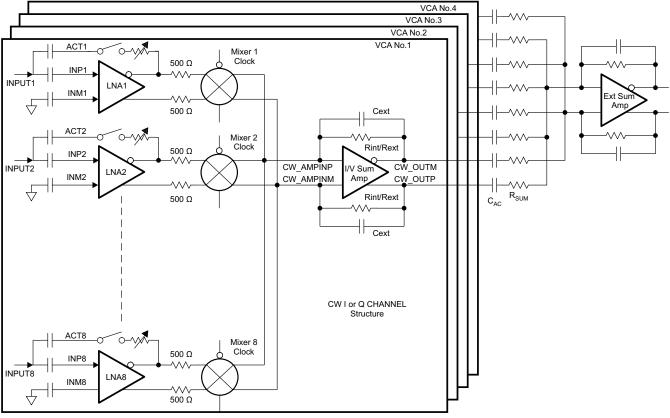

The VCA5807 is an integrated Voltage Controlled Amplifier (VCA) specifically designed for ultrasound systems in which high performance and small size are required. The VCA5807 integrates a complete time-gain-control (TGC) imaging path and a continuous wave Doppler (CWD) path. It also enables users to select one of various power/noise combinations to optimize system performance. Therefore, the VCA5807 is a suitable ultrasound analog front end solution not only for high-end systems, but also for portable systems.

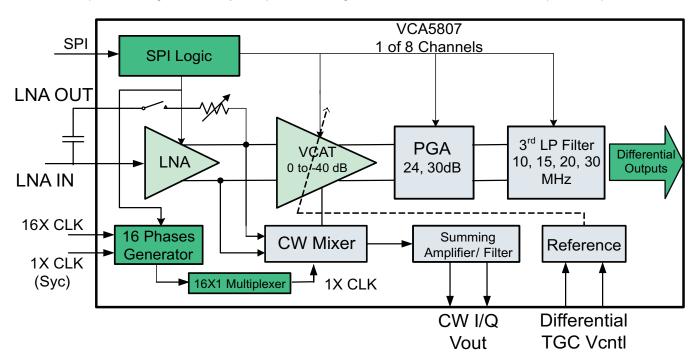

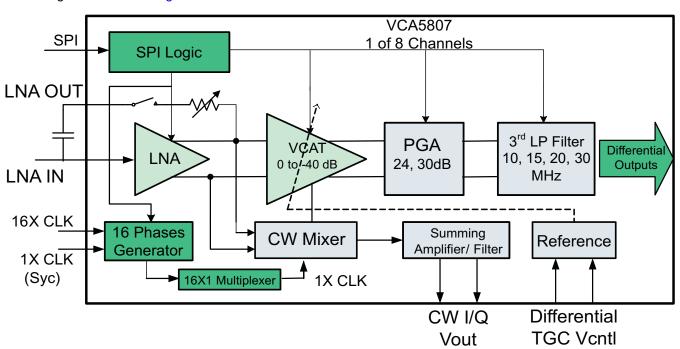

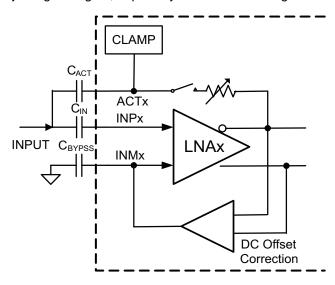

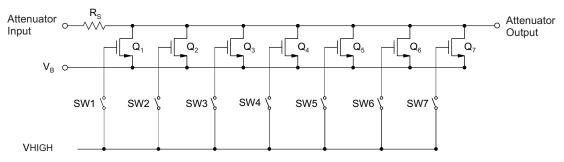

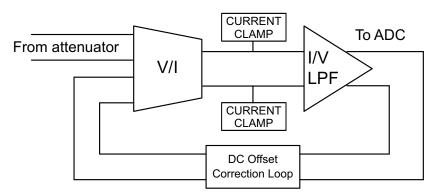

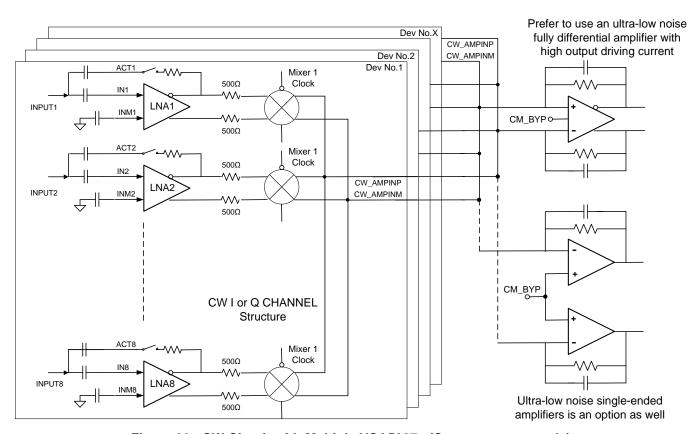

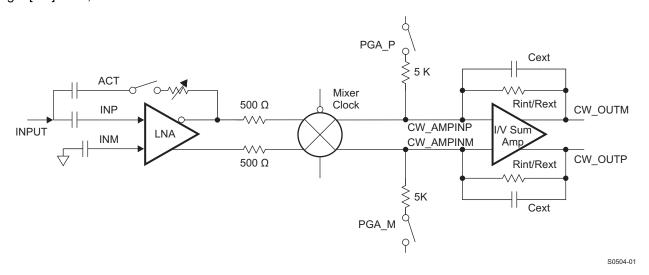

The VCA5807 contains eight channels of voltage controlled amplifier (VCA), and CW mixer. The VCA includes Low noise Amplifier(LNA), Voltage controlled Attenuator (VCAT), Programmable Gain Amplifier (PGA), and Low-Pass Filter (LPF). The LNA gain is programmable to support 250 mV<sub>PP</sub> to 1 V<sub>PP</sub> input signals. Programmable active termination is also supported by the LNA. The ultra-low noise VCAT provides an attenuation control range of 40dB and improves overall low gain SNR which benefits harmonic imaging and near field imaging. The PGA provides gain options of 24 dB and 30 dB. Before the ADC, a LPF can be configured as 10 MHz, 15 MHz, 20 MHz, or 30 MHz to support ultrasound applications with different frequencies. In addition, the signal chain of the VCA5807 can handle signal frequency lower than 100 KHz, which enables it to be used not only in ultrasound applications but also in sonar applications.

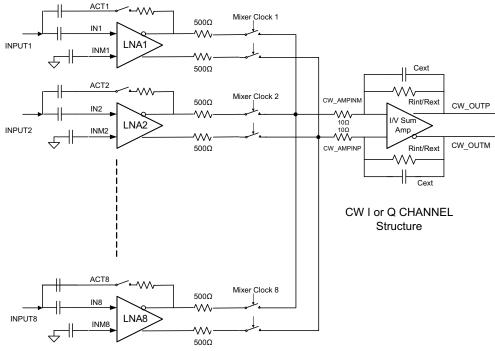

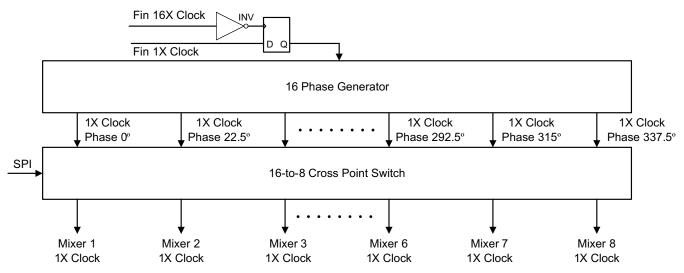

The VCA5807 integrates a low power passive mixer and a low noise summing amplifier to accomplish on-chip CWD beamformer. 16 selectable phase-delays can be applied to each analog input signal. Meanwhile a unique 3<sup>rd</sup> and 5<sup>th</sup> order harmonic suppression filter is implemented to enhance CW sensitivity.

The VCA5807 is available in a 14mm x 14mm, 100-pin TQFP package and it is specified for operation from -40°C to 85°C.

SLOS727 - DECEMBER 2012 www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

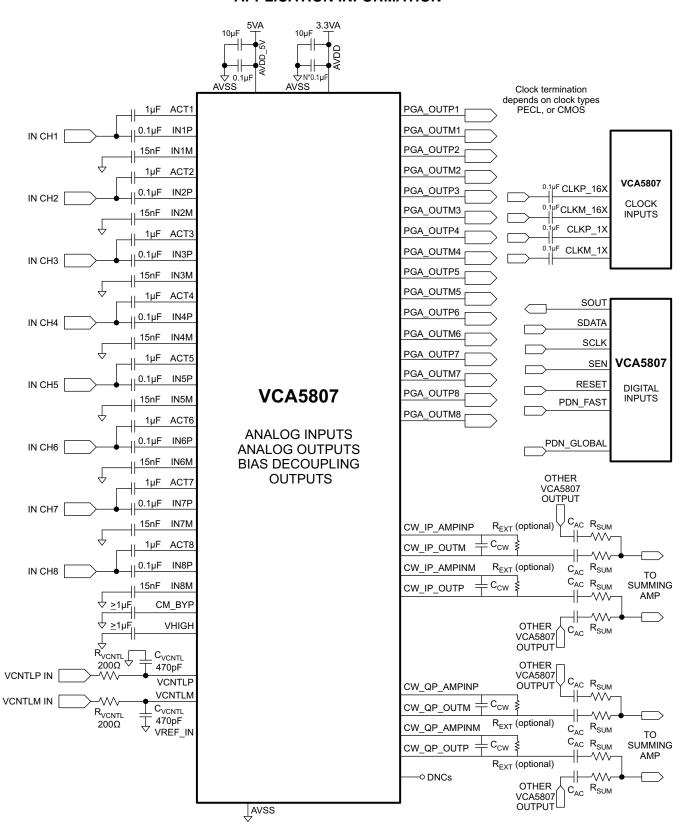

Figure 1. Block Diagram

#### PACKAGING/ORDERING INFORMATION<sup>(1)</sup>

| PRODUCT | PACKAGE TYPE | OPERATING | ORDERING NUMBER | PACKAGE QUANTITY |  |

|---------|--------------|-----------|-----------------|------------------|--|

| VCA5807 | VCA5807 TQFP |           | VCA5807PZP      | 90               |  |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                         |                                           | VALUE   |                    |    |  |

|-------------------------|-------------------------------------------|---------|--------------------|----|--|

|                         |                                           | MIN MAX |                    |    |  |

| Complete and make an    | AVDD                                      | -0.3    | 3.9                | V  |  |

| Supply voltage range    | AVDD_5V                                   | -0.3    | 6                  | V  |  |

| Voltage at analog input | s and digital inputs                      | -0.3    | min [3.6,AVDD+0.3] | V  |  |

| Peak solder temperatu   | re <sup>(2)</sup>                         |         | 260                | °C |  |

| Maximum junction temp   | perature (T <sub>J</sub> ), any condition |         | 105                | °C |  |

| Storage temperature ra  | nge                                       | -55     | 150                | °C |  |

| Operating temperature   | range                                     | -40     | 85                 | °C |  |

| ESD Botings             | НВМ                                       |         | 2000               | V  |  |

| ESD Ratings             | CDM                                       |         | 500                | V  |  |

<sup>(1)</sup> Stresses above those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied Exposure to absolute maximum rated conditions for extended periods may degrade device reliability.

(2) Device complies with JSTD-020D.

#### THERMAL INFORMATION

|                         |                                              | VCA5807  |       |

|-------------------------|----------------------------------------------|----------|-------|

|                         | THERMAL METRIC <sup>(1)</sup>                | TQFP     | UNITS |

|                         |                                              | 100 PINS |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 25.0     |       |

| $\theta_{\text{JCtop}}$ | Junction-to-case (top) thermal resistance    | 6.1      |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 7.7      | 90044 |

| Ψлт                     | Junction-to-top characterization parameter   | 0.2      | °C/W  |

| ΨЈВ                     | Junction-to-board characterization parameter | 7.6      |       |

| $\theta_{JCbot}$        | Junction-to-case (bottom) thermal resistance | 0.2      | 1     |

(1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953. **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                           | MIN  | MAX | UNIT |

|-------------------------------------|------|-----|------|

| AVDD                                | 3.15 | 3.6 | V    |

| AVDD_5V                             | 4.75 | 5.5 | V    |

| Ambient Temperature, T <sub>A</sub> |      | 85  | °C   |

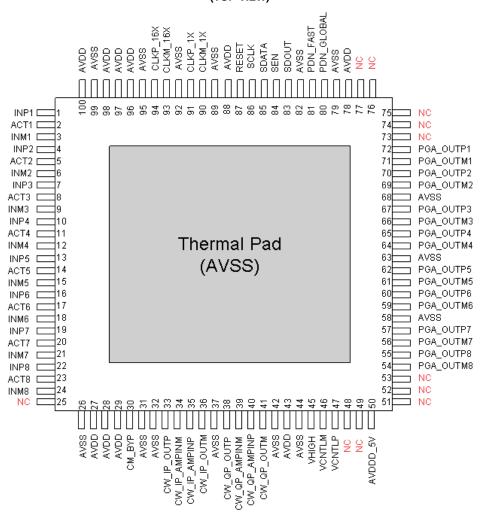

#### PINOUT INFORMATION

# TQFP PACKAGE (TOP VIEW)

#### **PIN FUNCTIONS**

|                                                                     | PIN      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.                                                                 | NAME     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |

| 2, 5, 8, 11, 14,<br>17, 20, 23                                      | ACT1ACT8 | Active termination input pins for CH1~8.1 μF capacitors are recommended.                                                                                                                                                                                                                                                                           |

| 27, 28, 29, 43,<br>78, 88, 96, 97,<br>98, 100                       | AVDD     | 3.3V Analog supply for LNA, VCAT, PGA, LPF and CWD blocks.                                                                                                                                                                                                                                                                                         |

| 50                                                                  | AVDD_5V  | 5V Analog supply for LNA, VCAT, PGA, LPF and CWD blocks.                                                                                                                                                                                                                                                                                           |

| 26, 31, 32, 37,<br>42, 44, 58, 63,<br>68, 79, 82. 89,<br>92, 95, 99 | AVSS     | Analog ground.                                                                                                                                                                                                                                                                                                                                     |

| 93                                                                  | CLKM_16X | Negative input of differential CW 16X clock. Tie to GND when the CMOS clock mode is enabled. In the 4X, 8X, and 32X CW clock modes, this pin becomes the 4X, 8X, or 32X CLKM input. In the 1X CW clock mode, this pin becomes the quadrature-phase 1X CLKM for the CW mixer. Can be floated if CW mode is not used. Please see CW Clock Selection. |

| 94                                                                  | CLKP_16X | Positive input of differential CW 16X clock. In 4X, 8X, and 32X clock modes, this pin becomes the 4X, 8X, or 32X CLKP input. In the 1X CW clock mode, this pin becomes the quadrature-phase 1X CLKP for the CW mixer. Can be floated if CW mode is not used. Please see CW Clock Selection.                                                        |

Submit Documentation Feedback

RUMENTS

#### PIN **DESCRIPTION** NO. NAME Negative input of differential CW 1X clock. Tie to GND when the CMOS clock mode is enabled (Refer 90 CLKM\_1X to Figure 94 for details). In the 1X clock mode, this pin is the In-phase 1X CLKM for the CW mixer. Can be floated if CW mode is not used. Please see CW Clock Selection. Positive input of differential CW 1X clock. In the 1X clock mode, this pin is the In-phase 1X CLKP for 91 CLKP\_1X the CW mixer. Can be floated if CW mode is not used. Please see CW Clock Selection. Bias voltage and bypass to ground. ≥ 1µF is recommended. To suppress ultra low frequency noise, 30 CM\_BYP 10µF can be used. Negative differential input of the In-phase summing amplifier. External LPF capacitor has to be connected between CW\_IP\_AMPINM and CW\_IP\_OUTP. This pin becomes the CH7 PGA negative 34 CW\_IP\_AMPINM output when PGA test mode is enabled. Can be floated if not used. Positive differential input of the In-phase summing amplifier. External LPF capacitor has to be connected between CW\_IP\_AMPINP and CW\_IP\_OUTM. This pin becomes the CH7 PGA positive 35 CW\_IP\_AMPINP output when PGA test mode is enabled. Can be floated if not used. Negative differential output for the In-phase summing amplifier. External LPF capacitor has to be 36 CW\_IP\_OUTM connected between CW\_IP\_AMPINP and CW\_IP\_OUTPM. Can be floated if not used. Positive differential output for the In-phase summing amplifier. External LPF capacitor has to be 33 CW\_IP\_OUTP connected between CW\_IP\_AMPINM and CW\_IP\_OUTP. Can be floated if not used. Negative differential input of the quadrature-phase summing amplifier. External LPF capacitor has to CW\_QP\_AMPIN 39 be connected between CW\_QP\_AMPINM and CW\_QP\_OUTP. This pin becomes CH8 PGA negative output when PGA test mode is enabled. Can be floated if not used. Positive differential input of the quadrature-phase summing amplifier. External LPF capacitor has to be connected between CW\_QP\_AMPINP and CW\_QP\_OUTM. This pin becomes CH8 PGA positive 40 CW\_QP\_AMPINP output when PGA test mode is enabled. Can be floated if not used. Negative differential output for the quadrature-phase summing amplifier. External LPF capacitor has to 41 CW\_QP\_OUTM be connected between CW\_QP\_AMPINP and CW\_QP\_OUTM. Can be floated if not used. Positive differential output for the quadrature-phase summing amplifier. External LPF capacitor has to 38 CW QP OUTP be connected between CW QP AMPINM and CW QP OUTP. Can be floated if not used. 25, 48, 49, 51, 52, 53, 73, 74, NC Do not connect. Must leave floated 75, 76, 77 3, 6, 9, 12, 15, CH1~8 complimentary analog inputs. Bypass to ground with ≥ 0.015µF capacitors. The HPF response INM1...INM8 of the LNA depends on the capacitors. Please see LOW-NOISE AMPLIFIER (LNA). 18, 21, 24 1, 4, 7, 10, 13, INP1...INP8 CH1~8 analog inputs. AC couple to inputs with ≥ 0.1µF capacitors. 16, 19, 22 81 PDN\_FAST VCA partial (fast) power down control pin with an internal pull down resistor of $20k\Omega$ . Active High. Global (complete) power-down control pin for the entire chip with an internal pull down resistor of 80 PDN GLOBAL 20kΩ. Active High. 54, 56, 59, 61, PGA\_OUTMx Negative PGA output 64, 66, 69, 71 55, 57, 60, 62, PGA\_OUTPx Positive PGA output 65, 67, 70, 72 87 RESET Hardware reset pin with an internal pull-down resistor of 20kΩ. Active high. 86 **SCLK** Serial interface clock input with an internal pull-down resistor of $20k\Omega$ 85 **SDATA** Serial interface data input with an internal pull-down resistor of 20kΩ 83 **SDOUT** Serial interface data readout. High impedance when readout is disabled. 84 SEN Serial interface enable with an internal pull up resistor of $20k\Omega$ . Active low. 46 **VCNTLM** Negative differential attenuation control pin. 47 **VCNTLP** Positive differential attenuation control pin 45 VHIGH Bias voltage; bypass to ground with ≥1µF. To suppress ultra low frequency noise, 10µF can be used.

**STRUMENTS**

SLOS727 -DECEMBER 2012 www.ti.com

#### **ELECTRICAL CHARACTERISTICS**

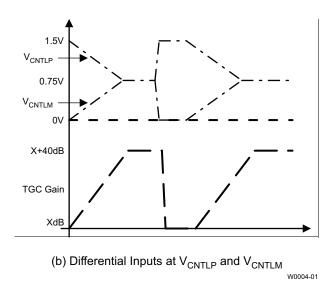

AVDD\_5V = 5V, AVDD = 3.3V, AC-coupled with 0.1µF at INP and bypassed to ground with 15nF at INM, No active termination, V<sub>CNTL</sub>= 0V, f<sub>IN</sub>= 5MHz, LNA = 18dB, PGA = 24dB, LPF Filter = 15MHz, low noise mode, V<sub>OUT</sub>= -1dBFS (1.8V<sub>PP</sub>), single-ended VCNTL mode, VCNTLM = GND, 2 kΩ load (ADC Rin), internal 500Ω CW feedback resistor, CMOS CW clocks, at ambient temperature  $T_A = 25$ °C, unless otherwise noted. Min and max values are specified across full-temperature range with AVDD\_5V=5V, AVDD=3.3V

|                     |                                                              |                                                                                            | MIN TYP        | MAX | UNITS                |

|---------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------|-----|----------------------|

| IGC FULL            | SIGNAL CHANNEL (LNA+VCAT+LPF)                                |                                                                                            |                |     |                      |

|                     | Input voltage noise over LNA Gain(low                        | $R_S = 0\Omega$ , $f = 2MHz$ , LNA =24/18/12dB, PGA = 24dB                                 | 0.76/0.83/1.16 |     |                      |

|                     | noise mode)                                                  | $R_S = 0\Omega$ , $f = 2MHz$ , LNA = 24/18/12dB, PGA = 30dB                                | 0.75/0.86/1.12 |     | nV/rtHz              |

| (DTI)               | Input voltage noise over LNA Gain(low                        | $R_S = 0\Omega$ , $f = 2MHz$ , LNA = 24/18/12dB, PGA = 24dB                                | 1.1/1.2/1.45   |     | ->//                 |

| en (RTI)            | power mode)                                                  | $R_S = 0\Omega$ , $f = 2MHz$ , LNA = 24/18/12dB, PGA = 30dB                                | 1.1/1.2/1.45   |     | nV/rtHz              |

|                     | Input Voltage Noise over LNA                                 | $R_S = 0\Omega$ , $f = 2MHz$ , LNA = 24/18/12dB, PGA = 24dB                                | 1/1.05/1.25    |     | ~\//~H.I=            |

|                     | Gain(Medium Power Mode)                                      | $R_S = 0\Omega$ , $f = 2MHz$ , LNA = 24/18/12dB, PGA = 30dB                                | 0.95/1.0/1.2   |     | nV/rtHz              |

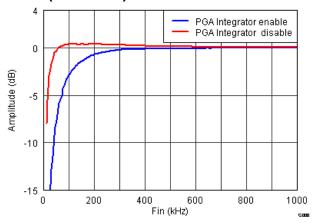

| en (RTI)            | Input voltage noise at low frequency                         | f = 100 KHz, INM Cap = 1uF, PGA integrator disabled (0x33[4]=1)                            | 0.9            |     | nV/rtHz              |

|                     | Input referred current noise                                 | Low Noise Mode/Medium Power Mode/Low Power Mode                                            | 2.7/2.1/2      |     | pA/rtHz              |

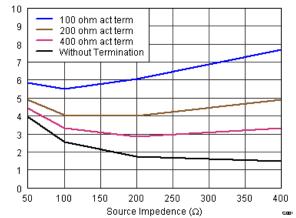

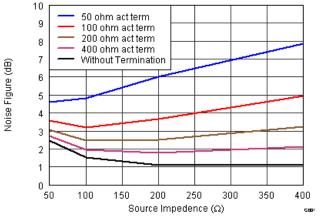

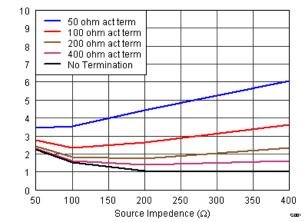

| NF                  | Noise figure                                                 | $R_S = 200\Omega$ , $200\Omega$ active termination, PGA = 24dB, LNA = 12/18/24dB           | 3.85/2.4/1.8   |     | dB                   |

| NF                  | Noise figure                                                 | $R_S = 100\Omega$ , $100\Omega$ active termination, PGA = 24dB, LNA = 12/18/24dB           | 5.3/3.1/2.3    |     | dB                   |

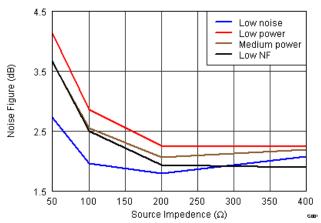

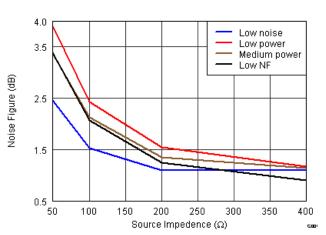

| NF                  | Noise figure                                                 | Rs = 500 $\Omega$ /1K $\Omega$ , no terminaiton, Low NF mode is enabled (Reg53[9]=1)       | 0.94/1.08      |     | dB                   |

| NF                  | Noise ligure                                                 | Noise figure                                                                               |                |     | dB                   |

| VIN <sub>MAX</sub>  | Maximum Linear Input Voltage                                 | LNA gain = 24/18/12dB                                                                      | 250/500/1000   |     | \ /                  |

| V <sub>CLAMP</sub>  | Clamp Voltage                                                | Reg52[10:9] = 0, LNA = 24/18/12dB                                                          | 350/600/1150   |     | $mV_{PP}$            |

|                     | DCA Coin                                                     | Low noise mode                                                                             | 24/30          |     | 4D                   |

|                     | PGA Gain                                                     | Medium/Low power mode                                                                      | 24/28.5        |     | dB                   |

|                     |                                                              | LNA = 24dB, PGA = 30dB, Low noise mode                                                     | 54             |     |                      |

|                     | Total gain                                                   | LNA = 24dB, PGA = 30dB, Med power mode                                                     | 52.5           |     | dB                   |

|                     |                                                              | LNA = 24dB, PGA = 30dB, Low power mode                                                     | 52.5           |     |                      |

| VOUT <sub>MAX</sub> | Maximum Linear Output Voltage                                | Defined as 0 dBFS                                                                          | 2              |     | $V_{PP}$             |

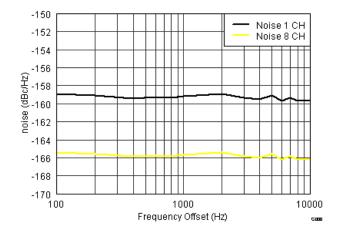

|                     | Ch-CH Noise Correlation Factor without Signal <sup>(1)</sup> | Summing of 8 channels                                                                      | 0              |     |                      |

|                     | Ch-CH Noise Correlation Factor with                          | Full band (V <sub>CNTL</sub> = 0/0.8)                                                      | 0.15/0.17      |     |                      |

|                     | Signal (1)                                                   | 1MHz band over carrier (V <sub>CNTL</sub> = 0/0.8)                                         | 0.18/0.75      |     |                      |

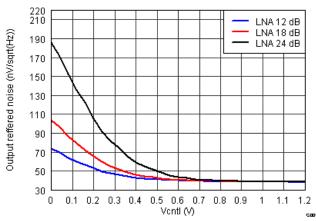

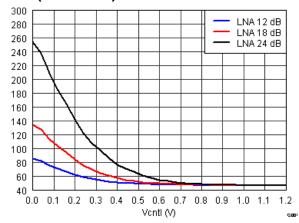

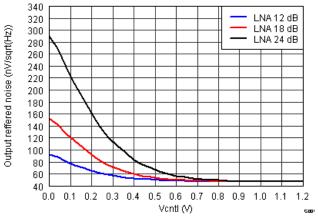

|                     |                                                              | V <sub>CNTL</sub> = 0.6V (22 dB total channel gain)                                        | 40             | 67  |                      |

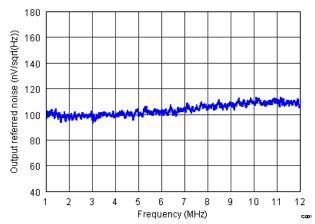

|                     | Output Referred Noise                                        | V <sub>CNTL</sub> = 0, LNA = 18dB, PGA = 24dB                                              | 104            | 153 | nV/rtHz              |

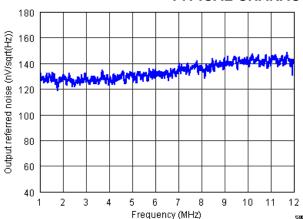

|                     |                                                              | V <sub>CNTL</sub> = 0, LNA = 24dB, PGA = 24dB                                              | 190            |     |                      |

|                     | Narrow Band Integrated Output Noise                          | Noise over 2MHz band around carrier at $V_{\text{CNTL}} = 0.6 \text{V}$ ( 22dB total gain) | 100            | 125 | $\mu V_{\text{RMS}}$ |

|                     | Input Common-mode Voltage                                    | At INP and INM pins                                                                        | 2.4            |     | V                    |

|                     | Input resistance                                             |                                                                                            | 8              |     | kΩ                   |

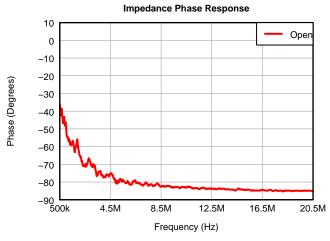

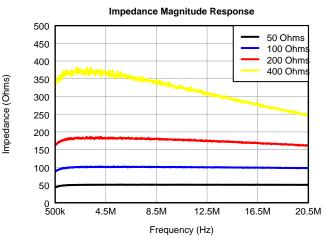

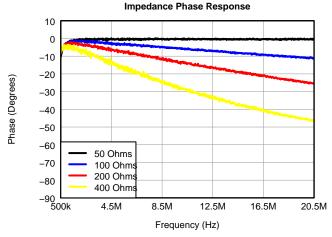

|                     | input resistance                                             | Preset active termination enabled                                                          | 50/100/200/400 |     | Ω                    |

|                     | Input capacitance                                            |                                                                                            | 20             |     | pF                   |

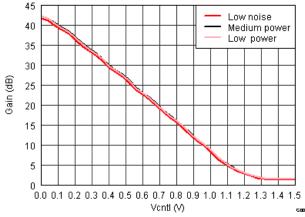

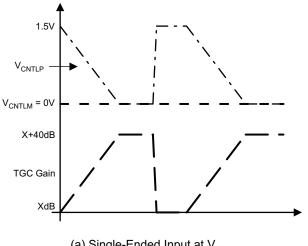

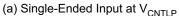

|                     | Input Control Voltage                                        | V <sub>CNTLP</sub> - V <sub>CNTLM</sub>                                                    | 0              | 1.5 | V                    |

|                     | Common-mode voltage                                          | V <sub>CNTLP</sub> and V <sub>CNTLM</sub>                                                  | 0.75           |     | V                    |

|                     | Gain Range                                                   |                                                                                            | -40            |     | dB                   |

|                     | Gain Slope                                                   | V <sub>CNTL</sub> = 0.1V to 1.1V                                                           | 35             |     | dB/V                 |

|                     | Input Resistance                                             | Between V <sub>CNTLP</sub> and V <sub>CNTLM</sub>                                          | 200            |     | ΚΩ                   |

|                     | Input Capacitance                                            | Between V <sub>CNTLP</sub> and V <sub>CNTLM</sub>                                          | 1              |     | pF                   |

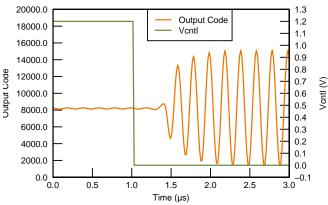

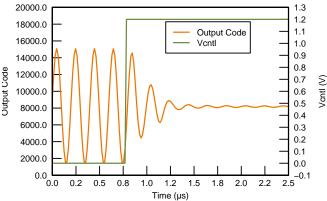

|                     | TGC Response Time                                            | V <sub>CNTL</sub> = 0V to 1.5V step function                                               | 1.5            |     | μs                   |

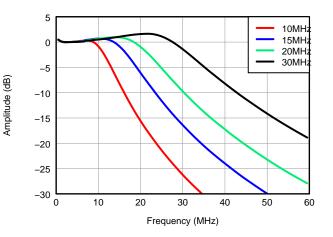

|                     | 3rd order-Low-pass Filter                                    |                                                                                            | 10, 15, 20, 30 |     | MHz                  |

|                     | Settling time for change in LNA gain                         |                                                                                            | 14             |     | μs                   |

|                     | Settling time for change in active termination setting       |                                                                                            | 1              |     | μs                   |

Noise correlation factor is defined as Nc/(Nu+Nc), where Nc is the correlated noise power in single channel; and Nu is the uncorrelated noise power in single channel. Its measurement follows the below equation, in which the SNR of single channel signal and the SNR of summed eight channel signal are measured.

8CH\_SNR

Product Folder Links: VCA5807

$$\frac{N_{C}}{N_{U} + N_{C}} = \frac{\frac{-0.01}{0.000}}{\frac{-0.01}{10}} \times \frac{1}{56} - \frac{1}{7}$$

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

#### **ELECTRICAL CHARACTERISTICS (continued)**

AVDD\_5V = 5V, AVDD = 3.3V, AC-coupled with  $0.1\mu F$  at INP and bypassed to ground with 15nF at INM, No active termination,  $V_{CNTL}$ = 0V,  $f_{IN}$ = 5MHz, LNA = 18dB, PGA = 24dB, LPF Filter = 15MHz, low noise mode,  $V_{OUT}$ = -1dBFS (1.8V<sub>PP</sub>), single-ended VCNTL mode, VCNTLM = GND, 2 k $\Omega$  load (ADC Rin), internal 500 $\Omega$  CW feedback resistor, CMOS CW clocks, at ambient temperature  $T_A$  = 25°C, unless otherwise noted. Min and max values are specified across full-temperature range with AVDD\_5V=5V, AVDD=3.3V

|                     | PARAMETER                     | TEST CONDITION                                                                                                                                             | MIN   | TYP           | MAX  | UNITS           |

|---------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------|------|-----------------|

| AC ACCU             | RACY                          |                                                                                                                                                            |       |               |      |                 |

|                     | LPF Bandwidth tolerance       |                                                                                                                                                            |       | ±5            |      | %               |

|                     | CH-CH group delay variation   | 2MHz to 15MHz                                                                                                                                              |       | 2             |      | ns              |

|                     | CH-CH Phase variation         | 15MHz signal                                                                                                                                               |       | 11            |      | Degree          |

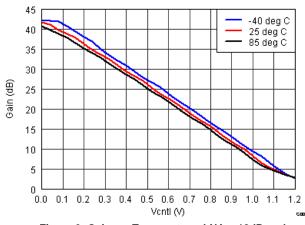

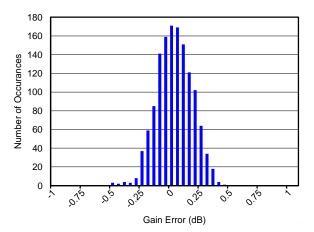

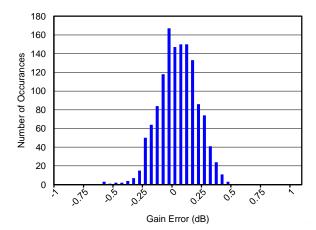

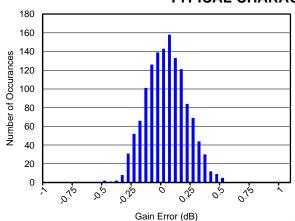

|                     |                               | 0V < V <sub>CNTL</sub> < 0.1V (Dev-to-Dev)                                                                                                                 |       | ±0.5          |      |                 |

|                     | Onin matchin a                | 0.1V< V <sub>CNTL</sub> < 1.1V(Dev-to-Dev)                                                                                                                 | -1.05 | ±0.5          | 1.05 | -ID             |

|                     | Gain matching                 | 0.1V< V <sub>CNTL</sub> < 1.1V(Dev-to-Dev) Temp = -40°C and 85°C                                                                                           | -1.25 | ±0.5          | 1.25 | dB              |

|                     |                               | 1.1V< V <sub>CNTL</sub> < 1.5V(Dev-to-Dev)                                                                                                                 |       | ±0.5          |      |                 |

|                     | Gain matching                 | Channel-to-Channel                                                                                                                                         |       | ±0.25         |      | dB              |

|                     | Output offset                 | V <sub>CNTL</sub> = 0, PGA = 30dB, LNA = 24dB                                                                                                              | -6    |               | 6    | mV              |

| AC PERF             | ORMANCE                       |                                                                                                                                                            |       |               |      |                 |

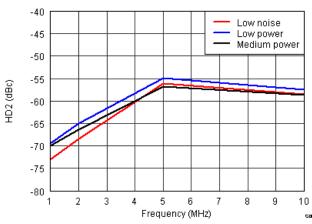

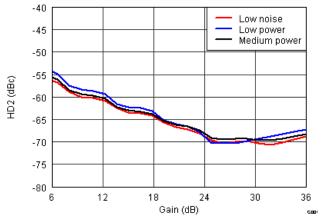

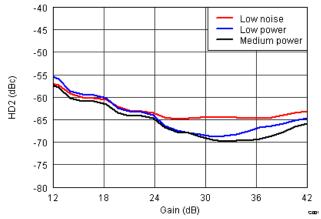

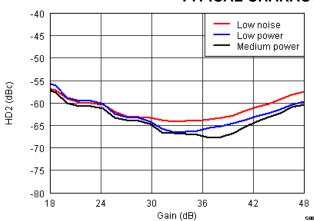

|                     |                               | F <sub>IN</sub> = 2MHz; V <sub>OUT</sub> = -1dBFS                                                                                                          |       | -60           |      |                 |

|                     |                               | F <sub>IN</sub> = 5MHz; V <sub>OUT</sub> = -1dBFS                                                                                                          |       | -60           |      |                 |

| HD2                 | Second-Harmonic Distortion    | $\begin{aligned} F_{IN} &= 5MHz; \ V_{IN} = 500mV_{PP}, \\ V_{OUT} &= -1dBFS, \ LNA = 18dB \end{aligned}$                                                  |       | -55           |      | dBc             |

|                     |                               | F <sub>IN</sub> = 5MHz; Vin = 250mV <sub>PP</sub> ,<br>V <sub>OUT</sub> =-1dBFS, LNA = 24dB                                                                |       | -55           |      |                 |

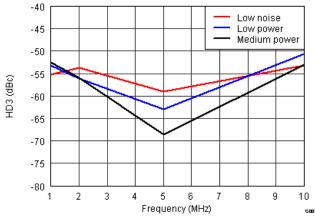

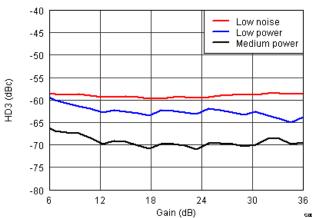

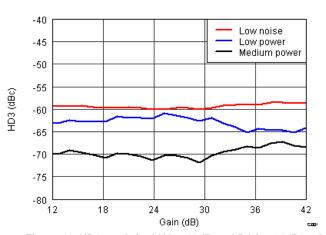

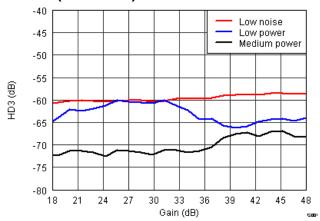

|                     |                               | F <sub>IN</sub> = 2MHz; V <sub>OUT</sub> = -1dBFS                                                                                                          |       | -53           |      |                 |

|                     |                               | F <sub>IN</sub> = 5MHz; V <sub>OUT</sub> = -1dBFS                                                                                                          |       | -55           |      |                 |

| HD3                 | Third-Harmonic Distortion     | $F_{IN} = 5MHz$ ; $VIN = 500mV_{PP}$ , $V_{OUT} = -10BFS$ , $LNA = 18dB$                                                                                   |       | -55           |      | dBc             |

|                     |                               | $\begin{aligned} F_{\text{IN}} &= 5 \text{MHz; VIN} = 250 \text{mV}_{\text{PP}} \;, \\ V_{\text{OUT}} &= -1 \text{dBFS, LNA} = 24 \text{dB} \end{aligned}$ |       | <b>-</b> 55   |      |                 |

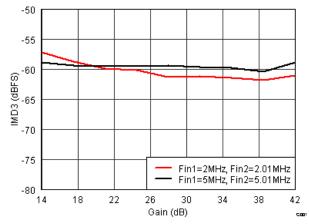

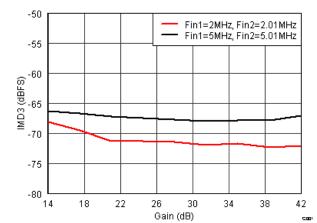

| TI ID               | T                             | F <sub>IN</sub> = 2MHz; V <sub>OUT</sub> = -1dBFS                                                                                                          |       | -52.5         |      |                 |

| THD                 | Total Harmonic Distortion     | F <sub>IN</sub> = 5MHz; V <sub>OUT</sub> = -1dBFS                                                                                                          |       | -55           |      | dBc             |

| IMD3                | Intermodulation distortion    | f1 = 5MHz at -1dBFS,<br>f2 = 5.01MHz at -27dBFS                                                                                                            |       | -60           |      | dBc             |

| XTALK               | Cross-talk                    | F <sub>IN</sub> = 5MHz; V <sub>OUT</sub> = -1dBFS                                                                                                          |       | -65           |      | dBc             |

|                     | Phase Noise                   | 1kHz off 5MHz (V <sub>CNTL</sub> =0V)                                                                                                                      |       | -132          |      | dBc/Hz          |

| LNA                 |                               |                                                                                                                                                            |       |               |      |                 |

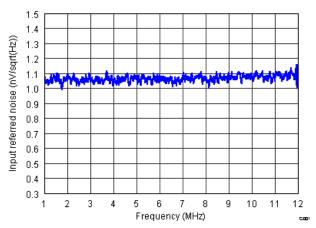

|                     | Input Referred Voltage Noise  | $R_S = 0\Omega$ , $f = 2MHz$ , $R_{IN} = High Z$ , $Gain = 24/18/12dB$                                                                                     |       | 0.63/0.70/0.9 |      | nV/rtHz         |

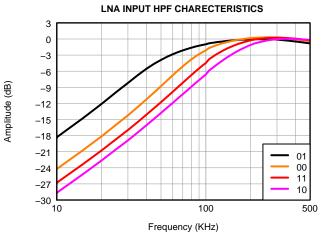

|                     | High-Pass Filter              | -3dB Cut-off Frequency                                                                                                                                     | 5     | 0/100/150/200 |      | KHz             |

|                     | LNA linear output             |                                                                                                                                                            |       | 4             |      | Vpp             |

| VCAT+ PO            | GA                            |                                                                                                                                                            |       |               |      |                 |

|                     | VCAT Input Noise              | 0dB/-40dB Attenuation                                                                                                                                      |       | 2/10.5        |      | nV/rtHz         |

|                     | PGA Input Noise               | 24dB/30dB                                                                                                                                                  |       | 1.75          |      | nV/rtHz         |

|                     | -3dB HPF cut-off Frequency    | High-Pass Filter is enabled                                                                                                                                |       | 80            |      | KHz             |

|                     | Output Common Mode Voltage    | -                                                                                                                                                          |       | 0.9           |      | V               |

| VOUT <sub>MAX</sub> | Maximum Linear Output Voltage | Defined as 0 dBFS                                                                                                                                          |       | 2             |      | V <sub>PP</sub> |

|                     | Minimum Load Impedance        |                                                                                                                                                            |       | 1             |      | ΚΩ              |

**STRUMENTS**

SLOS727 - DECEMBER 2012 www.ti.com

#### **ELECTRICAL CHARACTERISTICS (continued)**

AVDD\_5V = 5V, AVDD = 3.3V, AC-coupled with  $0.1\mu F$  at INP and bypassed to ground with 15nF at INM, No active termination,  $V_{CNTL}$ = 0V,  $f_{IN}$ = 5MHz, LNA = 18dB, PGA = 24dB, LPF Filter = 15MHz, low noise mode,  $V_{OUT}$ = -1dBFS (1.8V<sub>PP</sub>), single-ended VCNTL mode, VCNTLM = GND, 2 k $\Omega$  load (ADC Rin), internal 500 $\Omega$  CW feedback resistor, CMOS CW clocks, at ambient temperature  $T_A$  = 25°C, unless otherwise noted. Min and max values are specified across full-temperature range with AVDD\_5V=5V, AVDD=3.3V

| PARAMETER         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TEST CONDITION                                                                                                                | MIN TYP     | MAX | UNITS      |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------|-----|------------|

| CW DOPP           | LER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                               |             |     |            |

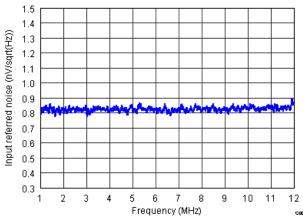

| (DTI)             | land wells as a size (OM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 channel mixer, LNA = 24dB, 500Ω feedback resistor                                                                           | 0.8         |     |            |

| en (RTI)          | Input voltage noise (CW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8 channel mixer, LNA = 24dB, 62.5Ω feedback resistor                                                                          | 0.33        |     | nV/rtHz    |

| (DTO)             | Output walters are in (OIAI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 channel mixer, LNA = 24dB, 500Ω feedback resistor                                                                           | 12          |     | ~\//~tl.l= |

| en (RTO)          | Output voltage noise (CW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8 channel mixer, LNA = 24dB, 62.5Ω feedback resistor                                                                          | 5           |     | nV/rtHz    |

| (DTI)             | land the land of the control of the | 1 channel mixer, LNA = 18dB, 500Ω feedback resistor                                                                           | 1.1         |     | ~\//~tl.l= |

| en (RTI)          | Input voltage noise (CW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8 channel mixer, LNA = 18dB, 62.5Ω feedback resistor                                                                          | 0.5         |     | nV/rtHz    |

| (DTO)             | Output walters are in (OIAI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 channel mixer, LNA = 18dB, 500Ω feedback resistor                                                                           | 8.1         |     | ~\//~tl.l= |

| en (RTO)          | Output voltage noise (CW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8 channel mixer, LNA = 18dB, 62.5Ω feedback resistor                                                                          | 4.0         |     | nV/rtHz    |

| NF                | Noise figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $R_S=100\Omega,R_{IN}=$ High Z, $F_{IN}=$ 2MHz (LNA, I/Q mixer and summing amplifier/filter)                                  | 1.8         |     | dB         |

| f <sub>CW</sub>   | CW Operation Range <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CW signal carrier frequency, 16X mode / 32X mode                                                                              | 8/4         |     | MHz        |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1X CLK (16X mode)                                                                                                             | 8           |     |            |

|                   | CW Clock frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16X CLK(16X mode)                                                                                                             | 128         |     | MHz        |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4X CLK(4X mode)                                                                                                               | 32          |     | IVITZ      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32X CLK(32X mode)                                                                                                             | 128         |     |            |

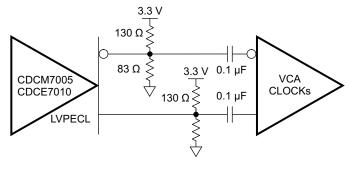

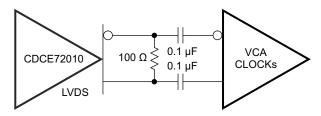

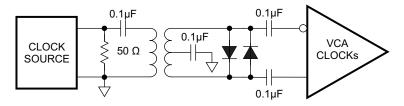

|                   | AC coupled LVDS clock amplitude                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CLYM 4CY CLYP 4CY, CLYM 4Y CLYP 4Y                                                                                            | 0.7         |     | V          |

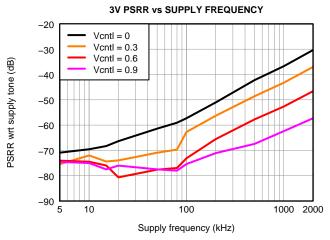

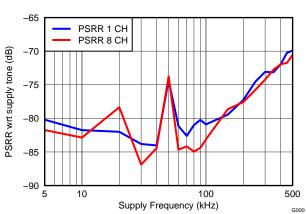

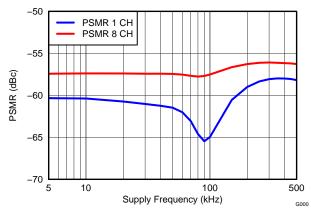

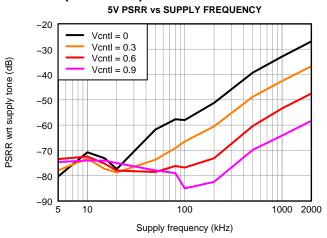

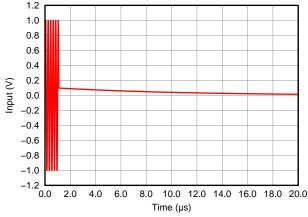

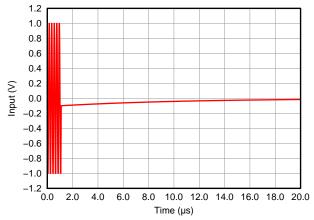

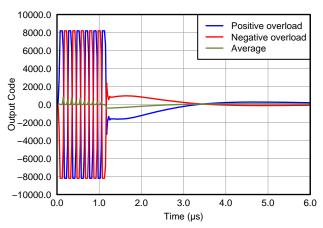

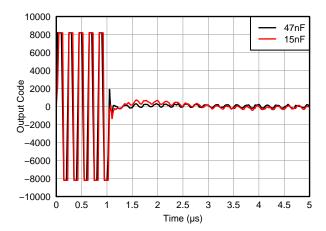

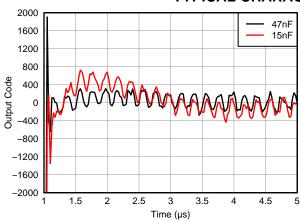

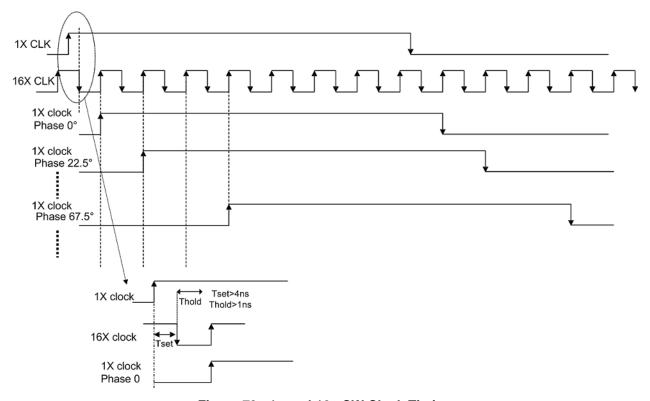

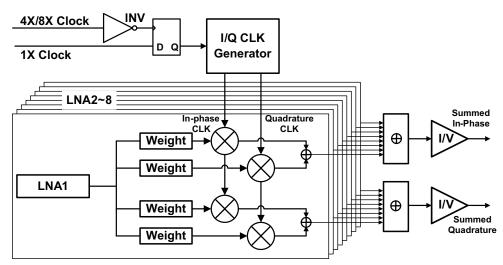

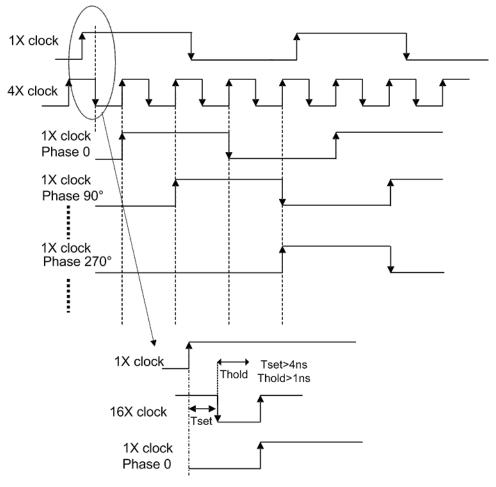

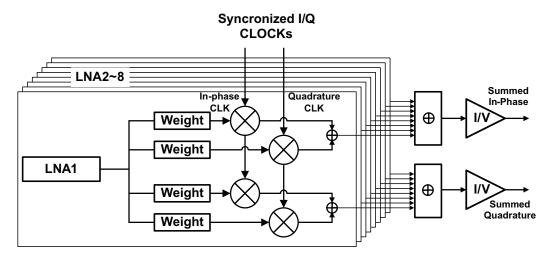

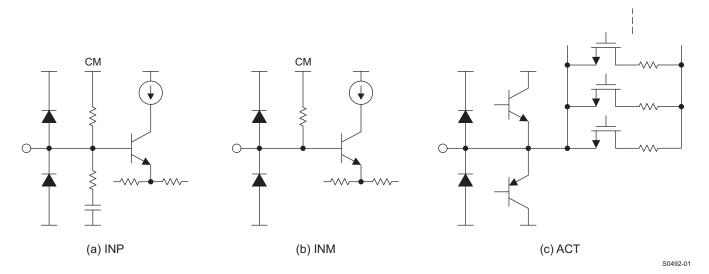

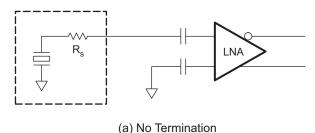

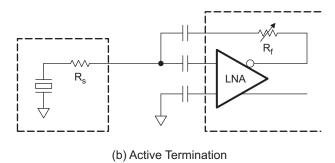

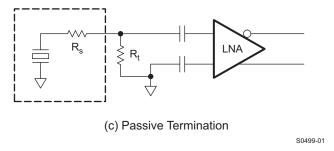

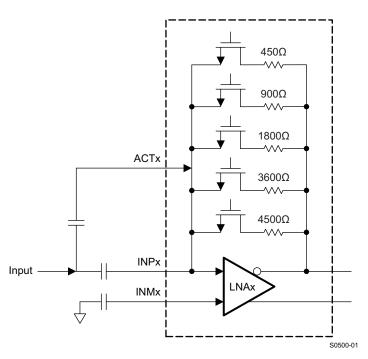

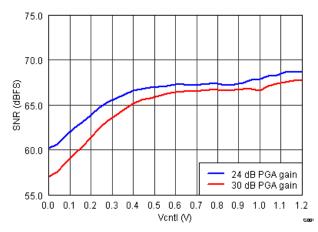

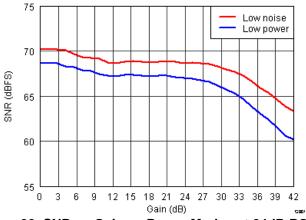

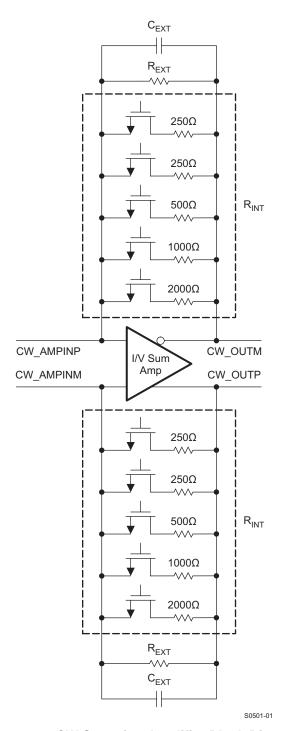

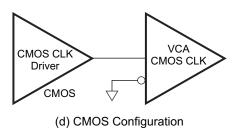

|                   | AC coupled LVPECL clock amplitude                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CLKM_16X-CLKP_16X; CLKM_1X-CLKP_1X                                                                                            | 1.6         |     | $V_{PP}$   |