# LM98640 Dual Channel, 14-Bit, 40 MSPS Analog Front End with LVDS Output

Check for Samples: LM98640

## **FEATURES**

- Seialized LVDS Outputs

- LVDS Input Clock

- CDS or S/H Processing for CCD or CIS Sensors

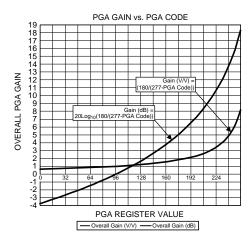

- Programmable Analog Gain for Each Channel

- Programmable Analog Offset Correction

- Programmable Input Clamp Voltage

- Programmable Sampling Edge up to 1/64th Pixel Period

## **KEY SPECIFICATIONS**

Input Level: 2.85 VoltsADC Resolution: 14 Bit

ADC Sampling Rate: 5 MSPS to 40 MSPS

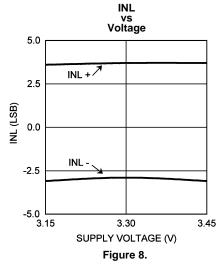

INL @ 15 MHz: ±3.5 LSB

CDS or S/H Gain: 0 dB or 6 dBPGA Gain Steps: 256 Steps

PGA Gain Range: -3 dB to 18 dB

• Coarse DAC Resolution: ±8 Bits

Coarse DAC Range: ±250 mV

Fine DAC Resolution: ±8 Bits

Fine DAC Range: ±5 mV

Noise Floor: -79 dB

Crosstalk: -80dB

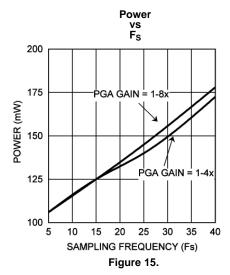

Power Consumption

PGA 1-4x Gain:

- 125 mW per Channel (15 MSPS)

140 mW per Channel (25 MSPS)

PGA 1-8x Gain:

125 mW per Channel (15 MSPS)

- 178 mW per Channel (40 MSPS)

Supply Voltages:

3.3V Nominal (3.15V to 3.45V Range)

1.8V Nominal (1.7V to 1.9V Range)

#### **APPLICATIONS**

- Focal Plane Electronics

- Imaging Attitude Control Systems

- Assembly Line Vision Systems

- Factory Automation Vision Systems

- High-speed Document Scanner

- Multi- Function Peripherals

#### DESCRIPTION

The LM98640 is a fully integrated, high performance 14-bit, 5 MSPS to 40 MSPS signal processing solution for image processing applications. The Serial LVDS Output format performs well during ionizing doses, preventing data loss. The LM98640 has an adaptive power scaling feature to optimize power consumption based on the operating frequency and amount of gain required. High-speed signal throughput is achieved with an innovative architecture utilizing Correlated Double Sampling (CDS), typically employed with CCD arrays, or Sample and Hold (S/H) inputs (for Contact Image Sensors and CMOS sensors). The image sampling edges programmable to a resolution of 1/64th of a pixel period. Both the CDS and S/H have a programmable gain of either 0 dB or 6 dB. The signal paths utilize two ±8 bit offset correction DACs for coarse and fine offset correction, and 8 bit Programmable Gain Amplifiers (PGA) for each channel. The PGA and offset DAC are programmed independently allowing unique values of gain and offset for each input. The signals are then routed to two on chip 14-bit 40 MHz high performance analog-to-digital converters (ADC). The fully differential processing channel provides exceptional noise immunity, having a very low noise floor of -79 dB with a gain of 1x. The 14-bit ADCs have excellent dynamic performance making the LM98640 transparent in the image reproduction chain.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

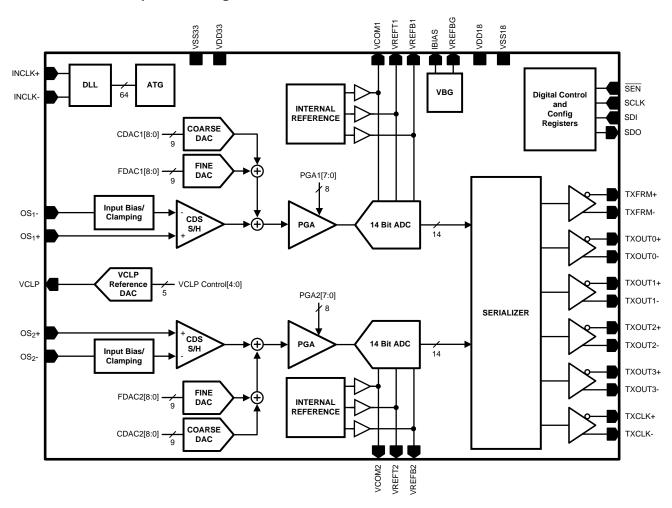

## LM98640 Overall Chip Block Diagram

Figure 1. Chip Block Diagram

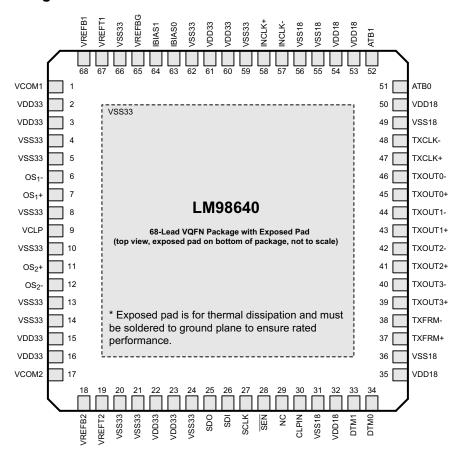

## LM98640 Pin Out Diagram

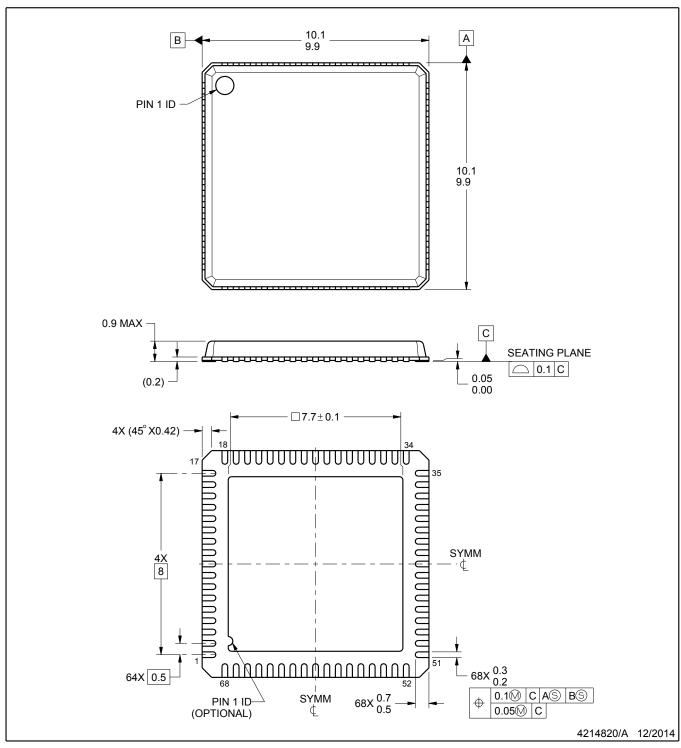

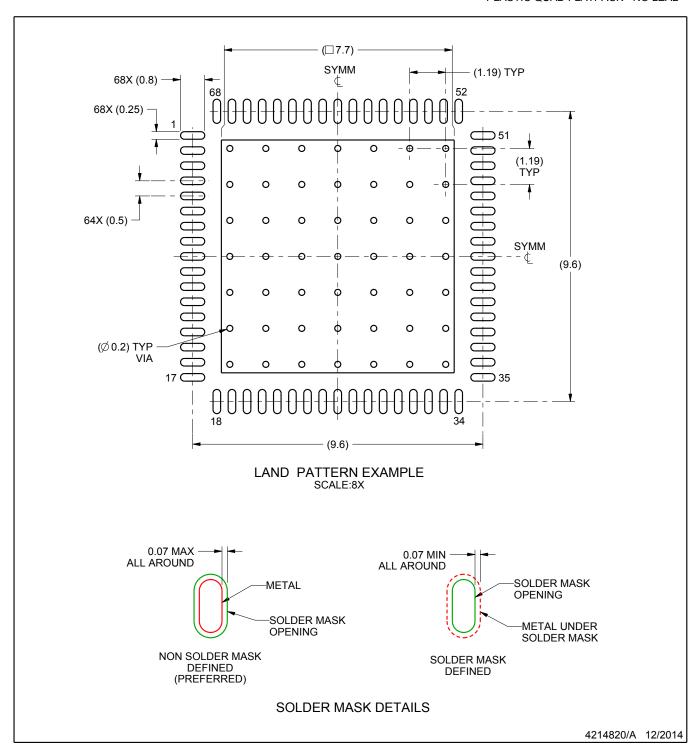

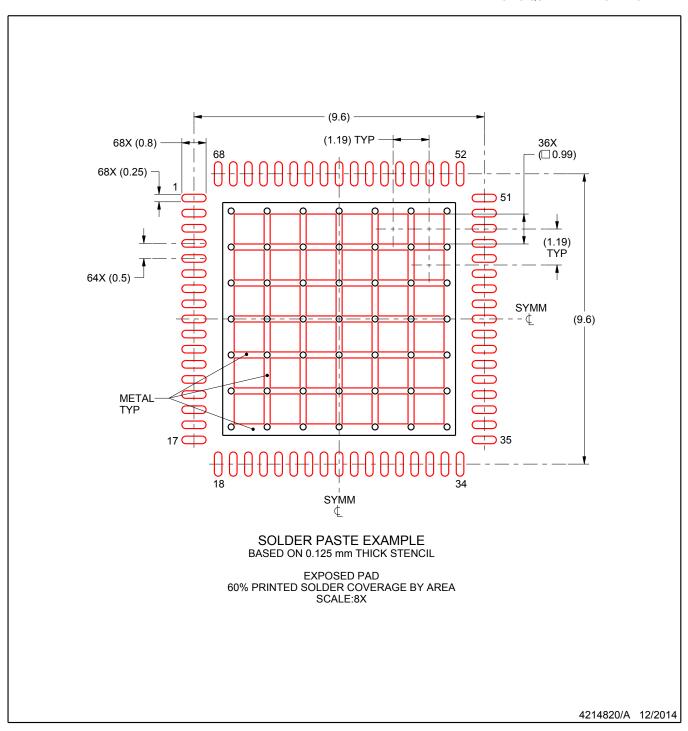

Figure 2. LM98640 Pin Out Diagram VQFN Package See Package Number NKE0068A

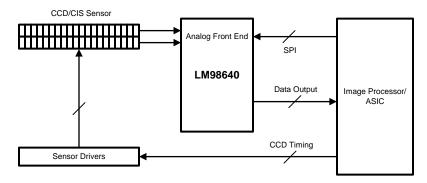

## **System Block Diagram**

Figure 3. TYPICAL CCD SYSTEM

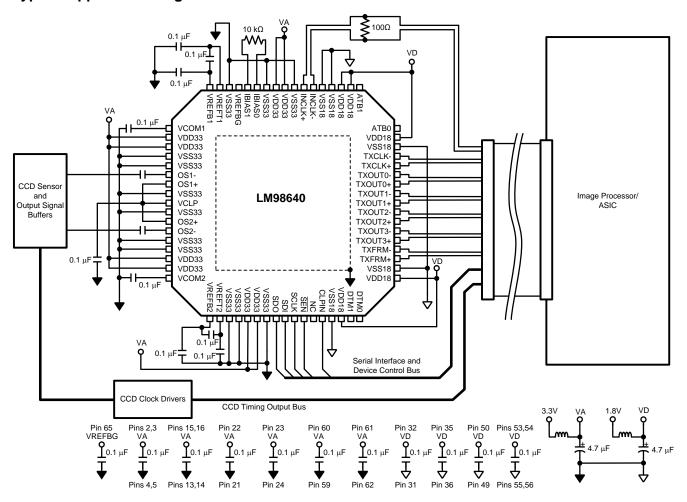

## **Typical Application Diagram**

Figure 4. Typical Sample/Hold Mode Application Diagram

## **PIN DESCRIPTIONS**

| Pin | Name    | I/O <sup>(1)</sup> | Тур | Res | Description                                                                                     |

|-----|---------|--------------------|-----|-----|-------------------------------------------------------------------------------------------------|

| 1   | VCOM1   | 0                  | Α   |     | Common mode of ADC reference. Bypass with 0.1 µF capacitor to VSS33.                            |

| 2   | VDD33   |                    | Р   |     | Analog power supply. Decouple with minimum 0.1 µF capacitor to VSS33 plane.                     |

| 3   | VDD33   |                    | Р   |     | Analog power supply. Decouple with minimum 0.1 µF capacitor to VSS33 plane.                     |

| 4   | VSS33   |                    | Р   |     | Analog supply return.                                                                           |

| 5   | VSS33   |                    | Р   |     | Analog supply return.                                                                           |

| 6   | OS1-    | 1                  | Α   |     | Analog input signal.                                                                            |

| 7   | OS1+    | 1                  | Α   |     | Sample/Hold Mode Reference Level. Bypassed with a 0.1 µF to ground in CDS mode.                 |

| 8   | VSS33   |                    | Р   |     | Analog supply return.                                                                           |

| 9   | VCLP    | 0                  | Α   |     | Programmable Clamp Voltage output. Normally bypassed with a 0.1 μF capacitor to VSS33.          |

| 10  | VSS33   |                    | Р   |     | Analog supply return.                                                                           |

| 11  | OS2+    | I                  | Α   |     | Sample/Hold Mode Reference Level. Bypassed with a 0.1 µF to ground in CDS mode.                 |

| 12  | OS2-    | I                  | Α   |     | Analog input signal.                                                                            |

| 13  | VSS33   |                    | Р   |     | Analog supply return.                                                                           |

| 14  | VSS33   |                    | Р   |     | Analog supply return.                                                                           |

| 15  | VDD33   |                    | Р   |     | Analog power supply. Decouple with minimum 0.1 µF capacitor to VSS33 plane.                     |

| 16  | VDD33   |                    | Р   |     | Analog power supply. Decouple with minimum 0.1 µF capacitor to VSS33 plane.                     |

| 17  | VCOM2   | 0                  | Α   |     | Common mode of ADC reference. Bypass with 0.1 µF capacitor to ground.                           |

| 18  | VREFB2  | 0                  | Α   |     | Bottom of ADC reference. Bypass with a 0.1 µF capacitor to ground.                              |

| 19  | VREFT2  | 0                  | Α   |     | Top of ADC reference. Bypass with a 0.1 μF capacitor to ground.                                 |

| 20  | VSS33   |                    | Р   |     | Analog supply return.                                                                           |

| 21  | VSS33   |                    | Р   |     | Analog supply return.                                                                           |

| 22  | VDD33   |                    | Р   |     | Analog power supply. Decouple with minimum 0.1 µF capacitor to VSS33 plane.                     |

| 23  | VDD33   |                    | Р   |     | Analog power supply. Decouple with minimum 0.1 µF capacitor to VSS33 plane.                     |

| 24  | VSS33   |                    | Р   |     | Analog supply return.                                                                           |

| 25  | SDO     | 0                  | D   |     | Serial Interface Data Output. (Tri-State when SEN is high)                                      |

| 26  | SDI     | I                  | D   |     | Serial Interface Data Input. (Tri-State when SEN is high)                                       |

| 27  | SCLK    | I                  | D   | PD  | Serial Interface shift register clock. (Tri-State when SEN is high)                             |

| 28  | SEN     | I                  | D   | PU  | Active-low chip enable for the Serial Interface.                                                |

| 29  | NC      |                    |     |     | No Connection. Can be connected to VSS18.                                                       |

| 30  | CLPIN   | I                  | D   |     | Input clamp signal.                                                                             |

| 31  | VSS18   |                    | Р   |     | Digital supply return.                                                                          |

| 32  | VDD18   |                    | Р   |     | Digital power supply. Decouple with minimum 0.1 μF capacitor to VSS18 plane.                    |

| 33  | DTM1    | 0                  | D   |     | Digital Timing Monitor. If not used, can be connected to VDD18 through a $10k\Omega$ resistor.  |

| 34  | DTM0    | 0                  | D   |     | Digital Timing Monitor. If not used, can be connected to VDD18 through a 10 $k\Omega$ resistor. |

| 35  | VDD18   |                    | Р   |     | Digital power supply. Decouple with minimum 0.1 μF capacitor to VSS18 plane.                    |

| 36  | VSS18   |                    | Р   |     | Digital supply return.                                                                          |

| 37  | TXFRM+  | 0                  | D   |     | LVDS Frame+                                                                                     |

| 38  | TXFRM-  | 0                  | D   |     | LVDS Frame-                                                                                     |

| 39  | TXOUT3+ | 0                  | D   |     | LVDS Data Out3+                                                                                 |

| 40  | TXOUT3- | 0                  | D   |     | LVDS Data Out3-                                                                                 |

| 41  | TXOUT2+ | 0                  | D   |     | LVDS Data Out2+                                                                                 |

| 42  | TXOUT2- | 0                  | D   |     | LVDS Data Out2-                                                                                 |

| 43  | TXOUT1+ | 0                  | D   |     | LVDS Data Out1+                                                                                 |

| 44  | TXOUT1- | 0                  | D   |     | LVDS Data Out1-                                                                                 |

| 45  | TXOUT0+ | 0                  | D   |     | LVDS Data Out0+                                                                                 |

<sup>(1) (</sup>I=Input), (O=Output), (IO=Bi-directional), (P=Power), (D=Digital), (A=Analog), (PU=Pull Up with an internal resistor), (PD=Pull Down with an internal resistor.).

## **PIN DESCRIPTIONS (continued)**

| Pin | Name    | I/O <sup>(1)</sup> | Тур | Res | Description                                                                                                              |  |

|-----|---------|--------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------|--|

| 46  | TXOUT0- | 0                  | D   |     | LVDS Data Out0-                                                                                                          |  |

| 47  | TXCLK+  | 0                  | D   |     | LVDS Clock+                                                                                                              |  |

| 48  | TXCLK-  | 0                  | D   |     | LVDS Clock-                                                                                                              |  |

| 49  | VSS18   |                    | Р   |     | Digital supply return.                                                                                                   |  |

| 50  | VDD18   |                    | Р   |     | Digital power supply. Decouple with minimum 0.1 µF capacitor to VSS18 plane.                                             |  |

| 51  | ATB0    | 0                  | Α   |     | Analog Test Bus. If not used, can be connected to VSS18 through a 10 $k\Omega$ resistor.                                 |  |

| 52  | ATB1    | 0                  | Α   |     | Analog Test Bus. If not used, can be connected to VSS18 through a 10 $k\Omega$ resistor.                                 |  |

| 53  | VDD18   |                    | Р   |     | Digital power supply. Decouple with minimum 0.1 µF capacitor to VSS18 plane.                                             |  |

| 54  | VDD18   |                    | Р   |     | Digital power supply. Decouple with minimum 0.1 µF capacitor to VSS18 plane.                                             |  |

| 55  | VSS18   |                    | Р   |     | Digital supply return.                                                                                                   |  |

| 56  | VSS18   |                    | Р   |     | Digital supply return.                                                                                                   |  |

| 57  | INCLK-  | I                  | D   |     | Clock Input. Inverting input for LVDS clocks.                                                                            |  |

| 58  | INCLK+  | I                  | D   |     | Clock Input. Non-Inverting input for LVDS clocks.                                                                        |  |

| 59  | VSS33   |                    | Р   |     | Analog supply return.                                                                                                    |  |

| 60  | VDD33   |                    | Р   |     | Analog power supply. Decouple with minimum 0.1 µF capacitor to VSS33 plane.                                              |  |

| 61  | VDD33   |                    | Р   |     | Analog power supply. Decouple with minimum 0.1 µF capacitor to VSS33 plane.                                              |  |

| 62  | VSS33   |                    | Р   |     | Analog supply return.                                                                                                    |  |

| 63  | IBIAS0  | 1                  | Α   |     | Connect with external 10 k $\Omega$ 1% resistor to IBIAS1 pin.                                                           |  |

| 64  | IBIAS1  | 1                  | Α   |     | Connect with external 10 k $\Omega$ 1% resistor to IBIAS0 pin.                                                           |  |

| 65  | VREFBG  | 0                  | Α   |     | Band gap reference output. Bypass with a 0.1 $\mu F$ capacitor to VSS33. Can be overdriven with external voltage source. |  |

| 66  | VSS33   |                    | Р   |     | Analog supply return.                                                                                                    |  |

| 67  | VREFT1  | 0                  | Α   |     | Top of ADC reference. Bypass with a 0.1 μF capacitor to VSS33.                                                           |  |

| 68  | VREFB1  | 0                  | Α   |     | Bottom of ADC reference. Bypass with a 0.1 µF capacitor to VSS33.                                                        |  |

|     | Exp Pad |                    | Р   |     | Exposed pad must be soldered to ground plane to ensure rated performance.                                                |  |

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# Absolute Maximum Ratings(1)(2)

| Supply Voltage (VDD33)                                                                                                          | 4.2V                          |                         |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------|--|--|

| Supply Voltage (VDD18)                                                                                                          | 2.35V                         |                         |  |  |

| Voltage on any VDD33 Input Pin (Not to ex                                                                                       | ceed 4.2V)                    | -0.3V to (VDD33 + 0.3V) |  |  |

| Voltage on any VDD33 Output Pin (Not to                                                                                         | exceed 4.2V)                  | -0.3V to (VDD33 + 0.3V) |  |  |

| Voltage on any VDD18 Input Pin (Not to ex                                                                                       | ceed 2.35V)                   | -0.3V to (VDD18 + 0.3V) |  |  |

| Voltage on any VDD18 Output Pin (Not to                                                                                         | exceed 2.35V)                 | -0.3V to (VDD18 + 0.3V) |  |  |

| Input Current at any pin other than Supply                                                                                      | ±25 mA                        |                         |  |  |

| Package Input Current (except Supply Pins                                                                                       | ±50 mA                        |                         |  |  |

| Maximum Junction Temperature (TA)                                                                                               |                               | 150°C                   |  |  |

| Thermal Resistance (4)                                                                                                          | (θ <sub>JA</sub> ) @ 225 LFPB | 16.7°C/W                |  |  |

| Thermal Resistance (7)                                                                                                          | (θ <sub>JA</sub> ) @ 0 LFPB   | 22.5°C/W                |  |  |

|                                                                                                                                 | Human Body Model              | 4000V                   |  |  |

| ESD Rating <sup>(5)</sup>                                                                                                       | Machine Model                 | 200V                    |  |  |

|                                                                                                                                 | Charged Device Model          | 750V                    |  |  |

| Storage Temperature                                                                                                             | -65°C to +150°C               |                         |  |  |

| Soldering process must comply with Texas Instruments Reflow Temperature Profile specifications. Refer to SNOA549 <sup>(6)</sup> |                               |                         |  |  |

- 1) All voltages are measured with respect to VSS = 0V, unless otherwise specified.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the Operating Ratings is not recommended.

- (3) When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supplies (V<sub>IN</sub> < VSS or V<sub>IN</sub> > VDD33), the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input current of 25 mA to two.

- (4) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub> and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any temperature is P<sub>D</sub> = (T<sub>JMAX</sub> T<sub>A</sub>)/θ<sub>JA</sub>. The values for maximum power dissipation listed above will be reached only when the device is operated in a severe fault condition (e.g. when input or output pins are driven beyond the power supply voltages, or the power supply polarity is reversed). Such conditions should always be avoided.

- (5) Human body model is 100 pF capacitor discharged through a 1.5 kΩ resistor. Machine model is 220 pF discharged through 0Ω.

- (6) Reflow temperature profiles are different for lead-free and non-lead-free packages.

# Operating Ratings<sup>(1)(2)</sup>

| Operating Temperature Range | 0°C ≤ T <sub>A</sub> ≤ +70°C |

|-----------------------------|------------------------------|

| VDD33                       | +3.15V to +3.45V             |

| VDD18                       | +1.7V to +1.9V               |

| VSS33 - VSS18               | ≤100 mV                      |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the Operating Ratings is not recommended.

- (2) All voltages are measured with respect to VSS = 0V, unless otherwise specified.

# LM98640 Electrical Characteristics (1)

The following specifications apply for VDD33 = 3.3V, VDD18 = 1.8V,  $C_L$  = 10 pF, and  $f_{\text{INCLK}}$  = 40 MHz unless otherwise specified. **Boldface limits apply for TA = TMIN to TMAX**; **all other limits TA = 25°C.**

| Symbol           | Parameter                                            | Conditions                                                  |       | Min  | Max | Units |

|------------------|------------------------------------------------------|-------------------------------------------------------------|-------|------|-----|-------|

| CMOS Digital In  | put DC Specifications (SCLK, SEN, SDI,               | CLPIN)                                                      |       |      |     |       |

| V <sub>IH</sub>  | Logical "1" Input Voltage                            |                                                             |       | 2.0  |     | V     |

| V <sub>IL</sub>  | Logical "0" Input Voltage                            |                                                             |       |      | 0.8 | V     |

|                  |                                                      | CLPIN                                                       | 40    |      | 46  | μA    |

| I <sub>IH</sub>  | Logical "1" Input Current<br>V <sub>IH</sub> = VDD33 | SCLK, SDI                                                   | 40    |      | 300 | nA    |

|                  |                                                      | SEN                                                         | 24    |      | 30  | μΑ    |

|                  | Lariaal "O" larut Cumant                             | CLPIN                                                       | -85   | -300 |     | nA    |

| I <sub>IL</sub>  | Logical "0" Input Current V <sub>II</sub> = VSS      | SCLK, SDI                                                   | -50   | -300 |     | nA    |

|                  | 12                                                   | SEN                                                         | -65   | -75  |     | μΑ    |

| CMOS Digital O   | utput DC Specifications (SDO)                        |                                                             |       |      |     |       |

| $V_{OH}$         | Logical "1" Output Voltage                           | $I_{OUT} = -0.5 \text{mA}$                                  | 1.93  | 1.8  |     | V     |

| $V_{OL}$         | Logical "0" Output Voltage                           | I <sub>OUT</sub> = 1.6mA                                    | 0.05  |      | 0.2 | V     |

| I <sub>OH</sub>  | Output Leakage Current                               | $V_{OUT} = V_{DD}$                                          | 20    |      | 50  | nA    |

| I <sub>OL</sub>  | Output Leakage Current                               | $V_{OUT} = V_{SS}$                                          | -20   | -50  |     | nA    |

| LVDS Clock Re    | ceiver DC Specifications (INCLK+ and INC             | CLK- Pins)                                                  |       |      |     |       |

|                  | Differential LVDS Clock                              | $R_L = 100\Omega$                                           |       |      |     |       |

| $V_{IHL}$        | High Threshold Voltage                               | V <sub>CM</sub> (LVDS Input Common Mode<br>Voltage) = 1.25V | 100   |      | 250 | mV    |

|                  | Differential LVDS Clock                              | RL = 100Ω                                                   |       |      |     |       |

| $V_{ILL}$        | Low Threshold Voltage                                | V <sub>CM</sub> (LVDS Input Common Mode<br>Voltage) = 1.25V | -100  | -250 |     | mV    |

| LVDS Output D    | C Specifications                                     | •                                                           | •     |      | •   |       |

| $V_{OD}$         | Differential Output Voltage                          | LVDS Output Modes =                                         | 275   |      |     | mV    |

| V <sub>OS</sub>  | LVDS Output Offset Voltage                           | $0000 \times 100$<br>$R_L = 100\Omega$                      | 1.19  |      |     | V     |

| $V_{OD}$         | Differential Output Voltage                          | LVDS Output Modes =                                         | 325   |      |     | mV    |

| $V_{OS}$         | LVDS Output Offset Voltage                           | $0000 \text{ x} 101$ $R_L = 100Ω$                           | 1.19  |      |     | V     |

| V <sub>OD</sub>  | Differential Output Voltage                          | LVDS Output Modes =                                         | 377   |      |     | mV    |

| Vos              | LVDS Output Offset Voltage                           | $0000 \text{ x}110$ $R_L = 100Ω$                            | 1.1   |      |     | V     |

| $V_{OD}$         | Differential Output Voltage                          | LVDS Output Modes =                                         | 425   | 350  | 590 | mV    |

| Vos              | LVDS Output Offset Voltage                           | $0000 \text{ x}111$ $R_L = 100Ω$                            | 1.1   | 0.95 | 1.2 | V     |

| I <sub>OH</sub>  | LVDS Output Leakage Current                          |                                                             | 4.25  |      | 5   | μΑ    |

| I <sub>OL</sub>  | LVDS Output Leakage Current                          |                                                             | -4.29 | -5   |     | μA    |

| los              | Output Short Circuit Current                         | $V_{OUT} = 0V$ , $R_L = 100\Omega$                          | 40    |      | 50  | mA    |

| I <sub>IHL</sub> | Diffferential LVDS Clock Input Current               | V <sub>IH</sub> = VDD33                                     | 23    |      | 36  | μA    |

| I <sub>ILL</sub> | Diffferential LVDS Clock Input Current               | V <sub>IL</sub> = VSS                                       | -34   | -49  |     | μA    |

<sup>(1)</sup> The analog inputs are protected as shown below. Input voltage magnitudes beyond the supply rails will not damage the device, provided the current is limited per note 3. However, input errors will be generated If the input goes above VDD33 and below VSS.

(2) Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured.

Submit Documentation Feedback

Copyright © 2012–2013, Texas Instruments Incorporated

The following specifications apply for VDD33 = 3.3V, VDD18 = 1.8V,  $C_L$  = 10 pF, and  $f_{\text{INCLK}}$  = 40 MHz unless otherwise specified. **Boldface limits apply for TA = TMIN to TMAX**; **all other limits TA = 25°C.**

| Symbol        | Parameter                                     | Conditions                                                                                                                             | Typical <sup>(2)</sup> | Min | Max  | Unit       |  |

|---------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|------|------------|--|

| ower Supply S | pecifications                                 |                                                                                                                                        |                        |     |      |            |  |

|               |                                               | Powerdown Control Reg = 0x00 (see Power Trimming section for PGA and ADC Power Trimming register settings)                             |                        |     |      |            |  |

|               |                                               | 5 MHz                                                                                                                                  | 51.5                   |     |      |            |  |

|               |                                               | 15 MHz                                                                                                                                 | 61.3                   |     |      | 1.         |  |

|               |                                               | 25 MHz                                                                                                                                 | 69.6                   |     |      | mA         |  |

|               |                                               | 40 MHz                                                                                                                                 | 87.6                   |     |      |            |  |

|               | VDD33 Analog Supply Current  Dual Channel     | Powerdown Control Reg = 0x00 (see Power Trimming section for PGA and ADC Power Trimming register settings)                             |                        |     |      |            |  |

|               | Power optimized for                           | 5 MHz                                                                                                                                  | 51.5                   |     |      |            |  |

|               | PGA Gain = 1-8x                               | 15 MHz                                                                                                                                 | 61.3                   |     |      | 1          |  |

|               |                                               | 25 MHz                                                                                                                                 | 72.9                   |     |      | m/         |  |

|               |                                               | 40 MHz                                                                                                                                 | 91.3                   |     | 103  |            |  |

| IA            |                                               | Powerdown Control Reg = 0x15 (CH1 PD) or = 0x2A (CH2 PD) (see Power Trimming section for PGA and ADC Power Trimming register settings) |                        |     |      |            |  |

|               |                                               | 5 MHz                                                                                                                                  | 29.5                   |     |      |            |  |

|               |                                               | 15 MHz                                                                                                                                 | 36.1                   |     |      |            |  |

|               |                                               | 25 MHz                                                                                                                                 | 42                     |     |      | m/         |  |

|               |                                               | 40 MHz                                                                                                                                 | 53.7                   |     |      |            |  |

|               | VDD33 Analog Supply Current Single Channel    | Powerdown Control Reg = 0x15 (CH1 PD) or = 0x2A (CH2 PD) (see Power Trimming section for PGA and ADC Power Trimming register settings) |                        |     |      |            |  |

|               | Power optimized for                           | 5 MHz                                                                                                                                  | 29.5                   |     |      |            |  |

|               | PGA Gain = 1-8x                               | 15 MHz                                                                                                                                 | 36.1                   |     |      | 1          |  |

|               |                                               | 25 MHz                                                                                                                                 | 43.8                   |     |      | m/         |  |

|               |                                               | 40 MHz                                                                                                                                 | 55.6                   |     | 64   |            |  |

|               | VDD33 Analog Supply Current<br>Powerdown      | Powerdown Control Reg<br>= 0x80                                                                                                        | 2.85                   |     | 3.85 | m/         |  |

|               | VDD18 Digital Supply Current                  | 5 MHz                                                                                                                                  | 36                     |     |      |            |  |

|               | LVDS Quad Lane Mode                           | 15 MHz                                                                                                                                 | 39                     |     |      | m/         |  |

|               | LVDS Output Mode Reg<br>= 0x0E                | 25 MHz                                                                                                                                 | 42                     |     |      |            |  |

|               | - 0,01                                        | 40 MHz                                                                                                                                 | 45                     |     |      |            |  |

| ID            |                                               | 5 MHz                                                                                                                                  | 23.5                   |     |      |            |  |

|               | VDD18 Digital Supply Current                  | 15 MHz                                                                                                                                 | 25.5                   |     |      | mA         |  |

|               | VDD TO Digital Supply Surrellt                | 25 MHz                                                                                                                                 | 27.5                   |     |      | 111/       |  |

|               |                                               | 40 MHz                                                                                                                                 | 30.5                   |     | 37   |            |  |

|               | VDD18 Digital Supply Current <b>Powerdown</b> | Powerdown Control<br>Reg = 0x80                                                                                                        | 1.2                    |     | 3.0  | m <i>A</i> |  |

The following specifications apply for VDD33 = 3.3V, VDD18 = 1.8V,  $C_L$  = 10 pF, and  $f_{\text{INCLK}}$  = 40 MHz unless otherwise specified. **Boldface limits apply for TA = TMIN to TMAX**; **all other limits TA = 25°C.**

| Symbol             | Parameter                                                  | Conditions                  | Typical <sup>(2)</sup> | Min | Max | Units  |

|--------------------|------------------------------------------------------------|-----------------------------|------------------------|-----|-----|--------|

|                    | Average Power Dissipation                                  | 5 MHz                       | 212                    |     |     |        |

|                    | Power optimized for                                        | 15 MHz                      | 250                    |     |     | \^/    |

|                    | PGA Gain = 1-4x<br>Dual Channel                            | 25 MHz                      | 280                    |     |     | mW     |

| DWD                | LVDS Dual Lane Mode                                        | 40 MHz                      | 345                    |     | 390 |        |

| PWR                | Average Power Dissipation                                  | 5 MHz                       | 212                    |     |     |        |

|                    | Power optimized for                                        | 15 MHz                      | 250                    |     |     | ,      |

|                    | PGA Gain = 1-8x<br>Dual Channel                            | 25 MHz                      | 290                    |     |     | mW     |

|                    | LVDS Dual Lane Mode                                        | 40MHz                       | 356                    |     | 407 |        |

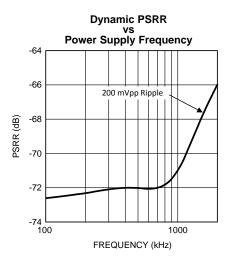

|                    |                                                            | 200 mVpp, 200 KHz           | -72.3                  |     |     |        |

|                    | Dynamic Power Supply Rejection Ratio                       | 200 mVpp, 500 KHz           | -72                    |     |     |        |

| PSRR               | CDS Gain = 1x                                              | 200 mVpp, 1 MHz             | -71                    |     |     | dB     |

|                    | PGA Gain = 1x <sup>(3)</sup>                               | 200 mVpp, 1.5 MHz           | -68                    |     |     |        |

|                    |                                                            | 200 mVpp, 2 MHz             | -66                    |     |     |        |

| ernal Referen      | nce Specifications                                         |                             |                        |     | 1   |        |

| V <sub>REFBG</sub> | Reference Voltage                                          | See <sup>(4)</sup>          | 1.218                  |     |     | V      |

|                    | Reference Tolerance<br>(chip to chip)                      | See <sup>(5)</sup>          | ±2                     |     |     | %      |

| R <sub>REFBG</sub> | Reference Impedance                                        | See <sup>(5)</sup>          | 20                     |     |     | kΩ     |

|                    |                                                            | 25°C to 125°C               | 80                     |     |     |        |

| $V_{REFTC}$        | Temperature Coefficient                                    | -55°C to 25°C               | 50                     |     |     | ppm/°C |

| ut Sampling        | Circuit Specifications                                     |                             |                        |     |     |        |

|                    |                                                            | CDS Gain=1x, PGA Gain=1x    |                        |     | 2   |        |

| $V_{IN}$           | Input Voltage Level                                        | CDS Gain=2x, PGA Gain=1x    |                        | 1   |     | Vp-p   |

|                    |                                                            | CDS Gain=1x, PGA Gain=0.7x  | 2.85                   |     |     |        |

| V <sub>RESET</sub> | Reset Feed Through                                         | •                           | 500                    |     |     | mV     |

| 112021             |                                                            | CDS Gain = 1x               |                        |     |     |        |

|                    | Sample and Hold Mode                                       | $OS_X = VDD33 (OS_X = VSS)$ | 384                    |     |     | μA     |

| $I_{IN\_SH}$       | Input Leakage Current <sup>(5)</sup>                       | CDS Gain = 2x               |                        |     |     |        |

|                    |                                                            | $OS_x = VDD33 (OS_x = VSS)$ | -475                   |     |     | μA     |

|                    | Sample/Hold Mode                                           | X                           |                        |     |     |        |

| $C_SH$             | Equivalent Input Capacitance                               | CDS Gain = 1x               | 4                      |     |     | pF     |

| - 011              | (see Figure 22) <sup>(5)</sup>                             | CDS Gain = 2x               | 8                      |     |     | pF     |

|                    | CDS Mode                                                   |                             |                        |     |     |        |

| $I_{IN\_CDS}$      | Input Leakage Current <sup>(5)</sup>                       | $OS_X = VDD33 (OS_X = VSS)$ | 300                    |     | 1   | nA     |

|                    | CLPIN Switch Resistance                                    |                             |                        |     |     | 1      |

| $R_{CLPIN}$        | (OS <sub>X</sub> to VCLP Node in Figure 19) <sup>(5)</sup> |                             | 16                     |     | 1   | Ω      |

|                    | (30 <sub>A</sub> 13 13 <u>-</u> 1 11343 1111 19413 10)     |                             |                        |     |     |        |

<sup>(3)</sup> Dynamic Power Supply Rejection Ratio is performed by injecting a 200 mVpp sine wave ac coupled to the analog supply pin. The LM98640's inputs are left floating in CDS mode and an FFT is captured. The spur specified by the injected signal is recorded.

(4) This Parameter is specified by design and/or characterization and is not tested.

Product Folder Links: LM98640

This Parameter is specified by design and/or characterization and is not tested.

The following specifications apply for VDD33 = 3.3V, VDD18 = 1.8V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 40 MHz unless otherwise specified. **Boldface limits apply for TA = TMIN to TMAX**; **all other limits TA = 25°C.**

| Symbol          | Parameter                             | Conditions                 | Typical <sup>(2)</sup> | Min   | Max  | Units |

|-----------------|---------------------------------------|----------------------------|------------------------|-------|------|-------|

| VCLP Referenc   | e Circuit Specification               |                            |                        |       |      |       |

|                 | VCLP DAC Resolution                   |                            | 5                      | 5     |      | Bits  |

|                 | VCLP DAC Step Size                    |                            | 98                     | 96    | 102  | mV    |

|                 | VCLD DAC Voltage Min Output           | VCLP Control Register =    | 224                    | 194   | 200  | mV    |

| V               | VCLP DAC Voltage Min Output           | 0110 0000                  | 224                    | 194   | 298  | mv    |

| $V_{VCLP}$      | VCLP DAC Voltage Max Output           | VCLP Control Register =    | 3.07                   | 2.99  | 3.11 | V     |

|                 | VCLF DAC Voltage Max Output           | 0111 1101                  | 3.07                   | 2.99  | 3.11 | V     |

| I <sub>SC</sub> | VCLP DAC Short Circuit Output Current | VCLP Control Register =    | 33                     |       |      | mA    |

| isc             | VOLI DAG SHOR GIRCUIT GUIPUT GUITEIR  | 011x xxxx                  | 33                     |       |      | ША    |

| Coarse Analog   | Offset DAC Specifications             |                            |                        |       |      |       |

|                 | Resolution                            |                            | ±8                     |       |      | Bits  |

|                 | Offset Adjustment Range Referred to   | Minimum DAC Code = 0x000   | -262                   |       |      |       |

|                 | AFE Input<br>CDS Gain = 1x            | Maximum DAC Code = 0x1FF   | 263                    |       |      | mV    |

|                 | Offset Adjustment Range Referred to   | Minimum DAC Code = 0x000   | -131                   |       |      |       |

|                 | AFE Input<br>CDS Gain = 2x            | Maximum DAC Code = 0x1FF   | 131                    |       |      | mV    |

|                 | Offset Adjustment Range               | Minimum DAC Code = 0x000   | -2146                  | -2146 |      |       |

|                 | Referred to AFE Output                | Maximum DAC Code = 0x1FF   | 2154                   |       |      | LSB   |

|                 | DAC Step Size<br>CDS Gain = 1x        | Input Referred             | 1                      |       |      | mV    |

|                 | DAC Step Size<br>CDS Gain = 1x        | Output Referred            | 8                      |       |      | LSB   |

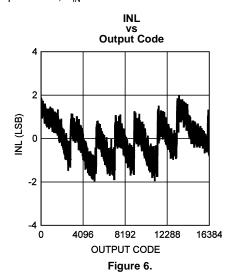

| DNL             | Differential Non-Linearity            | CDS Gain = 1x or 2x 40 MHz | ±0.97                  |       |      | LSB   |

| INL             | Integral Non-Linearity                | CDS Gain = 1x or 2x 40 MHz | ±1.5                   |       |      | LSB   |

| ine Analog Of   | fset DAC Specifications               |                            |                        |       |      |       |

|                 | Resolution                            |                            | ±8                     |       |      | Bits  |

|                 | Offset Adjustment Range Referred to   | Minimum DAC Code = 0x000   | -4.6                   |       |      |       |

|                 | AFE Input<br>CDS Gain = 1x            | Maximum DAC Code = 0x1FF   | 5.3                    |       |      | mV    |

|                 | Offset Adjustment Range Referred to   | Minimum DAC Code = 0x000   | -2.3                   |       |      |       |

|                 | AFE Input<br>CDS Gain = 2x            | Maximum DAC Code = 0x1FF   | 2.6                    |       |      | mV    |

|                 | Offset Adjustment Range               | Minimum DAC Code = 0x000   | -38                    |       |      |       |

|                 | Referred to AFE Output                | Maximum DAC Code = 0x1FF   | 43                     |       |      | LSB   |

|                 | DAC Step Size<br>CDS Gain = 1x        | Input Referred             | 20                     |       |      | uV    |

|                 | DAC Step Size<br>CDS Gain = 1x        | Output Referred            | 0.16                   |       |      | LSB   |

| DNL             | Differential Non-Linearity            |                            | ±1                     |       |      | LSB   |

| INL             | Integral Non-Linearity                |                            | ±2.2                   |       |      | LSB   |

The following specifications apply for VDD33 = 3.3V, VDD18 = 1.8V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 40 MHz unless otherwise specified. **Boldface limits apply for TA = TMIN to TMAX**; **all other limits TA = 25°C.**

| Symbol                                | Parameter                      | Conditions         | Typical <sup>(2)</sup> | Min                | Max   | Units |

|---------------------------------------|--------------------------------|--------------------|------------------------|--------------------|-------|-------|

| PGA Specifications                    | 5                              |                    | <u> </u>               | 1                  | II.   |       |

|                                       | Gain Resolution                |                    |                        |                    | 8     | Bits  |

|                                       | Monotonicity                   | See <sup>(6)</sup> |                        |                    |       |       |

|                                       | Mariana Osia                   | CDS Gain = 1x      | 8.3                    | 7.92               |       | V/V   |

|                                       | Maximum Gain                   | CDS Gain = 1x      | 18.4                   | 17.99              |       | dB    |

|                                       | Minimum Coin                   | CDS Gain = 1x      | 0.64                   |                    | .7    | V/V   |

|                                       | Minimum Gain                   | CDS Gain = 1x      | -3.8                   |                    | -3.10 | dB    |

|                                       | PGA Function                   | Gain (V/V) =       | : (180/(277-PGA        | 80/(277-PGA Code)) |       |       |

|                                       | PGA FUNCTION                   | Gain (dB) = 20L0   | OG10(180/(277-         | PGA Code           | e))   |       |

|                                       | Channel Matching               | Minimum PGA Gain   | 99.0                   | 95.2               |       | %     |

|                                       | Charmer Matching               | Maximum PGA Gain   | 99.0                   | 95.2               |       | %     |

| ADC Specifications                    | 5                              |                    |                        |                    |       |       |

| $V_{REFT}$                            | Top of Reference               |                    | 2.0                    |                    |       | V     |

| $V_{REFB}$                            | Bottom of Reference            |                    | 1.0                    |                    |       | V     |

| V <sub>REFT</sub> - V <sub>REFB</sub> | Differential Reference Voltage |                    | 1.0                    |                    |       | V     |

|                                       | Overrange Output Code          |                    | 16383                  | 16383              |       | Code  |

|                                       | Underrange Output Code         |                    | 0                      |                    | 0     | Code  |

| Full Channel Perfo                    | rmance Specifications          |                    |                        |                    |       |       |

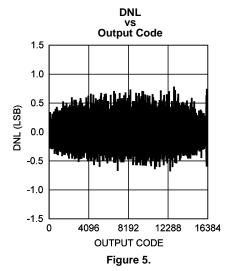

|                                       |                                | 5 MHz              | 0.78                   | -1.03              | 1.53  |       |

|                                       |                                | 5 MHz CDS          | 1.0                    |                    |       |       |

| DNL                                   | Differential Non-Linearity     | 15 MHz             | 0.78                   |                    |       | LSB   |

|                                       |                                | 25 MHz             | 0.78                   |                    |       |       |

|                                       |                                | 40 MHz             | 0.78                   |                    |       |       |

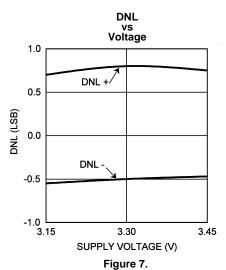

|                                       |                                | 5 MHz              | 1.7                    | -5.38              | 4.38  |       |

|                                       |                                | 5 MHz CDS          | 1.7                    |                    |       |       |

| INL                                   | Integral Non-Linearity         | 15 MHz             | 1.9                    |                    |       | LSB   |

|                                       |                                | 25 MHz             | 2.4                    |                    |       |       |

|                                       |                                | 40 MHz             | 6.0                    |                    |       |       |

|                                       |                                | 5 MHz              | -66.0                  |                    |       | dB    |

|                                       | Noise Floor CDS Gain = 1x      | 15 MHz             | -66.0                  |                    |       | dB    |

|                                       | PGA Gain = FE                  | 25 MHz             | -66.0                  |                    |       | dB    |

|                                       |                                | 40 MHz             | -66.0                  |                    |       | dB    |

|                                       | _                              | 5 MHz              | 8.20                   |                    |       | LSB   |

|                                       | Noise Floor CDS Gain = 1x      | 15 MHz             | 8.20                   |                    |       | LSB   |

|                                       | PGA Gain = FE                  | 25 MHz             | 8.20                   |                    |       | LSB   |

| Noise                                 |                                | 40 MHz             | 8.20                   |                    |       | LSB   |

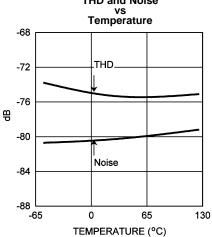

|                                       |                                | 5 MHz              | -79                    |                    |       | dB    |

|                                       | Noise Floor CDS Gain = 1x      | 15 MHz             | -79                    |                    |       | dB    |

|                                       | PGA Gain = 61                  | 25 MHz             | -79                    |                    |       | dB    |

| _                                     |                                | 40 MHz             | -79                    |                    |       | dB    |

|                                       |                                | 5 MHz              | 1.8                    |                    |       | LSB   |

|                                       | Noise Floor CDS Gain = 1x      | 15 MHz             | 1.8                    |                    |       | LSB   |

|                                       | PGA Gain = 61                  | 25 MHz             | 1.8                    |                    |       | LSB   |

|                                       |                                | 40 MHz             | 1.8                    |                    |       | LSB   |

<sup>(6)</sup> This Parameter is specified by design and/or characterization and is not tested.

The following specifications apply for VDD33 = 3.3V, VDD18 = 1.8V,  $C_L$  = 10 pF, and  $f_{\text{INCLK}}$  = 40 MHz unless otherwise specified. **Boldface limits apply for TA = TMIN to TMAX**; **all other limits TA = 25°C.**

| Symbol | Parameter                             | Conditions | Typical <sup>(2)</sup> | Min | Max | Units |

|--------|---------------------------------------|------------|------------------------|-----|-----|-------|

|        |                                       | 5 MHz      | -79                    |     |     |       |

|        | Channel to Channel Creatally          | 15 MHz     | -86                    |     |     | 40    |

|        | Channel to Channel Crosstalk          | 25 MHz     | -79                    |     |     | dB    |

|        |                                       | 40 MHz     | -76                    |     |     |       |

|        |                                       | 5 MHz      | 2.2                    |     |     |       |

|        | CDS Mode Bimodal Offset               | 15 MHz     | 2.1                    |     |     | \/    |

|        | CDS Gain = 1x<br>PGA Gain = 8x        | 25 MHz     | 2.2                    |     |     | mV    |

| DMD    |                                       | 40 MHz     | 2.3                    |     |     |       |

| BMD    |                                       | 5 MHz      | 0.35                   |     |     |       |

|        | CDS Mode Bimodal Offset               | 15 MHz     | 0.29                   |     |     | \     |

|        | CDS Gain = 1x PGA Gain = 1x           | 25 MHz     | 0.33                   |     |     | mV    |

|        |                                       | 40 MHz     | 0.4                    |     |     | 1     |

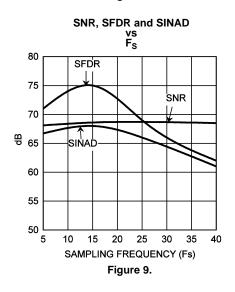

|        |                                       | 5 MHz      | 67.4                   |     |     | dB    |

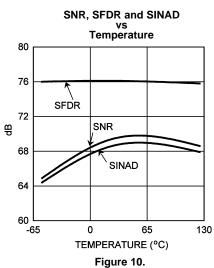

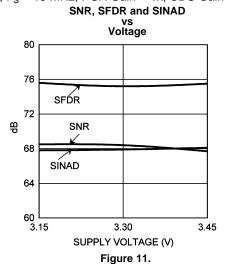

| OND    | O'mark to Naire Batis                 | 15 MHz     | 68.0                   |     |     | dB    |

| SNR    | Signal-to-Noise Ratio                 | 25 MHz     | 68.5                   |     |     | dB    |

|        |                                       | 40 MHz     | 68.5                   |     |     | dB    |

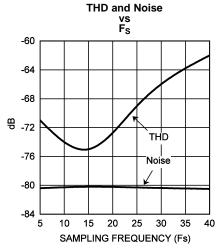

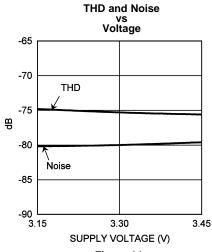

|        |                                       | 5 MHz      | -71.4                  |     |     | dB    |

| TUD    | Total Hanna and Distortion            | 15 MHz     | -75.1                  |     |     | dB    |

| THD    | Total Harmonic Distortion             | 25 MHz     | -68.9                  |     |     | dB    |

|        |                                       | 40 MHz     | -62.0                  |     |     | dB    |

|        |                                       | 5 MHz      | 71.5                   |     |     | dB    |

| 0500   |                                       | 15 MHz     | 76.0                   |     |     | dB    |

| SFDR   | Spurious-Free Dynamic Range           | 25 MHz     | 69.0                   |     |     | dB    |

|        |                                       | 40 MHz     | 62.0                   |     |     | dB    |

|        |                                       | 5 MHz      | 67.0                   |     |     | dB    |

| 011115 |                                       | 15 MHz     | 68.0                   |     |     | dB    |

| SINAD  | Signal-to-Noise Plus Distortion Ratio | 25 MHz     | 66.0                   |     |     | dB    |

|        |                                       | 40 MHz     | 61.0                   |     |     | dB    |

|        |                                       | 5 MHz      | 10.8                   |     |     | Bits  |

| ENIOD  | F″ " N 1 (5)                          | 15 MHz     | 11.0                   |     |     | Bits  |

| ENOB   | Effective Number of Bits              | 25 MHz     | 10.7                   |     |     | Bits  |

|        |                                       | 40 MHz     | 9.8                    |     |     | Bits  |

## **AC Timing Specifications**

The following specifications apply for VDD33 = 3.3V, VDD18 = 1.8V,  $C_L$  = 10pF, and  $f_{\text{INCLK}}$  = 15 MHz unless otherwise specified. Boldface limits apply for  $T_A$  =  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$ ; all other limits  $T_A$  = 25°C.

| Symbol             | Parameter                            | Conditions                                                        | Typical <sup>(1)</sup> | Min   | Max   | Units             |

|--------------------|--------------------------------------|-------------------------------------------------------------------|------------------------|-------|-------|-------------------|

| Input Clock Tim    | ing Specifications                   |                                                                   |                        |       |       |                   |

|                    |                                      | INCLK = ADCCLK                                                    |                        | _     | 40    |                   |

| fINCLK             | Input Clock Frequency                | (ADC Rate Clock)                                                  |                        | 5     | 40    | MHz               |

| T <sub>dc</sub>    | Input Clock Duty Cycle               |                                                                   | 50/50                  | 40/60 | 60/40 | %                 |

| Full Channel La    | tency Specifications                 |                                                                   |                        |       | •     | •                 |

| t <sub>LAT</sub>   | Pipeline Latency                     | See <sup>(2)</sup>                                                |                        |       | 10    | T <sub>ADC</sub>  |

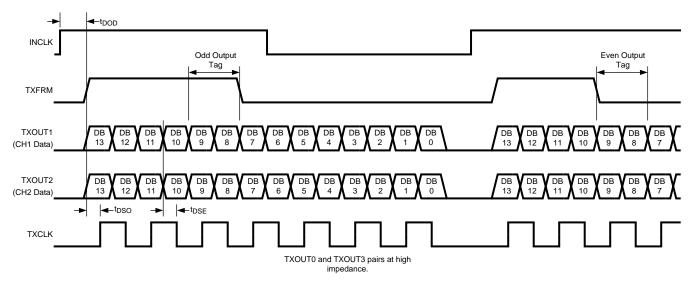

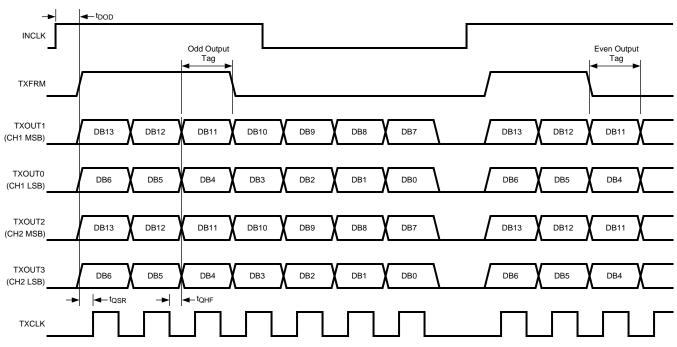

| LVDS Output Ti     | ming Specifications                  |                                                                   |                        |       |       |                   |

| t <sub>DOD</sub>   | Data Output Delay                    | f <sub>INCLK</sub> = 40 MHz                                       | 6.44                   |       |       | ns                |

|                    | Dual Lane Mode                       | INCLK = ADCCLK (ADC Rate Clock)                                   | 0.00                   |       |       |                   |

| t <sub>DSO</sub>   | Odd Data Setup                       | LVDS Output Specifications not                                    | 0.69                   |       |       | ns                |

|                    | Dual Lane Mode                       | tested in production. Min/Max ensured by design, characterization | 0.00                   |       |       |                   |

| t <sub>DSE</sub>   |                                      | and statistical analysis.                                         | 0.89                   |       |       | ns                |

|                    | Quad Lane Mode                       |                                                                   | 0.00                   |       |       |                   |

| t <sub>QSR</sub>   | Data to Rising Clock Setup           | 0.63                                                              |                        |       | ns    |                   |

|                    | Quad Lane Mode                       |                                                                   | 0.53                   |       |       |                   |

| t <sub>QHF</sub>   | Falling Clock to Data Hold           |                                                                   | 0.53                   |       |       | ns                |

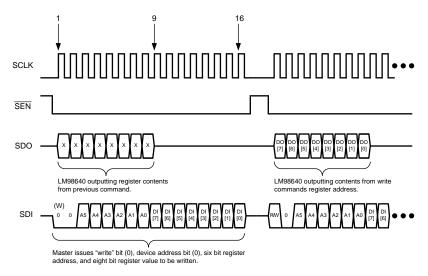

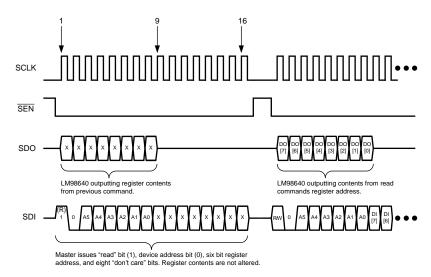

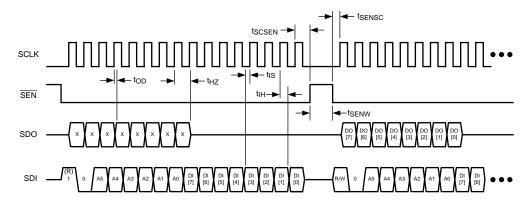

| Serial Interface   | Timing Specifications                |                                                                   |                        |       |       |                   |

|                    |                                      | f <sub>SCLK</sub> <= f <sub>INCLK</sub>                           |                        |       |       |                   |

| f <sub>SCLK</sub>  | Input Clock Frequency                | INCLK = ADCCLK                                                    |                        | 1     | 20    | MHz               |

|                    |                                      | (ADC Rate Clock)                                                  |                        |       |       |                   |

|                    | SCLK Duty Cycle                      |                                                                   | 50/50                  | 40/60 | 60/40 | ns                |

| t <sub>IH</sub>    | Input Hold Time                      |                                                                   | 1                      | 2.5   |       | ns                |

| t <sub>IS</sub>    | Input Setup Time                     |                                                                   | 1                      | 2.5   |       | ns                |

| t <sub>SENSC</sub> | SCLK Start Time After SEN Low        |                                                                   | 1                      | 1.5   |       | ns                |

| t <sub>SCSEN</sub> | SEN High after last SCLK Rising Edge |                                                                   | 2                      | 2.5   |       | ns                |

| t <sub>SENW</sub>  | SEN Pulse Width                      |                                                                   | 6                      | 8     |       | ns                |

| t <sub>OD</sub>    | Output Delay Time                    |                                                                   | 10.54                  |       | 11.6  | ns                |

| t <sub>HZ</sub>    | Data Output to High Z                |                                                                   | 1.2                    |       | 1.23  | T <sub>SCLK</sub> |

Typical figures are at  $T_A = 25$ °C, and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured.

This Parameter is specified by design and/or characterization and is not tested.

# **Typical Performance Characteristics**

$T_A = 25$ °C,  $F_S = 15$  MHz, PGA Gain = 1x, CDS Gain = 1x, Dual Lane Output Mode,  $F_{IN} = 7.48$  MHz unless otherwise stated.

## **Typical Performance Characteristics (continued)**

$T_A = 25$ °C,  $F_S = 15$  MHz, PGA Gain = 1x, CDS Gain = 1x, Dual Lane Output Mode,  $F_{IN} = 7.48$  MHz unless otherwise stated.

Figure 13.

Figure 12.

Figure 14.

Figure 16.

#### SYSTEM OVERVIEW

#### Introduction

The LM98640 is a 14-bit, 5 MSPS to 40 MSPS, dual channel, complete Analog Front End (AFE) for digital imaging applications. The system block diagram of the LM98640, shown in Figure 4 highlights the main features of the device. Each input has its own Input Bias and Clamping Network and Correlated Double Sample (CDS) amplifier (which can also be configure to operate in Sample/Hold Mode). Two ±8-Bit Offset DACs apply independent coarse and fine offset correction for each channel. A -3 to 18 dB Programmable Gain Amplifier (PGA) applies independent gain correction for each channel. The signals are digitized using two independent on chip high performance 14-bit, 40 MHz analog-to-digital converters. The data is finally output using a unique Serial LVDS output format that prevents data loss during any ionizing doses.

## **Input Sampling Modes**

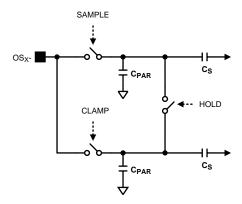

The LM98640 provides two input sampling modes: Sample & Hold mode and Correlated Double Sample (CDS) mode. The following sections describe these two input sampling modes.

#### Sample & Hold Mode

In Sample/Hold mode, a Video Level signal and a Reference Level signal need to be presented to the LM98640. The Reference Level signal must be connected to the  $OS_{X^+}$  pin, and the Video Level signal connected to the  $OS_{X^-}$  pin. The output code will then be  $OS_{X^+}$  minus  $OS_{X^-}$ , or the difference between the Reference Level and Video Level. A minimum code represents zero deviation between the Reference and Video Levels with CDS and PGA gains of 1x.

The Reference Level signal can be either an external signal from the image sensor, or the VCLP pin can be externally connected to the  $OS_X$ + pin. In order to fully utilize the range of the input circuitry it is desirable to cause the Black Level signal voltage to be as close to the Reference Level voltage as possible, resulting in a near zero scale output for Black Level pixels. The LM98640 provides several methods for ensuring the Black Level signal and Reference Level are matched, these are described in the Input Bias and Clamping section.

To place the LM98640 in Sample & Hold Mode from power up, first write the baseline configuration to the registers as shown in the Table 5 section. This configuration has Sample & Hold mode enabled by default. Next, the SAMPLE pulse must be properly positioned over the input signal using the CLAMP/SAMPLE Adjust.

#### Sample & Hold Mode Clamp/Sample Adjust

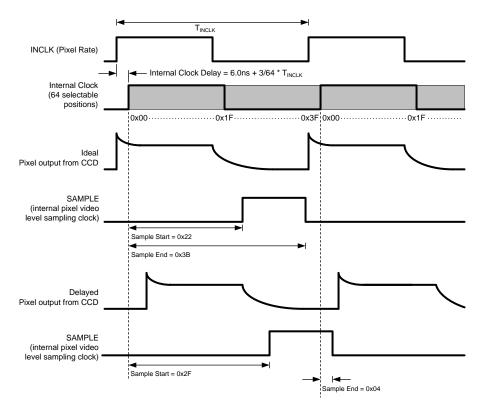

For accurate sampling of the input signals the LM98640 allows for full adjustment of the internal SAMPLE pulse to align it to the proper positions over the input signal. In Sample & Hold mode the SAMPLE pulse should be placed over the pixel output period of the image sensor. Only the Sample Start and Sample End Registers (0x22,0x23) need to be configured, the Clamp Start and Clamp End Registers (0x20,0x21) are not valid in Sample & Hold Mode. Internally the input clock is divided into 64 edges per clock period, the Sample Start and Sample End Registers correspond to the internal edge number the SAMPLE pulse will start and end. To adjust the SAMPLE pulse, first send the CLAMP and SAMPLE signals to the DTM pins by writing 10 to bits[4:3] of the Clock Monitor Register (0x09). This will allow the user to observe the SAMPLE pulse on pin DTM1 along with the image sensor output using an oscilloscope. Then, using the Sample Start and End Registers, adjust the SAMPLE pulse to align it over the Video Level portion of the image sensor output. To allow for settling and to reduce noise, the SAMPLE pulse should be made as wide as possible and fill the entire Video Level portion of the input signal.

Figure 17 shows some examples of an input waveform and where the SAMPLE pulse should be placed. Ideally the image sensor output would line up directly with the input clock at the AFE inputs, but due to trace delays in the system the image sensor output is delayed relative to the input clock. In the delayed image sensor waveform the Sample Start value is higher than the Sample End value. In this situation the SAMPLE pulse will start in one clock period and wraps around to the next. This allows the LM98640 to adjust for the delay in the image sensor waveform. Notice that edge zero of the internal clock does not line up with the rising edge of the input clock. This is due to internal delays of the clock signals. The amount of delay can be calculated from operating frequency using the following formula:  $t_{DCLK} = 6.0 \text{ ns} + 3/64 * T_{INCLK}$

Figure 17. S/H Mode CLAMP/SAMPLE Adjust

#### **CDS Mode**

In CDS mode, both the Reference Level and Video Level are presented to the LM98640 on the  $OS_{\chi^-}$  pin. The  $OS_{\chi^+}$  pin should be bypassed to ground with a 0.1  $\mu$ F capacitor. The CLAMP pulse is then used to sample the Reference Level and the SAMPLE pulse is used to sample the Video Level. The output code will then be the Reference Level minus the Video Level, or the difference between the Reference Level and Video Level. A minimum code represents zero deviation between the Reference and Video Levels and a maximum code represents a 2V deviation between the Reference and Video Levels with CDS and PGA gains of 1x.

To place the LM98640 in CDS Mode from power up, first write the baseline configuration to the registers as shown in the Table 5 Section. Then ensure S/H mode is disabled by clearing bit[7] of the Sample & Hold Register (0x06), then enable CDS mode by setting bit[0] of the Main Configuration Register (0x00). Next the CLAMP and SAMPLE pulses need to be positioned correctly over the reference and video levels respectively using the CLAMP/SAMPLE Adjust.

#### CDS Mode Bimodal Offset

In CDS mode, the input sampling amplifier has two physical paths through which a particular pixel will be sampled. These two sampling paths are a requirement in the Correlated Double Sampling architecture. The sampling of the one pixel will travel the first path (arbritrarily called an even pixel), and the sampling of the next pixel will travel the second path (called an odd pixel). The sampling will continue in an even/odd/even/odd fashion for all pixels processed in a particular channel. Due to slight variances in the sampling paths (most commonly a difference in switched capacitor matching), the processing of identical pixels through the two different paths may result in a small offset in ADC output data between the two paths. To correct this, a simple digital offset can be applied in post processing to either the even pixel data or the odd pixel data. To simplify this action, the LM98640 will indicate (with the TXFRM signal) whether the pixel traveled the even path or the odd path. For all "Odd" pixels, the TXFRM signal is high for three TXCLK periods. For "Even" pixels, the TXFRM signal is high for two TXCLK periods. In Sample and Hold Mode there is only one sampling path, therefore there is no need to indicate an even or odd pixel. As a result, the TXFRM signal is the same for every pixel in Sample and Hold mode (i.e. high for three TXCLK periods).

Product Folder Links: LM98640

18

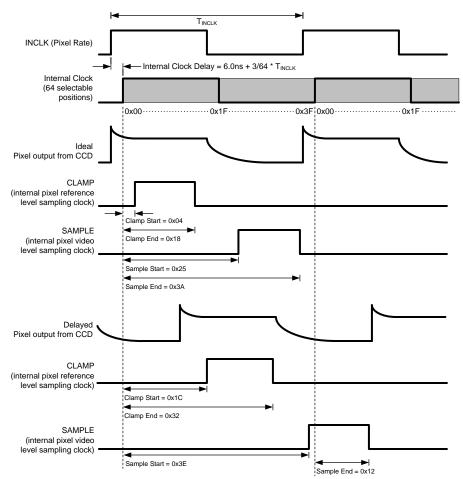

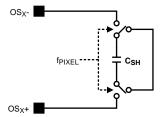

#### CDS Mode CLAMP/SAMPLE Adjust

In CDS mode, the LM98640 utilizes two input networks, alternating between them every pixel, to increase throughput speeds. Because of this, there are two sets of CLAMP and SAMPLE pulses in Figure 18, one for even pixels and one for odd. Sample Start and Sample End Registers (0x22,0x23) along with the Clamp Start and Clamp End Registers (0x20,0x21) control both the even and odd CLAMP and SAMPLE pulses. To adjust the CLAMP and SAMPLE pulses, first send the CLAMP<sub>ODD</sub> and SAMPLE<sub>ODD</sub> signals to the DTM pins by writing 10 to bits[4:3] of the Clock Monitor Register (0x09). This will allow the user to observe the CLAMP<sub>ODD</sub> and SAMPLE<sub>ODD</sub> pulses on pins DTM0 and DTM1 along with the image sensor output using an oscilloscope. The CLAMP and SAMPLE pulses will only be shown for every other pixel because of the even odd architecture, but the positions of the even CLAMP and SAMPLE pulses will be identical to that of the odd CLAMP and SAMPLE. Then, using the Clamp Start/End and Sample Start/End registers, adjust the positions of the CLAMP and SAMPLE pulses to align them over the Reference and Video Levels of the input signal. To allow for settling and to reduce noise, the CLAMP and SAMPLE pulses should be made as wide as possible and placed near the far edge of their respective input levels.

The following figure shows some examples of input CCD waveforms and placement of the CLAMP and SAMPLE positions for each. Ideally the CCD output would line up directly with the input clock at the AFE inputs, but due to trace delays in the system the CCD output is delayed relative to the input clock. In the Delayed CCD waveform the Sample Start/End Register values are lower than the Clamp Start/End Register Values. In this situation the sample pulse is not generated until the next clock period, which allows it to be correctly placed in the Video Level of the input signal. Notice that edge zero of the internal clock does not line up with the rising edge of the input clock. This is due to internal delays of the clock signals. The amount of delay can be calculated from operating frequency using the following formula:  $t_{DCLK} = 6.0 \text{ ns} + 3/64 * T_{INCLK}$

Figure 18. CDS Mode CLAMP/SAMPLE Adjust

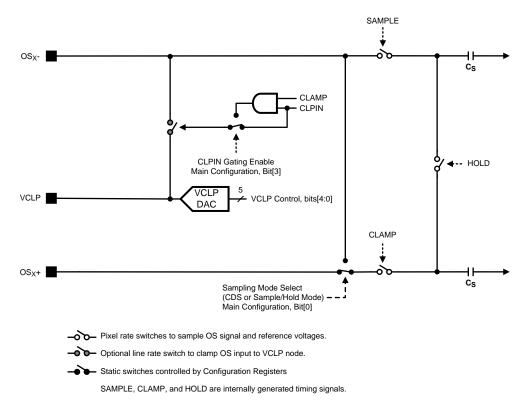

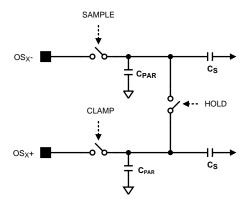

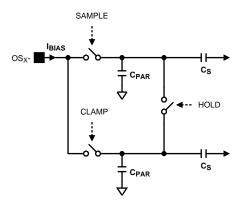

## Input Bias and Clamping

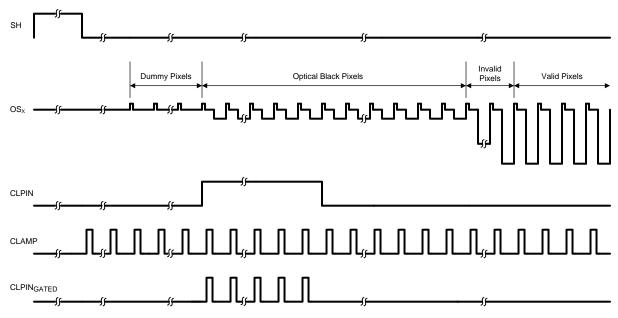

The inputs to the LM98640 are typically AC coupled and can be sampled in either Sample and Hold Mode (S/H Mode) or Correlated Double Sampling Mode (CDS Mode). The circuit of Figure 19 shows the input structure of the LM98640. The DC bias point for the LM98640 side of the AC coupling capacitor can to be set using an external DC bias resistor network, by using the CLPIN configuration, or by using the BITCLP configuration. A typical CCD waveform is shown in Figure 20. Also shown in Figure 20 is an internal signal "CLAMP" which can be used to "gate" the CLPIN signal so that it only occurs during the "pedestal" portion of the CCD pixel waveform.

Figure 19. Input Structure Diagram

Figure 20. Typical CCD Waveform and LM98640 Input Clamp Signal (CLPIN)

#### Sample and Hold Mode Biasing