July 2011

# FAN3850A Microphone Pre-Amplifier with Digital Output

#### **Features**

- Optimized for Mobile Handset and Notebook PC Microphone Applications

- Accepts Input from Electret Condenser Microphones (ECM)

- Pulse Density Modulation (PDM) Output

- Standard 5-Wire Digital Interface

- 16dB and 19dB Gain Versions Available<sup>(1)</sup>

- Low Input Capacitance, High PSR, 20kHz Pre-Amplifier

- Low-Power 1.5µA Sleep Mode

- Typical 470µA Supply Current

- SNR of 62/61dB(A) for 16/19dB Gain Respectively

- Total Harmonic Distortion 0.02%

- Input Clock Frequency Range of 1-4MHz

- Integrated Low Drop-Out Regulator (LDO)

- Small 1.26mm x 0.86mm 6-Ball WLCSP Package

#### Description

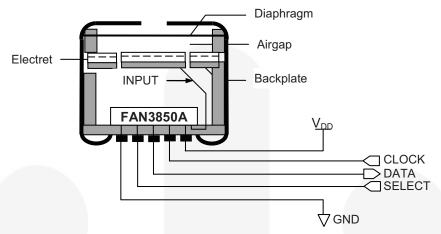

The FAN3850A integrates a pre-amplifier, LDO, and ADC that converts Electret Condenser Microphone (ECM) outputs to digital Pulse Density Modulation (PDM) data streams. The pre-amplifier accepts analog signals from the ECM and drives an over-sampled sigma delta Analog-to-Digital Converter (ADC) and outputs PDM data. The PDM digital audio has the advantage of noise rejection and easy interface to mobile handset processors.

The FAN3850A features an integrated LDO and is powered from the system supply rails up to 3.63V, with low power consumption of only 0.85mW and less than  $20\mu W$  in Power-Down Mode.

# **Applications**

- Electret Condenser Microphones with Digital Output

- Mobile Handset

- Headset Accessories

- Personal Computer (PC)

# **Ordering Information**

| Part Number   | Operating<br>Temperature<br>Range | Package                                        | Packing<br>Method            |

|---------------|-----------------------------------|------------------------------------------------|------------------------------|

| FAN3850AUC16X | -30°C to +85°C                    | 6 Ball, Wafer-Level Chip-Scale Package (WLCSP) | 3000 Units on<br>Tape & Reel |

| FAN3850AUC19X | -30°C to +85°C                    | 6-Ball, Wafer-Level Chip-Scale Package (WLCSP) | 3000 Units on<br>Tape & Reel |

#### Note:

1. Alternate gain options are possible. Please contact Fairchild.

# Block Diagram VDD Sleep Mode Ctrl Pre-Amp ADC DATA SELECT Figure 1. Block Diagram

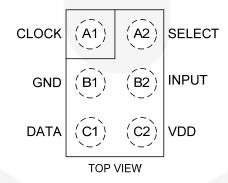

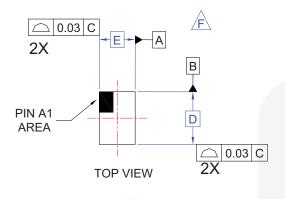

Pin Configuration

Figure 2. Pin Assignments

#### **Pin Definitions**

| Pin# | Name   | Туре   | Description                               |  |

|------|--------|--------|-------------------------------------------|--|

| A1   | CLOCK  | Input  | Clock Input                               |  |

| B1   | GND    | Input  | Ground Pin                                |  |

| C1   | DATA   | Output | PDM Output – 1 Bit ADC                    |  |

| A2   | SELECT | Input  | Input Rising or Falling Clock Edge Select |  |

| B2   | INPUT  | Input  | Microphone Input                          |  |

| C2   | VDD    | Input  | Device Power Pin                          |  |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol          | Parameter                                                       | Min. | Max.                 | Unit |

|-----------------|-----------------------------------------------------------------|------|----------------------|------|

| $V_{DD}$        | DC Supply Voltage                                               | -0.3 | 4.0                  | V    |

| V <sub>IO</sub> | Analog and Digital I/O                                          | -0.3 | V <sub>CC</sub> +0.3 | V    |

| ESD             | Human Body Model, JESD22-A114, All Pins Except Microphone Input | ±7   |                      | kV   |

|                 | Human Body Model, JESD22-A114 – Microphone Input                | ±300 |                      | V    |

#### Note:

This device is fabricated using CMOS technology and is therefore susceptible to damage from electrostatic discharges. Appropriate precautions must be taken during handling and storage of this device to prevent exposure to ESD.

#### **Reliability Information**

| Symbol            | Parameter                                                                | Min. | Тур. | Max. | Unit |

|-------------------|--------------------------------------------------------------------------|------|------|------|------|

| $T_J$             | T <sub>J</sub> Junction Temperature                                      |      |      | +150 | °C   |

| T <sub>STG</sub>  | Storage Temperature Range                                                | -65  |      | +125 | °C   |

| T <sub>RFLW</sub> | Peak Reflow Temperature                                                  |      |      | +260 | °C   |

| $\Theta_{JA}$     | Thermal Resistance, JEDEC Standard,<br>Multilayer Test Boards, Still Air |      | 90   |      | °C/W |

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol              | Parameter                   | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------|------|------|------|------|

| T <sub>A</sub>      | Operating Temperature Range | -30  |      | +85  | °C   |

| $V_{DD}$            | Supply Voltage Range        | 1.64 | 1.80 | 3.63 | V    |

| t <sub>RF-CLK</sub> | Clock Rise and Fall Time    |      |      | 10   | ns   |

## **Device Specific Electrical Characteristics**

Unless otherwise specified, all limits are guaranteed for  $T_A$ =25°C,  $V_{DD}$ =1.8V,  $V_{IN}$ =94dB (SPL), and  $f_{CLK}$ =2.4MHz. Duty Cycle=50% and  $C_{MIC}$ =15pF.

| Symbol          | Parameter                                                         | FAN3850AUC16X |      | FAN3850AUC19X |      |      | Unit |                   |

|-----------------|-------------------------------------------------------------------|---------------|------|---------------|------|------|------|-------------------|

| Symbol          | Tibol Farameter                                                   |               | Тур. | Max.          | Min. | Тур. | Max. | Unit              |

| SNR             | Signal-to-Noise Ratio f <sub>IN</sub> =1kHz (1Pa), A-Weighted     |               | 62   |               |      | 61   |      | dB(A)             |

| e <sub>N</sub>  | Total Input RMS Noise <sup>(4)</sup><br>20Hz to 20kHz, A-Weighted |               | 5.74 | 6.80          |      | 4.45 | 5.30 | μV <sub>RMS</sub> |

| V <sub>IN</sub> | Maximum Input Signal f <sub>IN</sub> =1kHz, THD+N < 10%, Level=0V |               |      | 448           |      |      | 317  | $mV_{PP}$         |

#### **Electrical Characteristics**

Unless otherwise specified, all limits are guaranteed for  $T_A$ =25°C,  $V_{DD}$ =1.8V,  $V_{IN}$ =94dB (SPL), and  $f_{CLK}$ =2.4MHz. Duty Cycle=50% and  $C_{MIC}$ =15pF.

| Symbol             | Parameter                                | Condition                                                                                                                                             | Min.                 | Тур. | Max.                 | Unit  |

|--------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|----------------------|-------|

| $V_{DD}$           | Supply Voltage Range                     |                                                                                                                                                       | 1.64                 | 1.80 | 3.63                 | V     |

| I <sub>DD</sub>    | Supply Current                           | INPUT=AC Coupled to GND, CLOCK=On, No Load                                                                                                            |                      | 470  |                      | μΑ    |

| I <sub>SLEEP</sub> | Sleep Mode Current                       | f <sub>CLK</sub> =GND                                                                                                                                 |                      | 1.5  | 8.0                  | μA    |

| PSR                | Power Supply Rejection <sup>(4)</sup>    | INPUT=AC Coupled to GND,<br>Test Signal on V <sub>DD</sub> =217Hz<br>Square Wave and<br>Broadband Noise <sup>(3)</sup> , Both<br>100mV <sub>P-P</sub> |                      | -74  |                      | dBFS  |

| IN <sub>NOM</sub>  | Nominal Sensitivity <sup>(5)</sup>       | INPUT=94dBSPL (1Pa)                                                                                                                                   |                      | -26  |                      | dBFS  |

| THD                | Total Harmonic Distortion <sup>(6)</sup> | f <sub>IN</sub> =1kHz, INPUT=-26dBFS                                                                                                                  |                      | 0.02 | 0.20                 | %     |

|                    | THD+N THD and Noise <sup>(4)</sup>       | $50Hz \le f_{IN} \le 1kHz$ ,<br>INPUT=-20dBFS                                                                                                         |                      | 0.2  | 1.0                  |       |

| THD+N              |                                          | f <sub>IN</sub> =1kHz, INPUT=-5dBFS                                                                                                                   |                      | 1.0  | 5.0                  | %     |

|                    |                                          | f <sub>IN</sub> =1kHz, INPUT=0dBFS                                                                                                                    |                      | 5.0  | 10.0                 |       |

| C <sub>IN</sub>    | Input Capacitance <sup>(7)</sup>         | INPUT                                                                                                                                                 |                      | 0.2  |                      | pF    |

| R <sub>IN</sub>    | Input Resistance <sup>(7)</sup>          | INPUT                                                                                                                                                 | >100                 | /    |                      | GΩ    |

| VIL                | CLOCK & SELECT Input<br>Logic LOW Level  |                                                                                                                                                       |                      |      | 0.3                  | V     |

| V <sub>IH</sub>    | CLOCK & SELECT Input<br>Logic HIGH Level |                                                                                                                                                       | 1.5                  |      | V <sub>DD</sub> +0.3 | V     |

| V <sub>OL</sub>    | Data Output Logic LOW<br>Level           |                                                                                                                                                       |                      |      | 0.35*V <sub>DD</sub> | V     |

| V <sub>OH</sub>    | Data Output Logic HIGH<br>Level          |                                                                                                                                                       | 0.65*V <sub>DD</sub> |      |                      | V     |

| V <sub>OUT</sub>   | Acoustic Overload Point <sup>(7)</sup>   | THD < 10%                                                                                                                                             | 120                  |      |                      | dBSPL |

Continued on the following page...

#### **Electrical Characteristics** (Continued)

Unless otherwise specified, all limits are guaranteed for  $T_A$ =25°C,  $V_{DD}$ =1.8V,  $V_{IN}$ =94dB(SPL), and  $f_{CLK}$ =2.4MHz. Duty Cycle=50% and  $C_{MIC}$ =15pF.

| Symbol                  | Parameter                                          | Condition                                                                     | Min. | Тур. | Max. | Unit |

|-------------------------|----------------------------------------------------|-------------------------------------------------------------------------------|------|------|------|------|

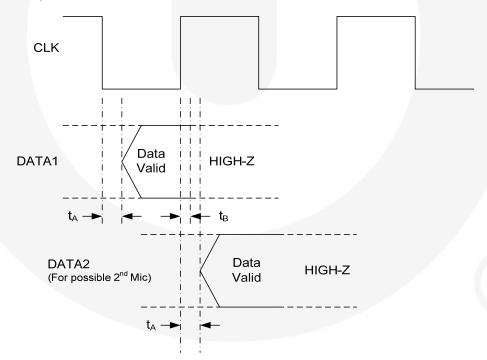

| t <sub>A</sub>          | Time from CLOCK Transition to Data becoming Valid  | On Falling Edge of CLOCK,<br>SELECT=GND, C <sub>LOAD</sub> =15pF              | 18   | 43   |      | ns   |

| t <sub>B</sub>          | Time from CLOCK Transition to Data becoming HIGH-Z | On Rising Edge of CLOCK,<br>SELECT=GND, C <sub>LOAD</sub> =15pF               | 0    | 5    | 16   | ns   |

| t <sub>A</sub>          | Time from CLOCK Transition to Data becoming Valid  | On Rising Edge of CLOCK,<br>SELECT=V <sub>DD</sub> , C <sub>LOAD</sub> =15pF  | 18   | 56   |      | ns   |

| t <sub>B</sub>          | Time from CLOCK Transition to Data becoming HIGH-Z | On Falling Edge of CLOCK,<br>SELECT=V <sub>DD</sub> , C <sub>LOAD</sub> =15pF | 0    | 5    | 16   | ns   |

| f <sub>CLK</sub>        | Input CLOCK Frequency <sup>(8)</sup>               | Active Mode                                                                   | 1.0  | 2.4  | 4.0  | MHz  |

| CLK <sub>dc</sub>       | CLOCK Duty Cycle <sup>(4)</sup>                    |                                                                               | 40   | 50   | 60   | %    |

| twakeup                 | Wake-Up Time <sup>(9)</sup>                        | f <sub>CLK</sub> =2.4MHz                                                      |      | 0.35 | 2.00 | ms   |

| t <sub>FALLASLEEP</sub> | Fall-Asleep Time <sup>(10)</sup>                   | f <sub>CLK</sub> =2.4MHz                                                      | 0    | 0.01 | 1.00 | ms   |

| C <sub>LOAD</sub>       | Load Capacitance on Data                           |                                                                               |      |      | 100  | pF   |

#### Notes:

- 3. Pseudo-random noise with triangular probability density function. Bandwidth up to 10MHz.

- 4. Guaranteed by characterization.

- 5. Assuming that 120dB(SPL) is mapped to 0dBFS.

- 6. Assuming an input of -45dBV

- 7. Guaranteed by design.

- 8. All parameters are tested at 2.4MHz. Frequency range guaranteed by characterization.

- 9. Device wakes up when f<sub>CLK</sub> ≥ 300kHz.

- 10. Device falls asleep when  $f_{CLK} \le 70kHz$ .

t<sub>A</sub> – Microphone delay from clock edge to data assertion.

t<sub>B</sub> – Microphone delay from clock edge to high-impedance state.

$t_A > t_B$  to have interim HIGH-Z state in both signals.

Figure 3. Interface Timing

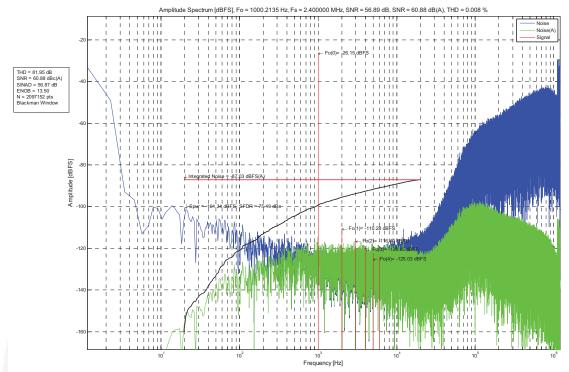

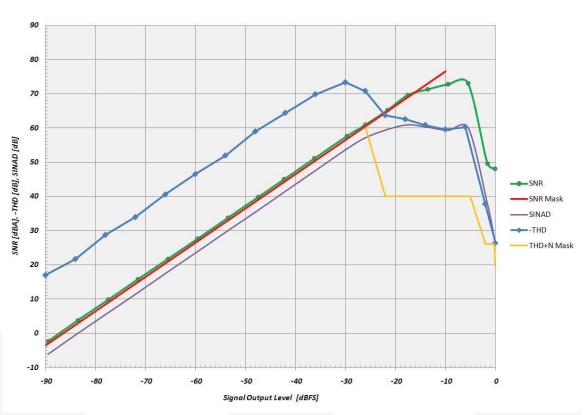

#### **Typical Performance Characteristics**

Unless otherwise specified, all limits are guaranteed for  $T_A$ =25°C,  $V_{DD}$ =1.8V,  $V_{IN}$ =94dB(SPL),  $f_{CLK}$ =2.4MHz, and duty cycle=50%.

Filename: fan3850a-1-BD9<sub>9</sub>M-20110125T122914.dat

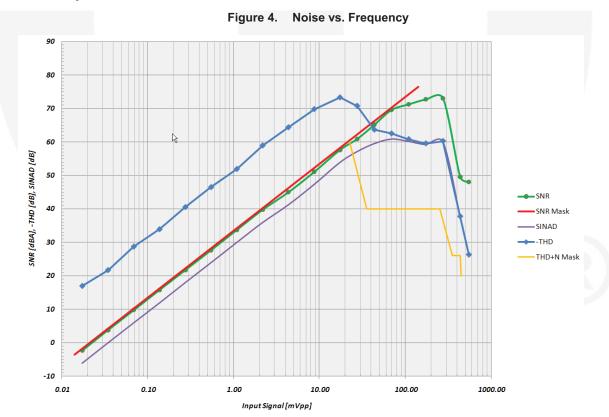

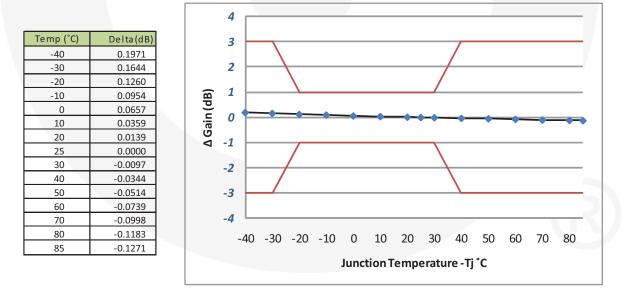

**Typical Performance Characteristics** (Continued)

Figure 6. THD, SINAD, and SNR vs. Output Level

Figure 7. Δ Gain vs. Temperature (Nominal Temperature= 25°C)

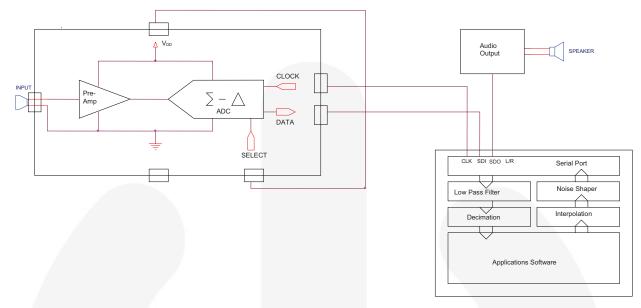

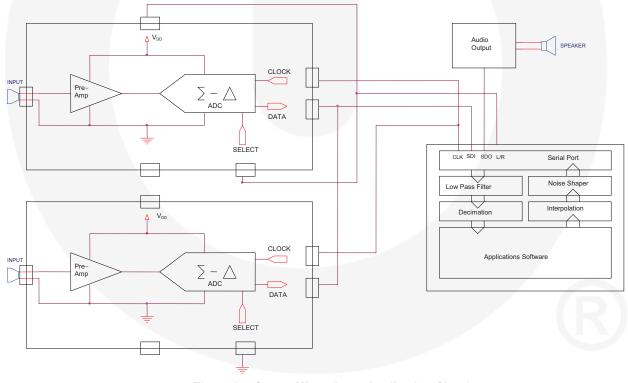

# **Applications Information**

Figure 8. Mono Microphone Application Circuit

Figure 9. Stereo Microphone Application Circuit

#### **Applications Information** (Continued)

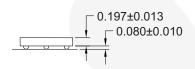

Figure 10. MIC Element Drawing

A 0.1 $\mu$ F decoupling capacitor is required for  $V_{DD}$ . It can be located inside the microphone or on the PCB very close to the VDD pin.

Due to high input impedance, care should be taken to remove all flux used during the reflow soldering process.

A  $100\Omega$  resistance is recommended on the clock output of the device driving the FAN3850A to minimize ringing and improve signal integrity.

For optimal PSR, route a trace to the VDD pin. Do not place a VDD plane under the device.

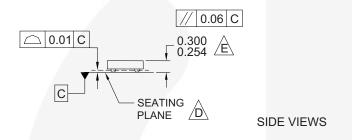

#### **Physical Dimensions**

+/-0.018

Ø0.120±0.010

(X) +/-0.018

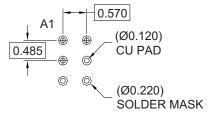

RECOMMENDED LAND PATTERN (NSMD)

#### **NOTES:**

- A. NO JEDEC REGISTRATION APPLIES.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M. 1994.

- D. DATUM C, THE SEATING PLANE IS DEFINED BY THE SPHERICAL CROWNS OF THE BALLS.

- E. PACKAGE TYPICAL HEIGHT IS 273 MICRONS ±23 MICRONS (254-300 MICRONS).

- F. FOR DIMENSIONS D, E, X, AND Y SEE PRODUCT DATASHEET.

- G. DRAWING FILENAME: UC006AHrev3.

Figure 11. 6-Ball, Wafer-Level Chip-Scale Package (WLCSP)

#### FAN3850A External Product Dimensions

**BOTTOM VIEW**

С

В

| Product ID            | D         | E       | X       | Υ       |

|-----------------------|-----------|---------|---------|---------|

| All options           | 1.260mm   | 0.860mm | 0.145mm | 0.145mm |

| Ball Composition: SN9 | 7.5-Ag2.5 |         |         |         |

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent version. Package specifications do not expand Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductors online packaging area for the most recent packaging drawings and tape and reel specifications. http://www.fairchildsemi.com/packaging/.

0.570

0.485

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

FlashVVriter®\* 2Cool™ AccuPower™ F-PFST Auto-SPM™ AX-CAP™ BitSiC® FRFFT® Global Power Resource<sup>SM</sup> Green FPS™ Build it Now™

Green FPS™ e-Series™ CorePLUS™ Gmax™ CorePOWER\*\* GTO™ CROSSVOLT™ IntelliMAX\*\* CTLIM

ISOPLANAR™ Current Transfer Logic™ Making Small Speakers Sound Louder DEUXPEED® and Better™

Dual Cool™ EcoSPARK® EfficientMax™ ESBC™

Fairchild® FACT Quiet Series™ FACT® FAST®

Fairchild Semiconductor® FastvCore™ FETBench™

PDP SPM™ Power-SPM™ PowerTrench® PowerXS™

Programmable Active Droop™ **QFET**

QSTM Quiet Series™

RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignalWise™ SmartM ax™ SMART START™

Solutions for Your Success™ SPM® STEALTH\*\* SuperFET® SuperSOT\*43 SuperSOT™-6 SuperSOT™-8 SupreM OS® SyncFET\*\*

Sync-Lock™ SYSTEM GENERAL® The Power Franchise®

p wer TinyBoost™ TinyBuck™ TinyCalc™ TinyLogic TINYOPTO\*\* TinyPower™ TinvPWM™ TinyWire™ TranSiC® TriFault Detect™ TRUECURRENT®\*

LIHO Ultra FRFET™ UniFET™ VCXTM VisualMax™ XSTM

μSerDes™

MegaBuck™

MicroFET\*\*

MicroPak™

MicroPak2™

MillerDrive™

MotionMax™

mWSaver™

OptoHiT\*\*

Motion-SPM™

OPTOLOGIC®

OPTOPLANAR®

MICROCOUPLER™

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS; SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### D-6-14 -- -- -- T----

| Datasheet Identification   Product Status |                       | Definition                                                                                                                                                                                          |  |  |

|-------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advance Information                       | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |

| Preliminary                               | First Production      | Datasheet contains preliminary data, supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |

| No Identification Needed                  | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |

| Obsolete                                  | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |  |  |

Rev 156

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

# AMEYA360 Components Supply Platform

# **Authorized Distribution Brand:**

#### Website:

Welcome to visit www.ameya360.com

#### Contact Us:

# > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

#### > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

# Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com