# LM3503 Dual-Display Constant Current LED Driver with Analog Brightness Control

Check for Samples: LM3503

#### **FEATURES**

- Drives up to 4, 6, 8 or 10 White LEDs for Dual Display Backlighting

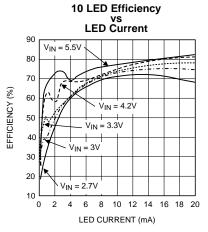

- >80% Peak Efficiency

- Output Voltage Protection Options: 16V, 25V, 35V & 44V

- Input Under-Voltage Protection

- Internal Soft Start Eliminates Inrush Current

- 1 MHz Constant Switching Frequency

- · Analog Brightness Control

- Wide Input Voltage Range: 2.5V to 5.5V

- Low Profile Packages: <1 mm Height</li>

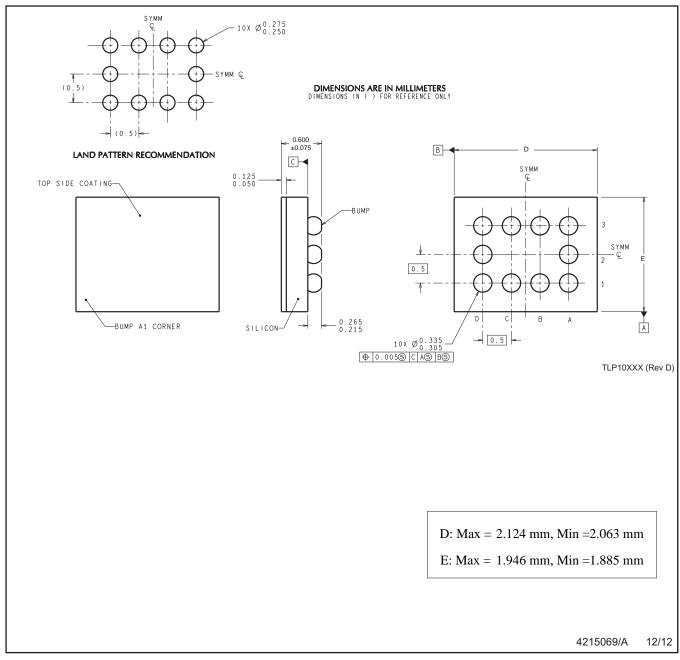

- 10 Bump DSBGA

- 16 Pin WQFN

## **APPLICATIONS**

- Dual Display Backlighting in Portable devices

- Cellular Phones and PDAs

#### DESCRIPTION

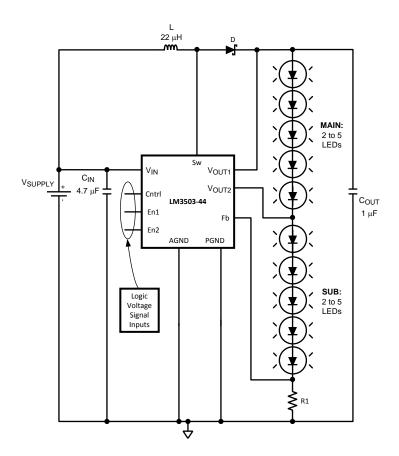

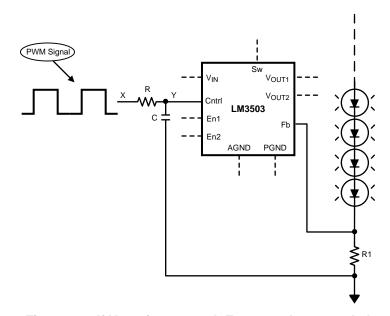

The LM3503 is a white LED driver for lighting applications. For dual display backlighting applications, the LM3503 provides a complete solution. The LM3503 contains two internal white LED current bypass FET (Field Effect Transistor) switches. The white LED current can be adjusted with a DC voltage from a digital to analog converter or RC filtered PWM (pulse-width-modulated) signal at the Cntrl pin.

## **Typical Application**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### **DESCRIPTION (CONTINUED)**

With no external compensation, cycle-by-cycle current limit, output over-voltage protection, input under-voltage protection, and dynamic white LED current control capability, the LM3503 offers superior performance over other step-up white LED drivers.

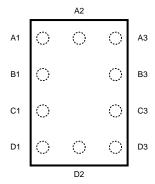

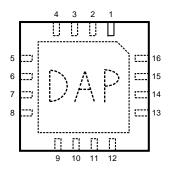

## **Connection Diagram**

Figure 1. 10-Bump Thin DSBGA Package (YPA0010) (Top View)

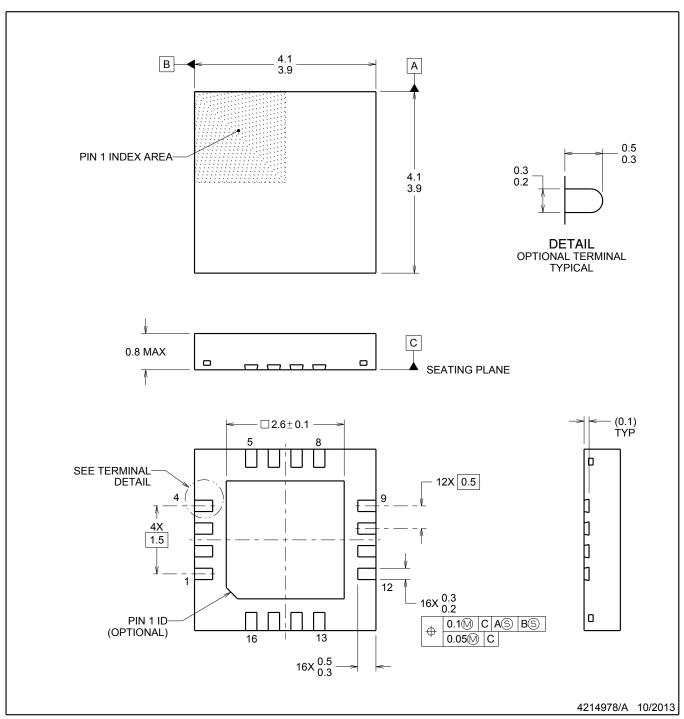

Figure 2. 16-Lead Thin WQFN Package (RGH0016A) (Top View)

#### **PIN DESCRIPTIONS**

| Bump # | Pin#      | Name       | Description                                                                                                                                                     |  |

|--------|-----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

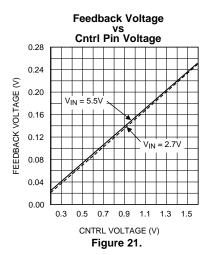

| A1     | 9         | Cntrl      | White LED Current Control Connection                                                                                                                            |  |

| B1     | 7         | Fb         | Feedback Voltage Connection                                                                                                                                     |  |

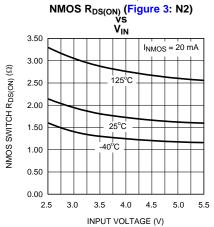

| C1     | 6         | $V_{OUT2}$ | Drain Connections of the NMOS and PMOS Field Effect Transistor (FET) Switches (Figure 3: N2 and P1). Connect 100nF at $V_{OUT2}$ node if $V_{OUT2}$ is not used |  |

| D1     | 4         | $V_{OUT1}$ | Over-Voltage Protection (OVP) and Source Connection of the PMOS FET Switch (Figure 3: P1)                                                                       |  |

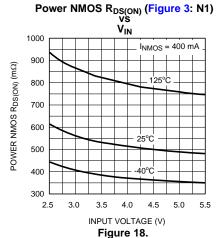

| D2     | 2 and 3   | Sw         | Drain Connection of the Power NMOS Switch (Figure 3: N1)                                                                                                        |  |

| D3     | 15 and 16 | Pgnd       | Power Ground Connection                                                                                                                                         |  |

| C3     | 14        | Agnd       | Analog Ground Connection                                                                                                                                        |  |

| В3     | 13        | $V_{IN}$   | Input Voltage Connection                                                                                                                                        |  |

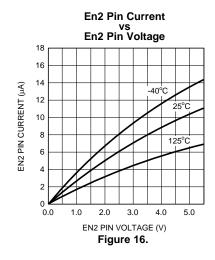

| A3     | 12        | En2        | NMOS FET Switch Control Connection                                                                                                                              |  |

| A2     | 10        | En1        | PMOS FET Switch Control Connection                                                                                                                              |  |

|        | 1         | NC         | No Connection                                                                                                                                                   |  |

|        | 5         | NC         | No Connection                                                                                                                                                   |  |

|        | 8         | NC         | No Connection                                                                                                                                                   |  |

|        | 11        | NC         | No Connection                                                                                                                                                   |  |

|        | DAP       | DAP        | Die Attach Pad (DAP), to be soldered to the printed circuit board's ground plane for enhanced thermal dissipation.                                              |  |

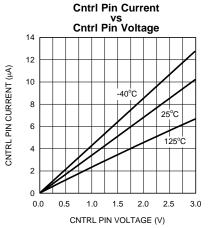

**Cntrl (Bump A1):** White LED current control pin. Use this pin to control the feedback voltage with an external DC voltage.

Fb (Bump B1):Output voltage feedback connection.

$V_{OUT2}$  (Bump C1):Drain connections of the internal PMOS and NMOS FET switches (Figure 3: P1 and N2). It is recommended to connect 100nF at  $V_{OUT2}$  if  $V_{OUT2}$  is not used for LM3503-35V & LM3503-44V versions.

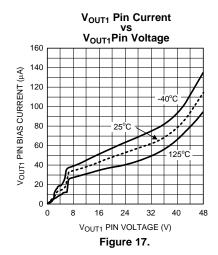

## V<sub>OUT1</sub>(Bump D1):

Source connection of the internal PMOS FET switch (Figure 3: P1) and OVP sensing node. The output capacitor must be connected as close to the device as possible, between the  $V_{OUT1}$  pin and ground plane. Also connect the Schottky diode as close as possible to the  $V_{OUT1}$  pin to minimize trace resistance and EMI radiation.

## Sw (Bump D2):

Drain connection of the internal power NMOS FET switch (Figure 3: N1). Minimize the metal trace length and maximize the metal trace width connected to this pin to reduce EMI radiation and trace resistance.

Pgnd (Bump D3): Power ground pin. Connect directly to the ground plane.

Agnd (Bump C3): Analog ground pin. Connect the analog ground pin directly to the Pgnd pin.

$V_{IN}$  (Bump B3): Input voltage connection pin. The  $C_{IN}$  capacitor should be as close to the device as possible, between the  $V_{IN}$  pin and ground plane.

**En2 (Bump A3):** Enable pin for the internal NMOS FET switch (Figure 3: N2) during device operation. When  $V_{En2}$  is  $\geq 1.4 \text{V}$ , the internal NMOS FET switch turns off and the SUB display is turned on. The En2 pin has an internal pull down circuit, thus the internal NMOS FET switch is normally in the on state of operation with the SUB display turned off. When  $V_{En2}$  is  $\leq 0.3 \text{V}$ , the internal NMOS FET switch turns on and the SUB display is turned off. If both  $V_{En1}$  and  $V_{En2}$  are  $\leq 0.3 \text{V}$  the LM3503 will shutdown. If  $V_{OUT2}$  is not used, En2 must be floating or grounded and En1 used to enable the device.

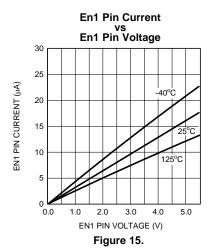

**En1 (Bump A2):** Enable pin for the internal PMOS FET switch (Figure 3: P1) during device operation. When  $V_{En1}$  is  $\leq 0.3V$ , the internal PMOS FET switch turns on and the MAIN display is turned off. When  $V_{En1}$  is  $\geq 1.4V$ , the internal PMOS FET switch turns off and the MAIN display is turned on. If both  $V_{En1}$  and  $V_{En2}$  are  $\leq 0.3V$  the LM3503 will shutdown. The En1 pin has an internal pull down circuit, thus the internal PMOS FET switch is normally in the on state of operation with the MAIN display turned off. If  $V_{OUT2}$  is not used, En2 must be grounded and En1 use to enable the device.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## Absolute Maximum Ratings (1)(2)

| Absolute maximum itali         | iigs                 |                            |

|--------------------------------|----------------------|----------------------------|

| V <sub>IN</sub> Pin            |                      | −0.3V to +5.5V             |

| Sw Pin                         |                      | -0.3V to +48V              |

| Fb Pin                         |                      | −0.3V to +5.5V             |

| Cntrl Pin                      |                      | −0.3V to +5.5V             |

| V <sub>OUT1</sub> Pin          |                      | −0.3V to +48V              |

| V <sub>OUT2</sub> Pin          |                      | −0.3V to V <sub>OUT1</sub> |

| En1                            |                      | −0.3V to +5.5V             |

| En2                            |                      | −0.3V to +5.5V             |

| Continuous Power Dissipation   |                      | Internally Limited         |

| Maximum Junction Temperature ( | T <sub>J-MAX</sub> ) | +150°C                     |

| Storage Temperature Range      |                      | −65°C to +150°C            |

| ESD Rating <sup>(3)</sup>      | Human Body Model     | 2 kV                       |

|                                | Machine Model        | 200V                       |

<sup>(1)</sup> Absolute maximum ratings indicate limits beyond which damage to the device may occur. Electrical characteristic specifications do not apply when operating the device outside of its rated operating conditions.

## Operating Conditions (1)(2)

| <u> </u>                                     |                 |

|----------------------------------------------|-----------------|

| Junction Temperature (T <sub>J</sub> ) Range | −40°C to +125°C |

| Ambient Temperature (T <sub>A</sub> ) Range  | −40°C to +85°C  |

| Supply Voltage, V <sub>IN</sub> Pin          | 2.5V to 5.5V    |

| En1 and En2 Pins                             | 0V to 5.5V      |

| Cntrl Pin                                    | 0V to 3.5V      |

<sup>(1)</sup> Absolute maximum ratings indicate limits beyond which damage to the device may occur. Electrical characteristic specifications do not apply when operating the device outside of its rated operating conditions.

Product Folder Links: LM3503

<sup>(2)</sup> If Military/Aerospace specified devices are required, please contact the TI Sales Office/ Distributors for availability and specifications.

<sup>(3)</sup> The human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin.

<sup>(2)</sup> All voltages are with respect to the potential at the GND pin.

## Thermal Properties (3)

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) |        |  |

|----------------------------------------------------------|--------|--|

| DSBGA Package 65                                         |        |  |

| WQFN Package                                             | 49°C/W |  |

(3) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J(MAX</sub>), the junction-to-ambient thermal resistance, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. See Thermal Properties for the thermal resistance. The maximum allowable power dissipation at any ambient temperature is calculated using: P<sub>D(MAX)</sub> = (T<sub>J(MAX)</sub>-T<sub>A</sub>)/ θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature. For more information on this topic, please refer to Application Note 1187(An1187): Leadless Leadframe Package (LLP) and Application Note 1112(AN1112) for DSBGA chip scale package.

## Electrical Characteristics (1)(2)

Limits in standard typeface are for  $T_J$  = +25°C. Limits in **bold typeface** apply over the full operating junction temperature range (-40°C  $\leq T_J \leq$  +125°C). Unless otherwise specified,  $V_{IN}$  = 2.5V.

| Symbol                  | Parameter                                                                              | Conditions                                                                                                                                                                                           | Min | Тур                      | Max                        | Units          |

|-------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------|----------------------------|----------------|

| V <sub>IN</sub>         | Input Voltage                                                                          |                                                                                                                                                                                                      | 2.5 |                          | 5.5                        | V              |

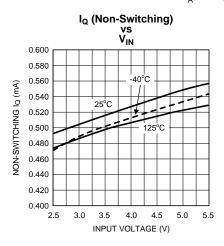

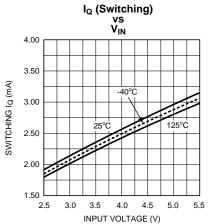

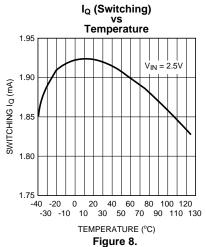

| IQ                      | Non-Switching<br>Switching<br>Shutdown                                                 | Cntrl = 1.6V<br>Fb = 0V, Sw Is Floating<br>En1 = En2 = 0V                                                                                                                                            |     | 0.5<br>1.9<br>0.1        | 1<br>3<br>3                | mA<br>mA<br>μA |

| V <sub>Fb</sub>         | Feedback Voltage                                                                       | Cntrl = 3.5V                                                                                                                                                                                         | 0.5 | 0.55                     | 0.6                        | V              |

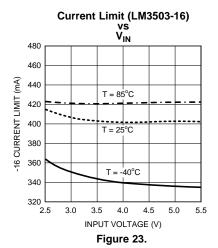

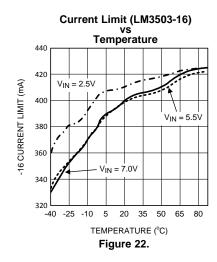

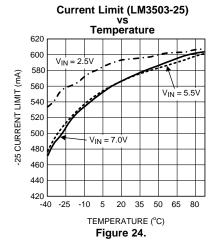

| I <sub>CL</sub>         | NMOS Power Switch<br>Current Limit                                                     | 16, Fb = 0V<br>25, Fb = 0V<br>35, Fb = 0V<br>44,FB = 0V<br>250<br>400<br>450<br>450                                                                                                                  |     | 400<br>600<br>750<br>750 | 650<br>800<br>1050<br>1050 | mA             |

| $I_{Fb}$                | Feedback Pin Output<br>Bias Current                                                    | Fb = 0.25V, Cntrl = 1.6V                                                                                                                                                                             |     | 64                       | 500                        | nA             |

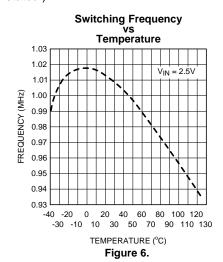

| F <sub>S</sub>          | Switching Frequency                                                                    |                                                                                                                                                                                                      | 0.8 | 1                        | 1.2                        | MHz            |

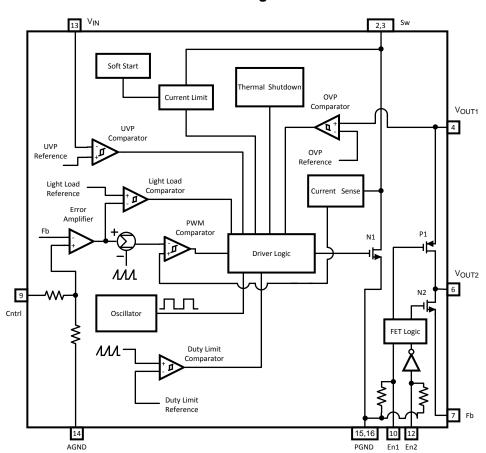

| R <sub>DS(ON)</sub>     | NMOS Power Switch ON<br>Resistance<br>(Figure 3: N1)                                   | I <sub>Sw</sub> = 500 mA <sup>(3)</sup>                                                                                                                                                              |     | 0.55                     | 1.1                        | Ω              |

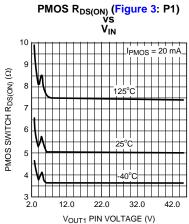

| R <sub>PDS(ON)</sub>    | PMOS ON Resistance<br>Of V <sub>OUT1</sub> /V <sub>OUT2</sub> Switch<br>(Figure 3: P1) | I <sub>PMOS</sub> = 20 mA, En1 = 0V, En2 = 1.5V                                                                                                                                                      |     | 5                        | 10                         | Ω              |

| R <sub>NDS(ON)</sub>    | NMOS ON Resistance<br>Of V <sub>OUT2</sub> /Fb Switch<br>(Figure 3: N2)                | I <sub>NMOS</sub> = 20 mA, En1 = 1.5V, En2 = 0V                                                                                                                                                      |     | 2.5                      | 5                          | Ω              |

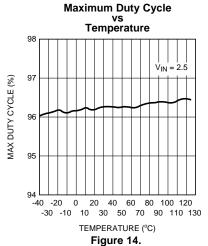

| D <sub>MAX</sub>        | Maximum Duty Cycle                                                                     | Fb = 0V                                                                                                                                                                                              | 90  | 95                       |                            | %              |

| I <sub>Sw</sub>         | Sw Pin Leakage<br>Current <sup>(4)</sup>                                               | Sw = 42V, En1 = En2 =0V                                                                                                                                                                              |     | 0.01                     | 5                          | μA             |

| I <sub>VOUT1(OFF)</sub> | V <sub>OUT1</sub> Pin Leakage<br>Current <sup>(4)</sup>                                | V <sub>OUT1</sub> = 14V, En1 = En2 = 0V (16)<br>V <sub>OUT1</sub> = 23V, En1 = En2 = 0V (25)<br>V <sub>OUT1</sub> = 32V, En1 = En2 = 0V (35)<br>V <sub>OUT1</sub> = 42V, En1 = En2 = 0V (44)         |     | 0.1<br>0.1<br>0.1<br>0.1 | 3<br>3<br>3<br>3           | μΑ             |

| I <sub>VOUT1(ON)</sub>  | V <sub>OUT1</sub> Pin Bias<br>Current <sup>(4)</sup>                                   | V <sub>OUT1</sub> = 14V, En1 = En1 = 1.5V (16)<br>V <sub>OUT1</sub> = 23V, En1 = En2 = 1.5V (25)<br>V <sub>OUT1</sub> = 32V, En1 = En2 = 1.5V (35)<br>V <sub>OUT1</sub> = 42V, En1 = En2 = 1.5V (44) |     | 40<br>50<br>50<br>85     | 80<br>100<br>100<br>140    | μА             |

| I <sub>VOUT2</sub>      | V <sub>OUT2</sub> Pin Leakage<br>Current <sup>(4)</sup>                                | Fb = En1 = En2 = 0V, V <sub>OUT2</sub> = V <sub>OUT1</sub> = 42V                                                                                                                                     |     | 0.1                      | 3                          | μA             |

| UVP                     | Under-Voltage<br>Protection                                                            | On Threshold<br>Off Threshold                                                                                                                                                                        | 2.2 | 2.4<br>2.3               | 2.5                        | ٧              |

<sup>(1)</sup> All voltages are with respect to the potential at the GND pin.

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

<sup>(2)</sup> Min and Max limits are ensured by design, test, or statistical analysis. Typical numbers are not specified, but do represent the most likely norm.

<sup>(3)</sup> NMOS Power On Resistance measured at I<sub>SW</sub>= 250mA for sixteen voltage version.

<sup>(4)</sup> Current flows into the pin.

## Electrical Characteristics(1)(2) (continued)

Limits in standard typeface are for  $T_J = +25^{\circ}C$ . Limits in **bold typeface** apply over the full operating junction temperature range ( $-40^{\circ}C \le T_J \le +125^{\circ}C$ ). Unless otherwise specified,  $V_{IN} = 2.5V$ .

| Symbol             | Parameter                                                          | Conditions                                                                                                                                            | Min                                                          | Тур                                            | Max                                                          | Units |

|--------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------|-------|

| OVP                | Over-Voltage<br>Protection (5)                                     | On Threshold (16) Off Threshold (16) On Threshold (25) F Off Threshold (25) On Threshold (35) Off Threshold (35) On Threshold (44) Off Threshold (44) | 14.5<br>14.0<br>22.5<br>21.5<br>32.0<br>31.0<br>40.5<br>39.0 | 15.5<br>15<br>24<br>23<br>34<br>33<br>42<br>41 | 16.5<br>16.0<br>25.5<br>24.5<br>35.0<br>34.0<br>43.5<br>42.0 | V     |

| V <sub>En1</sub>   | PMOS FET Switch and<br>Device Enabling<br>Threshold (Figure 3: P1) | Off Threshold On Threshold                                                                                                                            | 1.4                                                          | 0.8                                            | 0.3                                                          | V     |

| V <sub>En2</sub>   | NMOS FET Switch and<br>Device Enabling                             | Off Threshold                                                                                                                                         |                                                              | 0.8                                            | 0.3                                                          | V     |

|                    | Threshold (Figure 3: N2)                                           | On Threshold                                                                                                                                          | 1.4                                                          | 8.0                                            |                                                              |       |

| V <sub>Cntrl</sub> | V <sub>Cntrl</sub> Range                                           | V <sub>IN</sub> = 3.6V                                                                                                                                | 0.2                                                          |                                                | 3.5                                                          | V     |

| I <sub>En1</sub>   | En1 Pin Bias Current <sup>(6)</sup>                                | En1 = 2.5V<br>En1 = 0V                                                                                                                                |                                                              | 7<br>0.1                                       | 14                                                           | μΑ    |

| I <sub>En2</sub>   | En2 Pin Bias Current <sup>(6)</sup>                                | En2 = 2.5V<br>En2 = 0V                                                                                                                                |                                                              | 7<br>0.1                                       | 14                                                           | μΑ    |

| I <sub>CNTRL</sub> | Cntrl Pin Bias Current <sup>(6)</sup>                              | Cntrl = 2.5V                                                                                                                                          |                                                              | 8                                              | 14                                                           | μA    |

The on threshold indicates that the LM3503 is no longer switching or regulating LED current, while the off threshold indicates normal operation.

Current flows into the pin.

#### **Block Diagram**

Figure 3. Block Diagram

#### **Detailed Description of Operation**

The LM3503 utilizes an asynchronous current mode pulse-width-modulation (PWM) control scheme to regulate the feedback voltage over specified load conditions. The DC/DC converter behaves as a controlled current source for white LED applications. The operation can best be understood by referring to the block diagram in Figure 3 for the following operational explanation. At the start of each cycle, the oscillator sets the driver logic and turns on the internal NMOS power device, N1, conducting current through the inductor and reverse biasing the external diode. The white LED current is supplied by the output capacitor when the internal NMOS power device, N1, is turned on. The sum of the error amplifier's output voltage and an internal voltage ramp are compared with the sensed power NMOS, N1, switch voltage. Once these voltages are equal, the PWM comparator will then reset the driver logic, thus turning off the internal NMOS power device, N1, and forward biasing the external diode. The inductor current then flows through the diode to the white LED load and output capacitor. The inductor current recharges the output capacitor and supplies the current for the white LED load. The oscillator then sets the driver logic again repeating the process. The output voltage of the error amplifier controls the current through the inductor. This voltage will increase for larger loads and decrease for smaller loads limiting the peak current in the inductor and minimizing EMI radiation. The duty limit comparator is always operational, it prevents the internal NMOS power switch, N1, from being on for more than one oscillator cycle and conducting large amounts of current. The light load comparator allows the LM3503 to properly regulate light/small white LED load currents, where regulation becomes difficult for the LM3503's primary control loop. Under light load conditions, the LM3503 will enter into a pulse skipping pulse-frequency-mode (PFM) of operation where the operational frequency will vary with the load. As a result of PFM mode operation, the output voltage ripple magnitude will significantly increase.

The LM3503 has two control pins, En1 and En2, used for selecting which segment of a single white LED string network is active for dual display applications. En1 controls the main display (MAIN) segment of the single string white LED network between pins  $V_{OUT1}$  and  $V_{OUT2}$ . En2 controls the sub display (SUB) segment of the single string white LED network between the  $V_{OUT2}$  and Fb. If both  $V_{En1}$  and  $V_{En2}$  are  $\leq 0.3V$ , the LM3503 will shutdown, for further description of the En1 and En2 operation, see Figure 33. During shutdown the output capacitor discharges through the string of white LEDs and feedback resistor to ground. The LED current can be dynamically controlled by a DC voltage on the Cntrl pin. When  $V_{Cntrl} = 0V$  the white LED current may not be equal to zero because of offsets within the LM3503 internal circuitry. To ensure zero white LED current the LM3503 must be in shutdown mode operation.

The LM3503 has dedicated protection circuitry active during normal operation to protect the integrated circuit (IC) and external components. Soft start circuitry is present in the LM3503 to allow for slowly increasing the current limit to its steady-state value to prevent undesired high inrush current during start up. Thermal shutdown circuitry turns off the internal NMOS power device, N1, when the internal semiconductor junction temperature reaches excessive levels. The LM3503 has a under-voltage protection (UVP) comparator that disables the internal NMOS power device when battery voltages are too low, thus preventing an on state where the internal NMOS power device conducts large amounts of current. The over-voltage protection (OVP) comparator prevents the output voltage from increasing beyond the protection limit when the white LED string network is removed or if there is a white LED failure. OVP allows for the use of low profile ceramic capacitors at the output. The current through the internal NMOS power device, N1, is monitored to prevent peak inductor currents from damaging the IC. If during a cycle (cycle=1/switching frequency) the peak inductor current exceeds the current limit for the LM3503, the internal NMOS power device will be turned off for the remaining duration of that cycle.

| En1  | En2  | Result (See Figure 1 and Figure 2)                            | Shutdown |

|------|------|---------------------------------------------------------------|----------|

| 0.3V | 0.3V | [P1→OFF N2→OFF N1→OFF] or [MAIN→OFF SUB→OFF N1→OFF]           | х        |

| 1.4V | 0.3V | [P1→OFF N2→ON N1→Switching] or [MAIN→ON SUB→OFF N1→Switching] |          |

| 0.3V | 1.4V | [P1→ON N2→OFF N1→Switching] or [MAIN→OFF SUB→ON N1→Switching] |          |

| 1.4V | 1.4V | [P1→OFF N2→OFF N1→Switching] or [MAIN→ON SUB→ON N1→Switching] |          |

Figure 4. Operational Characteristics Table

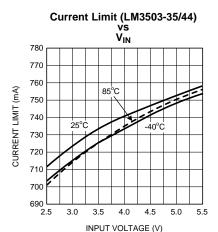

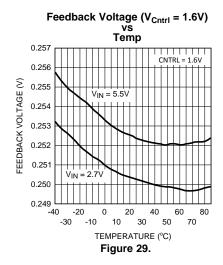

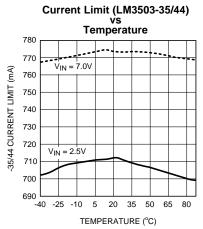

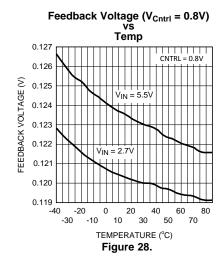

#### Typical Performance Characteristics

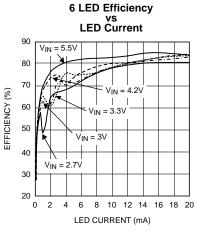

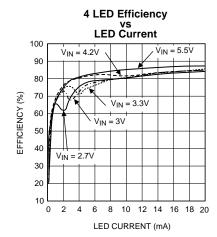

(See Typical Application Circuit : L=DO1608C-223 and D=B150-13. Efficiency:  $\eta = P_{OUT}/P_{IN} = [(V_{OUT} - V_{Fb}) * I_{OUT}] / [V_{IN} * I_{IN}]$ .  $T_A = +25$ °C, unless otherwise stated.)

Figure 5.

Submit Documentation Feedback

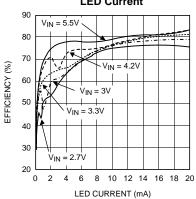

(See Typical Application Circuit : L=DO1608C-223 and D=B150-13. Efficiency:  $\eta = P_{OUT}/P_{IN} = [(V_{OUT} - V_{Fb}) * I_{OUT}]/[V_{IN} * I_{IN}]$ .  $T_A = +25^{\circ}C$ , unless otherwise stated.)

Figure 7.

Figure 9.

Figure 11.

8 LED Efficiency vs LED Current

Figure 10.

Figure 12.

(See Typical Application Circuit : L=DO1608C-223 and D=B150-13. Efficiency:  $\eta = P_{OUT}/P_{IN} = [(V_{OUT} - V_{Fb}) * I_{OUT}]/[V_{IN} * I_{IN}]$ .  $T_A = +25^{\circ}C$ , unless otherwise stated.)

Figure 13.

(See Typical Application Circuit : L=DO1608C-223 and D=B150-13. Efficiency:  $\eta = P_{OUT}/P_{IN} = [(V_{OUT} - V_{Fb}) * I_{OUT}]/[V_{IN} * I_{IN}]$ .  $T_A = +25^{\circ}C$ , unless otherwise stated.)

Figure 19.

Figure 20.

(See Typical Application Circuit : L=DO1608C-223 and D=B150-13. Efficiency:  $\eta = P_{OUT}/P_{IN} = [(V_{OUT} - V_{Fb}) * I_{OUT}]/[V_{IN} * I_{IN}]$ .  $T_A = +25^{\circ}C$ , unless otherwise stated.)

Figure 26.

Figure 30.

(See Typical Application Circuit : L=DO1608C-223 and D=B150-13. Efficiency:  $\eta = P_{OUT}/P_{IN} = [(V_{OUT} - V_{Fb}) * I_{OUT}]/[V_{IN} * I_{IN}]$ .  $T_A = +25^{\circ}C$ , unless otherwise stated.)

Figure 31.

Figure 32.

#### APPLICATION INFORMATION

#### WHITE LED CURRENT SETTING

The white LED current is controlled by a DC voltage at the Cntrl pin.

The relationship between the Cntrl pin voltage and Fb pin voltage can be computed with the following:

$V_{FB} = (0.156) \times (V_{Cntrl})$

V<sub>Cntrl</sub>: Cntrl Pin Voltage. Voltage Range: 0.2V ≤ V<sub>Cntrl</sub> ≤ 3.5V.

$$V_{\text{Fb}}$$

: Feedback Pin Voltage. (1)

#### LED CURRENT

The LED current is set using the following equation:

$$I_{LED} = \frac{V_{Fb}}{R1} \tag{2}$$

To determine the maximum output current capability of the device, it is best to estimate using equations on page 16 and the minimum peak current limit of the device (see electrical table). Note the current capability will be higher with less LEDs in the application.

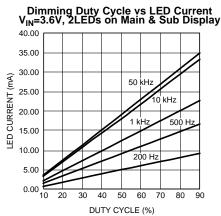

#### WHITE LED DIMMING

Figure 33. If  $V_{OUT2}$  is not used, En2 must be grounded

Aside from varying the DC voltage at the Cntrl pin, white LED dimming can be accomplished through the RC filtering of a PWM signal. The PWM signal frequency should be at least a decade greater than the RC filter bandwidth. WHITE LED DIMMING is how the LM3503 should be wired for PWM filtered white LED dimming functionality. When using PWM dimming, it is recommended to add 1-2ms delay between the Cntrl signal and the main Enable sginal (En1) to allow time for the output to discharge. This will prevent potential flickering especially if the Sub display is compose of 2 LEDs or less.

The equations below are guidelines for choosing the correct RC filter values in relation to the PWM signal frequency.

Equation:

$$F_{RC} = \frac{1}{2 \times \pi \times R \times C} \tag{3}$$

Equation:

$$F_{PWM} > 10 \text{ x } F_{RC}$$

(4)

**F**<sub>RC</sub>: RC Filter Bandwidth Cutoff Frequency.

F<sub>PWM</sub>: PWM Signal Frequency.R: Chosen Filter Resistor.C: Chosen Filter Capacitor.

For example, using the above equations to determine the proper RC values. Assume the following condition: $V_{IN}$ = 3.6V, C=0.01µF and  $F_{PWM}$  = 500Hz, then  $F_{RC}$ = 50Hz by relation to equation 2. By rearranging equation 1 to solve for R; R = 318.5K ohms (standard value, R = 316K).

#### PWM Dimming Duty Cycle vs. LED Current

The results are based on the 2LEDs on Main display and 2LEDs on Sub display

| Duty | 200Hz         | 500Hz        | 1KHz         | 10KHz        | 50KHz        | 100kHz       |

|------|---------------|--------------|--------------|--------------|--------------|--------------|

| (%)  | R = 787k ohms | R =316k ohms | R = 158kohms | R=16.2k ohms | R=3.16k ohms | R=1.62k ohms |

| 10   | 0.78mA        | 1.59mA       | 2.23mA       | 3.42mA       | 3.58mA       | 3.61mA       |

| 20   | 1.85mA        | 3.46mA       | 4.78mA       | 7.09mA       | 7.41mA       | 7.48mA       |

| 30   | 2.88mA        | 5.35mA       | 7.33mA       | 10.77mA      | 11.25mA      | 11.34mA      |

| 40   | 3.96mA        | 7.24mA       | 9.88mA       | 14.48mA      | 15.12mA      | 15.24mA      |

| 50   | 5.05mA        | 9.12mA       | 12.45mA      | 19.1mA       | 19.06mA      | 19.16mA      |

| 60   | 6.08mA        | 11.03mA      | 15.03mA      | 21.86mA      | 22.98mA      | 23.10mA      |

| 70   | 7.13mA        | 12.94mA      | 17.61mA      | 25.71mA      | 26.9mA       | 27.05mA      |

| 80   | 8.17mA        | 14.83mA      | 20.20mA      | 29.53mA      | 30.83mA      | 31.00mA      |

| 90   | 9.24mA        | 16.73mA      | 22.79mA      | 33.32mA      | 34.78mA      | 35.00mA      |

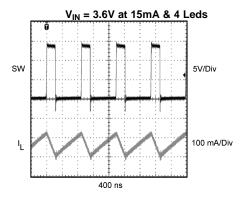

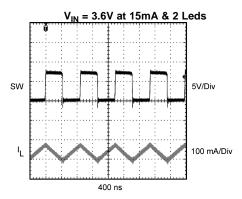

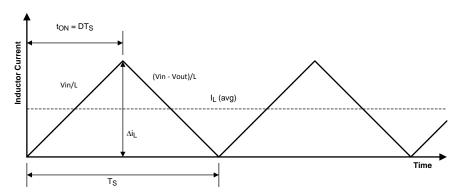

Figure 34. Inductor Current Waveform

#### CONTINUOUS AND DISCONTINUOUS MODES OF OPERATION

Since the LM3503 is a constant frequency pulse-width-modulated step-up regulator, care must be taken to make sure the maximum duty cycle specification is not violated. The duty cycle equation depends on which mode of operation the LM3503 is in. The two operational modes of the LM3503 are continuous conduction mode (CCM) and discontinuous conduction mode (DCM). Continuous conduction mode refers to the mode of operation where during the switching cycle, the inductor current never goes to and stays at zero for any significant amount of time during the switching cycle. Discontinuous conduction mode refers to the mode of operation where during the switching cycle, the inductor current goes to and stays at zero for a significant amount of time during the switching cycle. Figure 34 illustrates the threshold between CCM and DCM operation. In Figure 34 the inductor current is right on the CCM/DCM operational threshold. Using this as a reference, a factor can be introduced to calculate when a particular application is in CCM or DCM operation. R is a CCM/DCM factor we can use to compute which mode of operation a particular application is in. If R is  $\geq$  1, then the application is operating in CCM. Conversely, if R is < 1, the application is operating in DCM. The R factor inequalities are a result of the components that make up the R factor. From Figure 34, the R factor is equal to the average inductor current,  $I_L(avg)$ , divided by half the inductor ripple current,  $\Delta I_L$ . Using Figure 34, the following equation can be used to compute R factor:

www.ti.com

$$R = \frac{2 * I_{L} (avg)}{\Delta i_{L}}$$

(5)

$$I_{L} (avg) = \frac{[I_{OUT}]}{[(1-D) * Eff]}$$

(6)

$$\Delta i_{L} = \frac{[V_{IN} * D]}{[L * Fs]}$$

(7)

$$R = \frac{[2 * I_{OUT} * L * Fs * (V_{OUT})^2]}{[(V_{IN})^2 * Eff * (V_{OUT} - V_{IN})]}$$

(8)

V<sub>IN</sub>: Input Voltage.

**V<sub>OUT</sub>:** Output Voltage.

**Eff:** Efficiency of the LM3503.

**Fs:** Switching Frequency.

IOUT: White LED Current/Load Current.

L: Inductance Magnitude/Inductor Value.

**D:** Duty Cycle for CCM operation.

Δi<sub>L</sub>: Inductor Ripple Current.

I<sub>L</sub>(avg): Average Inductor Current.

For CCM operation, the duty cycle can be computed with:

$$D = \frac{t_{ON}}{T_{S}} \tag{9}$$

$$D = \frac{[V_{OUT} - V_{IN}]}{[V_{OUT}]}$$

(10)

**D:** Duty Cycle for CCM Operation.

Vour: Output Voltage.

V<sub>IN</sub>: Input Voltage.

For DCM operation, the duty cycle can be computed with:

$$D = \frac{t_{ON}}{T_S} \tag{11}$$

$$D = \sqrt{\frac{[2 * I_{OUT} * L * (V_{OUT} - V_{IN}) * Fs]}{[(V_{IN})^2 * Eff]}}$$

(12)

D: Duty Cycle for DCM Operation.

**V<sub>OUT</sub>:** Output Voltage.

V<sub>IN</sub>: Input Voltage.

IOUT: White LED Current/Load Current.

Fs: Switching Frequency.

L: Inductor Value/Inductance Magnitude.

#### INDUCTOR SELECTION

In order to maintain inductance, an inductor used with the LM3503 should have a saturation current rating larger than the peak inductor current of the particular application. Inductors with low DCR values contribute decreased power losses and increased efficiency. The peak inductor current can be computed for both modes of operation: CCM and DCM.

The cycle-by-cycle peak inductor current for CCM operation can be computed with:

$$I_{\text{Peak}} \approx I_{\text{L}} \text{ (avg)} + \frac{\Delta i_{\text{L}}}{2}$$

(13)

$$I_{\text{Peak}} \approx \frac{[I_{\text{OUT}}]}{[(1 - D)^* \text{ Eff}]} + \frac{[V_{\text{IN}} * D]}{[2 * L * Fs]}$$

(14)

V<sub>IN</sub>: Input Voltage.

**Eff:** Efficiency of the LM3503.

**Fs:** Switching Frequency.

Iour: White LED Current/Load Current.

L: Inductance Magnitude/Inductor Value.

**D:** Duty Cycle for CCM Operation.

IPEAK: Peak Inductor Current.

Δi<sub>L</sub>: Inductor Ripple Current.

IL(avg): Average Inductor Current.

The cycle-by-cycle peak inductor current for DCM operation can be computed with:

$$I_{Peak} \approx \frac{[V_{IN} * D]}{[L * Fs]}$$

(15)

**V**<sub>IN</sub>: Input Voltage.

Fs: Switching Frequency.

L: Inductance Magnitude/Inductor Value.

**D:** Duty Cycle for DCM Operation.

**IPEAK:** Peak Inductor Current.

The minimum inductance magnitude/inductor value for the LM3503 can be calculated using the following, which is only valid when the duty cycle is > 0.5:

$$L > \frac{[V_{IN} * R_{DS(ON)} * ((D/D') - 1)]}{[1.562 * Fs]}$$

(16)

D: Duty Cycle.

**D**': 1-D.

R<sub>DS(ON)</sub>: NMOS Power Switch ON Resistance.

**Fs:** Switching Frequency.

V<sub>IN</sub>: Input Voltage.

L: Inductance Magnitude/Inductor Value.

This equation gives the value required to prevent subharmonic oscillations. The result of this equation and the inductor ripple currents should be accounted for when choosing an inductor value.

Some recommended Inductor manufactures included but are not limited to:

| Coilcraft | DO1608C-223 | www.golloroft.com |

|-----------|-------------|-------------------|

|           | DT1608C-223 | www.coilcraft.com |

#### **CAPACITOR SELECTION**

Multilayer ceramic capacitors are the best choice for use with the LM3503. Multilayer ceramic capacitors have the lowest equivalent series resistance (ESR). Applied voltage or DC bias, temperature, dielectric material type (X7R, X5R, Y5V, etc), and manufacturer component tolerance have an affect on the true or effective capacitance of a ceramic capacitor. Be aware of how your application will affect a particular ceramic capacitor by analyzing the aforementioned factors of your application. Before selecting a capacitor always consult the capacitor manufacturer's data curves to verify the effective or true capacitance of the capacitor in your application.

#### INPUT CAPACITOR SELECTION

The input capacitor serves as an energy reservoir for the inductor. In addition to acting as an energy reservoir for the inductor the input capacitor is necessary for the reduction in input voltage ripple and noise experienced by the LM3503. The reduction in input voltage ripple and noise helps ensure the LM3503's proper operation, and reduces the effect of the LM3503 on other devices sharing the same supply voltage. To ensure low input voltage ripple, the input capacitor must have an extremely low ESR. As a result of the low input voltage ripple requirement multilayer ceramic capacitors are the best choice. A minimum capacitance of 2.0 µF is required for normal operation, so consult the capacitor manufacturer's data curves to verify whether the minimum capacitance requirement is going to be achieved for a particular application.

#### **OUTPUT CAPACITOR SELECTION**

The output capacitor serves as an energy reservoir for the white LED load when the internal power FET switch (Figure 3: N1) is on or conducting current. The requirements for the output capacitor must include worst case operation such as when the load opens up and the LM3503 operates in over-voltage protection (OVP) mode operation. A minimum capacitance of 0.5  $\mu$ F is required to ensure normal operation. Consult the capacitor manufacturer's data curves to verify whether the minimum capacitance requirement is going to be achieved for a particular application.

Some recommended capacitor manufacturers included but are not limited to:

| Taiyo-Yuden | GMK212BJ105MD (0805/35V)    | www.t-yuden.com |

|-------------|-----------------------------|-----------------|

| muRata      | GRM40-035X7R105K (0805/50V) | www.murata.com  |

| TDK         | C3216X7R1H105KT (1206/50V)  | www.tdktca.com  |

|             | C3216X7R1C475K (1206/16V)   |                 |

| AVX         | 08053D105MAT (0805/25V)     | www.avxcorp.com |

|             | 08056D475KAT (0805/6.3V)    |                 |

|             | 1206ZD475MAT (1206/10V)     |                 |

#### **DIODE SELECTION**

To maintain high efficiency it is recommended that the average current rating ( $I_F$  or  $I_O$ ) of the selected diode should be larger than the peak inductor current ( $I_{Lpeak}$ ). At the minimum the average current rating of the diode should be larger than the maximum LED current. To maintain diode integrity the peak repetitive forward current ( $I_{FRM}$ ) must be greater than or equal to the peak inductor current ( $I_{Lpeak}$ ). Diodes with low forward voltage ratings ( $V_F$ ) and low junction capacitance magnitudes ( $V_F$ ) or  $V_F$ ) are conducive to high efficiency. The chosen diode must have a reverse breakdown voltage rating ( $V_R$  and/or  $V_{RRM}$ ) that is larger than the output voltage ( $V_{OUT}$ ). No matter what type of diode is chosen, Schottky or not, certain selection criteria must be followed:

- 1.  $V_R$  and  $V_{RRM} > V_{OUT}$

- 2.  $I_F$  or  $I_O \ge I_{LOAD}$  or  $I_{OUT}$

- 3. I<sub>FRM</sub> ≥ I<sub>Lpeak</sub>

Some recommended diode manufacturers included but are not limited to:

| Vishay | SS12(1A/20V) | www.vishay.com |

|--------|--------------|----------------|

|        | SS14(1A/40V) |                |

|        | SS16(1A/60V) |                |

Product Folder Links: LM3503

| On Semiconductor      | MBRM120E (1A/20V)     | www.onsemi.com      |

|-----------------------|-----------------------|---------------------|

|                       | MBRS1540T3 (1.5A/40V) |                     |

|                       | MBR240LT (2A/40V)     |                     |

| Central Semiconductor | CMSH1-40M (1A/40V)    | www.centralsemi.com |

#### SHUTDOWN AND START-UP

On startup, the LM3503 contains special circuitry that limits the peak inductor current which prevents large current spikes from loading the battery or power supply. The LM3503 is shutdown when both En1 and En2 signals are less than 0.3V. During shutdown the output voltage is a diode drop below the supply voltage. When shutdown, the softstart is reset to prevent inrush current at the next startup.

#### THERMAL SHUTDOWN

The LM3503 stops regulating when the internal semiconductor junction temperature reaches approximately 140°C. The internal thermal shutdown has approximately 20°C of hysteresis which results in the LM3503 turning back on when the internal semiconductor junction temperature reaches 120°C. When the thermal shutdown temperature is reached, the softstart is reset to prevent inrush current when the die temperature cools.

#### **UNDER VOLTAGE PROTECTION**

The LM3503 contains protection circuitry to prevent operation for low input supply voltages. When Vin drops below 2.3V, typically, the LM3503 will no longer regulate. In this mode, the output voltage will be one diode drop below Vin and the softstart will be reset. When Vin increases above 2.4V, typically, the device will begin regulating again.

#### **OVER VOLTAGE PROTECTION**

The LM3503 contains dedicated ciruitry for monitoring the output voltage. In the event that the LED network is disconnected from the LM3503, the output voltage will increase and be limited to 15.5V(typ.) for the 16V version, 24V(typ.) for the 25V version, 34V(typ.) for 35V version and 42V(typ.) for the 44V version. (see electrical table for more details). In the event that the network is reconnected regulation will resume at the appropriate output voltage.

#### LAYOUT CONSIDERATIONS

All components, except for the white LEDs, must be placed as close as possible to the LM3503. The die attach pad (DAP) must be soldered to the ground plane.

The input bypass capacitor  $C_{IN}$ , as shown in the Typical Application Circuit, must be placed close to the IC and connect between the  $V_{IN}$  and Pgnd pins. This will reduce copper trace resistance which effects input voltage ripple of the IC. For additional input voltage filtering, a 100 nF bypass capacitor can be placed in parallel with  $C_{IN}$  to shunt any high frequency noise to ground. The output capacitor,  $C_{OUT}$ , must be placed close to the IC and be connected between the  $V_{OUT1}$  and Pgnd pins. Any copper trace connections for the  $C_{OUT}$  capacitor can increase the series resistance, which directly effects output voltage ripple and efficiency. The current setting resistor, R1, should be kept close to the Fb pin to minimize copper trace connections that can inject noise into the system. The ground connection for the current setting resistor network should connect directly to the Pgnd pin. The Agnd pin should be tied directly to the Pgnd pin. Trace connections made to the inductor should be minimized to reduce power dissipation and increase overall efficiency while reducing EMI radiation. For more details regarding layout guidelines for switching regulators, refer to Applications Note AN-1149.

Product Folder Links: LM3503

## **REVISION HISTORY**

| Changes from Revision D (May 2013) to Revision E |                                                    |  |    |  |  |  |  |

|--------------------------------------------------|----------------------------------------------------|--|----|--|--|--|--|

| •                                                | Changed layout of National Data Sheet to TI format |  | 18 |  |  |  |  |

Copyright © 2005–2013, Texas Instruments Incorporated

1-Nov-2013

## **PACKAGING INFORMATION**

| Orderable Device   | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|--------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|--------------------|--------------|----------------|---------|

| LM3503ITL-16/NOPB  | ACTIVE | DSBGA        | YPA                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -40 to 85    | SBHB           | Samples |

| LM3503ITL-25/NOPB  | ACTIVE | DSBGA        | YPA                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -40 to 85    | SBJB           | Samples |

| LM3503ITL-35/NOPB  | ACTIVE | DSBGA        | YPA                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -40 to 85    | SBKB           | Samples |

| LM3503ITL-44/NOPB  | ACTIVE | DSBGA        | YPA                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -40 to 85    | SDNB           | Samples |

| LM3503ITLX-16/NOPB | ACTIVE | DSBGA        | YPA                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -40 to 85    | SBHB           | Samples |

| LM3503ITLX-25/NOPB | ACTIVE | DSBGA        | YPA                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -40 to 85    | SBJB           | Samples |

| LM3503ITLX-35/NOPB | ACTIVE | DSBGA        | YPA                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -40 to 85    | SBKB           | Samples |

| LM3503ITLX-44/NOPB | ACTIVE | DSBGA        | YPA                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -40 to 85    | SDNB           | Samples |

| LM3503SQ-16/NOPB   | ACTIVE | WQFN         | RGH                | 16   | 1000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | L00045B        | Samples |

| LM3503SQ-25/NOPB   | ACTIVE | WQFN         | RGH                | 16   | 1000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | L00046B        | Samples |

| LM3503SQ-35        | NRND   | WQFN         | RGH                | 16   | 1000           | TBD                        | Call TI          | Call TI            | -40 to 85    | L00047B        |         |

| LM3503SQ-35/NOPB   | ACTIVE | WQFN         | RGH                | 16   | 1000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | L00047B        | Samples |

| LM3503SQ-44/NOPB   | ACTIVE | WQFN         | RGH                | 16   | 1000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | L00053B        | Samples |

| LM3503SQX-16/NOPB  | ACTIVE | WQFN         | RGH                | 16   | 4500           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | L00045B        | Samples |

| LM3503SQX-25/NOPB  | ACTIVE | WQFN         | RGH                | 16   | 4500           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | L00046B        | Samples |

| LM3503SQX-35/NOPB  | ACTIVE | WQFN         | RGH                | 16   | 4500           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | L00047B        | Samples |

| LM3503SQX-44/NOPB  | ACTIVE | WQFN         | RGH                | 16   | 4500           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | L00053B        | Samples |

## **PACKAGE OPTION ADDENDUM**

1-Nov-2013

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## PACKAGE MATERIALS INFORMATION

www.ti.com 11-Oct-2013

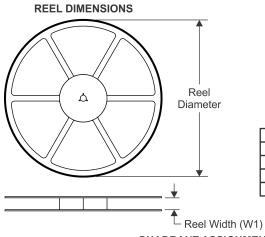

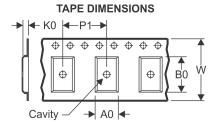

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

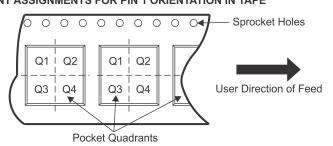

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device             | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM3503ITL-16/NOPB  | DSBGA           | YPA                | 10   | 250  | 178.0                    | 8.4                      | 2.03       | 2.21       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3503ITL-25/NOPB  | DSBGA           | YPA                | 10   | 250  | 178.0                    | 8.4                      | 2.03       | 2.21       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3503ITL-35/NOPB  | DSBGA           | YPA                | 10   | 250  | 178.0                    | 8.4                      | 2.03       | 2.21       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3503ITL-44/NOPB  | DSBGA           | YPA                | 10   | 250  | 178.0                    | 8.4                      | 2.03       | 2.21       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3503ITLX-16/NOPB | DSBGA           | YPA                | 10   | 3000 | 178.0                    | 8.4                      | 2.03       | 2.21       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3503ITLX-25/NOPB | DSBGA           | YPA                | 10   | 3000 | 178.0                    | 8.4                      | 2.03       | 2.21       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3503ITLX-35/NOPB | DSBGA           | YPA                | 10   | 3000 | 178.0                    | 8.4                      | 2.03       | 2.21       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3503ITLX-44/NOPB | DSBGA           | YPA                | 10   | 3000 | 178.0                    | 8.4                      | 2.03       | 2.21       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3503SQ-16/NOPB   | WQFN            | RGH                | 16   | 1000 | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM3503SQ-25/NOPB   | WQFN            | RGH                | 16   | 1000 | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM3503SQ-35        | WQFN            | RGH                | 16   | 1000 | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM3503SQ-35/NOPB   | WQFN            | RGH                | 16   | 1000 | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM3503SQ-44/NOPB   | WQFN            | RGH                | 16   | 1000 | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM3503SQX-16/NOPB  | WQFN            | RGH                | 16   | 4500 | 330.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM3503SQX-25/NOPB  | WQFN            | RGH                | 16   | 4500 | 330.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM3503SQX-35/NOPB  | WQFN            | RGH                | 16   | 4500 | 330.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM3503SQX-44/NOPB  | WQFN            | RGH                | 16   | 4500 | 330.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

www.ti.com 11-Oct-2013

\*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM3503ITL-16/NOPB  | DSBGA        | YPA             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| LM3503ITL-25/NOPB  | DSBGA        | YPA             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| LM3503ITL-35/NOPB  | DSBGA        | YPA             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| LM3503ITL-44/NOPB  | DSBGA        | YPA             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| LM3503ITLX-16/NOPB | DSBGA        | YPA             | 10   | 3000 | 210.0       | 185.0      | 35.0        |

| LM3503ITLX-25/NOPB | DSBGA        | YPA             | 10   | 3000 | 210.0       | 185.0      | 35.0        |

| LM3503ITLX-35/NOPB | DSBGA        | YPA             | 10   | 3000 | 210.0       | 185.0      | 35.0        |

| LM3503ITLX-44/NOPB | DSBGA        | YPA             | 10   | 3000 | 210.0       | 185.0      | 35.0        |

| LM3503SQ-16/NOPB   | WQFN         | RGH             | 16   | 1000 | 210.0       | 185.0      | 35.0        |

| LM3503SQ-25/NOPB   | WQFN         | RGH             | 16   | 1000 | 210.0       | 185.0      | 35.0        |

| LM3503SQ-35        | WQFN         | RGH             | 16   | 1000 | 210.0       | 185.0      | 35.0        |

| LM3503SQ-35/NOPB   | WQFN         | RGH             | 16   | 1000 | 210.0       | 185.0      | 35.0        |

| LM3503SQ-44/NOPB   | WQFN         | RGH             | 16   | 1000 | 210.0       | 185.0      | 35.0        |

| LM3503SQX-16/NOPB  | WQFN         | RGH             | 16   | 4500 | 367.0       | 367.0      | 35.0        |

| LM3503SQX-25/NOPB  | WQFN         | RGH             | 16   | 4500 | 367.0       | 367.0      | 35.0        |

| LM3503SQX-35/NOPB  | WQFN         | RGH             | 16   | 4500 | 367.0       | 367.0      | 35.0        |

| LM3503SQX-44/NOPB  | WQFN         | RGH             | 16   | 4500 | 367.0       | 367.0      | 35.0        |

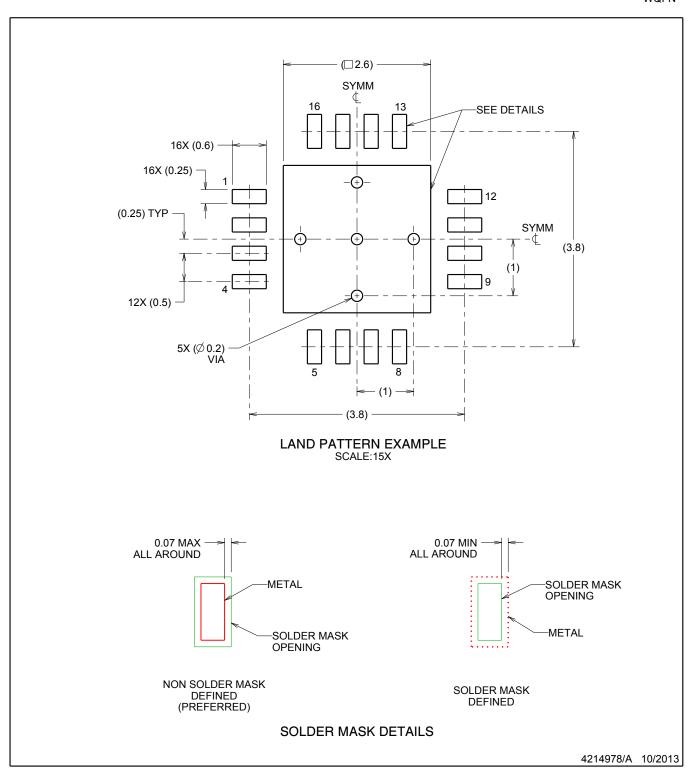

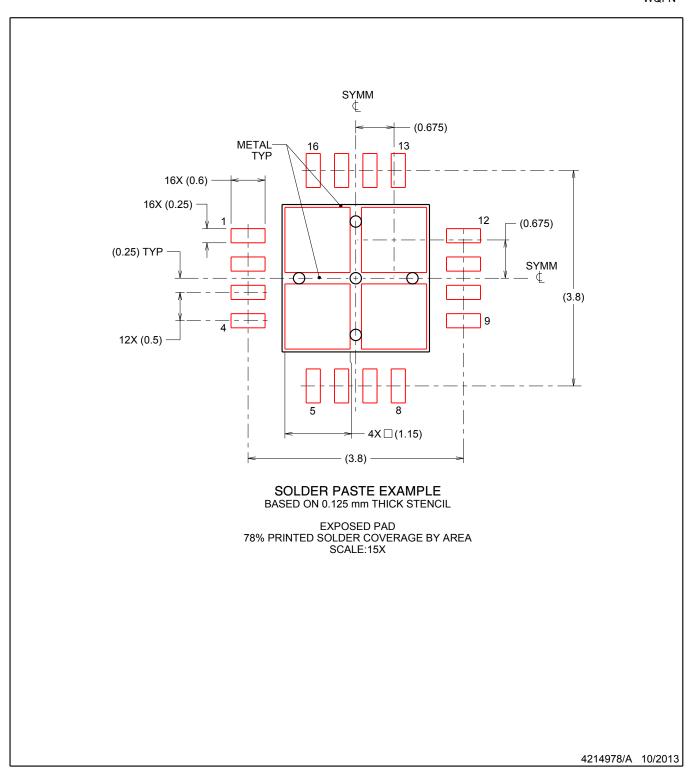

WQFN

#### NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

WQFN

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see QFN/SON PCB application report in literature No. SLUA271 (www.ti.com/lit/slua271).

WQFN

NOTES: (continued)

5. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

B. This drawing is subject to change without notice.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>

# AMEYA360 Components Supply Platform

## **Authorized Distribution Brand:**

## Website:

Welcome to visit www.ameya360.com

## Contact Us:

## > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

## > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

## Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com