- Controlled Baseline

- One Assembly/Test Site, One Fabrication Site

- Enhanced Diminishing Manufacturing Sources (DMS) Support

- Enhanced Product-Change Notification

- Qualification Pedigree<sup>†</sup>

- 21:3 Data Channel Compression at up to 1.36 Gigabits per Second Throughput

- Suited for Point-to-Point Subsystem Communication With Very Low EMI

- 21 Data Channels Plus Clock in Low-Voltage TTL and 3 Data Channels Plus Clock Out Low-Voltage Differential

- Operates From a Single 3.3-V Supply and 250 mW (Typ)

- 5-V Tolerant Data Inputs

- 'LVDS95 Has Rising Clock Edge Triggered Inputs

- Bus Pins Tolerate 6-kV HBM ESD

- Packaged in Thin Shrink Small-Outline Package With 20 Mil Terminal Pitch

- Consumes <1 mW When Disabled</li>

- Wide Phase-Lock Input Frequency Range 20 MHz to 68 MHz

- No External Components Required for PLL

† Component qualification in accordance with JEDEC and industry standards to ensure reliable operation over an extended temperature range. This includes, but is not limited to, Highly Accelerated Stress Test (HAST) or biased 85/85, temperature cycle, autoclave or unbiased HAST, electromigration, bond intermetallic life, and mold compound life. Such qualification testing should not be viewed as justifying use of this component beyond specified performance and environmental limits.

- Inputs Meet or Exceed the Requirements of ANSI EIA/TIA-644 Standard

- Industrial Temperature Qualified

T<sub>A</sub> = −40°C to 85°C

- Replacement for the National DS90CR215

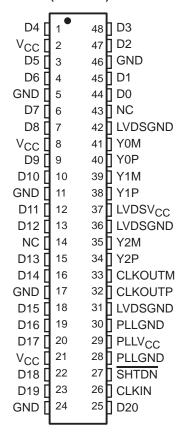

#### DGG PACKAGE (TOP VIEW)

#### description/ordering information

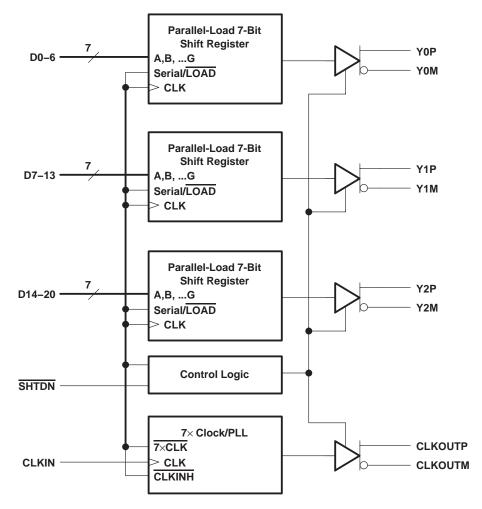

The SN65LVDS95 LVDS serdes (serializer/deserializer) transmitter contains three 7-bit parallel-load serial-out shift registers, a 7× clock synthesizer, and four low-voltage differential signaling (LVDS) line drivers in a single integrated circuit. These functions allow 21 bits of single-ended LVTTL data to be synchronously transmitted over 4 balanced-pair conductors for receipt by a compatible receiver, such as the SN65LVDS96.

When transmitting, data bits D0 through D20 are each loaded into registers of the SN65LVDS95 on the rising edge of the input clock signal (CLKIN). The frequency of CLKIN is multiplied seven times and then used to serially unload the data registers in 7-bit slices. The three serial streams and a phase-locked clock (CLKOUT) are then output to LVDS output drivers. The frequency of CLKOUT is the same as the input clock, CLKIN.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### description/ordering information (continued)

The SN65LVDS95 requires no external components and little or no control. The data bus appears the same at the input to the transmitter and output of the receiver with data transmission transparent to the user(s). The only user intervention is the possible use of the shutdown/clear (SHTDN) active-low input to inhibit the clock and shut off the LVDS output drivers for lower power consumption. A low level on this signal clears all internal registers to a low level.

#### **ORDERING INFORMATION**

| TA            | PACKAGET    |               | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|---------------|-------------|---------------|--------------------------|---------------------|

| -40°C to 85°C | TSSOP - DGG | Tape and reel | SN65LVDS95DGGREP         | 65LVDS95EP          |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

### functional block diagram

SGLS206A - OCTOBER 2003 - REVISED SEPTEMBER 2009

Figure 1. 'LVDS95 Load and Shift Sequences

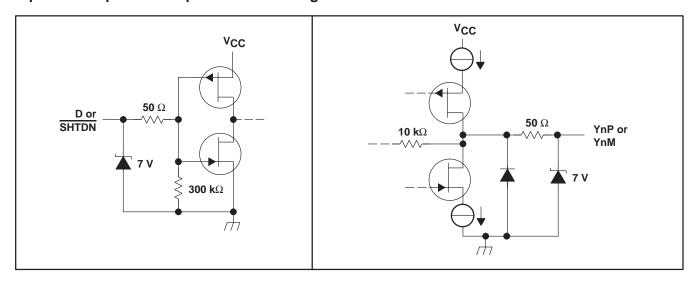

## equivalent input and output schematic diagrams

SGLS206A - OCTOBER 2003 - REVISED SEPTEMBER 2009

## absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)        | 0.5 V to 4 V                     |

|-----------------------------------------------------------|----------------------------------|

| Voltage range at any output terminal, VO                  | 0.5 V to V <sub>CC</sub> + 0.5 V |

| Voltage range at any input terminal, V <sub>1</sub>       | 0.5 V to 5.5 V                   |

| Electrostatic discharge (see Note 2): Bus pins (Class 3A) | 6 KV                             |

| Bus pins (Class 2B)                                       | 400 V                            |

| All pins (Class 3A) .                                     | 6 KV                             |

| All pins (Class 2B) .                                     | 200 V                            |

| Continuous total power dissipation                        | (see Dissipation Rating Table)   |

| Operating free-air temperature range, T <sub>A</sub>      | –40°C to 85°C                    |

| Storage temperature range, T <sub>sta</sub>               |                                  |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 sec  |                                  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR‡            | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------|-----------------------|-----------------------------|-----------------------|-----------------------|

|         | POWER RATING          | ABOVE T <sub>A</sub> = 25°C | POWER RATING          | POWER RATING          |

| DGG     | 1316 mW               | 13.1 mW/°C                  | 724 mW                | 526 mW                |

<sup>‡</sup> This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

#### recommended operating conditions

|                                                | MIN | NOM | MAX | UNIT |

|------------------------------------------------|-----|-----|-----|------|

| Supply voltage, V <sub>CC</sub>                | 3   | 3.3 | 3.6 | V    |

| High-level input voltage, V <sub>IH</sub>      | 2   |     |     | V    |

| Low-level input voltage, V <sub>IL</sub>       |     |     | 8.0 | V    |

| Differential load impedance, Z <sub>L</sub>    | 90  |     | 132 | Ω    |

| Operating free-air temperature, T <sub>A</sub> | -40 |     | 85  | °C   |

NOTES: 1. All voltage values are with respect to the GND terminals.

<sup>2.</sup> This rating is measured using MIL-STD-883C Method, 3015.7.

## electrical characteristics over recommended operating conditions (unless otherwise noted)

|                   | PARAMETER                                                                                       | TEST CONDITIONS                                                                                                       | MIN   | TYP† | MAX   | UNIT |

|-------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| V <sub>IT</sub>   | Input voltage threshold                                                                         |                                                                                                                       |       | 1.4  |       | V    |

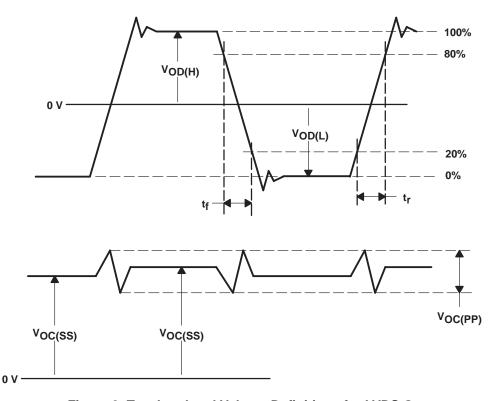

| IVODI             | Differential steady-state output voltage magnitude                                              |                                                                                                                       | 247   |      | 454   |      |

| Δ V <sub>OD</sub> | Change in the steady-state differential output voltage magnitude between opposite binary states | $R_L$ = 100 Ω, See Figure 3                                                                                           |       |      | 50    | mV   |

| Voc(ss)           | Steady-state common-mode output voltage                                                         | Can Figure 2                                                                                                          | 1.125 |      | 1.375 | V    |

| VOC(PP)           | Peak-to-peak common-mode output voltage                                                         | See Figure 3                                                                                                          |       | 80   | 150   | mV   |

| lн                | High-level input current                                                                        | V <sub>IH</sub> = V <sub>CC</sub>                                                                                     |       |      | 20    | μΑ   |

| I <sub>IL</sub>   | Low-level input current                                                                         | V <sub>IL</sub> = 0 V                                                                                                 |       |      | ±10   | μΑ   |

|                   | Object since it autout assessed                                                                 | VOY = 0 V                                                                                                             |       |      | ±24   | mA   |

| los               | Short-circuit output current                                                                    | V <sub>OD</sub> = 0 V                                                                                                 |       |      | ±12   | mA   |

| loz               | High-impedance state output current                                                             | $V_O = 0 V \text{ to } V_{CC}$                                                                                        |       |      | ±10   | μΑ   |

|                   |                                                                                                 | Disabled, all inputs at GND                                                                                           |       |      | 280   | μΑ   |

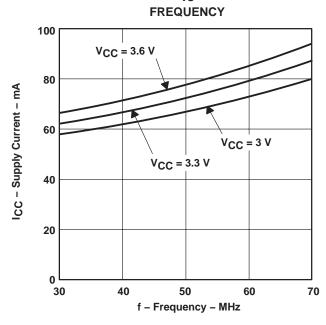

| ICC(AVG)          | Quiescent current (average)                                                                     | Enabled, R <sub>L</sub> = 100 $\Omega$ (4 places),<br>Worst-case pattern (see Figure 4),<br>t <sub>C</sub> = 15.38 ns |       | 85   | 110   | mA   |

| Ci                | Input capacitance                                                                               |                                                                                                                       |       | 3    |       | pF   |

<sup>†</sup> All typical values are  $V_{CC}$  = 3.3 V,  $T_A$  = 25°C.

## timing requirements

|                 |                                                                    | MIN               | NOM            | MAX               | UNIT |

|-----------------|--------------------------------------------------------------------|-------------------|----------------|-------------------|------|

| t <sub>C</sub>  | Input clock period                                                 | 14.7              | t <sub>C</sub> | 50                | ns   |

| t <sub>W</sub>  | High-level input clock pulse width duration                        | 0.4t <sub>C</sub> |                | 0.6t <sub>C</sub> | ns   |

| t <sub>t</sub>  | Input signal transition time                                       |                   |                | 5                 | ns   |

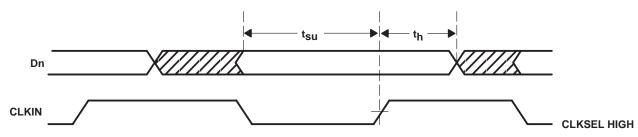

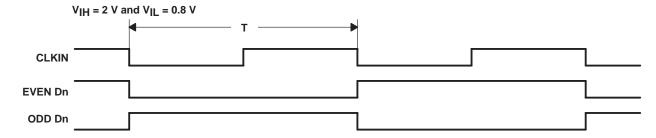

| t <sub>su</sub> | Data setup time, D0 through D27 before CLKIN↑ ('95) (see Figure 2) | 3                 |                |                   | ns   |

| th              | Data hold time, D0 through D27 after CLKIN↑ ('95) (see Figure 2)   | 1.5               |                |                   | ns   |

SGLS206A - OCTOBER 2003 - REVISED SEPTEMBER 2009

## switching characteristics over recommended operating conditions (unless otherwise noted)

|                  | PARAMETER                                                                       | TEST CONDITIONS                                                                                | MIN                     | TYP†                                                                                                            | MAX                     | UNIT |

|------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------|------|

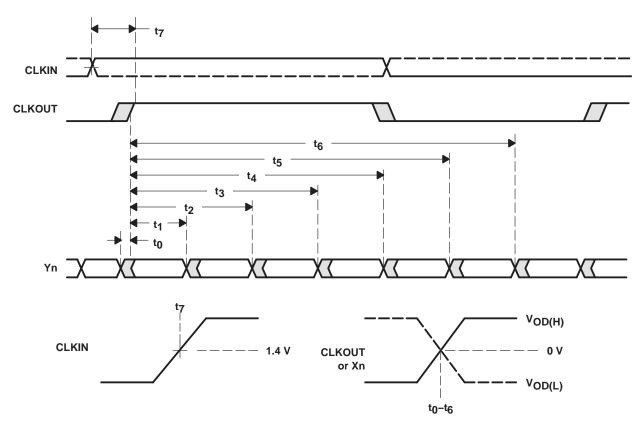

| t <sub>0</sub>   | Delay time, CLKOUT serial bit position 0                                        |                                                                                                | -0.20                   | 0                                                                                                               | 0.20                    | ns   |

| t <sub>1</sub>   | Delay time, CLKOUT↑ serial bit position 1                                       |                                                                                                | 1/7t <sub>C</sub> -0.20 |                                                                                                                 | 1/7t <sub>C</sub> +0.20 | ns   |

| t <sub>2</sub>   | Delay time, CLKOUT↑ serial bit position 2                                       |                                                                                                | 2/7t <sub>C</sub> -0.20 |                                                                                                                 | 2/7t <sub>C</sub> +0.20 | ns   |

| t <sub>3</sub>   | Delay time, CLKOUT↑ serial bit position 3                                       | $t_{\rm C} = 15.38 \text{ ns } (\pm 0.2\%),$                                                   | 3/7t <sub>C</sub> -0.20 |                                                                                                                 | 3/7t <sub>C</sub> +0.20 | ns   |

| t <sub>4</sub>   | Delay time, CLKOUT↑ serial bit position 4                                       | Input clock jitter  < 50 ps‡,<br>  See Figure 5                                                | 4/7t <sub>C</sub> -0.20 |                                                                                                                 | 4/7t <sub>C</sub> +0.20 | ns   |

| t <sub>5</sub>   | Delay time, CLKOUT↑ serial bit position 5                                       | 3                                                                                              | 5/7t <sub>C</sub> -0.20 |                                                                                                                 | 5/7t <sub>C</sub> +0.20 | ns   |

| t <sub>6</sub>   | Delay time, CLKOUT↑ serial bit position 6                                       |                                                                                                | 6/7t <sub>C</sub> -0.20 |                                                                                                                 | 6/7t <sub>C</sub> +0.20 | ns   |

| tsk(o)           | Output skew, $t_{\rm n}$ –n/7 $t_{\rm C}$                                       |                                                                                                | -0.20                   |                                                                                                                 | 0.20                    | ns   |

| t <sub>7</sub>   | Delay time, CLKIN <sup>↑</sup> to CLKOUT <sup>↑</sup>                           | $t_{\rm C}$ = 15.38 ns (±0.2%),<br> Input clock jitter  < 50 ps <sup>‡</sup> ,<br>See Figure 5 |                         | 4.2                                                                                                             |                         | ns   |

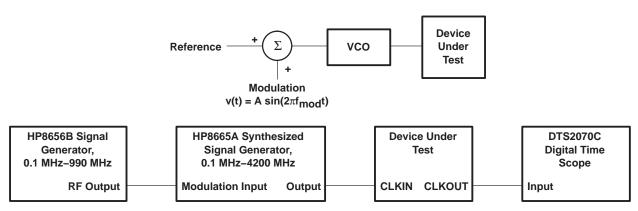

|                  | Output also to south "Its &                                                     | $t_{\rm C}$ = 15.38 ns + 0.75 sin(2 $\pi$ 500E3t) $\pm$ 0.05 ns, See Figure 6                  |                         | ±80                                                                                                             |                         | ps   |

| ∆tC(O)           | Output clock cycle-to-cycle jitter§                                             | $t_{\rm C}$ = 15.38 ns + 0.75 sin(2 $\pi$ 2E6t)<br>±0.05 ns, See Figure 6                      |                         | 20 5/7t <sub>C</sub> +0.20<br>20 6/7t <sub>C</sub> +0.20<br>20 0.20<br>4.2<br>±80<br>±300<br>4/7 t <sub>C</sub> | ps                      |      |

| t <sub>W</sub>   | High-level output clock pulse duration                                          |                                                                                                |                         | 4/7 t <sub>C</sub>                                                                                              |                         | ns   |

| t <sub>t</sub>   | Differential output voltage transition time (t <sub>r</sub> or t <sub>f</sub> ) | See Figure 3                                                                                   | 260                     | 700                                                                                                             | 1500                    | ps   |

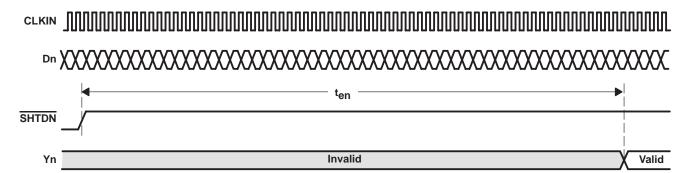

| t <sub>en</sub>  | Enable time, SHTDN↑ to phase lock (Yn valid)                                    | See Figure 7                                                                                   |                         | 1                                                                                                               |                         | ms   |

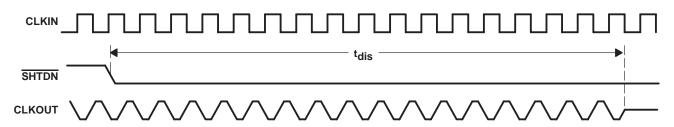

| <sup>t</sup> dis | Disable time, SHTDN↓ to off-state (CLKOUT low)                                  | See Figure 8                                                                                   |                         | 250                                                                                                             |                         | ns   |

<sup>†</sup> All typical values are  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

#### PARAMETER MEASUREMENT INFORMATION

NOTE: All input timing is defined at 1.4 V on an input signal with a 10% to 90% rise or fall time of less than 5 ns.

Figure 2. Setup and Hold Time Definition

<sup>‡ |</sup>Input clock jitter| is the magnitude of the change in the input clock period.

<sup>§</sup> The output clock jitter is the change in the output clock period from one cycle to the next cycle observed over 15,000 cycles.

#### PARAMETER MEASUREMENT INFORMATION

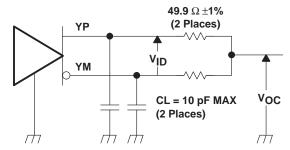

NOTE: The lumped instrumentation capacitance for any single ended voltage measurement is less than or equal to 10 pF. When making measurements at YP or YM, the complementary output shall be similarly loaded.

Figure 3. Test Load and Voltage Definitions for LVDS Outputs

Figure 4. Worst-Case<sup>‡</sup> Power Test Pattern

<sup>‡</sup> The worst-case test pattern produces nearly the maximum switching frequency for all of the LV-TTL outputs.

#### PARAMETER MEASUREMENT INFORMATION

Figure 5. Timing Definitions

Figure 6. Clock Jitter Test Setup

#### PARAMETER MEASUREMENT INFORMATION

Figure 7. Enable Time Measurement Definition

Figure 8. Disable Time Measurement Definition

#### TYPICAL CHARACTERISTICS

# WORST-CASE SUPPLY CURRENT

Figure 9

#### APPLICATION INFORMATION

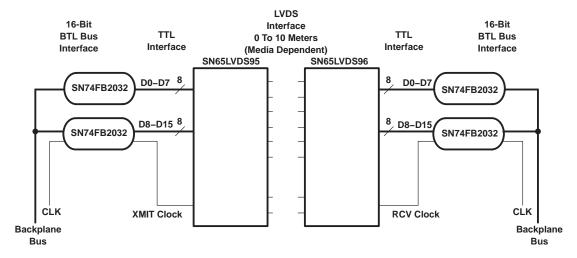

#### 16-bit bus extension

In a 16-bit bus application (Figure 10), TTL data and clock coming from bus transceivers that interface the backplane bus arrive at the Tx parallel inputs of the LVDS serdes transmitter. The clock associated with the bus is also connected to the device. The on-chip PLL synchronizes this clock with the parallel data at the input. The data is then multiplexed into three different line drivers which perform the TTL to LVDS conversion. The clock is also converted to LVDS and presented to a separate driver. This synchronized LVDS data and clock at the receiver, which recovers the LVDS data and clock, performs a conversion back to TTL. Data is then demultiplexed into a parallel format. An on-chip PLL synchronizes the received clock with the parallel data, and then all are presented to the parallel output port of the receiver.

Figure 10. 16-Bit Bus Extension

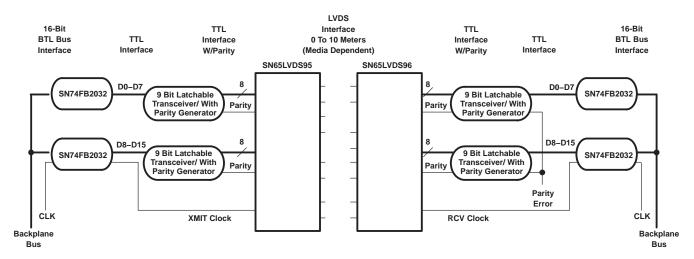

#### 16-bit bus extension with parity

In the previous application we did not have a checking bit that would provide assurance that the data crosses the link. If we add a parity bit to the previous example, we would have a diagram similar to the one in Figure 11. The device following the SN74FB2032 is a low cost parity generator. Each transmit-side transceiver/parity generator takes the LVTTL data from the corresponding transceiver, performs a parity calculation over the byte, and then passes the bits with its calculated parity value on the parallel input of the LVDS serdes transmitter. Again, the on-chip PLL synchronizes this transmit clock with the eighteen parallel bits (16 data + 2 parity) at the input. The synchronized LVDS data/parity and clock arrive at the receiver.

The receiver performs the conversion from LVDS to LVTTL and the transceiver/parity generator performs the parity calculations. These devices compare their corresponding input bytes with the value received on the parity bit. The transceiver/parity generator will assert its parity error output if a mismatch is detected.

#### APPLICATION INFORMATION

Figure 11. 16-Bit Bus Extension With Parity

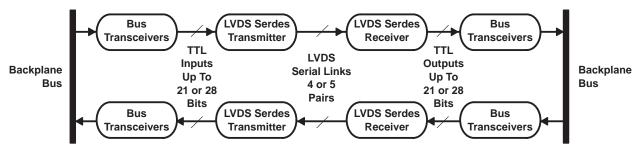

#### low cost virtual backplane transceiver

Figure 12 represents LVDS serdes in an application as a virtual backplane transceiver (VBT). The concept of a VBT can be achieved by implementing individual LVDS serdes chipsets in both directions of subsystem serialized links.

Depending on the application, the designer will face varying choices when implementing a VBT. In addition to the devices shown in Figure 12, functions such as parity and delay lines for control signals could be included. Using additional circuitry, half-duplex or full-duplex operation can be achieved by configuring the clock and control lines properly.

The designer may choose to implement an independent clock oscillator at each end of the link and then use a PLL to synchronize LVDS serdes's parallel I/O to the backplane bus. Resynchronizing FIFOs may also be required.

Figure 12. Virtual Backplane Transceiver

#### PACKAGE OPTION ADDENDUM

www.ti.com 23-Sep-2009

#### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package<br>Type | Package<br>Drawing | Pins P | ackage<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|------------|-----------------|--------------------|--------|---------------|---------------------------|------------------|------------------------------|

| SN65LVDS95DGGREP | ACTIVE     | TSSOP           | DGG                | 48     | 2000          | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| V62/04643-01XE   | ACTIVE     | TSSOP           | DGG                | 48     | 2000          | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND**: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF SN65LVDS95-EP:

Catalog: SN65LVDS95

Automotive: SN65LVDS95-Q1

NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Automotive Q100 devices qualified for high-reliability automotive applications targeting zero defects

## PACKAGE MATERIALS INFORMATION

www.ti.com 23-Sep-2009

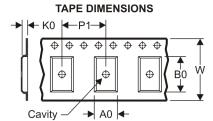

## TAPE AND REEL INFORMATION

| _ |    |                                                           |

|---|----|-----------------------------------------------------------|

|   | Α0 | Dimension designed to accommodate the component width     |

|   |    | Dimension designed to accommodate the component length    |

|   | K0 | Dimension designed to accommodate the component thickness |

|   | W  | Overall width of the carrier tape                         |

| Γ | P1 | Pitch between successive cavity centers                   |

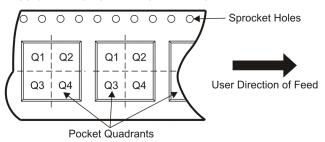

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN65LVDS95DGGREP | TSSOP           | DGG                | 48 | 2000 | 330.0                    | 24.4                     | 8.6        | 15.8       | 1.8        | 12.0       | 24.0      | Q1               |

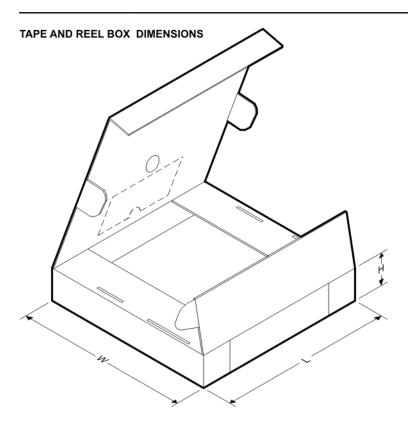

www.ti.com 23-Sep-2009

#### \*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| SN65LVDS95DGGREP | TSSOP        | DGG             | 48   | 2000 | 346.0       | 346.0      | 41.0        |  |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Applications Products Amplifiers** amplifier.ti.com Audio www.ti.com/audio Data Converters Automotive www.ti.com/automotive dataconverter.ti.com DLP® Products Broadband www.dlp.com www.ti.com/broadband DSP Digital Control dsp.ti.com www.ti.com/digitalcontrol Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Military Interface www.ti.com/military interface.ti.com Optical Networking Logic logic.ti.com www.ti.com/opticalnetwork Power Mgmt power.ti.com Security www.ti.com/security Telephony Microcontrollers microcontroller.ti.com www.ti.com/telephony Video & Imaging www.ti-rfid.com www.ti.com/video RF/IF and ZigBee® Solutions www.ti.com/lprf Wireless www.ti.com/wireless

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated

# AMEYA360 Components Supply Platform

## **Authorized Distribution Brand:**

## Website:

Welcome to visit www.ameya360.com

## Contact Us:

## > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

## > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

## Customer Service :

Email service@ameya360.com

## Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com