July 2009

# SG6105A Power Supply Supervisor + Regulator + PWM

### **Features**

- PC Half-Bridge (or 494) Power Supply Supervisor + two 431 + PWM

- High Integration with Few External Components

- Over-Voltage Protection for 3.3V, 5V, and 12V

- Under-Voltage Protection for 3.3V, 5V, and 12V

- Under-Voltage Protection for -12V and/or -5V

- Over-Power and Short-Circuit Protection

- Power-Down Warning Circuitry

- Power-Good Circuitry

- Delay Time for PSON and PG Signal

- Remote ON/OFF Function

- On-Chip Oscillator and Error Amplifier

- Two Shunt Regulators for 3.3V and 5V-Standby

- Latching PWM for Cycle-by-Cycle Switching

- Push-Pull PWM Operation and Totem Pole Outputs

- Soft-Start and Maximum 93% Duty Cycle

### Description

SG6105A controller is designed for switching-mode power supplies for desktop PCs. It provides all the functions necessary to monitor and control the output of the power supply. Remote ON/OFF control, power-good circuitry, and protection features against over-voltage and over-power are implemented. It directly senses all the output rails for OVP without the need for external dividers. An innovative AC-signal sampling circuitry provides a sufficient power-down warning signal for PG.

A built-in timer generates accurate timing for the control circuit, including the PS-off delay. The cycle-by-cycle PWM switching prevents the power transformer from saturation and ensures the fastest response for the short-circuit protection, which greatly reduces stress for power transistors. Two internal precision TL431 shunt regulators provide stable reference voltage and a driver for 3.3V and 5V standby regulation.

Utilizing minimum external components, the SG6105A includes the functions for push-pull and/or half-bridge topology, decreasing production cost and PCB space, and increasing the MTBF for power supply.

### **Applications**

Switching mode power supply for computers:

- AT

- NLX

- SFX (micro-ATX)

# **Ordering Information**

| Part<br>Number | Operating<br>Temperature<br>Range | © Eco Status Package |                                       | Packing Method |

|----------------|-----------------------------------|----------------------|---------------------------------------|----------------|

| SG6105ADZ      | -40 to +105°C                     | RoHS                 | 20-pin Dual In-Line Package (DIP)     | Tube           |

| SG6105ADY      | -40 to +105°C                     | Green                | een 20-pin Dual In-Line Package (DIP) |                |

Por Fairchild's definition of Eco Status, please visit: <a href="http://www.fairchildsemi.com/company/green/rohs\_green.html">http://www.fairchildsemi.com/company/green/rohs\_green.html</a>.

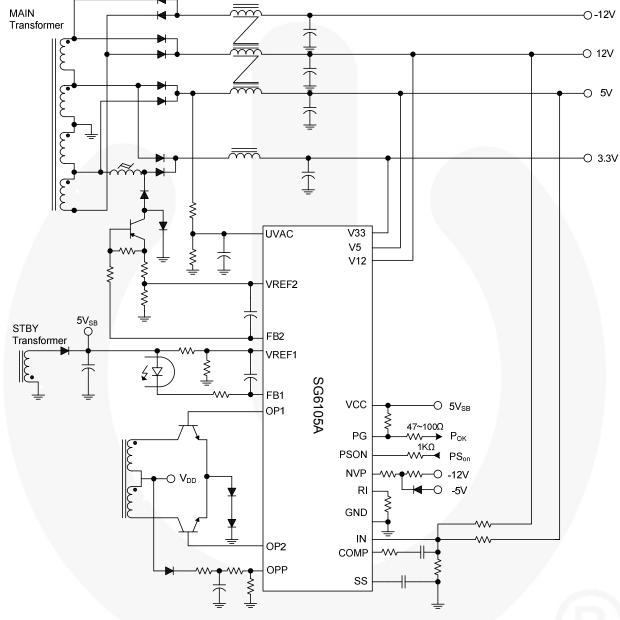

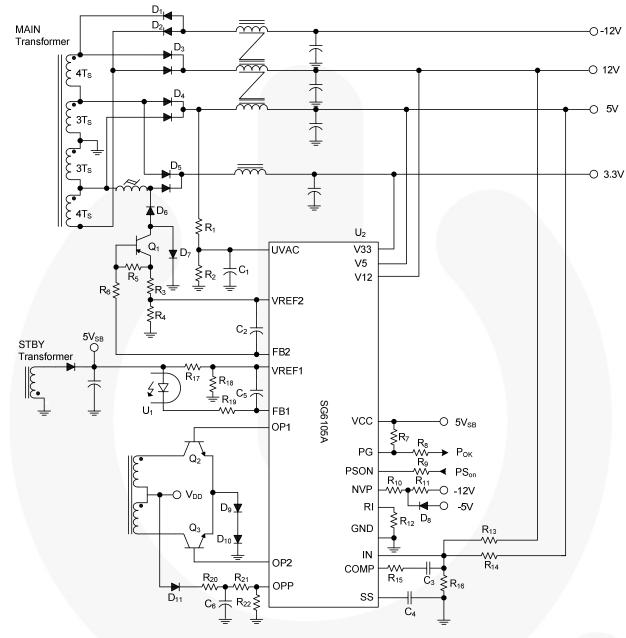

# **Application Diagram**

Figure 1. Typical Application

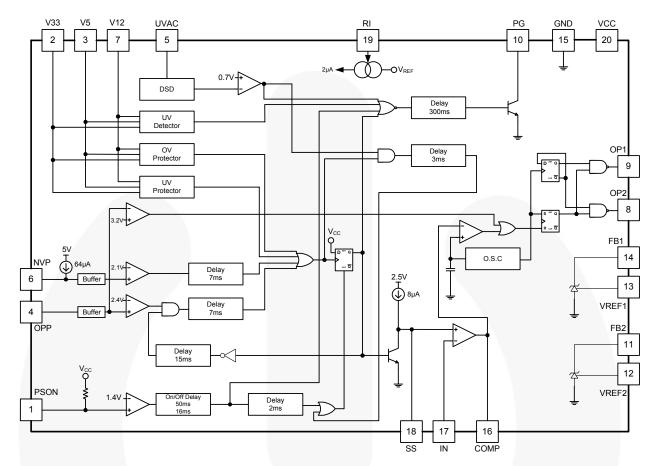

# **Block Diagram**

Figure 2. Function Block Diagram

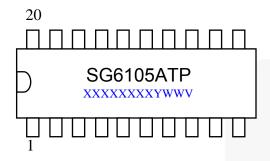

# **Marking Information**

Marking for SG6105ADZ (Pb-free)

%Marking for SG6105ADY(Green compound)

T : D = DIP

P: Z = Lead Free Null=Regular Ppackage XXXXXXXX: Wafer Lot Y: Year; WW: Week

Y: Year; WW: Week

V: Assembly Location

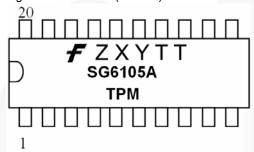

F- Fairchild Logo

Z- Plant Code

X- 1 Digit Year Code

Y- 1 Digit Week Code

TT: 2 Digits Die Run Code

T: Package Type (D=DIP)

P: Y:Green Package

M: Manufacture Flow Code

Figure 3. Top Mark

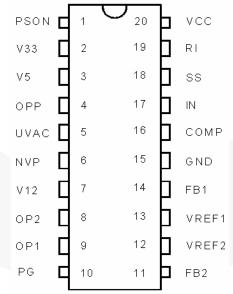

# **Pin Configuration**

Figure 4. Pin Configuration (Top View)

# Pin Definitions

| Pin# | Name    | Description                                                                                                                                                                                             |  |  |  |

|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | PSON    | Remote on/off logic input for CPU or controller. Turn on/off the PWM output after the 7.5ms / 26ms delay.  PSON=0, the main SMPS is operational.  PSON =1, the main SMPS is off and the latch is reset. |  |  |  |

| 2    | V33     | 3.3V over-voltage/under-voltage control sense input.                                                                                                                                                    |  |  |  |

| 3    | V5      | 5V over-voltage/under-voltage control sense input.                                                                                                                                                      |  |  |  |

| 4    | OPP     | Over-power sense input. This pin is connected to driver transformer or the output of current transformer. When not in use, this pin should be grounded.                                                 |  |  |  |

| 5    | UVAC    | AC fail detection. Detect main AC voltage under-voltage and/or failure.                                                                                                                                 |  |  |  |

| 6    | NVP     | The protection input for negative output, such as -12V and/or -5V. Trip voltage=2.1V.                                                                                                                   |  |  |  |

| 7    | V12     | 12V over-voltage/under-voltage control sense input.                                                                                                                                                     |  |  |  |

| 9/8  | OP1/OP2 | The totem-pole output drivers of push-pull PWM. The outputs are enabled (LOW) only when the NAND gate inputs are HIGH. The maximum duty cycle on an output (OP1 or OP2) is 46%.                         |  |  |  |

| 10   | PG      | Power-good logic output, 0 or 1 (open-collector). PG=1, the power is good for operation. The PG delay is 300ms.                                                                                         |  |  |  |

| 11   | FB2     | Output for second converter regulation loop.                                                                                                                                                            |  |  |  |

| 12   | VREF2   | Reference comparison input for second converter regulation loop, 2.5V.                                                                                                                                  |  |  |  |

| 13   | VREF1   | Reference comparison input for first converter regulation loop, 2.5V.                                                                                                                                   |  |  |  |

| 14   | FB1     | Output for first converter regulation loop.                                                                                                                                                             |  |  |  |

| 15   | GND     | Ground.                                                                                                                                                                                                 |  |  |  |

| 16   | COMP    | Error amplifier output and the input of the PWM comparator.                                                                                                                                             |  |  |  |

| 17   | IN      | The negative input of error amplifier. The positive input of error amplifier is a 2.5V reference voltage.                                                                                               |  |  |  |

| 18   | SS      | Soft-start, settable through an external capacitor. The current source output at this pin is 8µA and the voltage is clamped at 2.5V.                                                                    |  |  |  |

| 19   | RI      | Connected to external resistor for the reference setting. $R_i$ =75k $\Omega$ .                                                                                                                         |  |  |  |

| 20   | VCC     | Supply voltage. 4.5V ~ 5.5V connected to 5V-standby.                                                                                                                                                    |  |  |  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                                     | Min.                   | Max. | Unit |      |

|------------------|---------------------------------------------------------------|------------------------|------|------|------|

| V <sub>CC</sub>  | DC Supply Voltage at Pin 20                                   |                        |      | 16   | V    |

| I <sub>OUT</sub> | Output Current at PG, Fb1, F                                  | b2 Pins                |      | 30   | mA   |

|                  | V12, OP1, OP2, FB1, FB2, S                                    | S                      | -0.3 | 16.0 | V    |

| VPIN             | PSON, V33, V5, VREF1, VREF2, OPP, UVAC, RI, NVP, IN, COMP, PG |                        | -0.3 | 7.0  | V    |

| D                | Power Dissipation                                             | (T <sub>A</sub> =25°C) |      | 1.5  | W    |

| P <sub>D</sub>   |                                                               | (T <sub>A</sub> =90°C) |      | 0.5  | VV   |

| T <sub>STG</sub> | Storage Temperature Range                                     |                        | -55  | +150 | °C   |

| $\theta_{JA}$    | Thermal Resistance, Junction-To-Air                           |                        |      | 82.5 | °C/W |

| TJ               | Operating Junction Temperature                                |                        |      | +150 | °C   |

| T <sub>A</sub>   | Operating Ambient Temperature                                 |                        | -30  | +125 | °C   |

| T <sub>L</sub>   | Lead Temperature (Soldering                                   | g, 10 Seconds)         |      | +260 | °C   |

| ESD              | Human Body Model, JESD22                                      | ?-A114                 |      | 3    | KV   |

### Notes:

- 1. All voltage values, except differential voltages, are given with respect to GND pin.

- 2. Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol         | Parameter                           | Min. | Max. | Unit |

|----------------|-------------------------------------|------|------|------|

| T <sub>A</sub> | Operating Ambient Temperature Range | -40  | +105 | °C   |

## **Electrical Characteristics**

$V_{CC}$ =5V,  $T_A$ = 25°C,  $R_I$ =75K $\Omega$ , unless noted operating specs.

| Symbol                 | Parameter                                                                  |                                              | Conditions                     | Min.  | Тур.  | Max. | Units |

|------------------------|----------------------------------------------------------------------------|----------------------------------------------|--------------------------------|-------|-------|------|-------|

| Icc                    | Total Supply Current                                                       |                                              | PG High                        |       | 5     | 10   | mA    |

|                        |                                                                            | 3.3V                                         |                                | 3.9   | 4.1   | 4.3  | V     |

| $V_{OVP}$              | Over-Voltage Protection                                                    | 5.0V                                         |                                | 5.8   | 6.1   | 6.5  |       |

|                        |                                                                            | 12.0V                                        |                                | 13.9  | 14.5  | 14.9 |       |

|                        |                                                                            | 3.3V                                         |                                | 2.0   | 2.6   | 2.8  |       |

| $V_{UVP}$              | Under-Voltage Protection                                                   | 5.0V                                         |                                | 3.0   | 3.6   | 3.9  | V     |

|                        |                                                                            | 12.0V                                        |                                | 6.0   | 7.2   | 8.0  |       |

|                        | Under-Voltage Sense for PG                                                 | 3.3V                                         |                                | 2.5   | 2.8   | 3.0  |       |

| $V_{\text{UVS}}$       | Low                                                                        | 5.0V                                         |                                | 4.0   | 4.3   | 4.5  | V     |

|                        |                                                                            | 12.0V                                        |                                | 9.4   | 10.1  | 10.4 |       |

| $V_{OPP}$              | Over-Power Protection<br>(With T <sub>OPP</sub> Delay Time) <sup>(3)</sup> |                                              | V <sub>UVAC</sub> =1.5V        | 2.25  | 2.32  | 2.39 | V     |

| $V_{OPPH}$             | Over-Power Protection<br>(Without Delay Time)                              |                                              |                                | 3.0   | 3.2   | 3.4  | V     |

| Vx                     | Disable Under-Voltage / Over-Power Protection Threshold                    |                                              |                                | 0.2   | 0.3   | 0.4  | V     |

| $V_{NVP}$              | Negative Voltage Protection:<br>Voltage Level                              |                                              |                                | 2.0   | 2.1   | 2.2  | V     |

| I <sub>NVP</sub>       | Negative Voltage Protection:<br>Source Current                             |                                              |                                | 63    | 67    | 71   | μA    |

| T <sub>OVP</sub>       | Timing for Over-Voltage Protein                                            | ction                                        |                                | 0.37  | 0.70  | 1.35 | ms    |

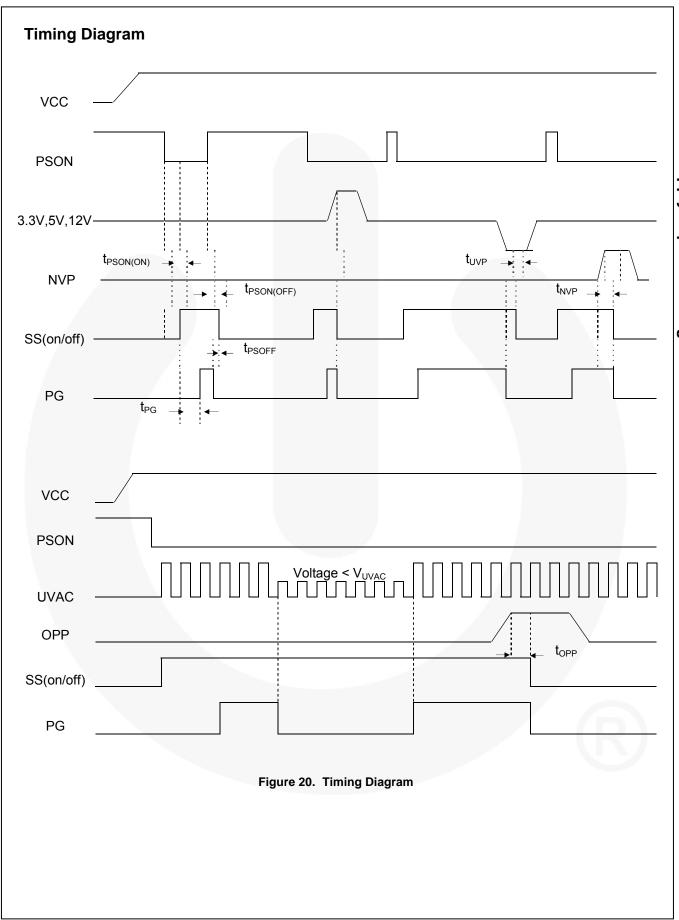

| T <sub>UVP</sub>       | Timing for Under-Voltage Prote                                             | ection                                       |                                | 0.80  | 2.40  | 3.75 | ms    |

| T <sub>UVS</sub>       | Timing for Under-Voltage Sens                                              | se for                                       |                                | 0.37  | 1.20  | 1.88 | ms    |

| T <sub>OPP</sub>       | Timing for Over-Power Protect                                              | ion                                          |                                | 5     | 7     | 9    | ms    |

| T <sub>NVP</sub>       | Timing for Negative Voltage Pr                                             |                                              | 3.3                            | 7.0   | 10.2  | Ms   |       |

| Shunt Re               | gulator Section Current                                                    |                                              |                                |       |       |      |       |

| $V_{REF}$              | Reference Voltage                                                          | I <sub>FB</sub> =0.5mA, T <sub>A</sub> =25°C | 2.475                          | 2.500 | 2.525 | V    |       |

| V <sub>DEV, I</sub>    | Deviation of V <sub>REF</sub> Over FB Current <sup>(4)</sup>               |                                              | I <sub>FB</sub> =0.5mA to 10mA |       |       | 20   | mV    |

| V <sub>DEV, T</sub>    | Deviation of V <sub>REF</sub> Over Temperature <sup>(4)</sup>              |                                              |                                |       | 10    | 30   | mV    |

| R <sub>EGLI-FB</sub>   | Line Regulation <sup>(4)</sup>                                             |                                              | $4 \le V_{FB} \le 15V$         |       | 1     |      | mV/V  |

| I <sub>OUT-FB</sub> ** | Output Sinking Current Capab                                               | V <sub>FB</sub> =2V                          | 10                             |       |       | mA   |       |

### Notes:

- V<sub>OPPS</sub>=(2/3) x V<sub>OPP</sub> + (1/3) x V<sub>UVAC</sub>. Not tested in production.

Continued on following page...

# **Electrical Characteristics** (Continued)

$V_{CC}$ =5V,  $T_A$ = 25°C,  $R_I$ =75K $\Omega$ , unless noted operating specs.

| Symbol                  | Parameter                                    | Conditions                             | Min. | Тур. | Max. | Units |

|-------------------------|----------------------------------------------|----------------------------------------|------|------|------|-------|

| Power-God               | od Section                                   | ,                                      |      | 1    | •    | 1     |

| T <sub>PG</sub>         | Timing for PG Delay                          | R <sub>I</sub> =75kΩ                   | 200  | 300  | 400  | ms    |

| $V_{UVAC}$              | U <sub>VAC</sub> Voltage Sense for PG        |                                        | 0.68 | 0.70 | 0.72 | V     |

| T <sub>R</sub>          | Power-Good Output Rising Time <sup>(5)</sup> | C <sub>L</sub> =100pF, Pull 2.2K to 5V |      | 1    | 3    | μs    |

| T <sub>F</sub>          | Power-Good Falling Time <sup>(5)</sup>       | C <sub>L</sub> =100pF, Pull 2.2K to 5V |      | 300  | 500  | ns    |

| $V_{\text{OL2}}$        | Power-Good Output<br>Saturation Level        | I <sub>PG</sub> =5mA                   |      |      | 0.5  | V     |

| I <sub>ON2</sub>        | Power-Good Leakage<br>Current Collector      | V <sub>PG</sub> =5V                    |      |      | 1    | μA    |

| Remote Or               | n/Off Section                                |                                        |      |      |      |       |

| V <sub>IH</sub>         | High-Level Input Voltage                     |                                        | 2    |      |      | V     |

| V <sub>IL</sub>         | Low-Level Input Voltage                      |                                        |      |      | 0.8  | V     |

| V <sub>HYSTERESIS</sub> | PSON Input Hysteresis<br>Voltage             |                                        | 0.3  |      |      | V     |

| I <sub>PSON</sub>       | Remote Input Driving<br>Current              |                                        |      |      | 0.5  | mA    |

| T <sub>PSON(ON)</sub>   | Timing PSON to On                            | $R_i$ =75k $\Omega$                    | 38   | 50   | 62   | ms    |

| T <sub>PSON(OFF)</sub>  | Timing PSON to Off (PS-off)                  | $R_i$ =75k $\Omega$                    | 8    | 16   | 24   | ms    |

| T <sub>PSOFF</sub>      | Timing PG Low to Power Off                   | $R_I$ =75k $\Omega$                    | 1.5  | 2.0  | 6.3  | ms    |

| Error Ampl              | lifier Section                               |                                        |      |      |      |       |

| V <sub>2.5</sub>        | Reference Voltage                            | T <sub>A</sub> =25°C                   | 2.46 | 2.50 | 2.54 | V     |

| I <sub>IB</sub>         | Input Bias Current <sup>(5)</sup>            |                                        |      |      | 0.1  | μA    |

| A <sub>VOL</sub>        | Open-Loop Voltage Gain <sup>(5)</sup>        |                                        | 50   | 60   |      | dB    |

| BW                      | Unity Gain Bandwidth <sup>(5)</sup>          |                                        | 0.3  | 1.0  |      | MHz   |

| PSRR                    | Power Supply Rejection Ratio <sup>(5)</sup>  |                                        | 50   |      |      | dB    |

| Oscillator :            | Section                                      |                                        |      |      |      |       |

| f <sub>OSC</sub>        | PWM Frequency                                | $R_I=75k\Omega$                        | 62   | 65   | 68   | KHz   |

| Soft-Start S            | Section                                      |                                        |      |      |      |       |

| I <sub>SS</sub>         | Charge Current                               |                                        | 7    | 8    | 9    | μA    |

| Comparato               | or Section                                   |                                        | ı    |      |      |       |

| DC                      | Duty Cycle                                   |                                        | 85   |      | 93   | %     |

| PWM Outp                |                                              |                                        | ·    |      |      |       |

| V <sub>OL</sub>         | Output Voltage Low                           | I <sub>O</sub> =20mA                   |      |      | 0.8  | V     |

| V <sub>OH</sub>         | Output Voltage High                          | V12=12V                                | 4    |      |      | V     |

| Ro                      | Output Impedance of V <sub>OH</sub>          |                                        | 1.5  |      | 3.3  | ΚΩ    |

### Note:

5. Not tested in production.

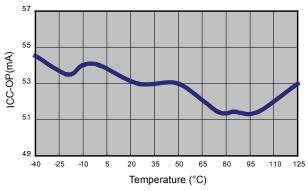

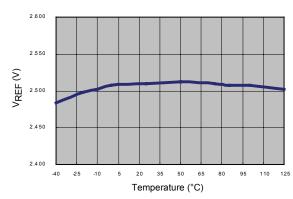

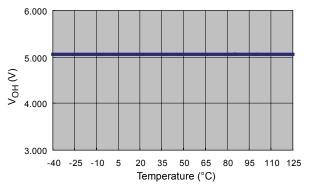

# **Typical Performance Characteristics**

Figure 5. Operating Supply Current vs. Temperature

Figure 6. Reference Voltage vs. Temperature

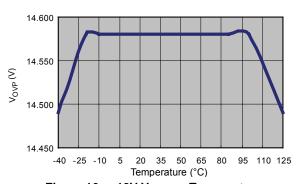

Figure 7. PWM Output Voltage vs. Temperature

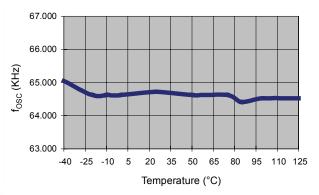

Figure 8. Frequency vs. Temperature

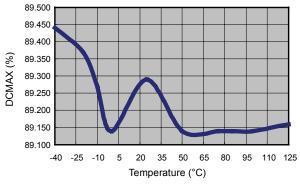

Figure 9. MAX Duty Cycle vs. Temperature

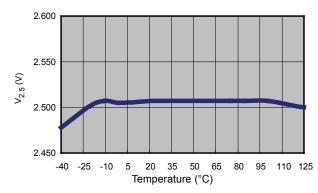

Figure 10. Reference Voltage vs. Temperature

# **Typical Performance Characteristics** (Continued)

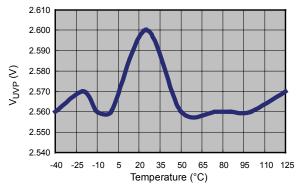

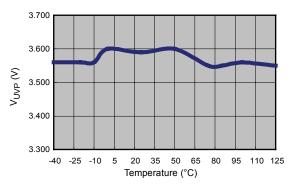

Figure 11. 3.3V V<sub>UVP</sub> vs. Temperature

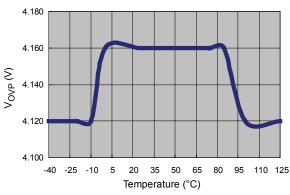

Figure 12. 3.3V V<sub>OVP</sub> vs. Temperature

Figure 13. 5V V<sub>UVP</sub> vs. Temperature

Figure 14. 5V V<sub>OVP</sub> vs. Temperature

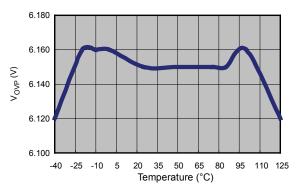

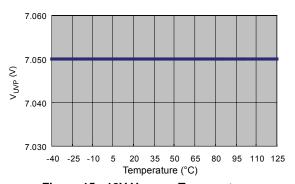

Figure 15. 12V  $V_{\text{UVP}}$  vs. Temperature

Figure 16. 12V V<sub>OVP</sub> vs. Temperature

# **Functional Description**

Protection against over-voltage, short-circuit, and fault conditions is mandatory in PC power supplies. These protection circuits can be realized by using many discrete components and comparators, which occupy a lot of PCB space and add to assembling costs. This single chip controller IC provides complete protection circuits, shunt regulators, and PWM control function with fewer components. SG6105A is an ideal controller IC for PC switching mode power supplies.

The features and benefits of this device are:

- Over-voltage and under-voltage protection for 3.3V, 5V, and 12V without external divider.

- 2. Over-power protection.

- 3. UV protection for -12V and/or -5V.

- 4. Power-down warning for power-good signal.

- 5. Power-good signal and power-fail lockup.

- 6. Remote on/off control.

- 7. Delay time for PSON and PS-off signal.

- 8. Two shunt regulators for 3.3V and 5V-standby regulation.

- Complete pulse width modulation (PWM) control circuitry.

- 10. On-chip oscillator.

- 11. Programmable soft-start.

- 12. Maximum 93% duty cycle.

- 13. Few external components.

- 14. More reliable system.

- 15. Little space on PCB.

- 16. Easy trouble-shooting and implementation.

### **Feature Descriptions**

- Over-voltage protection can be implemented without any additional components. Overvoltage sense levels for 3.3V, 5V, 12V, are 4.1V, 6.1V, 14.5V, respectively.

- Over-current and/or short-circuit protection can also be achieved using over-power protection, in which the OPP pin is connected to the current transformer (driver transformer).

- The power-good signal is asserted to indicate the 3.3V, 5V, and 12V is above the undervoltage threshold level. PG pin goes high when the above condition is reached. A 2K pull-up resistor may connect to 5V.

- 4. The  $V_{CC}$  can be supplied from the 5V-standby.

- 5. When the  $V_{\text{CC}}$  voltage is higher than 7V, besides the shunt regulator, the circuit is shutdown and reset. No extra power supply is needed.

- 6. Two internal high-precision 431 shunt regulators are built-in to provide stable reference voltages.

- Complete PWM control circuitry, including the error amplifier for push-pull or half-bridge operation.

### **Supervisory Circuit Operation**

The PC generates the remote ON/OFF logic (PSON), which is LOW for power supply on and HIGH to switch off the power supply. The remote ON/OFF is connected to PSON input.

# **Application Information**

### Introduction

The application guide shows the key features of SG6105A and illustrates how to design in an ATX switching mode power supply (SMPS). SG6105A is suitable for half-bridge, push-pull topology and incorporates with a four-channel supervisor, including 5V-standby. The PWM section of SG6105A comprises a built-in 65kHz oscillator and high-immunity circuits, which protect the system from noise interference and provide more noise margins for improper PCB layout. SG6105A has OVP and UVP for 12V, 5V, and 3.3V. NVP is used for negative voltage protection, such as – 12V and/or –5V. The U<sub>VAC</sub> (AC fails detection) is applied to detect AC line condition. Two built-in internal precision TL431 shunt regulators can be used for 3.3V or 5V auxiliary standby power.

### **AC Fails Detection**

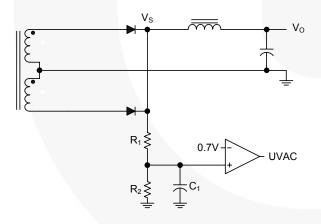

Through a resistor divider,  $U_{VAC}$  is connected to the secondary power transformer for detecting the AC line condition. Once the voltage of  $U_{VAC}$  is lower than 0.7V for a period of time, such as 200µs, the PG (powergood) signal is pulled low to indicate an AC line powerdown condition. The voltage amplitude of the PWM switching signal in the secondary power transformer is proportional to the AC line voltage. Adjust the ratio of resistor divider to decide the threshold of power-down warning. A small capacitor is connected from  $U_{VAC}$  to ground for filtering the switching noise.

Figure 17. AC Detection Circuit

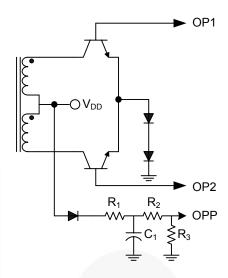

# **Over-Power Protection (OPP)**

The OPP is used for detecting over-power and/or short-circuit conditions. When OPPS voltage (p.4, Note-1) is higher than 2.1V and this situation exists for longer than 7ms, SG6105A pulls the PG low and locks off the power outputs.

Figure 18. OPP Protection Circuit

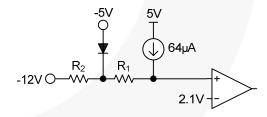

# **Negative Voltage Protection (NVP)**

The NVP provides an under-voltage protection (UVP) for negative voltage outputs. An under-voltage represents the phenomenal of the overload condition in negative voltage output. For example, the -12V output may drop to -10V during the overload situation. A resistor determining the threshold of the protection is connected from pin NVP to the negative voltage output. Via this resistor, NVP outputs a 64 $\mu$ A constant current to the negative voltage output. When the NVP voltage is over 2.1V and the situation kept for longer than 7ms, SG6105A locks the power outputs off:

$$V_{NVP}$$

=64 $\mu$ A × (R1 + R2) – V-12V (1)

The power outputs are locked off when VNVP  $\geq 2.1V$ .

Figure 19. NVP Protection Circuit

## **Reference Circuit**

Figure 21. Reference Circuit

# **BOM**

| Reference        | Component  | Reference | Component   |  |

|------------------|------------|-----------|-------------|--|

| D1,D2,D6 PR1004  |            | R14       | 100ΚΩ 1%    |  |

| D3               | 2A45V      | R15       | 47KΩ 1/8W   |  |

| D4,D5            | 30C40      | R16       | 9.47KΩ 1/8W |  |

| D7,D8,D9,D10,D11 | 1N4148     | R17       | 1.5ΚΩ 1%    |  |

| R1               | 62KΩ 1/8W  | R18       | 1.45ΚΩ 1%   |  |

| R2               | 3.2KΩ 1/8W | R19       | 39Ω 1/8W    |  |

| R3               | 510Ω 1%    | R20       | 1KΩ 1/8W    |  |

| R4               | 1.5ΚΩ 1%   | R21       | 96.7KΩ 1/8W |  |

| R5               | 100Ω 1/8W  | R22       | 10KΩ 1/8W   |  |

| R6               | 100Ω 1/8W  | C1        | 101/50V     |  |

| R7               | 1KΩ 1/8W   | C2,C5     | 2.2µF/50V   |  |

| R8               | 47~100Ω    | C3,C6     | 103/50V     |  |

| R9               | 1ΚΩ        | C4        | 333/50V     |  |

| R10              | 95.3ΚΩ     | Q1        | A928        |  |

| R11              | 93.7ΚΩ     | Q2,Q3     | 2SC945      |  |

| R12              | 75 KΩ      | U1        | PC817       |  |

| R13              | 14.2ΚΩ     | U2        | SG6105A     |  |

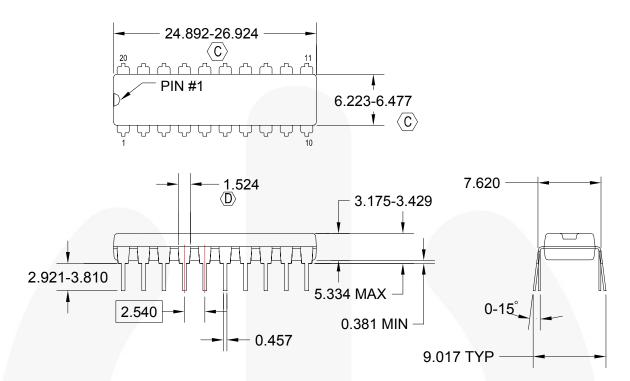

# **Physical Dimensions**

- NOTES:

A. CONFORMS TO JEDEC REGISTRATION MS-001, **VARIATIONS AD**

- B. ALL DIMENSIONS ARE IN MILLIMETERS

- © DOES NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.25MM.

- (D) DOES NOT INCLUDE DAMBAR PROTRUSIONS. DAMBAR PROTRUSIONS SHALL NOT EXCEED 0.25MM.

- E. DRAWING FILE NAME: N20SREV1

Figure 22. 20-Lead Dual Inline Package (DIP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/.

### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks

AccuPower™ Auto-SPM™ Build it Now™ CorePLUS™ CorePOWER™

CROSSVOLT™ CTL<sup>TM</sup> Current Transfer Logic™

EcoSPARK® EfficentMax™ EZSWTCH™\*

Fairchild® Fairchild Semiconductor® FACT Quiet Series™ FACT®

Fast∨Core™ FETBench™ FlashWriter®\* F-PESTM FRFET®

Global Power Resource<sup>SM</sup> Green FPS™

Green FPS™ e-Series™ Gmax<sup>TM</sup> GTO\*\*

IntelliMAX<sup>™</sup> ISOPLANAR™ MegaBuck™ MICROCOUPLER™ MicroFET™ MicroPak™ MillerDrive™

MotionMax™ Motion-SPM™ OPTOLOGIC® OPTOPLANAR®

PDP SPM™ Power-SPM™ PowerTrench® PowerXS™

Programmable Active Droop™ OFFT'

OSTM Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™ SmartMax™ SMART START™ SPM®

STEALTH™ SuperFET™ SuperSOT\*\*-3 SuperSOT™6 SuperSOT™8 SupreMOS™ SyncFET™ Sync-Lock™ SYSTEM 69

GENERAL The Power Franchise®

wer

TinyBoost™ TinyBuck™ TinyCalc™ TinyLogic® TINYOPTO" TinyPower™ TinyPWM™ TinyWire™ TriFault Detect™ TRUECURRENT\*\*\* μSerDes™

UHC Ultra FRFET™ UniFET™ **VCXTM** VisualMax™ XSTM

### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness

### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise, Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors

### PRODUCT STATUS DEFINITIONS

### Definition of Terms

| Datasheet Identification     | Product Status        | Definition                                                                                                                                                                                             |  |  |  |

|------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Advance Information          | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                          |  |  |  |

| Preliminary First Production |                       | Datasheet contains preliminary data, supplementary data will be published at a later date. Fairchild<br>Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |  |

| No Identification Needed     | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                                  |  |  |  |

| Obsolete                     | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                       |  |  |  |

Rev. 141

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

# AMEYA360 Components Supply Platform

# **Authorized Distribution Brand:**

# Website:

Welcome to visit www.ameya360.com

# Contact Us:

# > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

# > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

# Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com