# Product Preview

# **Self Test Ground Fault Circuit Interrupter (GFCI)**

#### **Description**

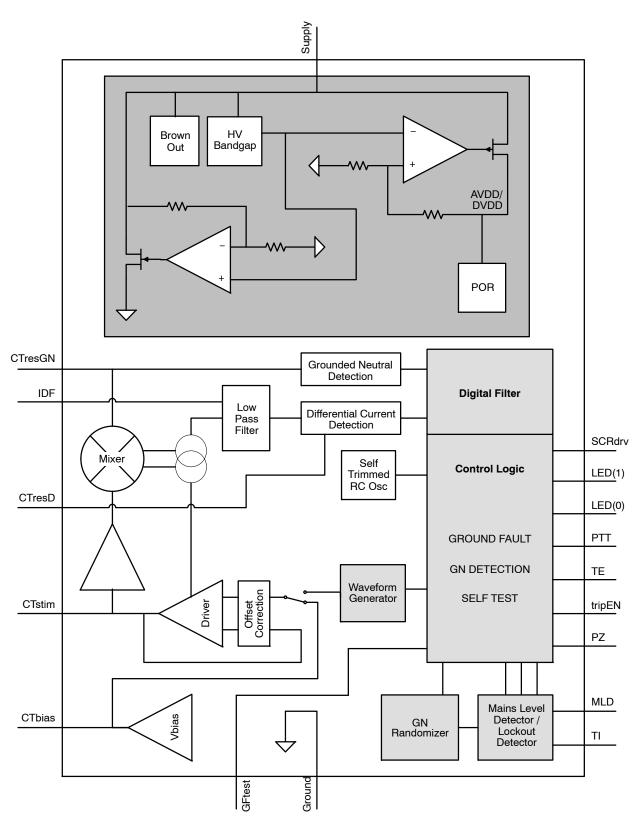

The NCS37012 is a fully UL943 compliant signal processor for GFCI applications with self test. The device integrates a flexible power supply (including both shunt and LDO regulators), differential fault, and grounded-neutral detection circuits. Proprietary impedance measurement and signal processing techniques are used to minimize the number of external components and improve performance. The device also includes a specialized DSP controller that offers best in class immunity to nuisance loads without the need for external analog filters. Self test is monitored every 17 minutes through an external current path and internally generated grounded neutral fault.

#### **Features**

- 6.0 V 12 V Operation (120 480 V AC mains with the appropriate series impedance)

- -40 to 85°C

- Very Low Power Consumption: <15 mW @ 5 V

- 16 Pin QFN Package or 20 Pin TSSOP Package

- Single Current Transformer (CT) Detection of both Differential and Grounded-Neutral Faults

- Full Self Test and Trip Indicator Monitoring

- Self Syncing Internal Oscillator Adjusts to AC Mains Frequency to Guarantee Full Resolution on 50 and 60 Hz Distribution Systems

- Optimized Solenoid Deployment (coil is not energized near the AC mains zero crossings)

- Randomized Testing Sequence to Minimize Noise and Potential Interactions on the AC Mains

- >5 mA SCR Driver for use with High Igt SCR's for Improved Noise Immunity

- Superior Immunity to Nuisance Loads/Noise (up to 10 A) without Loss of Detection Capability or CT Saturation

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Typical Applications**

- Load Panel GFCI Breakers

- GFCI Receptacles

- In-line GFCI Circuits (power cords)

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

#### ON Semiconductor®

#### www.onsemi.com

#### **MARKING DIAGRAMS**

XXXXX = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb-Free Package

CCCCC = Country of Origin

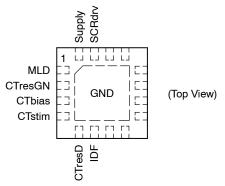

#### **PIN CONNECTIONS**

#### ORDERING INFORMATION

| Device        | Package              | Shipping <sup>†</sup> |

|---------------|----------------------|-----------------------|

| NCS37012MNTWG | QFN16<br>(Pb-Free)   | 3000 / Tape &<br>Reel |

| NCS37012DBRG  | TSSOP20<br>(Pb-Free) | 2500 / Tape &<br>Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

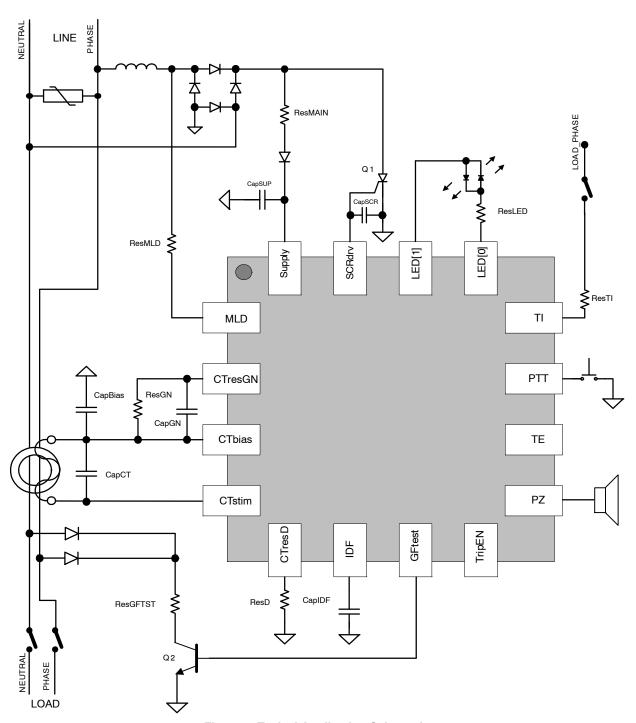

Figure 1. Simplified Block Diagram

**Table 1. PIN FUNCTION DESCRIPTION - QFN**

| Pin# | Name    | Pad Description                                                                                         |

|------|---------|---------------------------------------------------------------------------------------------------------|

| 0    | Ground  | QFN center slug                                                                                         |

| 1    | MLD     | Mains Level Detect (Zero Cross)                                                                         |

| 2    | CTresGN | Determines IV converter gain for detection threshold / matched to CT turns ratio (Ground-Neutral)       |

| 3    | CTbias  | Direct connection to the CT                                                                             |

| 4    | CTstim  | Direct connection to the CT                                                                             |

| 5    | CTresD  | Determines IV converter gain for detection threshold / matched to CT turns ratio (Differential Current) |

| 6    | IDF     | Front end noise filter capacitor                                                                        |

| 7    | GFtest  | Output to induce external differential current                                                          |

| 8    | TripEN  | (H) Trip / (L) No Trip on Self Test Failure                                                             |

| 9    | PZ      | Piezo output driver                                                                                     |

| 10   | NC      | Tie to Ground or leave floating                                                                         |

| 11   | PTT     | Push to test input                                                                                      |

| 12   | TI      | Tip indicator input                                                                                     |

| 13   | LED[0]  | LED[0] output driver                                                                                    |

| 14   | LED[1]  | LED[1] output driver                                                                                    |

| 15   | SCRdrv  | Used to trigger the solenoid at a fault detection                                                       |

| 16   | Supply  | Power supply                                                                                            |

#### **Table 2. PIN FUNCTION DESCRIPTION - TSSOP**

| Pin # | Name    | Pad Description                                                                                         |

|-------|---------|---------------------------------------------------------------------------------------------------------|

| 1     | CTstim  | Differential and ground to neutral stimulus point for the current transformer                           |

| 2     | Ground  | Ground connection for IC                                                                                |

| 3     | CTresD  | Determines IV converter gain for detection threshold / matched to CT turns ratio (Differential Current) |

| 4     | IDF     | Determines corner frequency of the differential current path filter                                     |

| 5     | GFtest  | Output to induce external differential current                                                          |

| 6     | TripEN  | (H) Trip / (L) No Trip on Self Test Failure                                                             |

| 7     | PZ      | Piezo output driver                                                                                     |

| 8     | NC      | Tie to Ground or leave floating                                                                         |

| 9     | PTT     | Push to test input                                                                                      |

| 10    | TI      | Tip indicator input                                                                                     |

| 11    | Ground  | Ground connection for IC                                                                                |

| 12    | LED[0]  | LED[0] output driver                                                                                    |

| 13    | LED[1]  | LED[1] output driver                                                                                    |

| 14    | SCRdrv  | Used to trigger the solenoid at a fault detection                                                       |

| 15    | DVDD    | Internal digital 5 V regulated supply                                                                   |

| 16    | AVDD    | Internal analog 5 V regulated supply                                                                    |

| 17    | Supply  | 12 V shunt regulated power supply                                                                       |

| 18    | MLD     | Mains Level Detect (Zero Cross) and AM slope detect (for oscillator sync/trim and AM init)              |

| 19    | CTresGN | Determines IV converter gain for detection threshold / matched to CT turns ratio (Ground-Neutral)       |

| 20    | CTbias  | External 2 V bias for the current transformer                                                           |

**Table 3. ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                            | Symbol              | Value                                                           | Unit |

|-----------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------|------|

| Supply Voltage Range                                                              | Vs                  | 6.0 to 12 V                                                     | V    |

| Input Voltage Range (Note 1)                                                      | V <sub>in</sub>     | -0.3 to 6.0                                                     | V    |

| Output Voltage Range                                                              | V <sub>out</sub>    | -0.3 to 6.0 V or (V <sub>in</sub> + 0.3),<br>whichever is lower | V    |

| Maximum Junction Temperature                                                      | T <sub>J(max)</sub> | 140                                                             | °C   |

| Storage Temperature Range                                                         | T <sub>STG</sub>    | -65 to 150                                                      | °C   |

| ESD Capability, Human Body Model (Note 2)                                         | ESD <sub>HBM</sub>  | 2                                                               | kV   |

| ESD Capability, Machine Model (Note 2)                                            | ESD <sub>MM</sub>   | 200                                                             | V    |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only), Pb-Free Versions (Note 3) | T <sub>SLD</sub>    | 260                                                             | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 2. This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

- ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

- Latchup Current Maximum Rating: ≤ 150 mA per JEDEC standard: JESD78

3. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

**Table 4. THERMAL CHARACTERISTICS**

| Rating                                                                                                                                       | Symbol                               | Value      | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------|------|

| Thermal Characteristics, QFN16, 3x3.3 mm (Note 4) Thermal Resistance, Junction-to-Air (Note 5) Thermal Reference, Junction-to-Lead2 (Note 5) | R <sub>θJA</sub><br>R <sub>ΨJL</sub> | TBD<br>TBD | °C/W |

| Thermal Characteristics, TSSOP-20 (Note 4) Thermal Resistance, Junction-to-Air (Note 5)                                                      | $R_{	hetaJA}$                        | TBD        | °C/W |

- 4. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 5. Values based on copper area of 645 mm<sup>2</sup> (or 1 in<sup>2</sup>) of 1 oz copper thickness and FR4 PCB substrate.

Table 5. OPERATING RANGES (Note 6)

| Parameter                            | Conditions                         | Min | Тур | Max | Units |

|--------------------------------------|------------------------------------|-----|-----|-----|-------|

| Operating Temperature                |                                    | -40 |     | 85  | С     |

| IDD in typical power state           |                                    |     | 2.0 |     | mA    |

| Stimulus Generator Frequency         | Tri-tone                           | 3.1 |     | 3.4 | kHz   |

| SCR Trigger Current                  |                                    |     |     | 8.0 | mA    |

| SCR Trigger output voltage           | With 5 V supply                    | 4.5 |     | 5.5 | V     |

| Fault Current Sensitivity            | Programmable with CTresD           | 4.6 | 4.8 | 5.0 | mA    |

| Ground Fault Response Time           | 5 – 20 mA                          |     | 150 |     | ms    |

| Ground Fault Response Time           | 20 – 40 mA                         |     | 75  |     | ms    |

| Ground Fault Response Time           | >40 mA                             |     | 25  |     | ms    |

| Saturation Fault Response Time       | >300 mA                            |     | 1.4 |     | ms    |

| CT Turns Ratio                       |                                    | 200 |     | 300 |       |

| Ground – Neutral Detection Threshold | Total series impedance (Rn and Rg) | 3.0 |     | 6.0 | Ω     |

| Internal Oscillator Frequency        |                                    |     | 2.0 |     | MHz   |

| CT Stimulus Current                  | Internally limited                 |     |     | 1.0 | mA    |

| CT Driver Closed Loop BW             |                                    |     |     | 500 | kHz   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

6. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

# **APPLICATIONS INFORMATION**

Figure 2. Typical Application Schematic

#### **RECOMMENDED EXTERNAL COMPONENTS:**

| Component Type | Instance | Value       | Note                                                       |

|----------------|----------|-------------|------------------------------------------------------------|

| SCR            | Q1       | -           | ON-MCR08                                                   |

| Diode          | Dx       | -           | ON-1N4007                                                  |

| NPN            | Q2       | -           | MMBT6517LT1G                                               |

| LED            | Lx       | -           | LED pins drive opposite polarities                         |

| Capacitor      | CapSUP   | 3.3 μF      | For a full bridge rectifier                                |

| Capacitor      | CapGN    | 1-10 nF     | Matched to current transformer                             |

| Capacitor      | CapIDF   | 220 nF      | Sets the differential corner frequency at 1 kHz            |

| Capacitor      | CapBias  | 10 nF       | Filtering component for CTbias voltage                     |

| Capacitor      | CapCT    | 2.2 - 10 nF | Filtering and resonant capacitor for CT                    |

| Capacitor      | CapSCR   | -           | Filtering component                                        |

| Resistor       | ResD     | 40 - 80k    | Matched to current transformer                             |

| Resistor       | ResGN    | 100 - 400k  | Matched to current transformer                             |

| Resistor       | ResMLD   | 400 - 800k  | Limiting resistor for the Mains Level Detector (MLD) input |

| Resistor       | ResTI    | 400 - 800k  | Limiting resistor for the Trip Indicator (TI) input        |

| Resistor       | ResMAIN  | 10k         | For a full bridge rectifier                                |

| Resistor       | ResGFTST | 15k         | Sets the external differential test current (8 mA)         |

| Resistor       | ResLED   | 1-5k        | Sets the brightness of the LEDs                            |

| TVS            | T1       | -           | ~250-400V                                                  |

#### **LED AND SPEAKER FUNCTIONS**

| Device Function | ce Function Device State      |                             | LED[1] | Speaker     |

|-----------------|-------------------------------|-----------------------------|--------|-------------|

|                 | No Power / Line Load Reversed | OFF                         | LOW    | OFF         |

|                 | Power Up                      | HIGH for 500 ms             | LOW    | OFF         |

| Normal          | Reset (Entered through PTT)   | HIGH for 500 ms<br>then LOW | HIGH   | ON (250 ms) |

|                 | Tripped                       | LOW                         | HIGH   | OFF         |

|                 | Self-Test Fails (Tripped)     | (Blink) HIGH                | LOW    | OFF         |

| Abnormal        | Self-Test Fails (Reset)       | (Blink) HIGH                | LOW    | ON          |

|                 | No Trip on Fault              | (Blink) HIGH                | LOW    | ON          |

#### **Filtering**

The analog signal capture portion of the IC includes a single pole filter that can be set externally with Cidf. This provides an additional layer of protection against false tripping under steady state noise conditions. High frequency steady state noise is common with pumps, motors or other cyclic noise generators.

Cidf = 220 nF = 1 kHz low pass.

For additional filtering suggestions please contact ON Semiconductor.

#### **Setting Trip Sensitivity**

The CTresD resistor sets the threshold for the differential current fault levels. Increasing CTresD causes the fault

levels to trip at lower differential currents. CT efficiency at 60 Hz must be considered.

. CTresD= 400\*#Turns – Subject to CT efficiency at 60 Hz The CTresGN resistor sets the threshold for ground to neutral fault detection. The Rt parameter is the desired ground to neutral resistance trip level. Higher CTresGN values will cause the part to trip at higher ground to neutral impedances.

CtresGN = #Turns^2 x Rt/2 – Subject to CT efficiency from 3 kHz to 4 kHz

#### Setting Grounded - Neutral Response Time

Cgn is used to define the response time of the grounded-neutral detection circuit. The analog portion converts the impedance into a DC voltage and a high frequency (aliased) component. The capacitor is used to remove the high frequency component leaving just the DC representation of the impedance.

CTcapGN= 1.8E-4/CTresGN

#### **Self Test**

Automatic self test will occur every 17 minutes. If a failure is observed it will be retested every second until it passes. If it fails 8 successive tests then the GFCI will indicate that it has failed self test. See the LED and speaker functions table to see the different self test indicators. If TripEN is asserted high the GFCI unit will trip.

Differential ground fault test – tests the CT and the internal differential detection signal path by asserting the GFtest output high for 2 half cycles. The test will pass if a 6-8 mA differential current is enabled during these two half waves. Greater than 20 mA current during this test will cause a fault to be detected.

Ground neutral fault test – tests the internal ground neutral stimulus and detection paths by enabling an internal 50k resistor between the CTstim and CTbias pins. If the resistor and capacitor on CTresGN are connected this will pass the GN self test.

#### PTT

When the PTT input pin is de-asserted for greater than 80 ms a self test will be performed. If this test is successful the SCR will be fired which will trip the GFCI unit. If the test is unsuccessful the LED[0] pin will flash indicating a failure.

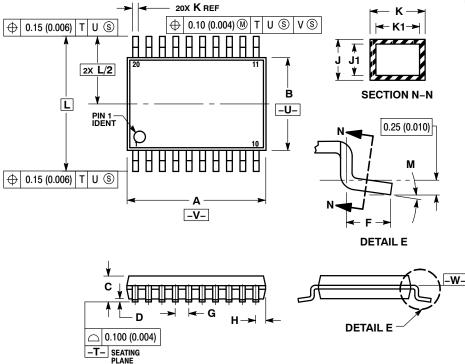

#### PACKAGE DIMENSIONS

#### TSSOP-20 CASE 948E-02 **ISSUE C**

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

4. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION. SHALL NOT EXCEED 0.25 (0.010) PER SIDE.

5. DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. SHALL BE 0.08

- DAMBAR PROTRUSION. ALLOWABLE

DAMBAR PROTRUSION SHALL BE 0.08

(0.003) TOTAL IN EXCESS OF THE K

DIMENSION AT MAXIMUM MATERIAL

CONDITION.

TERMINAL NUMBERS ARE SHOWN FOR

REFERENCE ONLY.

DIMENSION A AND B ARE TO BE

DETERMINED AT DATUM PLANE -W-.

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 6.40        | 6.60 | 0.252     | 0.260 |

| В   | 4.30        | 4.50 | 0.169     | 0.177 |

| С   |             | 1.20 |           | 0.047 |

| D   | 0.05        | 0.15 | 0.002     | 0.006 |

| F   | 0.50        | 0.75 | 0.020     | 0.030 |

| G   | 0.65        | BSC  | 0.026 BSC |       |

| Н   | 0.27        | 0.37 | 0.011     | 0.015 |

| J   | 0.09        | 0.20 | 0.004     | 0.008 |

| J1  | 0.09        | 0.16 | 0.004     | 0.006 |

| K   | 0.19        | 0.30 | 0.007     | 0.012 |

| K1  | 0.19        | 0.25 | 0.007     | 0.010 |

| L   | 6.40 BSC    |      | 0.252     |       |

| М   | 0°          | 8°   | 0°        | 8°    |

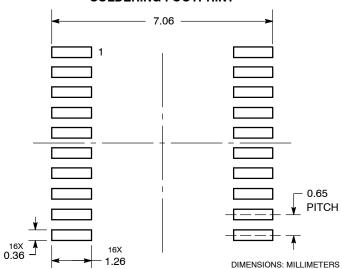

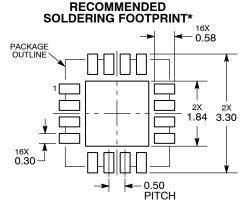

#### **SOLDERING FOOTPRINT**

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

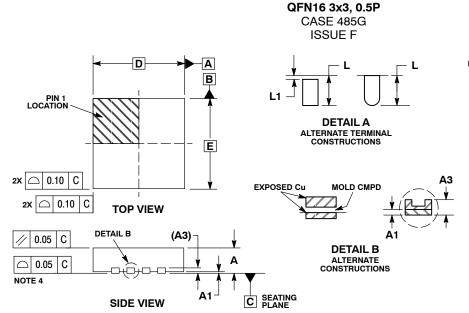

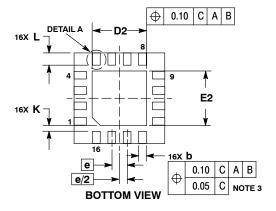

#### PACKAGE DIMENSIONS

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: MILLIMETERS. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL.

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |         |      |  |

|-----|-------------|---------|------|--|

| DIM | MIN         | NOM     | MAX  |  |

| Α   | 0.80        | 0.90    | 1.00 |  |

| A1  | 0.00        | 0.03    | 0.05 |  |

| А3  | 0           | .20 REF |      |  |

| b   | 0.18        | 0.24    | 0.30 |  |

| D   | 3           | .00 BSC | )    |  |

| D2  | 1.65        | 1.75    | 1.85 |  |

| E   | 3           | .00 BSC | )    |  |

| E2  | 1.65        | 1.75    | 1.85 |  |

| е   | 0.50 BSC    |         |      |  |

| K   | 0.18 TYP    |         |      |  |

| L   | 0.30        | 0.40    | 0.50 |  |

| L1  | 0.00        | 0.08    | 0.15 |  |

**DIMENSIONS: MILLIMETERS**

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and the (III) are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# AMEYA360 Components Supply Platform

# **Authorized Distribution Brand:**

# Website:

Welcome to visit www.ameya360.com

# Contact Us:

# > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

# > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

# Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com