## WirelessUSB™ LS 2.4 GHz DSSS Radio SoC

### Features

- 2.4-GHz radio transceiver

- Operates in the unlicensed Industrial, Scientific, and Medical (ISM) band (2.4 GHz to 2.483 GHz)

- Receive sensitivity:  $-90$  dBm

- Up to 0 dBm output power

- Range of up to 10 meters or more

- Data throughput of up to 62.5 kbits/sec

- Highly integrated low cost, minimal number of external components required

- Dual direct sequence spread spectrum (DSSS) reconfigurable baseband correlators

- SPI microcontroller interface (up to 2-MHz data rate)

- 13-MHz  $\pm$  50-ppm input clock operation

- Low standby current  $< 1$   $\mu$ A

- Integrated 30-bit Manufacturing ID

- Operating voltage from 2.7 V to 3.6 V

- Operating temperature from  $0^\circ$  to  $70^\circ$ C

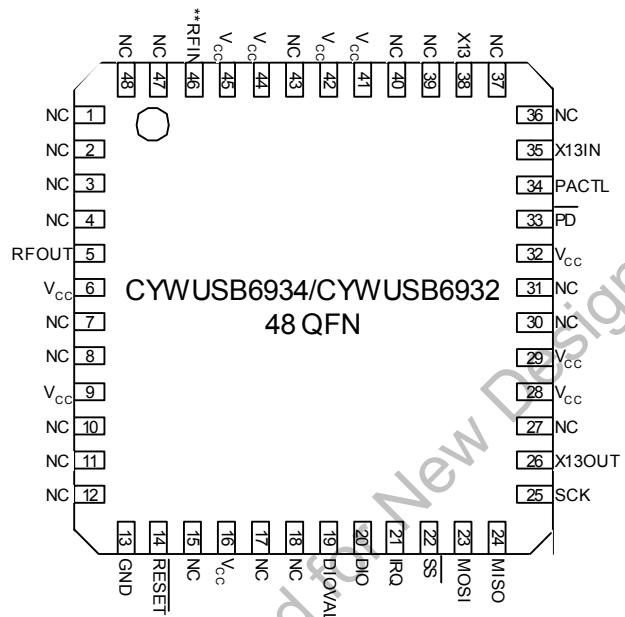

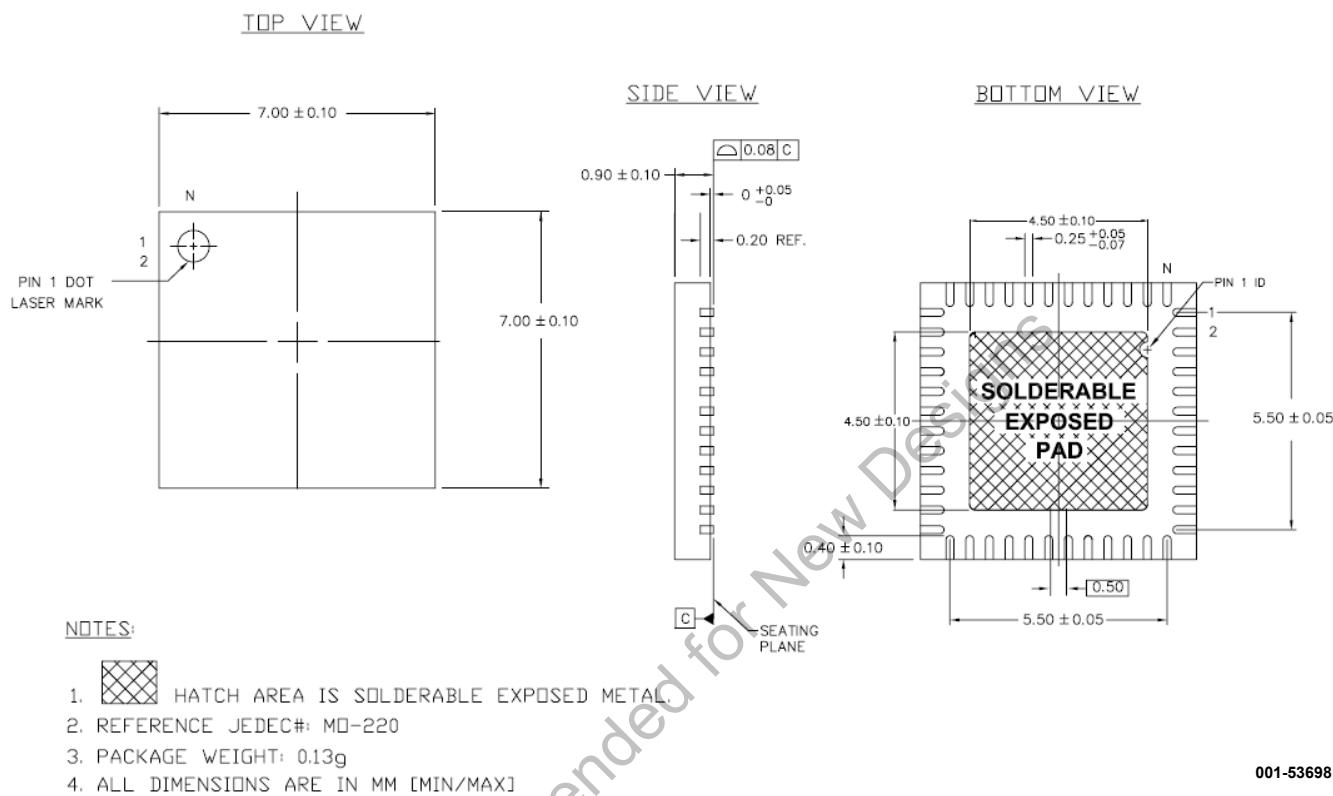

- Offered in a small footprint 48 quad flat pack no leads (QFN)

### Functional Description

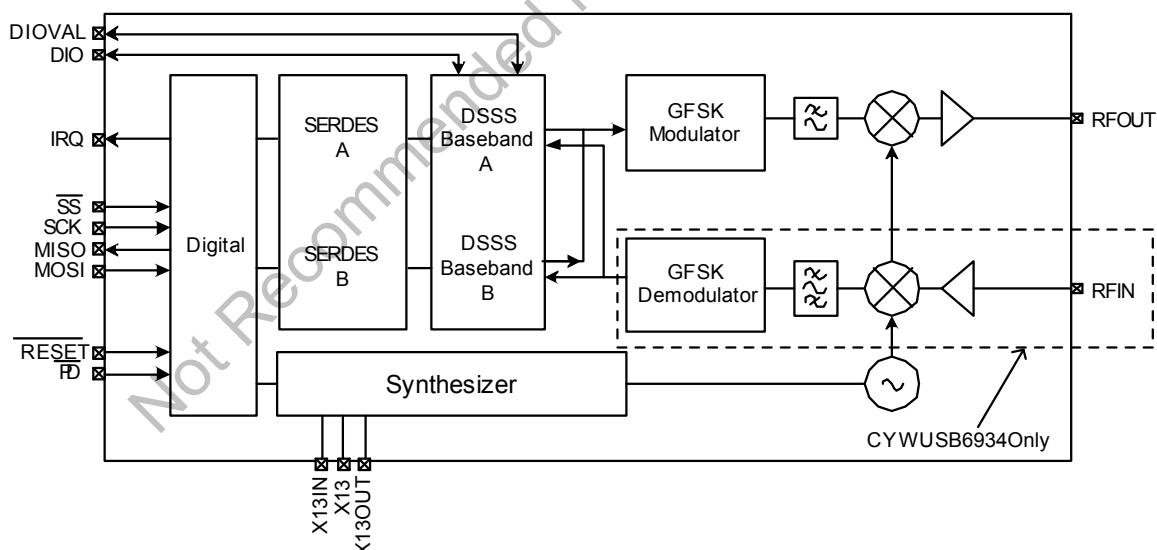

The CYWUSB6932<sup>[1]</sup>/CYWUSB6934 Integrated Circuits (ICs) are highly integrated 2.4-GHz DSSS radio system-on-chip (SoC) ICs. From the serial peripheral interface (SPI) to the antenna, these ICs are single-chip 2.4-GHz DSSS Gaussian Frequency Shift Keying (GFSK) baseband modems that connect directly to a microcontroller via simple serial interface.

The CYWUSB6932 transmit-only IC and the CYWUSB6934 transceiver IC are available in a small footprint 48-pin QFN package.

### Logic Block Diagram – CYWUSB6932/CYWUSB6934

#### Note

1. CYWUSB6932 is now obsolete and is no longer supported.

## Contents

|                                                            |           |

|------------------------------------------------------------|-----------|

| <b>Applications</b> .....                                  | <b>3</b>  |

| Applications Support                                       | 3         |

| <b>Functional Overview</b> .....                           | <b>3</b>  |

| 2.4-GHz Radio                                              | 3         |

| GFSK Modem                                                 | 3         |

| Dual DSSS Baseband                                         | 3         |

| Serializer/Deserializer (SERDES)                           | 4         |

| Application Interfaces                                     | 4         |

| Clocking and Power Management                              | 4         |

| Receive Signal Strength Indicator (RSSI)                   | 4         |

| <b>Application Interfaces</b> .....                        | <b>4</b>  |

| SPI Interface                                              | 4         |

| DIO Interface                                              | 6         |

| Interrupts                                                 | 6         |

| <b>Application Examples</b> .....                          | <b>7</b>  |

| <b>Register Descriptions</b> .....                         | <b>8</b>  |

| <b>Pin Definitions</b> .....                               | <b>23</b> |

| <b>Absolute Maximum Ratings</b> .....                      | <b>25</b> |

| <b>Operating Conditions</b> .....                          | <b>25</b> |

| <b>DC Characteristics (Over the Operating Range)</b> ..... | <b>25</b> |

| <b>AC Characteristics</b> .....                            | <b>26</b> |

| Radio Parameters                                           | 28        |

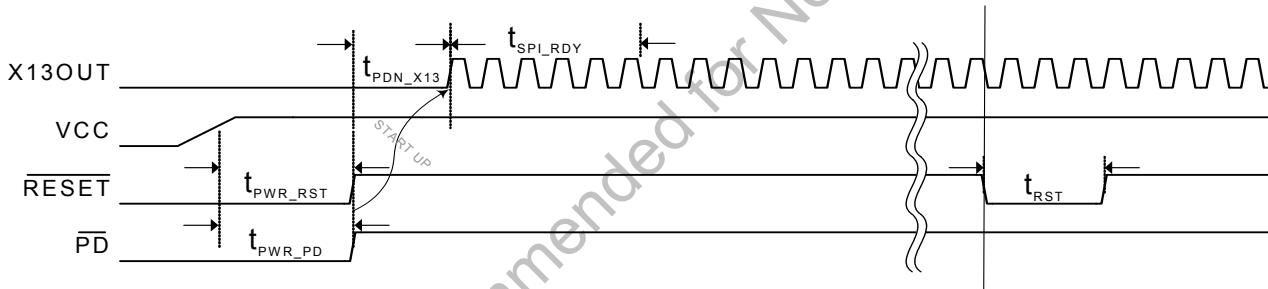

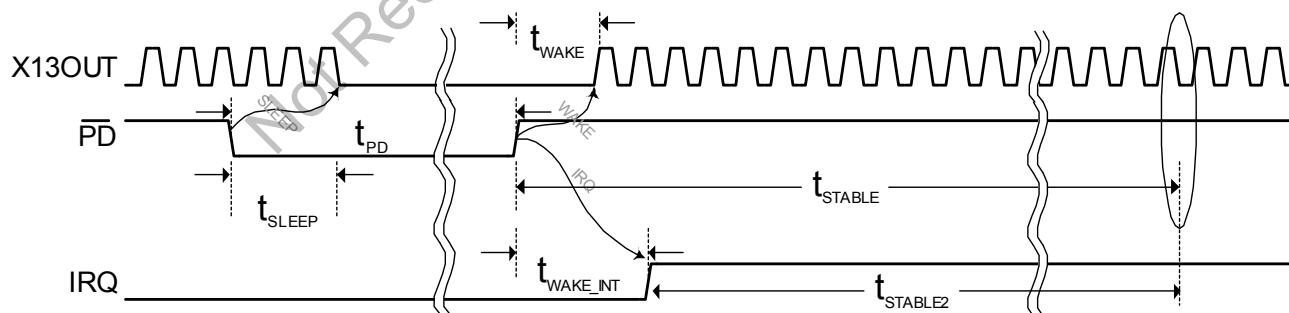

| Power Management Timing                                    | 29        |

| <b>Ordering Information</b> .....                          | <b>30</b> |

| Ordering Code Definition                                   | 30        |

| <b>Package Description</b> .....                           | <b>31</b> |

| <b>Acronyms</b> .....                                      | <b>32</b> |

| <b>Document Conventions</b> .....                          | <b>32</b> |

| <b>Document History Page</b> .....                         | <b>33</b> |

| <b>Sales, Solutions, and Legal Information</b> .....       | <b>34</b> |

| Worldwide Sales and Design Support                         | 34        |

| Products                                                   | 34        |

| PSoC Solutions                                             | 34        |

## Applications

### ■ PC human interface devices (HIDs)

- Mice

- Keyboards

- Joysticks

### ■ Peripheral gaming devices

- Game controllers

- Console keyboards

### ■ General

- Presenter tools

- Remote controls

- Consumer electronics

- Barcode scanners

- POS peripherals

- Toys

## Applications Support

The CYWUSB6932/CYWUSB6934 ICs are supported by the CY3632 WirelessUSB Development Kit. The development kit provides all of the materials and documents needed to cut the cord on wired applications such as:

1. Two radio modules that connect directly to two prototyping platform boards

2. Comprehensive WirelessUSB protocol code examples

3. A WirelessUSB Listener tool

4. All of the associated schematics, gerber files, and bill of materials.

The CY4632 WirelessUSB LS keyboard mouse reference design provides a production-worthy example of a wireless mouse and keyboard system.

The CY3633 WirelessUSB LS gaming development kit provides support for designing a wireless gamepad for the major gaming consoles and is offered as an accessory to the CY3632 WirelessUSB development kit.

## Functional Overview

The CYWUSB6932/CYWUSB6934 ICs provide a complete WirelessUSB LS SPI to antenna radio modem. The SoC is designed to implement wireless devices operating in the worldwide 2.4-GHz ISM frequency band (2.400 GHz to 2.4835 GHz). It is intended for systems compliant with world-wide regulations covered by ETSI EN 301 489-1 V1.4.1, ETSI EN 300 328-1 V1.3.1 (European countries); FCC CFR 47 Part 15 (USA and Industry Canada) and ARIB STD-T66 (Japan).

The CYWUSB6934 IC contains a 2.4-GHz radio transceiver, a GFSK modem and a dual DSSS reconfigurable baseband. The CYWUSB6932 IC contains a 2.4-GHz radio transmit-only, a GFSK modem and a DSSS baseband. The radio and baseband are both code- and frequency-agile. Forty-nine spreading codes selected for optimal performance (Gold codes) are supported across 78 1-MHz channels yielding a theoretical spectral capacity of 3822 channels. Both ICs support a range of up to 10 meters or more.

## 2.4-GHz Radio

The receiver and transmitter are a single-conversion low-Intermediate Frequency (low-IF) architecture with fully integrated IF channel matched filters to achieve high performance in the presence of interference. An integrated Power Amplifier (PA) provides an output power control range of 30 dB in seven steps.

**Table 1. Internal PA Output Power Step Table**

| PA Setting | Typical Output Power (dBm) |

|------------|----------------------------|

| 7          | 0                          |

| 6          | -2.4                       |

| 5          | -5.6                       |

| 4          | -9.7                       |

| 3          | -16.4                      |

| 2          | -20.8                      |

| 1          | -24.8                      |

| 0          | -29.0                      |

Both the receiver and transmitter integrated Voltage Controlled Oscillator (VCO) and synthesizer have the agility to cover the complete 2.4-GHz GFSK radio transmitter ISM band. The synthesizer provides the frequency-hopping local oscillator for the transmitter and receiver. The VCO loop filter is also integrated on-chip.

## GFSK Modem

The transmitter uses a DSP-based vector modulator to convert the 1-MHz chips to an accurate GFSK carrier.

The receiver uses a fully integrated Frequency Modulator (FM) detector with automatic data slicer to demodulate the GFSK signal.

## Dual DSSS Baseband

Data is converted to DSSS chips by a digital spreader. De-spreading is performed by an oversampled correlator. The DSSS baseband cancels spurious noise and assembles properly correlated data bytes.

The DSSS baseband has three operating modes: 64 chips/bit Single Channel, 32 chips/bit Single Channel, and 32 chips/bit Single Channel Dual Data Rate (DDR).

### 64 Chips/Bit Single Channel

The baseband supports a single data stream operating at 15.625 kbits/sec. The advantage of selecting this mode is its ability to tolerate a noisy environment. This is because the 15.625 kbits/sec data stream utilizes the longest PN Code resulting in the highest probability for recovering packets over the air. This mode can also be selected for systems requiring data transmissions over longer ranges.

### 32 Chips/Bit Single Channel

The baseband supports a single data stream operating at 31.25 kbits/sec.

### 32 Chips/Bit Single Channel Dual Data Rate (DDR)

The baseband spreads bits in pairs and supports a single data stream operating at 62.5 kbits/sec.

## Serializer/Deserializer (SERDES)

The CYWUSB6934 IC has a data Serializer/Deserializer (SERDES), which provides byte-level framing of transmit and receive data. Bytes for transmission are loaded into the SERDES and receive bytes are read from the SERDES via the SPI interface. The SERDES provides double buffering of transmit and receive data. While one byte is being transmitted by the radio the next byte can be written to the SERDES data register insuring there are no breaks in transmitted data.

After a receive byte has been received it is loaded into the SERDES data register and can be read at any time until the next byte is received, at which time the old contents of the SERDES data register will be overwritten. The CYWUSB6932 IC only has a data serializer.

## Application Interfaces

Both ICs have a fully synchronous SPI slave interface for connectivity to the application MCU. Configuration and byte-oriented data transfer can be performed over this interface. An interrupt is provided to trigger real time events.

An optional SERDES Bypass mode (DIO) is provided for applications that require a synchronous serial bit-oriented data path. This interface is for data only.

## Clocking and Power Management

A 13-MHz crystal ( $\pm 50$  ppm or better) is directly connected to X13IN and X13 without the need for external capacitors. Both ICs have a programmable trim capability for adjusting the on-chip load capacitance supplied to the crystal.

Below are the requirements for the crystal to be directly connected to X13IN and X13:

- Nominal frequency: 13 MHz

- Operating mode: Fundamental mode

- Resonance mode: Parallel resonant

- Frequency stability:  $\pm 50$  ppm

- Series resistance:  $\leq 100$  ohms

- Load capacitance: 10 pF

- Drive level: 10 uW to 100 uW

The Radio Frequency (RF) circuitry has on-chip decoupling capacitors. Both devices are powered from a 2.7 V to 3.6 V DC supply. Both devices can be shutdown to a fully static state using the PD pin.

## Receive Signal Strength Indicator (RSSI)

The RSSI register (Reg 0x22) (applies only to the CYWUSB6934 IC) returns the relative signal strength of the ON-channel signal power and can be used to:

1. Determine the connection quality

2. Determine the value of the noise floor

3. Check for a quiet channel before transmitting.

The internal RSSI voltage is sampled through a 5-bit analog-to-digital converter (ADC). A state machine controls the conversion process. Under normal conditions, the RSSI state machine initiates a conversion when an ON-channel carrier is detected and remains above the noise floor for over 50  $\mu$ s. The conversion produces a 5-bit value in the RSSI register (Reg

0x22, bits 4:0) along with a valid bit, RSSI register (Reg 0x22, bit 5). The state machine then remains in HALT mode and does not reset for a new conversion until the receive mode is toggled off and on. Once a connection has been established, the RSSI register can be read to determine the relative connection quality of the channel. A RSSI register value lower than 10 indicates that the received signal strength is low, a value greater than 28 indicates a strong signal level.

To check for a quiet channel before transmitting, first set up receive mode properly and read the RSSI register (Reg 0x22). If the valid bit is zero, then force the Carrier Detect register (Reg 0x2F, bit 7=1) to initiate an ADC conversion. Then, wait greater than 50  $\mu$ s and read the RSSI register again. Next, clear the Carrier Detect Register (Reg 0x2F, bit 7=0) and turn the receiver OFF. Measuring the noise floor of a quiet channel is inherently a 'noisy' process so, for best results, this procedure should be repeated several times (~20) to compute an average noise floor level. A RSSI register value of 0-10 indicates a channel that is relatively quiet. A RSSI register value greater than 10 indicates the channel is probably being used. A RSSI register value greater than 28 indicates the presence of a strong signal.

## Application Interfaces

### SPI Interface

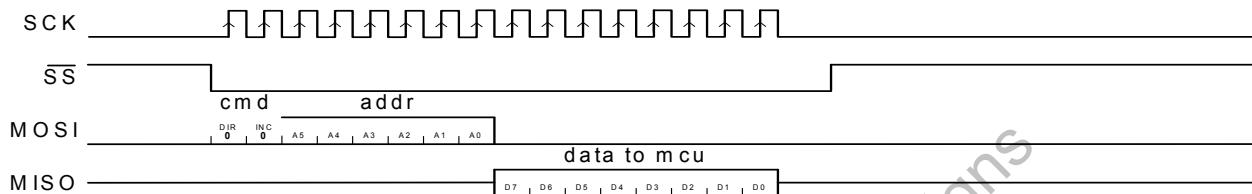

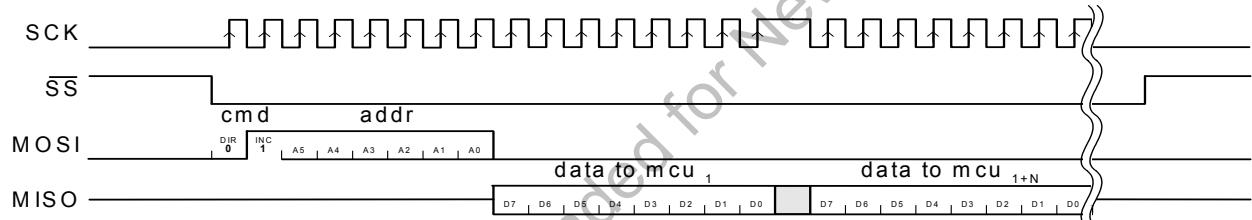

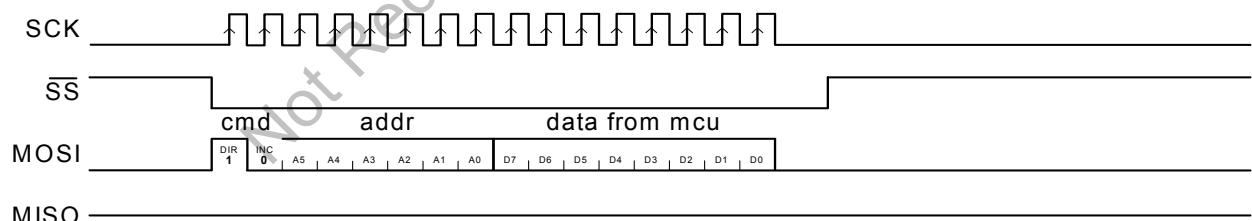

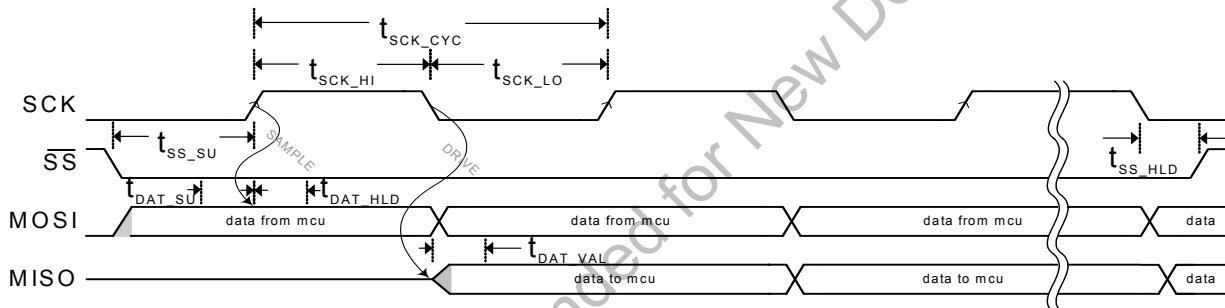

The CYWUSB6932/CYWUSB6934 ICs have a four-wire SPI communication interface between an application MCU and one or more slave devices. The SPI interface supports single-byte and multi-byte serial transfers. The four-wire SPI communications interface consists of Master Out-Slave In (MOSI), Master In-Slave Out (MISO), Serial Clock (SCK), and Slave Select (SS).

The SPI receives SCK from an application MCU on the SCK pin. Data from the application MCU is shifted in on the MOSI pin. Data to the application MCU is shifted out on the MISO pin. The active-low Slave Select (SS) pin must be asserted to initiate a SPI transfer.

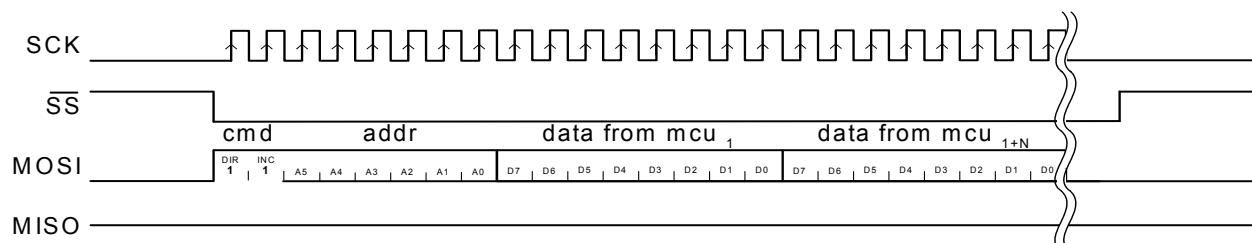

The application MCU can initiate a SPI data transfer via a multi-byte transaction. The first byte is the Command/Address byte, and the following bytes are the data bytes as shown in [Figure 2](#) through [Figure 3](#). The SS signal should not be deasserted between bytes. The SPI communications is as follows:

- Command Direction (bit 7) = "0" Enables SPI read transaction. A "1" enables SPI write transactions.

- Command Increment (bit 6) = "1" Enables SPI auto address increment. When set, the address field automatically increments at the end of each data byte in a burst access, otherwise the same address is accessed.

- Six bits of address.

- Eight bits of data.

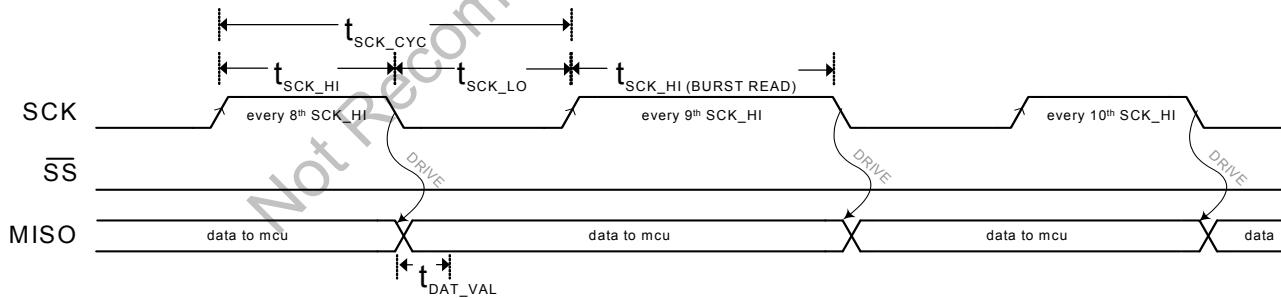

The SPI communications interface has a burst mechanism, where the command byte can be followed by as many data bytes as desired. A burst transaction is terminated by deasserting the slave select (SS = 1). For burst read transactions, the application MCU must abide by the timing shown in [Figure 12](#).

The SPI communications interface single read and burst read sequences are shown in [Figure 1](#) and [Figure 2](#), respectively.

The SPI communications interface single write and burst write sequences are shown in [Figure 3](#) and [Figure 4](#), respectively.

**Table 2. SPI Transaction Format**

| Bit #    | Byte 1 |     |         |  |  |  | Byte 1+N |       |  |  |  |  |

|----------|--------|-----|---------|--|--|--|----------|-------|--|--|--|--|

|          | 7      | 6   | [5:0]   |  |  |  |          | [7:0] |  |  |  |  |

| Bit Name | DIR    | INC | Address |  |  |  |          | Data  |  |  |  |  |

**Figure 1. SPI Single Read Sequence**

**Figure 2. SPI Burst Read Sequence**

**Figure 3. SPI Single Write Sequence**

**Figure 4. SPI Burst Write Sequence**

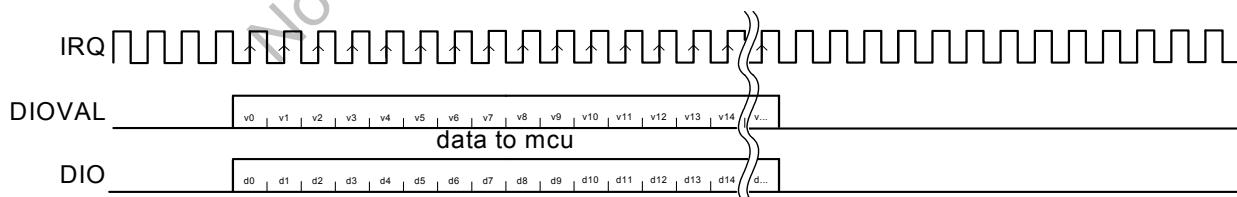

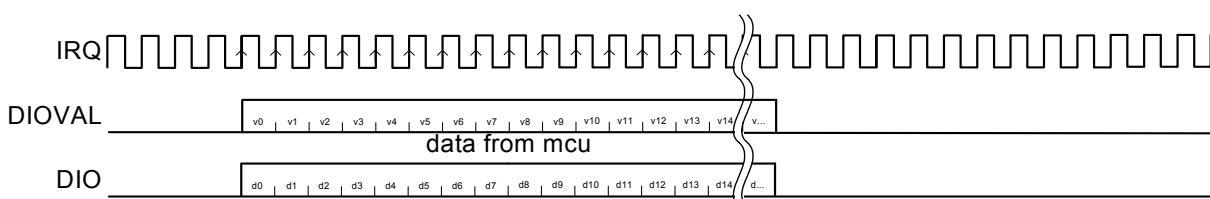

## DIO Interface

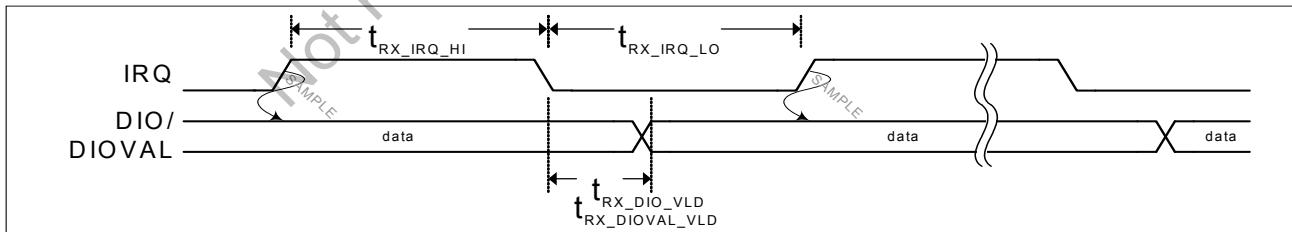

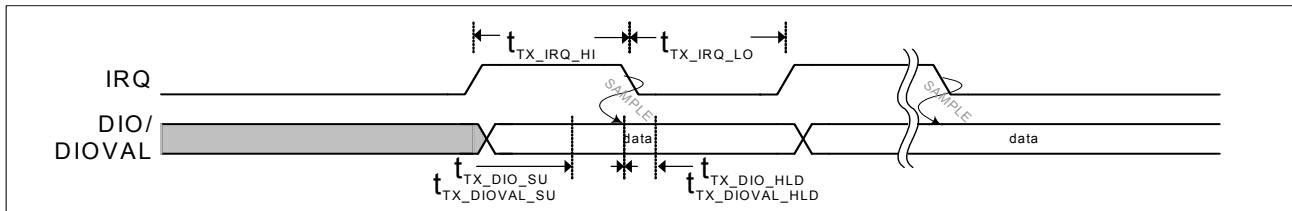

The DIO communications interface is an optional SERDES bypass data-only transfer interface. In receive mode, DIO and DIOVAL are valid after the falling edge of IRQ, which clocks the data as shown in [Figure 5](#). In transmit mode, DIO and DIOVAL are sampled on the falling edge of the IRQ, which clocks the data as shown in [Figure 6](#). The application MCU samples the DIO and DIOVAL on the rising edge of IRQ.

## Interrupts

The CYWUSB6932/CYWUSB6934 ICs feature three sets of interrupts: transmit, receive (CYWUSB6934 only), and a wake interrupt. These interrupts all share a single pin (IRQ), but can be independently enabled/disabled. In transmit mode, all receive interrupts are automatically disabled, and in receive mode all transmit interrupts are automatically disabled. However, the contents of the enable registers are preserved when switching between transmit and receive modes.

Interrupts are enabled and the status read through 6 registers: Receive Interrupt Enable (Reg 0x07), Receive Interrupt Status (Reg 0x08), Transmit Interrupt Enable (Reg 0x0D), Transmit Interrupt Status (Reg 0x0E), Wake Enable (Reg 0x1C), Wake Status (Reg 0x1D).

If more than 1 interrupt is enabled at any time, it is necessary to read the relevant interrupt status register to determine which event caused the IRQ pin to assert. Even when a given interrupt source is disabled, the status of the condition that would otherwise cause an interrupt can be determined by reading the appropriate interrupt status register. It is therefore possible to use the devices without making use of the IRQ pin at all. Firmware can poll the interrupt status register(s) to wait for an event, rather than using the IRQ pin.

The polarity of all interrupts can be set by writing to the Configuration register (Reg 0x05), and it is possible to configure the IRQ pin to be open drain (if active low) or open source (if active high).

## Wake Interrupt

When the PD pin is low, the oscillator is stopped. After PD is deasserted, the oscillator takes time to start, and until it has done so, it is not safe to use the SPI interface. The wake interrupt indicates that the oscillator has started, and that the device is ready to receive SPI transfers.

The wake interrupt is enabled by setting bit 0 of the Wake Enable register (Reg 0x1C, bit 0=1). Whether or not a wake interrupt is pending is indicated by the state of bit 0 of the Wake Status register (Reg 0x1D, bit 0). Reading the Wake Status register (Reg 0x1D) clears the interrupt.

## Transmit Interrupts

Four interrupts are provided to flag the occurrence of transmit events. The interrupts are enabled by writing to the Transmit Interrupt Enable register (Reg 0x0D), and their status may be determined by reading the Transmit Interrupt Status register (Reg 0x0E). If more than 1 interrupt is enabled, it is necessary to read the Transmit Interrupt Status register (Reg 0x0E) to determine which event caused the IRQ pin to assert.

The function and operation of these interrupts are described in detail in [Section](#).

## Receive Interrupts

Eight interrupts are provided to flag the occurrence of receive events, four each for SERDES A and B. In 64 chips/bit and 32 chips/bit DDR modes, only the SERDES A interrupts are available, and the SERDES B interrupts will never trigger, even if enabled. The interrupts are enabled by writing to the Receive Interrupt Enable register (Reg 0x07), and their status may be determined by reading the Receive Interrupt Status register (Reg 0x08). If more than one interrupt is enabled, it is necessary to read the Receive Interrupt Status register (Reg 0x08) to determine which event caused the IRQ pin to assert.

The function and operation of these interrupts are described in detail in [Section](#).

**Figure 5. DIO Receive Sequence**

**Figure 6. DIO Transmit Sequence**

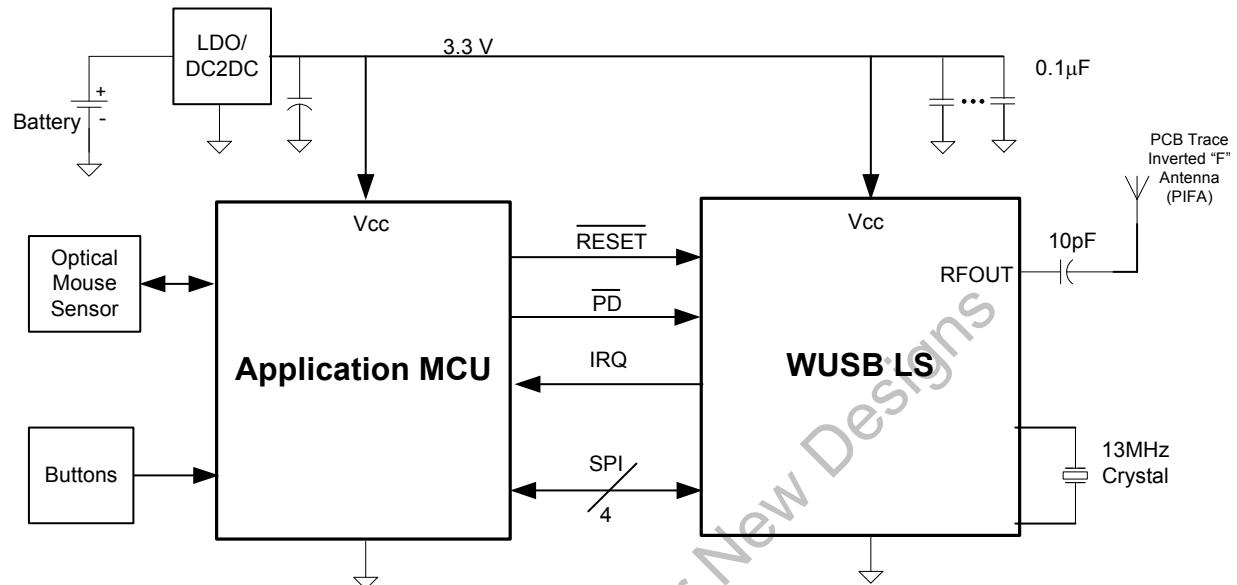

## Application Examples

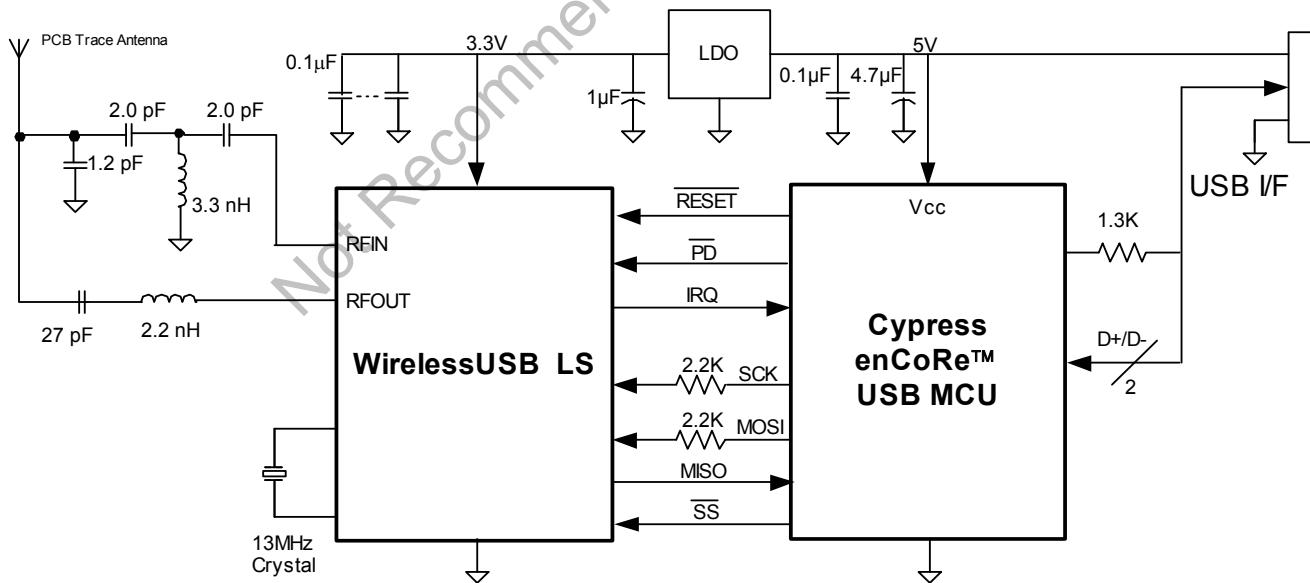

Figure 7. CYWUSB6932 Transmit-Only Battery-Powered Device

Figure 8. CYWUSB6934 USB Bridge Transceiver

## Register Descriptions

Table 3 displays the list of registers inside the CYWUSB6932/CYWUSB6934 ICs that are addressable through the SPI interface. All registers are read and writable, except where noted.

**Table 3. CYWUSB6932/CYWUSB6934 Register Map<sup>[2]</sup>**

| Register Name                     | Mnemonic           | Address             | Page    | Default           | Access |

|-----------------------------------|--------------------|---------------------|---------|-------------------|--------|

| Revision ID                       | REG_ID             | 0x00                | page 9  | 0x07              | RO     |

| Control                           | REG_CONTROL        | 0x03                | page 9  | 0x00              | RW     |

| Data Rate                         | REG_DATA_RATE      | 0x04                | page 10 | 0x00              | RW     |

| Configuration                     | REG_CONFIG         | 0x05                | page 10 | 0x01              | RW     |

| SERDES Control                    | REG_SERDES_CTL     | 0x06                | page 11 | 0x03              | RW     |

| Receive SERDES Interrupt Enable   | REG_RX_INT_EN      | 0x07 <sup>[3]</sup> | page 11 | 0x00              | RW     |

| Receive SERDES Interrupt Status   | REG_RX_INT_STAT    | 0x08 <sup>[3]</sup> | page 12 | 0x00              | RO     |

| Receive SERDES Data A             | REG_RX_DATA_A      | 0x09 <sup>[3]</sup> | page 14 | 0x00              | RO     |

| Receive SERDES Valid A            | REG_RX_VALID_A     | 0x0A <sup>[3]</sup> | page 14 | 0x00              | RO     |

| Receive SERDES Data B             | REG_RX_DATA_B      | 0x0B <sup>[3]</sup> | page 14 | 0x00              | RO     |

| Receive SERDES Valid B            | REG_RX_VALID_B     | 0x0C <sup>[3]</sup> | page 14 | 0x00              | RO     |

| Transmit SERDES Interrupt Enable  | REG_TX_INT_EN      | 0x0D                | page 14 | 0x00              | RW     |

| Transmit SERDES Interrupt Status  | REG_TX_INT_STAT    | 0x0E                | page 16 | 0x00              | RO     |

| Transmit SERDES Data              | REG_TX_DATA        | 0x0F                | page 17 | 0x00              | RW     |

| Transmit SERDES Valid             | REG_TX_VALID       | 0x10                | page 17 | 0x00              | RW     |

| PN Code                           | REG_PN_CODE        | 0x18–0x11           | page 17 | 0x1E8B6A3DE0E9B22 | RW     |

| Threshold Low                     | REG_THRESHOLD_L    | 0x19 <sup>[3]</sup> | page 18 | 0x08              | RW     |

| Threshold High                    | REG_THRESHOLD_H    | 0x1A <sup>[3]</sup> | page 18 | 0x38              | RW     |

| Wake Enable                       | REG_WAKE_EN        | 0x1C                | page 18 | 0x00              | RW     |

| Wake Status                       | REG_WAKE_STAT      | 0x1D                | page 19 | 0x01              | RO     |

| Analog Control                    | REG_ANALOG_CTL     | 0x20                | page 19 | 0x04              | RW     |

| Channel                           | REG_CHANNEL        | 0x21                | page 20 | 0x00              | RW     |

| Receive Signal Strength Indicator | REG_RSSI           | 0x22 <sup>[3]</sup> | page 20 | 0x00              | RO     |

| PA Bias                           | REG_PA             | 0x23                | page 20 | 0x00              | RW     |

| Crystal Adjust                    | REG_CRYSTAL_ADJ    | 0x24                | page 21 | 0x00              | RW     |

| VCO Calibration                   | REG_VCO_CAL        | 0x26                | page 21 | 0x00              | RW     |

| Reg Power Control                 | REG_PWR_CTL        | 0x2E                | 21      | 0x00              | RW     |

| Carrier Detect                    | REG_CARRIER_DETECT | 0x2F                | page 22 | 0x00              | RW     |

| Clock Manual                      | REG_CLOCK_MANUAL   | 0x32                | page 22 | 0x00              | RW     |

| Clock Enable                      | REG_CLOCK_ENABLE   | 0x33                | page 22 | 0x00              | RW     |

| Synthesizer Lock Count            | REG_SYN_LOCK_CNT   | 0x38                | page 22 | 0x64              | RW     |

| Manufacturing ID                  | REG_MID            | 0x3C–0x3F           | page 22 | –                 | RO     |

### Notes

2. All registers are accessed Little Endian.

3. Register not applicable to CYWUSB6932.

**Table 4. Revision ID Register**

| Addr: 0x00 |   |   |   |   |   |   |   | REG_ID     | Default: 0x07 |  |

|------------|---|---|---|---|---|---|---|------------|---------------|--|

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |            |               |  |

| Silicon ID |   |   |   |   |   |   |   | Product ID |               |  |

| Bit | Name       | Description                                                                                        |  |  |  |  |  |  |  |

|-----|------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7:4 | Silicon ID | These are the Silicon ID revision bits. 0000 = Rev A, 0001 = Rev B, etc. These bits are read-only. |  |  |  |  |  |  |  |

| 3:0 | Product ID | These are the Product ID revision bits. Fixed at value 0111. These bits are read-only.             |  |  |  |  |  |  |  |

**Table 5. Control**

| Addr: 0x03 |           |                |                                 |                          |                    |          |          | REG_CONTROL | Default: 0x00 |  |

|------------|-----------|----------------|---------------------------------|--------------------------|--------------------|----------|----------|-------------|---------------|--|

| 7          | 6         | 5              | 4                               | 3                        | 2                  | 1        | 0        |             |               |  |

| RX Enable  | TX Enable | PN Code Select | Bypass Internal Syn Lock Signal | Auto Internal PA Disable | Internal PA Enable | Reserved | Reserved |             |               |  |

| Bit | Name                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|-----|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7   | RX Enable                       | The Receive Enable bit is used to place the IC in receive mode.<br>1 = Receive Enabled<br>0 = Receive Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 6   | TX Enable                       | The Transmit Enable bit is used to place the IC in transmit mode.<br>1 = Transmit Enabled<br>0 = Transmit Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 5   | PN Code Select                  | The Pseudo-Noise Code Select bit selects between the upper or lower half of the 64 chips/bit PN code.<br>1 = 32 Most Significant Bits of PN code are used<br>0 = 32 Least Significant Bits of PN code are used<br>This bit applies only when the Code Width bit is set to 32 chips/bit PN codes (Reg 0x04, bit 2=1).                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 4   | Bypass Internal Syn Lock Signal | This bit controls whether the state machine waits for the internal Syn Lock Signal before waiting for the amount of time specified in the Syn Lock Count register (Reg 0x38), in units of 2 $\mu$ s. If the internal Syn Lock Signal is used then set Syn Lock Count to 25 to provide additional assurance that the synthesizer has settled.<br>1 = Bypass the Internal Syn Lock Signal and wait the amount of time in Syn Lock Count register (Reg 0x38)<br>0 = Wait for the Syn Lock Signal and then wait the amount of time specified in Syn Lock Count register (Reg 0x38)<br>It is recommended that the application MCU sets this bit to 1 in order to guarantee a consistent settle time for the synthesizer. |  |  |  |  |  |  |  |

| 3   | Auto Internal PA Disable        | The Auto Internal PA Disable bit is used to determine the method of controlling the Internal Power Amplifier. The two options are automatic control by the baseband or by firmware through register writes. For external PA usage, please see the description of the REG_ANALOG_CTL register (Reg 0x20).<br>1 = Register controlled Internal PA Enable<br>0 = Auto controlled Internal PA Enable<br>When this bit is set to 1, the enabled state of the Internal PA is directly controlled by bit Internal PA Enable (Reg 0x03, bit 2). It is recommended that this bit is set to 0, leaving the PA control to the baseband.                                                                                        |  |  |  |  |  |  |  |

| 2   | Internal PA Enable              | The Internal PA Enable bit is used to enable or disable the Internal Power Amplifier.<br>1 = Internal Power Amplifier Enabled<br>0 = Internal Power Amplifier Disabled<br>This bit only applies when the Auto Internal PA Disable bit is selected (Reg 0x03, bit 3=1), otherwise this bit is don't care.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 1   | Reserved                        | This bit is reserved and should be written with a zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 0   | Reserved                        | This bit is reserved and should be written with a zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

**Table 6. Data Rate**

| Addr: 0x04 |   |   |   |   |            |           |             | REG_DATA_RATE | Default: 0x00 |  |  |

|------------|---|---|---|---|------------|-----------|-------------|---------------|---------------|--|--|

| 7          | 6 | 5 | 4 | 3 | 2          | 1         | 0           |               |               |  |  |

| Reserved   |   |   |   |   | Code Width | Data Rate | Sample Rate |               |               |  |  |

| Bit              | Name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3              | Reserved    | These bits are reserved and should be written with zeroes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2 <sup>[4]</sup> | Code Width  | <p>The Code Width bit is used to select between 32 chips/bit and 64 chips/bit PN codes.</p> <p>1 = 32 chips/bit PN codes<br/>   0 = 64 chips/bit PN codes</p> <p>The number of chips/bit used impacts a number of factors such as data throughput, range and robustness to interference. By choosing a 32 chips/bit PN-code, the data throughput can be doubled or even quadrupled (when double data rate is set). A 64 chips/bit PN code offers improved range over its 32 chips/bit counterpart as well as more robustness to interference. By selecting to use a 32 chips/bit PN code a number of other register bits are impacted and need to be addressed. These are PN Code Select (Reg 0x03, bit 5), Data Rate (Reg 0x04, bit 1), and Sample Rate (Reg 0x04, bit 0).</p>                                                                                                                                                                                             |

| 1 <sup>[4]</sup> | Data Rate   | <p>The Data Rate bit allows the user to select Double Data Rate mode of operation which delivers a raw data rate of 62.5 kbits/sec.</p> <p>1 = Double Data Rate - 2 bits per PN code (No odd bit transmissions)<br/>   0 = Normal Data Rate - 1 bit per PN code</p> <p>This bit is applicable only when using 32 chips/bit PN codes which can be selected by setting the Code Width bit (Reg 0x04, bit 2=1). When using Double Data Rate, the raw data throughput is 62.5 kbits/sec because every 32 chips/bit PN code is interpreted as 2 bits of data. When using this mode a single 64 chips/bit PN code is placed in the PN code register. This 64 chips/bit PN code is then split into two and used by the baseband to offer the Double Data Rate capability. When using Normal Data Rate, the raw data throughput is 32kbits/sec.</p> <p>Additionally, Normal Data Rate enables the user to potentially correlate data using two differing 32 chips/bit PN codes.</p> |

| 0 <sup>[4]</sup> | Sample Rate | <p>The Sample Rate bit allows the use of the 12x sampling when using 32 chips/bit PN codes and Normal Data Rate.</p> <p>1 = 12x Oversampling<br/>   0 = 6x Oversampling</p> <p>Using 12x oversampling improves the correlators receive sensitivity. When using 64 chips/bit PN codes or Double Data Rate this bit is don't care. The only time when 12x oversampling can be selected is when a 32 chips/bit PN code is being used with Normal Data Rate.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

**Table 7. Configuration**

| Addr: 0x05 |   |   |   |   |   |   |   | REG_CONFIG | Default: 0x01  |  |  |

|------------|---|---|---|---|---|---|---|------------|----------------|--|--|

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |            |                |  |  |

| Reserved   |   |   |   |   |   |   |   |            | IRQ Pin Select |  |  |

| Bit | Name           | Description                                                                                                                                                                                                                                                                                                                                                     |

|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Reserved       | These bits are reserved and should be written with zeroes.                                                                                                                                                                                                                                                                                                      |

| 1:0 | IRQ Pin Select | <p>The Interrupt Request Pin Select bits are used to determine the drive method of the IRQ pin.</p> <p>11 = Open Source (IRQ asserted = 1, IRQ deasserted = Hi-Z)<br/>   10 = Open Drain (IRQ asserted = 0, IRQ deasserted = Hi-Z)<br/>   01 = CMOS (IRQ asserted = 1, IRQ deasserted = 0)<br/>   00 = CMOS Inverted (IRQ asserted = 0, IRQ deasserted = 1)</p> |

**Note**

- The following Reg 0x04, bits 2:0 values are not valid:

- 001 – Not Valid

- 010 – Not Valid

- 011 – Not Valid

- 111 – Not Valid.

**Table 8. SERDES Control**

| Addr: 0x06 |   |   |   |   |               |            |   | REG_SERDES_CTL | Default: 0x03 |

|------------|---|---|---|---|---------------|------------|---|----------------|---------------|

| 7          | 6 | 5 | 4 | 3 | 2             | 1          | 0 |                |               |

| Reserved   |   |   |   |   | SERDES Enable | EOF Length |   |                |               |

| Bit | Name          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Reserved      | These bits are reserved and should be written with zeroes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3   | SERDES Enable | <p>The SERDES Enable bit is used to switch between bit-serial mode and SERDES mode.<br/>           1 = SERDES enabled.<br/>           0 = SERDES disabled, bit-serial mode enabled.</p> <p>When the SERDES is enabled data can be written to and read from the IC one byte at a time, through the use of the SERDES Data registers. The bit-serial mode requires bits to be written one bit at a time through the use of the DIO/DIOVAL pins, refer to section 3.2. It is recommended that SERDES mode be used to avoid the need to manage the timing required by the bit-serial mode.</p> |

| 2:0 | EOF Length    | <p>The End of Frame Length bits are used to set the number of sequential bit times for an inter-frame gap without valid data before an EOF event will be generated. When in receive mode and a valid bit has been received the EOF event can then be identified by the number of bit times that expire without correlating any new data. The EOF event causes data to be moved to the proper SERDES Data Register and can also be used to generate interrupts. If 0 is the EOF length, an EOF condition will occur at the first invalid bit after a valid reception.</p>                   |

**Table 9. Receive SERDES Interrupt Enable**

| Addr: 0x07  |            |       |        |             |            |       |        | REG_RX_INT_EN | Default: 0x00 |

|-------------|------------|-------|--------|-------------|------------|-------|--------|---------------|---------------|

| 7           | 6          | 5     | 4      | 3           | 2          | 1     | 0      |               |               |

| Underflow B | Overflow B | EOF B | Full B | Underflow A | Overflow A | EOF A | Full A |               |               |

| Bit | Name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Underflow B | <p>The Underflow B bit is used to enable the interrupt associated with an underflow condition with the Receive SERDES Data B register (Reg 0x0B)</p> <p>1 = Underflow B interrupt enabled for Receive SERDES Data B<br/>           0 = Underflow B interrupt disabled for Receive SERDES Data B</p> <p>An underflow condition occurs when attempting to read the Receive SERDES Data B register (Reg 0x0B) when it is empty.</p>                                                                                                                                                                                                                       |

| 6   | Overflow B  | <p>The Overflow B bit is used to enable the interrupt associated with an overflow condition with the Receive SERDES Data B register (Reg 0x0B)</p> <p>1 = Overflow B interrupt enabled for Receive SERDES Data B<br/>           0 = Overflow B interrupt disabled for Receive SERDES Data B</p> <p>An overflow condition occurs when new received data is written into the Receive SERDES Data B register (Reg 0x0B) before the prior data is read out.</p>                                                                                                                                                                                            |

| 5   | EOF B       | <p>The End of Frame B bit is used to enable the interrupt associated with the Channel B Receiver EOF condition.</p> <p>1 = EOF B interrupt enabled for Channel B Receiver.<br/>           0 = EOF B interrupt disabled for Channel B Receiver.</p> <p>The EOF IRQ asserts during an End of Frame condition. End of Frame conditions occur after at least one bit has been detected, and then the number of invalid bits in the frame exceeds the number in the EOF length field. If 0 is the EOF length, and EOF condition will occur at the first invalid bit after a valid reception. This IRQ is cleared by reading the receive status register</p> |

| 4   | Full B      | <p>The Full B bit is used to enable the interrupt associated with the Receive SERDES Data B register (Reg 0x0B) having data placed in it.</p> <p>1 = Full B interrupt enabled for Receive SERDES Data B<br/>           0 = Full B interrupt disabled for Receive SERDES Data B</p> <p>A Full B condition occurs when data is transferred from the Channel B Receiver into the Receive SERDES Data B register (Reg 0x0B). This could occur when a complete byte is received or when an EOF event occurs whether or not a complete byte has been received.</p>                                                                                           |

| Bit | Name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | Underflow A | The Underflow A bit is used to enable the interrupt associated with an underflow condition with the Receive SERDES Data A register (Reg 0x09)<br>1 = Underflow A interrupt enabled for Receive SERDES Data A<br>0 = Underflow A interrupt disabled for Receive SERDES Data A<br>An underflow condition occurs when attempting to read the Receive SERDES Data A register (Reg 0x09) when it is empty.                                                                                                                                                                                                                                      |

| 2   | Overflow A  | The Overflow A bit is used to enable the interrupt associated with an overflow condition with the Receive SERDES Data A register (0x09)<br>1 = Overflow A interrupt enabled for Receive SERDES Data A<br>0 = Overflow A interrupt disabled for Receive SERDES Data A<br>An overflow condition occurs when new receive data is written into the Receive SERDES Data A register (Reg 0x09) before the prior data is read out.                                                                                                                                                                                                                |

| 1   | EOF A       | The End of Frame A bit is used to enable the interrupt associated with an End of Frame condition with the Channel A Receiver.<br>1 = EOF A interrupt enabled for Channel A Receiver.<br>0 = EOF A interrupt disabled for Channel A Receiver.<br>The EOF IRQ asserts during an End of Frame condition. End of Frame conditions occur after at least one bit has been detected, and then the number of invalid bits in a frame exceeds the number in the EOF length field. If 0 is the EOF length, an EOF condition will occur at the first invalid bit after a valid reception. This IRQ is cleared by reading the receive status register. |

| 0   | Full A      | The Full A bit is used to enable the interrupt associated with the Receive SERDES Data A register (0x09) having data written into it.<br>1 = Full A interrupt enabled for Receive SERDES Data A<br>0 = Full A interrupt disabled for Receive SERDES Data A<br>A Full A condition occurs when data is transferred from the Channel A Receiver into the Receive SERDES Data A register (Reg 0x09). This could occur when a complete byte is received or when an EOF event occurs whether or not a complete byte has been received.                                                                                                           |

**Table 10. Receive SERDES Interrupt Status<sup>[5]</sup>**

| Addr: 0x08 |  |                  |  |       |  |        |  | REG_RX_INT_STAT |  |                  |  |       |  |        |  | Default: 0x00 |  |  |  |  |  |  |  |

|------------|--|------------------|--|-------|--|--------|--|-----------------|--|------------------|--|-------|--|--------|--|---------------|--|--|--|--|--|--|--|

| 7          |  | 6                |  | 5     |  | 4      |  | 3               |  | 2                |  | 1     |  | 0      |  |               |  |  |  |  |  |  |  |

| Valid B    |  | Flow Violation B |  | EOF B |  | Full B |  | Valid A         |  | Flow Violation A |  | EOF A |  | Full A |  |               |  |  |  |  |  |  |  |

| Bit | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Valid B          | The Valid B bit is true when all the bits in the Receive SERDES Data B register (Reg 0x0B) are valid.<br>1 = All bits are valid for Receive SERDES Data B.<br>0 = Not all bits are valid for Receive SERDES Data B.<br>When data is written into the Receive SERDES Data B register (Reg 0x0B) this bit is set if all of the bits within the byte that has been written are valid. This bit cannot generate an interrupt.                                                                                                                                                                                                                                          |

| 6   | Flow Violation B | The Flow Violation B bit is used to signal whether an overflow or underflow condition has occurred for the Receive SERDES Data B register (Reg 0x0B).<br>1 = Overflow/underflow interrupt pending for Receive SERDES Data B.<br>0 = No overflow/underflow interrupt pending for Receive SERDES Data B.<br>Overflow conditions occur when the radio loads new data into the Receive SERDES Data B register (Reg 0x0B) before the prior data has been read. Underflow conditions occur when trying to read the Receive SERDES Data B register (Reg 0x0B) when the register is empty. This bit is cleared by reading the Receive Interrupt Status register (Reg 0x08) |

**Note**

5. All status bits are set and readable in the registers regardless of IRQ enable status. This allows a polling scheme to be implemented without enabling IRQs. The status bits are affected by TX Enable and RX Enable (Reg 0x03, bits 7:6). For example, the receive status will read 0 if the IC is not in receive mode. These registers are read-only.

| Bit | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | EOF B            | <p>The End of Frame B bit is used to signal whether an EOF event has occurred on the Channel B receive.</p> <p>1 = EOF interrupt pending for Channel B.</p> <p>0 = No EOF interrupt pending for Channel B.</p> <p>An EOF condition occurs for the Channel B Receiver when receive has begun and then the number of bit times specified in the SERDES Control register (Reg 0x06) elapse without any valid bits being received. This bit is cleared by reading the Receive Interrupt Status register (Reg 0x08)</p>                                                                                                                                                                    |

| 4   | Full B           | <p>The Full B bit is used to signal when the Receive SERDES Data B register (Reg 0x0B) is filled with data.</p> <p>1 = Receive SERDES Data B full interrupt pending.</p> <p>0 = No Receive SERDES Data B full interrupt pending.</p> <p>A Full B condition occurs when data is transferred from the Channel B Receiver into the Receive SERDES Data B register (Reg 0x0B). This could occur when a complete byte is received or when an EOF event occurs whether or not a complete byte has been received.</p>                                                                                                                                                                        |

| 3   | Valid A          | <p>The Valid A bit is true when all of the bits in the Receive SERDES Data A Register (Reg 0x09) are valid.</p> <p>1 = All bits are valid for Receive SERDES Data A.</p> <p>0 = Not all bits are valid for Receive SERDES Data A.</p> <p>When data is written into the Receive SERDES Data A register (Reg 0x09) this bit is set if all of the bits within the byte that has been written are valid. This bit cannot generate an interrupt.</p>                                                                                                                                                                                                                                       |

| 2   | Flow Violation A | <p>The Flow Violation A bit is used to signal whether an overflow or underflow condition has occurred for the Receive SERDES Data A register (Reg 0x09).</p> <p>1 = Overflow/underflow interrupt pending for Receive SERDES Data A.</p> <p>0 = No overflow/underflow interrupt pending for Receive SERDES Data A.</p> <p>Overflow conditions occur when the radio loads new data into the Receive SERDES Data A register (Reg 0x09) before the prior data has been read. Underflow conditions occur when trying to read the Receive SERDES Data A register (Reg 0x09) when the register is empty. This bit is cleared by reading the Receive Interrupt Status register (Reg 0x08)</p> |

| 1   | EOF A            | <p>The End of Frame A bit is used to signal whether an EOF event has occurred on the Channel A receive.</p> <p>1 = EOF interrupt pending for Channel A.</p> <p>0 = No EOF interrupt pending for Channel A.</p> <p>An EOF condition occurs for the Channel A Receiver when receive has begun and then the number of bit times specified in the SERDES Control register (0x06) elapse without any valid bits being received. This bit is cleared by reading the Receive Interrupt Status register (Reg 0x08).</p>                                                                                                                                                                       |

| 0   | Full A           | <p>The Full A bit is used to signal when the Receive SERDES Data A register (Reg 0x09) is filled with data.</p> <p>1 = Receive SERDES Data A full interrupt pending.</p> <p>0 = No Receive SERDES Data A full interrupt pending.</p> <p>A Full A condition occurs when data is transferred from the Channel A Receiver into the Receive SERDES Data A Register (Reg 0x09). This could occur when a complete byte is received or when an EOF event occurs whether or not a complete byte has been received.</p>                                                                                                                                                                        |

**Table 11. Receive SERDES Data A**

| Addr: 0x09 |   |   |   |   |   |   |   | REG_RX_DATA_A | Default: 0x00 |

|------------|---|---|---|---|---|---|---|---------------|---------------|

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Data          |               |

| Data       |   |   |   |   |   |   |   |               |               |

| Bit | Name | Description                                                                                                                                                                                                                            |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Data | Received Data for Channel A. The over-the-air received order is bit 0 followed by bit 1, followed by bit 2, followed by bit 3, followed by bit 4, followed by bit 5, followed by bit 6, followed by bit 7. This register is read-only. |

**Table 12. Receive SERDES Valid A**

| Addr: 0x0A |   |   |   |   |   |   |   | REG_RX_VALID_A | Default: 0x00 |

|------------|---|---|---|---|---|---|---|----------------|---------------|

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Valid          |               |

| Valid      |   |   |   |   |   |   |   |                |               |

| Bit | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Valid | These bits indicate which of the bits in the Receive SERDES Data A register (Reg 0x09) are valid. A "1" indicates that the corresponding data bit is valid for Channel A. If the Valid Data bit is set in the Receive Interrupt Status register (Reg 0x08) all eight bits in the Receive SERDES Data A register (Reg 0x0A) are valid. Therefore, it is not necessary to read the Receive SERDES Valid A register (Reg 0x0C). This register is read-only. |

**Figure 9. Receive SERDES Data B**

| Addr: 0x0B |   |   |   |   |   |   |   | REG_RX_DATA_B | Default: 0x00 |

|------------|---|---|---|---|---|---|---|---------------|---------------|

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Data          |               |

| Data       |   |   |   |   |   |   |   |               |               |

| Bit | Name | Description                                                                                                                                                                                                                            |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Data | Received Data for Channel B. The over-the-air received order is bit 0 followed by bit 1, followed by bit 2, followed by bit 3, followed by bit 4, followed by bit 5, followed by bit 6, followed by bit 7. This register is read-only. |

**Table 13. Receive SERDES Valid B**

| Addr: 0x0C |   |   |   |   |   |   |   | REG_RX_VALID_B | Default: 0x00 |

|------------|---|---|---|---|---|---|---|----------------|---------------|

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Valid          |               |

| Valid      |   |   |   |   |   |   |   |                |               |

| Bit | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Valid | These bits indicate which of the bits in the Receive SERDES Data B register (Reg 0x0B) are valid. A "1" indicates that the corresponding data bit is valid for Channel B. If the Valid Data bit is set in the Receive Interrupt Status register (0x08) all eight bits in the Receive SERDES Data B register (Reg 0x0C) are valid. Therefore, it is not necessary to read the Receive SERDES Valid B register (Reg 0x0C). This register is read-only. |

**Table 14. Transmit SERDES Interrupt Enable**

| Addr: 0x0D |   |   |   |           |   |          |   | REG_TX_INT_EN | Default: 0x00 |

|------------|---|---|---|-----------|---|----------|---|---------------|---------------|

| 7          | 6 | 5 | 4 | 3         | 2 | 1        | 0 |               |               |

| Reserved   |   |   |   | Underflow |   | Overflow |   | Done          | Empty         |

| Bit | Name     | Description                                                |

|-----|----------|------------------------------------------------------------|

| 7:4 | Reserved | These bits are reserved and should be written with zeroes. |

| Bit | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | Underflow | The Underflow bit is used to enable the interrupt associated with an underflow condition associated with the Transmit SERDES Data register (Reg 0x0F)<br>1 = Underflow interrupt enabled.<br>0 = Underflow interrupt disabled.<br>An underflow condition occurs when attempting to transmit while the Transmit SERDES Data register (Reg 0x0F) does not have any data.                                        |

| 2   | Overflow  | The Overflow bit is used to enable the interrupt associated with an overflow condition with the Transmit SERDES Data register (0x0F).<br>1 = Overflow interrupt enabled.<br>0 = Overflow interrupt disabled.<br>An overflow condition occurs when attempting to write new data to the Transmit SERDES Data register (Reg 0x0F) before the preceding data has been transferred to the transmit shift register. |

| 1   | Done      | The Done bit is used to enable the interrupt that signals the end of the transmission of data.<br>1 = Done interrupt enabled.<br>0 = Done interrupt disabled.<br>The Done condition occurs when the Transmit SERDES Data register (Reg 0x0F) has transmitted all of its data and there is no more data for it to transmit.                                                                                    |

| 0   | Empty     | The Empty bit is used to enable the interrupt that signals when the Transmit SERDES register (Reg 0x0F) is empty.<br>1 = Empty interrupt enabled.<br>0 = Empty interrupt disabled.<br>The Empty condition occurs when the Transmit SERDES Data register (Reg 0x0F) is loaded into the transmit buffer and it's safe to load the next byte                                                                     |

**Table 15. Transmit SERDES Interrupt Status<sup>[6]</sup>**

| Addr: 0x0E |   |   |   |           |          |      |       | REG_TX_INT_STAT | Default: 0x00 |

|------------|---|---|---|-----------|----------|------|-------|-----------------|---------------|

| 7          | 6 | 5 | 4 | 3         | 2        | 1    | 0     |                 |               |

| Reserved   |   |   |   | Underflow | Overflow | Done | Empty |                 |               |

| Bit | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Reserved  | These bits are reserved. This register is read-only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3   | Underflow | <p>The Underflow bit is used to signal when an underflow condition associated with the Transmit SERDES Data register (Reg 0x0F) has occurred.</p> <p>1 = Underflow Interrupt pending.<br/>0 = No Underflow Interrupt pending.</p> <p>This IRQ will assert during an underflow condition to the Transmit SERDES Data register (Reg 0x0F). An underflow occurs when the transmitter is ready to sample transmit data, but there is no data ready in the Transmit SERDES Data register (Reg 0x0F). This will only assert after the transmitter has transmitted at least one bit. This bit is cleared by reading the Transmit Interrupt Status register (Reg 0x0E).</p> |

| 2   | Overflow  | <p>The Overflow bit is used to signal when an overflow condition associated with the Transmit SERDES Data register (0x0F) has occurred.</p> <p>1 = Overflow Interrupt pending.<br/>0 = No Overflow Interrupt pending.</p> <p>This IRQ will assert during an overflow condition to the Transmit SERDES Data register (Reg 0x0F). An overflow occurs when the new data is loaded into the Transmit SERDES Data register (Reg 0x0F) before the previous data has been sent. This bit is cleared by reading the Transmit Interrupt Status register (Reg 0x0E).</p>                                                                                                      |

| 1   | Done      | <p>The Done bit is used to signal the end of a data transmission.</p> <p>1 = Done Interrupt pending.<br/>0 = No Done Interrupt pending.</p> <p>This IRQ will assert when the data is finished sending a byte of data and there is no more data to be sent. This will only assert after the transmitter has transmitted at least one bit. This bit is cleared by reading the Transmit Interrupt Status register (Reg 0x0E).</p>                                                                                                                                                                                                                                      |

| 0   | Empty     | <p>The Empty bit is used to signal when the Transmit SERDES Data register (Reg 0x0F) has been emptied.</p> <p>1 = Empty Interrupt pending.<br/>0 = No Empty Interrupt pending.</p> <p>This IRQ will assert when the transmit serdes is empty. When this IRQ is asserted it is ok to write to the Transmit SERDES Data register (Reg 0x0F). Writing the Transmit SERDES Data register (Reg 0x0F) will clear this IRQ. It will be set when the data is loaded into the transmitter, and it is ok to write new data.</p>                                                                                                                                               |

**Note**

6. All status bits are set and readable in the registers regardless of IRQ enable status. This allows a polling scheme to be implemented without enabling IRQs. The status bits are affected by the TX Enable and RX Enable (Reg 0x03, bits 7:6). For example, the transmit status will read 0 if the IC is not in transmit mode. These registers are read-only.

**Table 16. Transmit SERDES Data**

| Addr: 0x0F |   |   |   |   |   |   |   | REG_TX_DATA |  | Default: 0x00 |  |

|------------|---|---|---|---|---|---|---|-------------|--|---------------|--|

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Data        |  |               |  |

|            |   |   |   |   |   |   |   |             |  |               |  |

| Bit | Name | Description                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 7:0 | Data | Transmit Data. The over-the-air transmitted order is bit 0 followed by bit 1, followed by bit 2, followed by bit 3, followed by bit 4, followed by bit 5, followed by bit 6, followed by bit 7. |  |  |  |  |  |  |  |  |  |

**Table 17. Transmit SERDES Valid**

| Addr: 0x10 |   |   |   |   |   |   |   | REG_TX_VALID |  | Default: 0x00 |  |

|------------|---|---|---|---|---|---|---|--------------|--|---------------|--|

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Valid        |  |               |  |

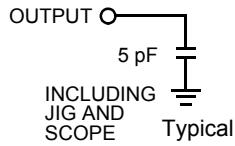

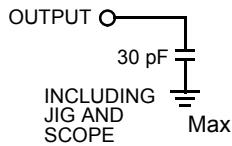

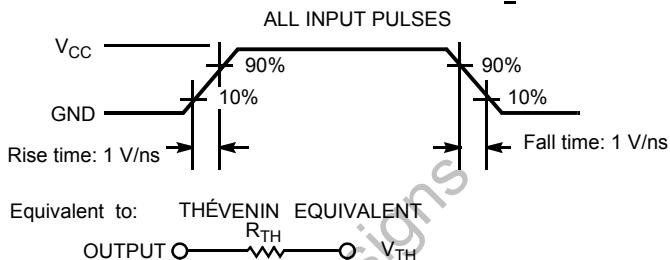

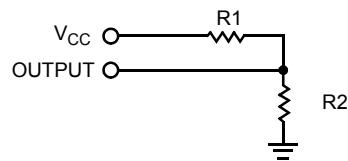

|            |   |   |   |   |   |   |   |              |  |               |  |