# **Future Technology Devices International Ltd.**

# V2-EVAL

# Vinculum II Evaluation Board Datasheet

**Document Reference No.: FT\_000247**

Version 1.0

Issue Date: 2010-04-15

**Future Technology Devices International Ltd (FTDI)**

Unit 1, 2 Seaward Place, Centurion Business Park, Glasgow, G41 1HH, United Kingdom

Tel.: +44 (0) 141 429 2777 Fax: + 44 (0) 141 429 2758

E-Mail (Support): <a href="mailto:support1@ftdichip.com">support1@ftdichip.com</a>

Web: http://www.vinculum.com

Neither the whole nor any part of the information contained in, or the product described in this manual, may be adapted or reproduced in any material or electronic form without the prior written consent of the copyright holder. This product and its documentation are supplied on an as-is basis and no warranty as to their suitability for any particular purpose is either made or implied. Future Technology Devices International Ltd will not accept any claim for damages howsoever arising as a result of use or failure of this product. Your statutory rights are not affected. This product or any variant of it is not intended for use in any medical appliance, device or system in which the failure of the product might reasonably be expected to result in personal injury. This document provides preliminary information that may be subject to change without notice. No freedom to use patents or other intellectual property rights is implied by the publication of this document. Future Technology Devices International Ltd, Unit 1, 2 Seaward Place, Centurion Business Park, Glasgow, G41 1HH, United Kingdom. Scotland Registered Number: SC136640

# **Table of Contents**

| 1 | Int                 | troduction                             | . 3 |

|---|---------------------|----------------------------------------|-----|

|   | 1.1                 | Handling the board                     | . 3 |

|   | 1.2                 | Environmental requirements             | . 3 |

|   | 1.3                 | References                             | . 4 |

|   | 1.4                 | Acronyms and Abbreviations             | . 5 |

| 2 | Во                  | ard Description                        |     |

|   | 2.1                 | V2-EVAL Board Features                 |     |

|   | 2.2                 | Specifications                         |     |

|   |                     | -Eval Board Components and Interfaces  |     |

|   | <b>V</b> 2<br>3.1   |                                        |     |

|   | 3.1.                | <del>-</del>                           |     |

|   | 3.1.                | ·                                      |     |

| 4 |                     | itial Board Set-up & Test              |     |

| _ | 4.1                 | Installing VNC2 Daughterboard          |     |

|   | <del>-</del><br>4.2 | Testing the board                      |     |

|   |                     | _                                      |     |

| 5 |                     | tailed Description of Board Components |     |

|   | 5.1                 | Power Select Jumper JP6                |     |

|   | 5.2                 | GPIO BUS Connectors                    |     |

|   | 5.2.                | L- J                                   |     |

|   | 5.2.                |                                        |     |

|   | 5.2.<br>5.2.        |                                        |     |

|   | 5.2.                |                                        |     |

|   | 5.2.                |                                        |     |

|   | 5.3                 | SPI Connector C9                       |     |

|   | 5.4                 | UART Interface Connector C10           |     |

|   | 5.5                 | FIFO Interface Connector CN11          |     |

|   | 5.6                 | Prototyping area                       |     |

|   | 5.7                 | USB1 interface CN1                     |     |

|   | 5.8                 | USB2 interface CN2                     |     |

|   | 5.9                 | GPIO Jumpers JP1, JP2                  |     |

|   |                     | User LEDs. LED3 – LED6                 |     |

|   |                     |                                        |     |

|   | <b>3.</b> 11        | LED enable/disable jumpers JP10 - JP14 | 23  |

1

| Clearance | No.: | FTDI#14 | 8 |

|-----------|------|---------|---|

| o.ca.aco  |      |         | _ |

|   | 5.12      | User push button switches                 | 30 |

|---|-----------|-------------------------------------------|----|

|   | 5.13      | Host USB power jumpers JP4, JP5           | 30 |

|   | 5.14      | Remote Wakeup jumper JP3                  | 31 |

|   | 5.15      | Reset Push-button Switch                  | 32 |

|   | 5.16      | 'PROG' LED                                | 32 |

|   | 5.17      | VNC2 Daughterboard Connector – J1         | 33 |

|   | 5.18      | VNC2 Daughterboard Connector – J2         | 34 |

|   | 5.19      | VNC2 Daughterboard Connector – J3         | 35 |

|   | 5.20      | VNC2 Daughterboard Connector – J4         | 36 |

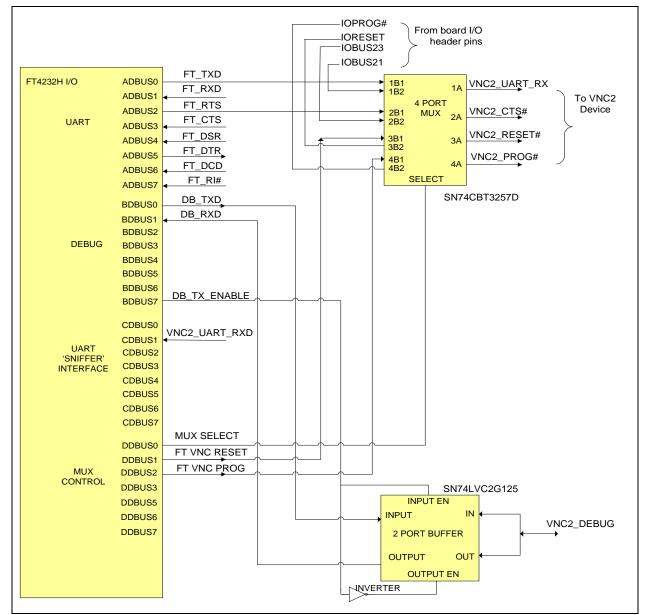

| 6 | FT        | 4232H Configuration                       | 37 |

|   | 6.1       | UART Interface                            | 38 |

|   | 6.2       | Debug Interface - UART Mode               | 39 |

|   | 6.3       | UART 'Sniffer' Interface                  | 39 |

|   | 6.4       | Device Control – Bit Bang Mode            | 39 |

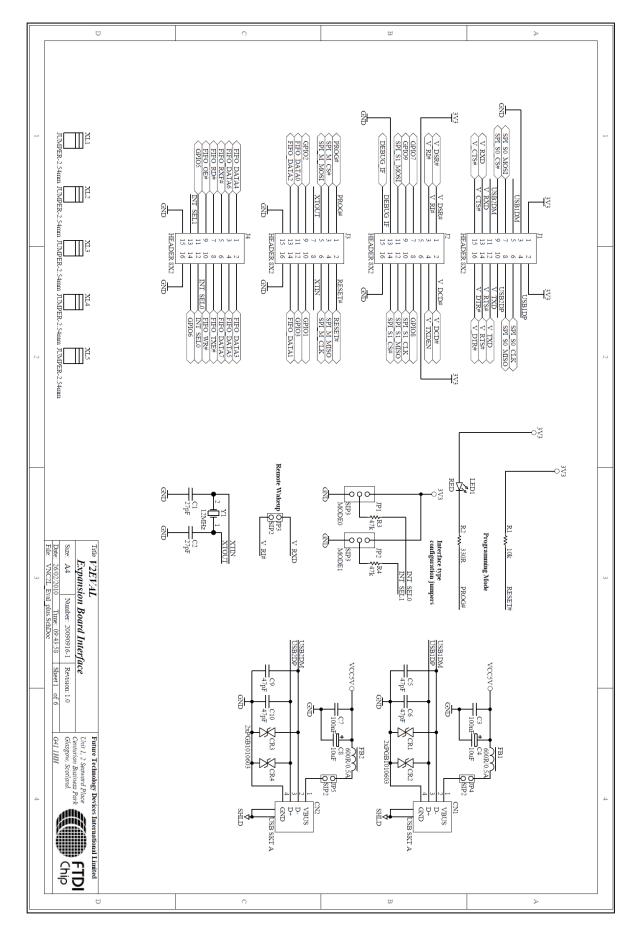

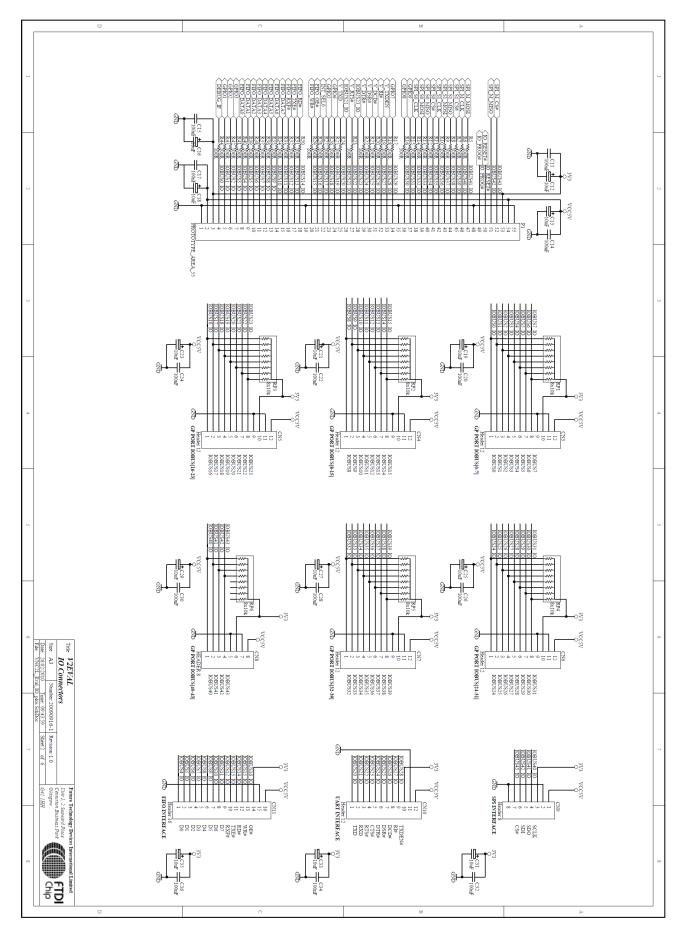

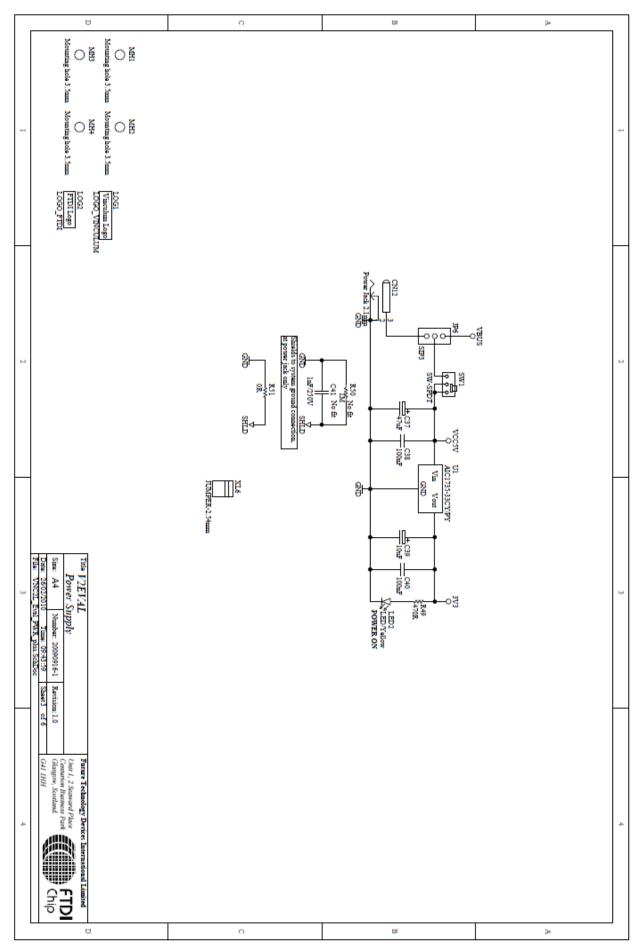

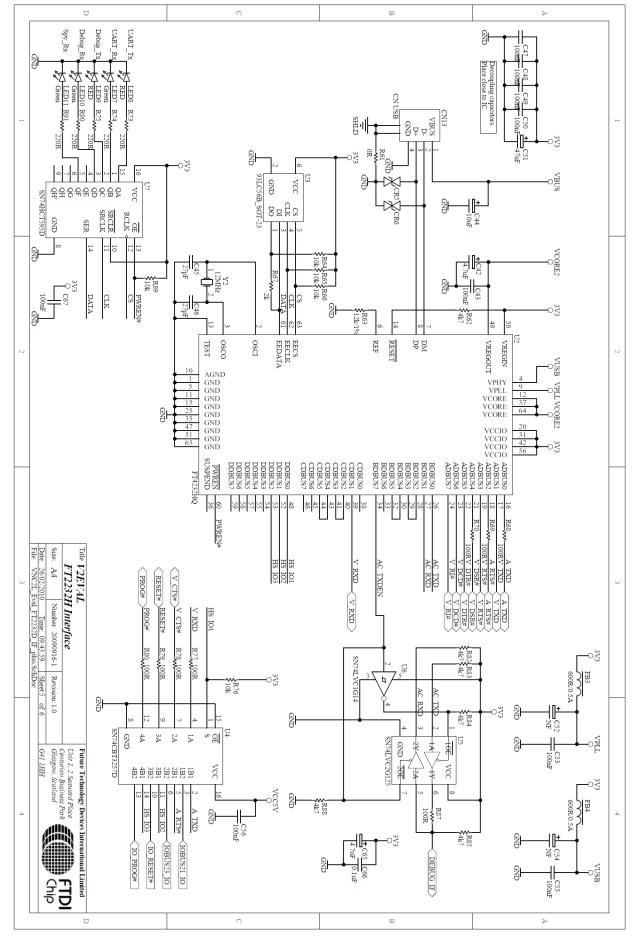

| 7 | Во        | ard Schematics                            | 40 |

|   | 7.1       | V2-EVAL Board Schematics                  | 41 |

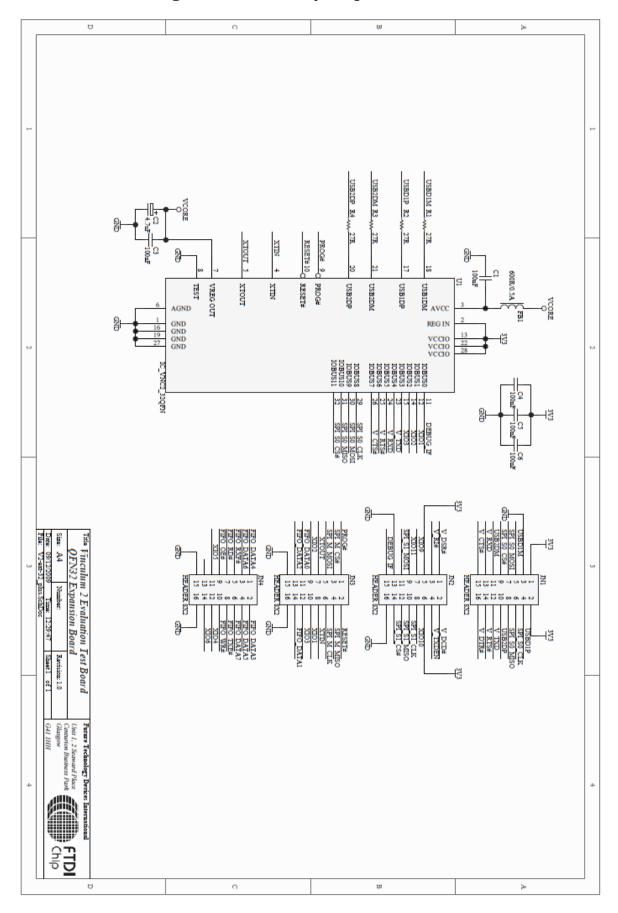

|   | 7.2       | VNC2 Daughterboard 32-pin QFN Schematic   | 46 |

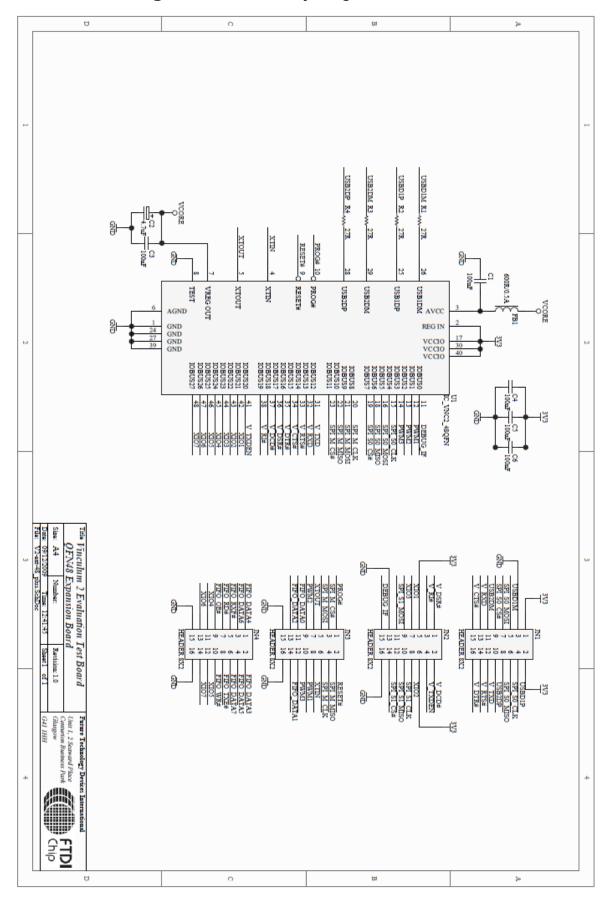

|   | 7.3       | VNC2 Daughterboard - 48-pin QFN Schematic | 47 |

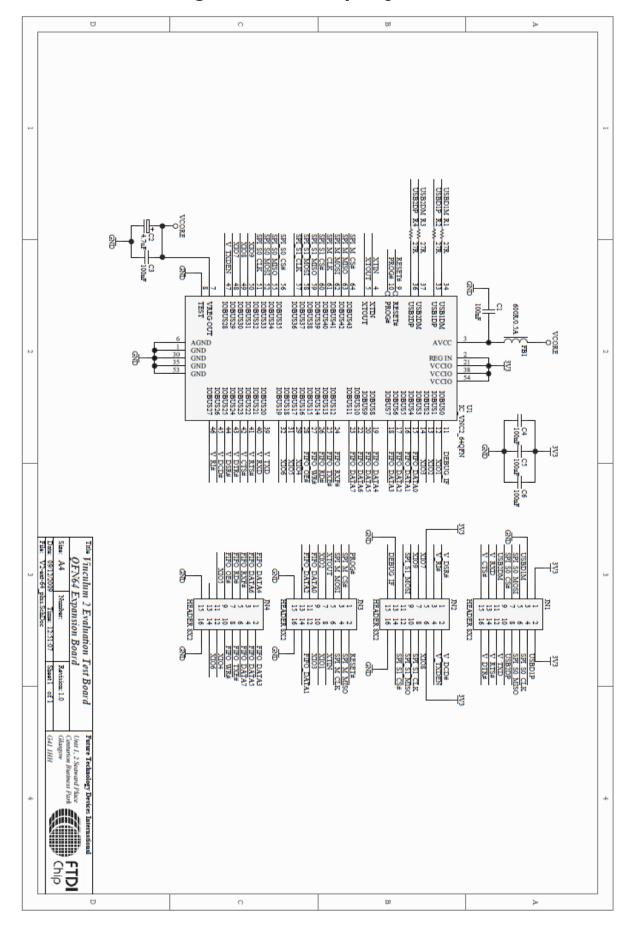

|   | 7.4       | VNC2 Daughterboard - 64-pin QFN Schematic |    |

| 8 | <b>V2</b> | -EVAL Board Assembly Drawing              |    |

|   |           | ct Information                            |    |

| _ |           | ndix A - List of Figures and Tables       |    |

|   |           | of Figures                                |    |

|   |           | of Tables                                 |    |

| Λ |           | ndix B – Revision History                 |    |

| ~ | Phei      | IUIA D — NEVISIUII IIISIUI Y              | JJ |

#### 1 Introduction

The following document details the features and specifications of the V2-EVAL board. The V2-EVAL is a hardware platform designed to support easy evaluation of FTDI's Vinculum-II (VNC2) series of embedded USB host controller devices.

The V2-Eval kit includes the following hardware items as standard

- 1 x V2-Eval base board.

- 1 x 5V/1A mains adapter PSU UK, US, European and Japanese versions available.

- 1 x USB A/B cable to connect to a host PC in programming / terminal emulation or debugging modes.

- 1 x USB gender changer for USB slave mode applications.

#### NOTE:

The V2-EVAL kit requires a VNC2 based daughterboard module to be installed into the V2-EVAL base board socket site, in order to enable development with the kit.

Daughterboard modules are sold separately, with 3 versions available for 32-pin, 48-pin and 64-pin package devices. Daughterboard modules can be purchased from FTDI or via our website <a href="http://www.ftdichip.com">http://www.ftdichip.com</a>.

#### Before you proceed:

Please check that all the contents of the package are not damaged.

Ensure that your kit includes a proper version of the power supply, depending on the region where you live. Eval application software and project examples can be downloaded from: <a href="http://www.ftdichip.com">http://www.ftdichip.com</a>

## 1.1 Handling the board

**Static discharge precaution** – Without proper anti-static handling the board can be damaged. Therefore, take anti-static precautions while handling the board.

#### 1.2 Environmental requirements

The V2-Eval Board must be stored between -40°C and  $80^{\circ}$ C. The recommended operating temperature is between  $0^{\circ}$ C and  $55^{\circ}$ C

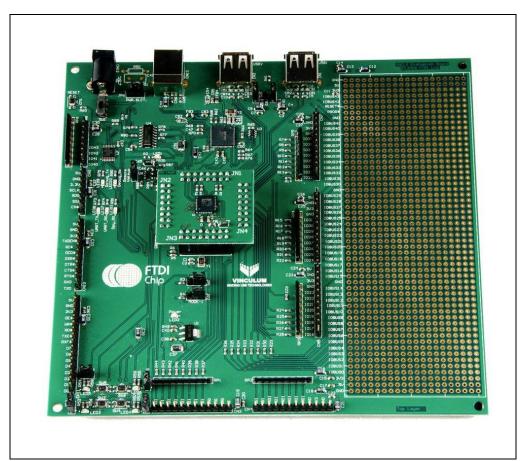

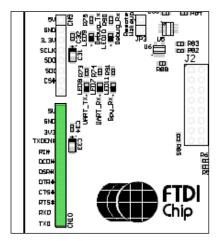

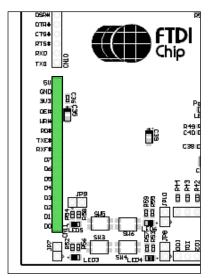

Figure 1.1 - V2-EVAL Motherboard(left) with Daughterboard Module(right)

## 1.3 Part Numbers

| Part Number                                                   | Description                                                                 |  |  |

|---------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| V2-EVAL V2-EVAL kit with base board, power supply and cables. |                                                                             |  |  |

| V2-EVAL-EXT32                                                 | VNC2 daughterboard module with 32-pin QFN VNC2 device for use with V2-EVAL. |  |  |

| V2-EVAL-EXT48                                                 | VNC2 daughterboard module with 48-pin QFN VNC2 device for use with V2-EVAL. |  |  |

| V2-EVAL-EXT64                                                 | VNC2 daughterboard module with 64-pin QFN VNC2 device for use with V2-EVAL. |  |  |

Table 1.0 Part Numbers.

## 1.4 References

The document contains references to the following websites and documents. Links to most documents are available from the FTDI website,  $\frac{\text{http://www.ftdichip.com}}{\text{http://www.ftdichip.com}}$ .

| Document Name Description                                                 |                                                                                                                              |  |  |  |  |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1. FT_000138 Vinculum-II Embedded Dual USB Host Controller IC Data Sheet. |                                                                                                                              |  |  |  |  |

| 2. FT_000060 FT4232H Data Sheet.                                          |                                                                                                                              |  |  |  |  |

| 3. AN_137 Vinculum-II IO Cell Description.                                |                                                                                                                              |  |  |  |  |

| 4. AN_138 Vinculum-II Debug Interface Description.                        |                                                                                                                              |  |  |  |  |

| 5. AN_139 Vinculum-II IO Mux Explained.                                   |                                                                                                                              |  |  |  |  |

| 6. AN_140 Vinculum-II PWM Example.                                        |                                                                                                                              |  |  |  |  |

| 7. USB 2.0                                                                | Universal Serial Bus Specification Revision 2.0 USB Implementers Forum <a href="http://www.usb.org">http://www.usb.org</a> . |  |  |  |  |

Table 1.1 Document References.

Clearance No.: FTDI#148

# 1.5 Acronyms and Abbreviations

| Terms | Description                                  |  |  |  |

|-------|----------------------------------------------|--|--|--|

| FIFO  | First In First Out.                          |  |  |  |

| GPIO  | General Purpose Input Output.                |  |  |  |

| I/O   | Input / Output.                              |  |  |  |

| MISO  | Master In Slave Out.                         |  |  |  |

| MOSI  | Master Out Slave In.                         |  |  |  |

| SPI   | Serial Peripheral Interface.                 |  |  |  |

| UART  | Universal Asynchronous Receiver/Transmitter. |  |  |  |

| USB   | Universal Serial Bus.                        |  |  |  |

| VNC2  | Vinculum-II.                                 |  |  |  |

Table 1.2 Acronyms and Abbreviations

2 Board Description

V2-Eval Board is intended for use as a hardware platform to enable easy evaluation of FTDI's Vinculum-II VNC2 series of embedded USB Host / Slave controllers. The V2-Eval Board includes all the necessary components required by a user to begin developing USB Host / Slave system applications based on the VNC2 device.

#### 2.1 V2-EVAL Board Features

- VNC2 Embedded USB Host / Slave chip accessible via daughterboard.

- Selection of VNC2 daughterboards to support 32-pin, 48-pin and 64-pin QFN packages.

- Two USB type A connectors for connecting to USB slave peripherals.

- VNC2 IO port connectors grouped by port name/or function.

- FT42232H –USB to guad channel UART device for VNC2 programming & debug functions.

- One USB type B connector for connection to PC host via FT4232H.

- 4 User-programmable LEDs.

- 4 User-programmable push button switches.

## 2.2 Specifications

- Board supply voltage: 4.75V ... 5.25V.

- Board supply current: 60mA (with no USB devices on USB1 or USB2 port).

- IO connectors power output: 5V/150mA, 3.3V/150mA.

- Base board dimensions: 167mm x 156mm x 1.5mm (L x W x H).

- VNC2 daughterboard dimensions: 37.9mm x 32.48mm x 10.0mm (L x W x H).

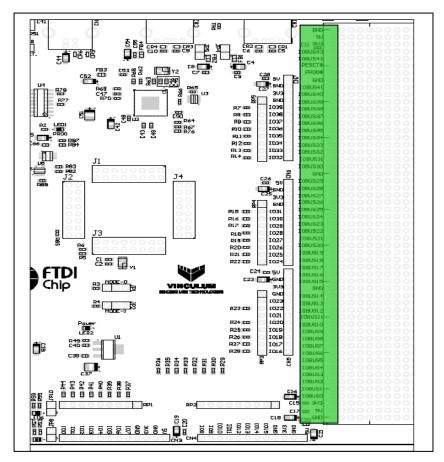

#### 3 V2-Eval Board Components and Interfaces

This chapter describes the operational and connectivity information for the V2-Eval board major components and interfaces.

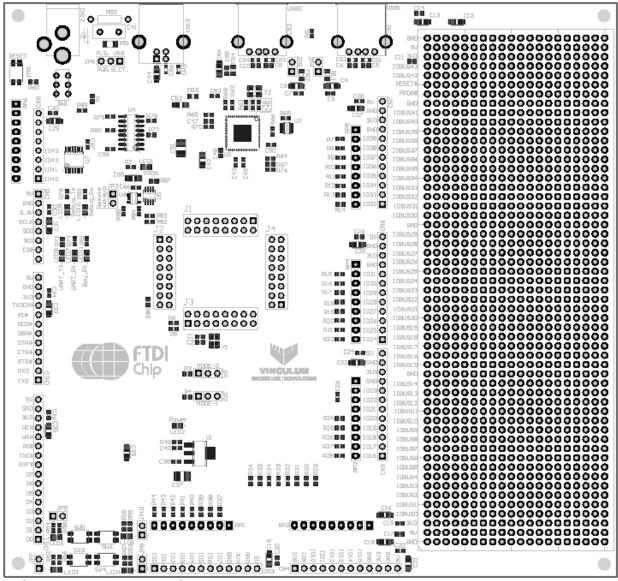

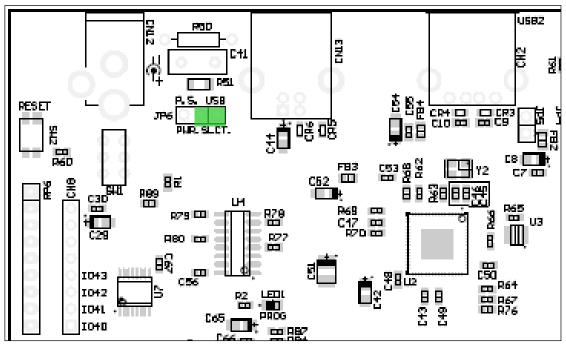

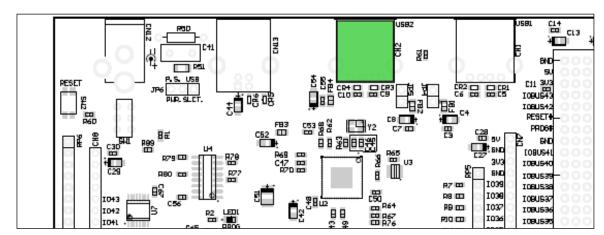

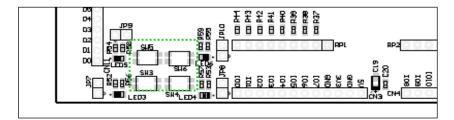

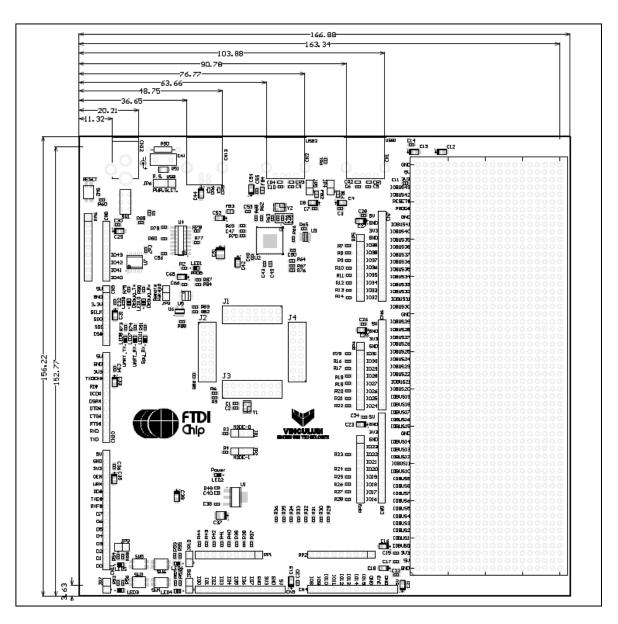

Figure 3.1 V2-EVAL Board Layout

## 3.1 Block Diagram

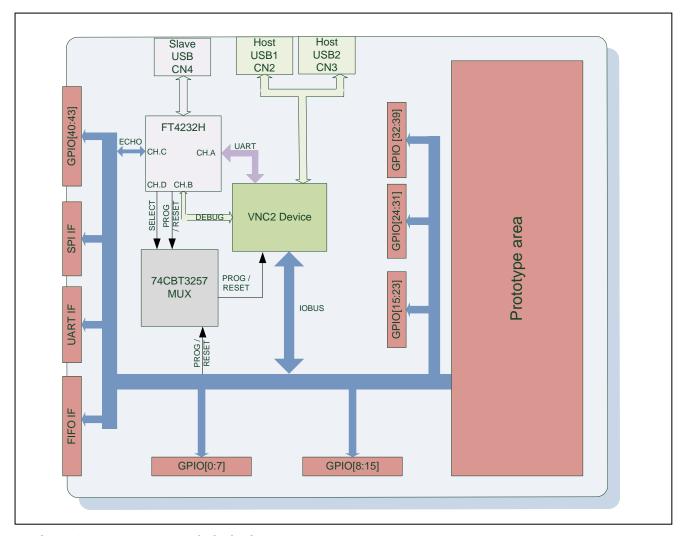

Figure 3.2 V2-EVAL Board Block Diagram.

## 3.1.1 Components.

| Component                 | Board designator | Description                                            |  |  |  |  |

|---------------------------|------------------|--------------------------------------------------------|--|--|--|--|

| USB-UART bridge           | U2               | FT4232H USB $\Leftrightarrow$ Quad UART/FIFO device.   |  |  |  |  |

| Configuration memory      | U3               | 9356 Serial SPI EEPROM for FT4232H configuration data. |  |  |  |  |

| IO multiplexer            | U4               | 74CBT3257 4-bit, 1to2, FET Multiplexer/Demultiplexer.  |  |  |  |  |

| 3.3V regulator            | U1               | AIC1735-33 Ultra low dropout 3.3V voltage regulator.   |  |  |  |  |

| 12MHz crystal             | Y2               | 12MHz crystal for FT4232H.                             |  |  |  |  |

| Single 5V DC power supply | CN12             | Board adapter for included 5V DC power supply.         |  |  |  |  |

| Power switch              | SW1              | Power On/Off switch.                                   |  |  |  |  |

| Power source select       | JP6              | Power source selection jumper.                         |  |  |  |  |

| Reset button              | SW2              | Push-button switch for manual reset of VNC2 device.    |  |  |  |  |

| Keyboard                  | SW3-SW6          | Four user push-button switches.                        |  |  |  |  |

| User LEDs                 | LED3-LED6        | Four green user LEDs.                                  |  |  |  |  |

| PROG LED                  | LED1             | Red LED.                                               |  |  |  |  |

| Power LED                 | LED2             | Green LED.                                             |  |  |  |  |

| UART RX LED               | LED7             | Green LED.                                             |  |  |  |  |

| UART TX LED               | LED8             | Red LED.                                               |  |  |  |  |

| Debug TX                  | LED9             | Red LED.                                               |  |  |  |  |

| Debug RX                  | LED10            | Green LED.                                             |  |  |  |  |

| SPI_RX                    | LED11            | Green LED.                                             |  |  |  |  |

| LEDs enable jumpers       | JP7-JP10         | Enable/disable user-defined LEDs.                      |  |  |  |  |

| GPIO I/O Jumpers          | JP1, JP2         | GPIO I/O jumpers .                                     |  |  |  |  |

| REMOTE WAKEUP             | JP3              | VNC2 remote wakeup jumper.                             |  |  |  |  |

| VBUS jumpers              | JP4, JP5         | USB1, USB2 power bus enable jumpers.                   |  |  |  |  |

Table 3.1 V2-Eval Board Components.

## 3.1.2 Interfaces.

| Component                          | Board designator | Description                                                              |  |  |  |  |

|------------------------------------|------------------|--------------------------------------------------------------------------|--|--|--|--|

| USB1, USB2 <sup>(1)</sup> CN1, CN2 |                  | VNC2 USB host ports 1&2.                                                 |  |  |  |  |

| USB Type B                         | CN13             | FT4232H USB Slave connection.                                            |  |  |  |  |

| VNC2 Socket                        | J1 -J4           | Daughterboard connectors for VNC2 Daughterboard.                         |  |  |  |  |

| SPI (2)                            | CN9              | VNC2 SPI interface pins.                                                 |  |  |  |  |

| UART (2)                           | CN10             | VNC2 UART interface pins.                                                |  |  |  |  |

| FIFO <sup>(2)</sup> CN11           |                  | VNC2 FIFO interface pins.                                                |  |  |  |  |

| IOBUS[70] <sup>(2)</sup> CN3       |                  | VNC2 IOBUS [7:0] port pins.                                              |  |  |  |  |

| IOBUS[815] <sup>(2)</sup> CN4      |                  | VNC2 IOBUS [8:15] port pins.                                             |  |  |  |  |

| IOBUS[1623] (2) CN5                |                  | VNC2 IOBUS [16:23] port pins.                                            |  |  |  |  |

| IOBUS[2431] (2) CN6                |                  | VNC2 IOBUS [24:31] port pins.                                            |  |  |  |  |

| IOBUS[3239] <sup>(2)</sup> CN7     |                  | VNC2 IOBUS [32:39] port pins.                                            |  |  |  |  |

| IOBUS[4043] <sup>(2)</sup> CN8     |                  | VNC2 IOBUS [40:43] port pins.                                            |  |  |  |  |

| Prototyping area <sup>(2)</sup>    | P1               | All of VNC2 IO ports and PROG#, RESET# pins are brought on to this area. |  |  |  |  |

- (1) Gender changer required when ports are configured as slave ports by VNC2 firmware, to enable connection to a USB host port.

- (2) Those pins are shared between different areas and connectors on the board. You can use only one device at time connected to those pins.

Table 3.2 V2-Eval Board Interfaces.

4 Initial Board Set-up & Test

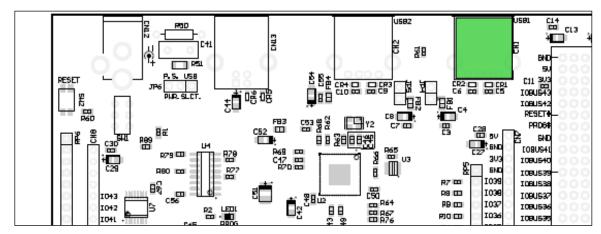

## 4.1 Installing VNC2 Daughterboard

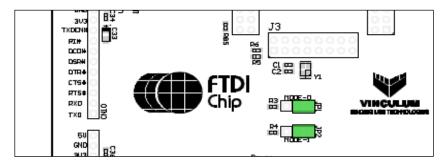

Prior to first powering the board, users must ensure that the daughterboard module hosting the VNC2 chip is correctly installed on to the main V2-Eval board. The V2-Eval board has 4 socket connectors, J1-J4, onto which the VNC2 daughterboard module is installed.

On the VNC2 daughterboard module, connector JN1 connects to corresponding socket J1, JN2 connects to socket J2, JN3 connects to socket J3 and JN4 connects to J4 on the V2-Eval board.

#### Warning!

Please check that the VNC2 daughterboard module is correctly installed onto the V2-Eval board prior to power-up. Incorrect installation can cause the VNC2 to not function.

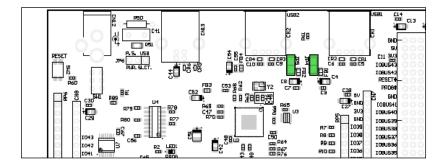

Figure 4.1 V2-EVAL Board with VNC2 Daughterboard Installed.

## 4.2 Testing the board.

Ensure that the Power Select jumper JP6 is in 'P.S.' position (pins 2 & 3 shorted), to enable the board to be powered from the external power adapter.

Connect the 5V DC/1A power supply included in V2-Eval Kit to the external input power adapter connector (CN12), connect USB A/B cable to USB B connector (CN13) on V2-Eval Board and to a free USB port on host PC. Switch SW1 to the ON position (towards board edge). LED2 – POWER should now be on.

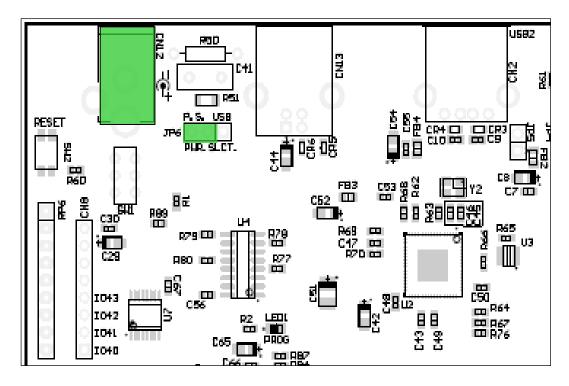

Figure 4.2 Power connector with Jumper JP6.

The PCB circuitry will draw power either directly from the board 5V supply or from a 3.3V regulator that is powered by this 5V supply. This includes the VNC2 daughterboard module that is installed on the board. Upon power up, the power LED (LED2) will illuminate.

## 5 Detailed Description of Board Components.

## **5.1** Power Select Jumper JP6.

Figure 5.1 Power Select Jumper Configuration for USB Power.

V2-Eval Board can draw its power either from the external 5V/1A DC Power Supply or from the USB interface when connected to a USB host via the B type connector (CN13). To enable USB power supply feature, switch the jumper JP6 to USB position, pins 1&2 shorted (pin 1 has a rectangle shaped pad on the bottom side of the board).

#### Warning!

Please remember that every device connected to the PC through USB port can draw NO MORE than 500mA from the USB host PC 5V power bus.

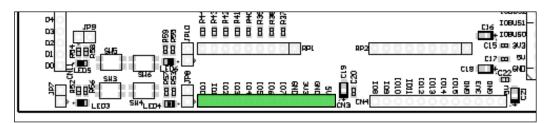

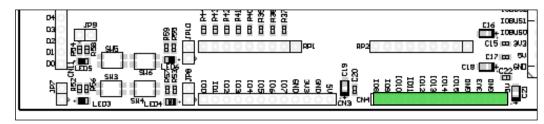

**5.2 GPIO BUS Connectors**

The V2-EVAL board features a set of 6 connectors providing access to GPIO capable pins on the VNC2 device. The GPIO pins are distributed across 6 connectors. The configuration of each connector is outlined in subsequent sections. Further each connector has a 5V and 3.3V power and GND pins.

## 5.2.1 **GPIO** [0:7] Connector CN3

Figure 5.2 GPIO[0:7] Connector CN3.

| Signal              | Connector pin | VCN2 Pin No |        |        | 10   |                       |

|---------------------|---------------|-------------|--------|--------|------|-----------------------|

| name                |               | 32-PIN      | 48-PIN | 64-PIN | type | Description           |

| GPIO0 (3)           | 1             | 11          | 11     | 11     | IO   | GPIO data bit 0       |

| GPIO1 (3)           | 2             | 12          | 12     | 12     | IO   | GPIO data bit 1       |

| GPIO2 (3)           | 3             | 14          | 13     | 13     | IO   | GPIO data bit 2       |

| GPIO3 (3)           | 4             | 15          | 14     | 14     | IO   | GPIO port, data bit 3 |

| GPIO4 (3)           | 5             | -           | -      | 15     | IO   | GPIO port, data bit 4 |

| GPIO5 (3)           | 6             | -           | -      | 16     | IO   | GPIO port, data bit 5 |

| GPIO6 (3)           | 7             | -           | -      | 17     | IO   | GPIO port, data bit 6 |

| GPIO7 (3)           | 8             | -           | -      | 18     | IO   | GPIO port, data bit 7 |

| GND                 | 9             | -           | -      | -      | -    | Ground pin            |

| 3.3V <sup>(4)</sup> | 10            | -           | -      | -      | -    | 3.3V power rail.      |

| GND                 | 11            | -           | -      | -      | -    | Ground pin            |

| 5V <sup>(5)</sup>   | 12            | -           | -      | -      | -    | 5V power rail.        |

- (3) All VNC2's IO pins can be driven from 3.3V LVTTL TTL logic levels.

The use of these pins for GPIO is set by the IOMUX on the VNC2 device. The pins are shared by other connectors on the board. Care should be taken to ensure that pins are not driven from other headers on the board.

- (4) This pin is connected to 3.3V regulator output. External device can draw no more than 100mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB bus.

- (5) This pin is connected to the board's 5V power rail. External device can draw no more than 250mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB bus.

Table 5.1 GPIO port connector CN3.

## 5.2.2 GPIO [8:15] Connector CN4

Figure 5.3 GPIO[8:15] Connector CN4.

|                     | Connector | Connector VCN2 Pin No |        |        | 10   |                        |

|---------------------|-----------|-----------------------|--------|--------|------|------------------------|

| Signal name         | pin       | 32-PIN                | 48-PIN | 64-PIN | type | Description            |

| GPIO8 (6)           | 1         | -                     | -      | 19     | IO   | GPIO port, data bit 8  |

| GPIO9 (6)           | 2         | -                     | -      | 20     | IO   | GPIO port, data bit 9  |

| GPIO10 (6)          | 3         | -                     | -      | 22     | IO   | GPIO port, data bit 10 |

| GPIO11 (6)          | 4         | -                     | -      | 23     | IO   | GPIO port, data bit11  |

| GPIO12 (6)          | 5         | -                     | -      | 24     | IO   | GPIO port, data bit 12 |

| GPIO13 (6)          | 6         | -                     | -      | 25     | IO   | GPIO port, data bit 13 |

| GPIO14 (6)          | 7         | -                     | -      | 26     | IO   | GPIO port, data bit 14 |

| GPIO15 (6)          | 8         | -                     | -      | 27     | IO   | GPIO port, data bit 15 |

| GND                 | 9         | -                     | -      | -      | -    | Ground pin             |

| 3.3V <sup>(7)</sup> | 10        | -                     | -      | -      | -    | 3.3V power rail.       |

| GND                 | 11        | -                     | -      | -      | -    | Ground pin             |

| 5V <sup>(8)</sup>   | 12        | -                     | -      | -      | -    | 5V power rail.         |

- (6) All VNC2's IO pins can be driven from 3.3V LVTTL TTL logic levels. The use of these pins for GPIO is set by the IOMUX on the VNC2 device. The pins are shared by other connectors on the board. Care should be taken to ensure that pins are not driven from other headers on the board.

- (7) This pin is connected to 3.3V regulator output. External device can draw no more than 100mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB bus

- (8) This pin is connected to the board's 5V power rail. External device can draw no more than 250mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB bus.

Table 5.2 GPIO[8:15] connector CN4.

## 5.2.3 GPIO [16:23] Connector CN5

Figure 5.4 GPIO[16:23] Connector CN5.

| a: .                  | Connector |                    | VCN2 Pin N         | o      | IO<br>type | Description            |

|-----------------------|-----------|--------------------|--------------------|--------|------------|------------------------|

| Signal name           | pin       | 32-PIN             | 48-PIN             | 64-PIN |            |                        |

| GPIO16 (9)            | 1         | -                  | -                  | 27     | IO         | GPIO port, data bit 16 |

| GPIO17 (9)            | 2         | =                  | 46                 | 28     | IO         | GPIO port, data bit 17 |

| GPIO18 (9)            | 3         | =                  | 45                 | 29     | IO         | GPIO port, data bit 18 |

| GPIO19 (9)            | 4         | -                  | 48                 | 31     | IO         | GPIO port, data bit19  |

| GPIO20 <sup>(9)</sup> | 5         | 23                 | 31                 | 32     | IO         | GPIO port, data bit 20 |

| GPIO21 <sup>(9)</sup> | 6         | 24 <sup>(10)</sup> | 32 <sup>(10)</sup> | 39     | IO         | GPIO port, data bit 21 |

| GPIO22 <sup>(9)</sup> | 7         | 25                 | 33                 | 40     | IO         | GPIO port, data bit 22 |

| GPIO23 <sup>(9)</sup> | 8         | 26 <sup>(10)</sup> | 34 (10)            | 41     | IO         | GPIO port, data bit 23 |

| GND                   | 9         | -                  | -                  | -      | -          | Ground pin             |

| 3.3V <sup>(11)</sup>  | 10        | -                  | -                  | -      | -          | 3.3V power rail.       |

| GND                   | 11        | =                  | -                  | -      | -          | Ground pin             |

| 5V <sup>(12)</sup>    | 12        | -                  | -                  | 1      | -          | 5V power rail.         |

- (9) All VNC2's IO pins can be driven from 3.3V LVTTL TTL logic levels.

The use of these pins for GPIO is set by the IOMUX on the VNC2 device. The pins are shared by other connectors on the board. Care should be taken to ensure that pins are not driven from other headers

- on the board.

(10) The following pins are only accessible on VNC2 when the onboard multiplexer select input is high. See section 6.4 for details.

- (11) This pin is connected to 3.3V regulator output. External device can draw no more than 100mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB bus.

- (12) This pin is connected to the board's 5V power rail. External device can draw no more than 250mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB bus.

Table 5.3 GPIO port connector CN5.

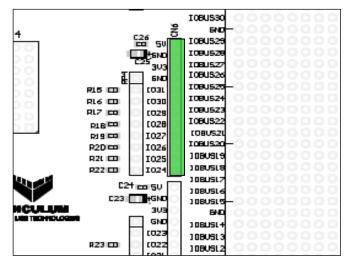

## 5.2.4 GPIO [24:31] Connector CN6

Figure 5.5 GPIO[24:31] Connector CN6.

|                      | Connecto | VCN2 Pin No |        |        | 10   |                        |

|----------------------|----------|-------------|--------|--------|------|------------------------|

| Signal name          | r pin    | 32-PIN      | 48-PIN | 64-PIN | type | Description            |

| GPIO24 (13)          | 1        | -           | 35     | 43     | IO   | GPIO port, data bit 24 |

| GPIO25 (13)          | 2        | -           | 36     | 44     | IO   | GPIO port, data bit 25 |

| GPIO26 (13)          | 3        | -           | 37     | 45     | IO   | GPIO port, data bit 26 |

| GPIO27 (13)          | 4        | -           | 38     | 46     | IO   | GPIO port, data bit 27 |

| GPIO28 (13)          | 5        | -           | 41     | 47     | IO   | GPIO port, data bit 28 |

| GPIO29 (13)          | 6        | -           | 42     | 48     | IO   | GPIO port, data bit 29 |

| GPIO30 (13)          | 7        | -           | 43     | 49     | IO   | GPIO port, data bit 30 |

| GPIO31 (13)          | 8        | -           | 44     | 50     | IO   | GPIO port, data bit 31 |

| GND                  | 9        | -           | -      | -      | -    | Ground pin             |

| 3.3V <sup>(14)</sup> | 10       |             | -      | -      | -    | 3.3V power rail.       |

| GND                  | 11       |             | -      | -      | -    | Ground pin             |

| 5V <sup>(15)</sup>   | 12       |             | =      | -      | -    | 5V power rail.         |

- (13) All VNC2's IO pins can be driven from 3.3V LVTTL TTL logic levels.

The use of these pins for GPIO is set by the IOMUX on the VNC2 device. The pins are shared by other connectors on the board. Care should be taken to ensure that pins are not driven from other headers on the board.

- (14) This pin is connected to 3.3V regulator output. External device can draw no more than 100mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB bus.

- (15) This pin is connected to the board's 5V power rail. External device can draw no more than 250mA when board is powered from power supply and no more than 50mA when the board is powered from USB bus.

Table 5.4 GPIO port connector CN6.

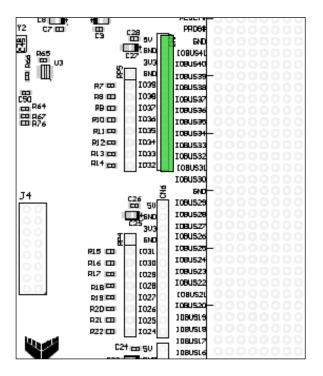

## 5.2.5 GPIO [32:39] Connector CN7

Figure 5.6 GPIO[32:39] Connector CN7.

|                      | Connector |        | VCN2 Pin No | D      |         |                        |

|----------------------|-----------|--------|-------------|--------|---------|------------------------|

| Signal name          | pin       | 32-PIN | 48-PIN      | 64-PIN | IO type | Description            |

| GPIO32 (16)          | 1         | 29     | 15          | 51     | IO      | GPIO port, data bit 32 |

| GPIO33 (16)          | 2         | 30     | 16          | 52     | IO      | GPIO port, data bit 33 |

| GPIO34 (16)          | 3         | 31     | 18          | 55     | IO      | GPIO port, data bit 34 |

| GPIO35 (16)          | 4         | 32     | 19          | 56     | IO      | GPIO port, data bit 35 |

| GPIO36 (16)          | 5         | -      | -           | 57     | IO      | GPIO port, data bit 36 |

| GPIO37 (16)          | 6         | -      | -           | 58     | IO      | GPIO port, data bit 37 |

| GPIO38 (16)          | 7         | -      | -           | 59     | IO      | GPIO port, data bit 38 |

| GPIO39 (16)          | 8         | -      | -           | 60     | IO      | GPIO port, data bit 39 |

| GND                  | 9         | -      | -           | -      | -       | Ground pin             |

| 3.3V <sup>(17)</sup> | 10        | -      | -           | -      | -       | 3.3V power rail.       |

| GND                  | 11        | -      | -           | -      | -       | Ground pin             |

| 5V <sup>(18)</sup>   | 12        | -      | -           | -      | -       | 5V power rail.         |

- (16) All VNC2's IO pins can be driven from 3.3V LVTTL TTL logic levels.

The use of these pins for GPIO is set by the IOMUX on the VNC2 device. The pins are shared by other connectors on the board. Care should be taken to ensure that pins are not driven from other headers on the board.

- (17) This pin is connected to 3.3V regulator output. External device can draw no more than 100mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB

- (18) This pin is connected to the board's 5V power rail. External device can draw no more than 250mA when board is powered from power supply and no more than 50mA when the board is powered from USB power bus.

Table 5.5 GPIO port connector CN7.

## 5.2.6 GPIO [40:43] Connector CN8

Figure 5.7 GPIO[32:39] Connector CN8.

| Signal               | Connector |        | VCN2 Pin No |        | 10   |                        |  |

|----------------------|-----------|--------|-------------|--------|------|------------------------|--|

| name                 | pin       | 32-PIN | 48-PIN      | 64-PIN | type | Description            |  |

| GPIO40 (19)          | 1         | -      | 20          | 61     | IO   | GPIO port, data bit 40 |  |

| GPIO41 (19)          | 2         | -      | 21          | 62     | IO   | GPIO port, data bit 41 |  |

| GPIO42 (19)          | 3         | -      | 22          | 63     | IO   | GPIO port, data bit 42 |  |

| GPIO43 (19)          | 4         | -      | 23          | 64     | IO   | GPIO port, data bit 43 |  |

| GND                  | 5         | -      | -           | -      | -    | Ground pin             |  |

| 3.3V <sup>(20)</sup> | 6         | -      | -           | -      | -    | 3.3V power rail.       |  |

| GND                  | 7         | -      |             | -      | -    | Ground pin             |  |

| 5V <sup>(21)</sup>   | 8         | 1      | -           | -      | -    | 5V power rail.         |  |

- (19) All VNC2's IO pins can be driven from 3.3V LVTTL TTL logic levels.

The use of these pins for GPIO is set by the IOMUX on the VNC2 device. The pins are shared by other connectors on the board. Care should be taken to ensure that pins are not driven from other headers on the board.

- (20) This pin is connected to 3.3V regulator output. External device can draw no more than 100mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB hus

- (21) This pin is connected to the board's 5V power rail. External device can draw no more than 250mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB bus.

Table 5.6 GPIO port connector CN8.

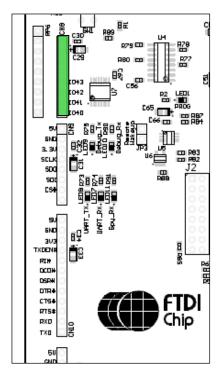

## 5.3 SPI Connector C9

**Table 5.7** details connector pinout for the SPI connector C9. A full description of each signal is available in the <u>VNC2</u> data sheet.

Figure 5.8 SPI Connector CN9.

| Signal name          | Connector VCN2 Pin No |        | Bassishian. |         |                                                       |

|----------------------|-----------------------|--------|-------------|---------|-------------------------------------------------------|

| Signal name          | pin                   | 48-PIN | 64-PIN      | IO type | Description                                           |

| 5V <sup>(22)</sup>   | 1                     | -      | -           | -       | 5V power rail.                                        |

| GND                  | 2                     | -      | -           | -       | Ground pin                                            |

| 3.3V <sup>(23)</sup> | 3                     | -      | -           | -       | 3.3V power rail.                                      |

| SCLK (24)            | 4                     | 20     | 61          | Input   | SPI CLK Input                                         |

| SDO <sup>(24)</sup>  | 5                     | 21     | 62          | Output  | SPI Master out slave in                               |

| SDI <sup>(24)</sup>  | 6                     | 22     | 63          | Input   | SDI Master in slave out                               |

| CS# <sup>(24)</sup>  | 7                     | 23     | 64          | Output  | Active low slave chip select 0 from master to slave 0 |

| GND                  | 8                     | -      | -           | -       | Ground pin                                            |

- (22) This pin is connected to the board's 5V power rail. External device can draw no more than 250mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB bus.

- (23) This pin is connected to 3.3V regulator output. External device can draw no more than 100mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB bus.

- (24) All VNC2's IO pins can be driven from 3.3V LVTTL TTL logic levels..

The use of these pins for GPIO is set by the IOMUX on the VNC2 device. The pins are shared by other connectors on the board. Care should be taken to ensure that pins are not driven from other headers on the board.

Table 5.7 SPI Port Connector CN9.

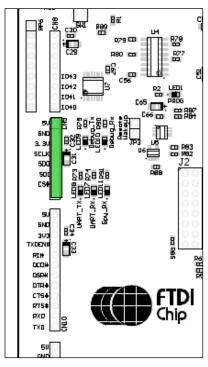

#### 5.4 UART Interface Connector C10

**Table 5.8** details connector pinout for the UART connector C10. A full description of each signal is available in the <u>VNC2</u> data sheet.

Figure 5.9 UART Connector CN10.

| Signal                 | Connector | V                  | CN2 Pin N          | 0      |         |                                                    |

|------------------------|-----------|--------------------|--------------------|--------|---------|----------------------------------------------------|

| name                   | pin       | 32-PIN             | 48-PIN             | 64-PIN | IO type | Description                                        |

| TXD (25)               | 1         | 23                 | 31                 | 39     | Output  | Transmit data                                      |

| RXD (25)               | 2         | 24 <sup>(26)</sup> | 32 <sup>(26)</sup> | 40     | Input   | Receive data                                       |

| RTS# (25)              | 3         | 25                 | 33                 | 41     | Output  | Request to Send Control Output / Handshake signal. |

| CTS# (25)              | 4         | 26 <sup>(26)</sup> | 34 <sup>(26)</sup> | 42     | Input   | Clear to Send Input / Handshake signal.            |

| DTR# (25)              | 5         |                    | 35                 | 43     | Output  | Data Terminal Ready Output / Handshake signal.     |

| DSR# (25)              | 6         |                    | 36                 | 44     | Input   | Data Set Ready Input / Handshake signal.           |

| DCD# (25)              | 7         |                    | 37                 | 45     | Input   | Data Carrier Detect Control Input                  |

| RI# (25)               | 8         |                    | 38                 | 46     | Input   | Ring Indicator Control Input                       |

| TXDEN# <sup>(25)</sup> | 9         |                    | -                  | 47     | Output  | Transmit Data Enable                               |

| 3.3V <sup>(27)</sup>   | 10        |                    | -                  | -      | -       | 3.3V power rail.                                   |

| GND                    | 11        |                    | -                  | -      | -       | Ground pin                                         |

| 5V <sup>(28)</sup>     | 12        |                    | -                  | -      | -       | 5V power rail.                                     |

- (25) All VNC2's IO pins can be driven from 3.3V LVTTL TTL logic levels..

The use of these pins for GPIO is set by the IOMUX on the VNC2 device. The pins are shared by other connectors on the board. Care should be taken to ensure that pins are not driven from other headers on the board.

- (26) The following pins are only accessible on VNC2 when the onboard multiplexer select input is high. See section 6.4 for details.

- (27) This pin is connected to 3.3V regulator output. External device can draw no more than 100mA when board is powered from power supply and no more than 50mA when the board is powered from USB power bus.

- (28) This pin is connected to the board's 5V power rail. External device can draw no more than 250mA when board is powered from power supply and no more than 50mA when the board is powered from USB power bus.

**Table 5.8 UART Interface Connector CN10.**

#### 5.5 FIFO Interface Connector CN11

**Table 5.9** details connector pinout for the FIFO connector C11. A full description of each signal is available in the <u>VNC2</u> data sheet.

Figure 5.10 FIFO Connector CN11.

| Signal               |               | V      | CN2 Pin N | 0      |         |                                               |

|----------------------|---------------|--------|-----------|--------|---------|-----------------------------------------------|

| name                 | Connector pin | 32-PIN | 48-PIN    | 64-PIN | IO type | Description                                   |

| D0 <sup>(29)</sup>   | 1             | -      | -         | 15     | IO      | FIFO data bit 0, bidirectional                |

| D1 <sup>(29)</sup>   | 2             | -      | -         | 16     | IO      | FIFO data bit 1, bidirectional                |

| D2 <sup>(29)</sup>   | 3             | -      | -         | 17     | IO      | FIFO data bit 2, bidirectional                |

| D3 <sup>(29)</sup>   | 4             | -      | -         | 18     | IO      | FIFO data bit 3, bidirectional                |

| D4 <sup>(29)</sup>   | 5             | -      | -         | 19     | IO      | FIFO data bit 4, bidirectional                |

| D5 <sup>(29)</sup>   | 6             | -      | -         | 20     | IO      | FIFO data bit 5, bidirectional                |

| D6 <sup>(29)</sup>   | 7             | -      | -         | 22     | IO      | FIFO data bit 6, bidirectional                |

| D7 <sup>(29)</sup>   | 8             | -      | -         | 23     | IO      | FIFO data bit 7, bidirectional                |

| RXF#                 | 9             | -      | -         | 24     | Output  | FIFO receive full output                      |

| TXE#                 | 10            | -      | -         | 25     | Output  | FIFO transmitter buffer empty output          |

| RD#                  | 11            | -      | -         | 26     | Input   | FIFO read enable input                        |

| WR#                  | 12            | -      | -         | 27     | Input   | FIFO write enable input                       |

| OE#                  | 13            | -      | -         | 28     | Input   | FIFO output enable –<br>synchronous FIFO only |

| 3.3V <sup>(30)</sup> | 14            | -      | -         | -      | -       | 3.3V power rail.                              |

| GND                  | 15            | -      | -         | -      | -       | Ground pin                                    |

| 5V <sup>(31)</sup>   | 16            | -      | -         | -      | -       | 5V power rail.                                |

- (29) All VNC2's IO pins can be driven from 3.3V LVTTL TTL logic levels.

- The use of these pins for GPIO is set by the IOMUX on the VNC2 device. The pins are shared by other connectors on the board. Care should be taken to ensure that pins are not driven from other headers on the board.

- (30) This pin is connected to 3.3V regulator output. External device can draw no more than 100mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB bus.

- (31) This pin is connected to the board's 5V power rail. External device can draw no more than 250mA when board is powered from an external power supply and no more than 50mA when the board is powered from USB bus.

Table 5.9 FIFO Interface Connector CN11.

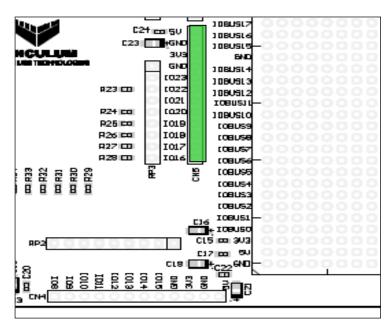

## 5.6 Prototyping area

Figure 5.11 Prototyping area P1.

A prototype area consisting of an array of 1100, 0.1-inch pitch holes is provided. The area can be used to create custom circuitry and connect components to the V2-EVAL board. The prototyping area includes connections to the 5V, 3.3 V planes and ground planes. The silk-screen text on the board indicates which holes are connected to which signals. Only the first column is connected to VNC2 IO ports, power and ground planes. All the other holes are not connected to anything on the board.

Signal pins are shared between other IO connectors on the board. For more information refer to the V2-Eval Board schematics.

| Connector     | Silk Screen                                     | \                        | /CN2 Pin No              | 0        | ю    |                                                            |

|---------------|-------------------------------------------------|--------------------------|--------------------------|----------|------|------------------------------------------------------------|

| pin<br>number | Signal Label                                    | 32-PIN                   | 48-PIN                   | 64-PIN   | type | Description                                                |

| 1             | GND                                             | -                        | -                        | -        | -    | Ground pin                                                 |

| 2             | 5V <sup>(32)</sup>                              | -                        | -                        | -        | -    | 5V power rail.<br>Can be used to power external devices    |

| 3             | 3.3V <sup>(33)</sup>                            | -                        | -                        | -        | -    | 3.3V power rail. Can be used to power external devices     |

| 4             | IOBUS0 <sup>(34)</sup>                          | 11                       | 11                       | 11       | IO   | IOBUS port Data Bit 0. Debug port – default configuration. |

| 5             | IOBUS1 <sup>(34)</sup>                          | 12                       | 12                       | 12       | IO   | IOBUS port Data Bit 1.                                     |

| 6             | IOBUS2 <sup>(34)</sup>                          | 14                       | 13                       | 13       | IO   | IOBUS port Data Bit 2.                                     |

| 7             | IOBUS3 <sup>(34)</sup>                          | 15                       | 14                       | 14       | IO   | IOBUS port Data Bit 3.                                     |

| 8             | IOBUS4 <sup>(34)</sup>                          | 1                        | ı                        | 15       | IO   | IOBUS port Data Bit 4.                                     |

| 9             | IOBUS5 <sup>(34)</sup>                          | -                        | -                        | 16       | IO   | IOBUS port Data Bit 5.                                     |

| 10            | IOBUS6 <sup>(34)</sup>                          | -                        | -                        | 17       | IO   | IOBUS port Data Bit 6.                                     |

| 11            | IOBUS7 <sup>(34)</sup>                          | -                        | -                        | 18       | IO   | IOBUS port Data Bit 7.                                     |

| 12            | IOBUS8 <sup>(34)</sup>                          | -                        | -                        | 19       | IO   | IOBUS port Data Bit 8.                                     |

| 13            | IOBUS9 <sup>(34)</sup>                          | -                        | -                        | 20       | IO   | IOBUS port Data Bit 9.                                     |

| 14            | IOBUS10 <sup>(34)</sup>                         | -                        | -                        | 22       | IO   | IOBUS port Data Bit 10.                                    |

| 15            | IOBUS11 <sup>(34)</sup>                         | =                        | =                        | 23       | IO   | IOBUS port Data Bit 11.                                    |

| 16            | IOBUS12 <sup>(34)</sup>                         | -                        | -                        | 24       | IO   | IOBUS port Data Bit 12.                                    |

| 17            | IOBUS13 <sup>(34)</sup>                         | -                        | _                        | 25       | IO   |                                                            |

| 18            | IOBUS14 <sup>(34)</sup>                         | _                        | _                        | 26       | IO   | IOBUS port Data Bit 13.                                    |

| 19            | GND                                             | -                        | _                        | -        | -    | IOBUS port Data Bit 14.  Ground pin                        |

| 20            | IOBUS15 <sup>(34)</sup>                         | -                        |                          | 27       | IO   | IOBUS port Data Bit 15.                                    |

| 21            | IOBUS16 <sup>(34)</sup>                         | _                        | _                        | 27       | IO   |                                                            |

| 22            | IOBUS17 <sup>(34)</sup>                         | -                        | 46                       | 28       | IO   | IOBUS port Data Bit 16.  IOBUS port Data Bit 17.           |

| 23            | IOBUS18 <sup>(34)</sup>                         | -                        | 45                       | 29       | IO   |                                                            |

| 24            | IOBUS19 <sup>(34)</sup>                         | -                        | 48                       | 31       | IO   | IOBUS port Data Bit 18.                                    |

| 25            | IOBUS20 <sup>(34)</sup>                         |                          |                          |          |      | IOBUS port Data Bit 19.                                    |

|               |                                                 | 23<br>24 <sup>(35)</sup> | 31<br>32 <sup>(35)</sup> | 32       | IO   | IOBUS port Data Bit 20.                                    |

| 26            | IOBUS21 <sup>(34)</sup> IOBUS22 <sup>(34)</sup> |                          |                          | 39       | IO   | IOBUS port Data Bit 21.                                    |

| 27            | IOBUS22 <sup>(34)</sup>                         | 25<br>26 <sup>(35)</sup> | 33<br>34 <sup>(35)</sup> | 40       | IO   | IOBUS port Data Bit 22.                                    |

| 28<br>29      | IOBUS23(34)                                     | -                        | 35                       | 41       | IO   | IOBUS port Data Bit 23.  IOBUS port Data Bit 24.           |

| 30            | IOBUS25 <sup>(34)</sup>                         | -                        | 36                       | 43       | IO   | IOBUS port Data Bit 25.                                    |

| 31            | IOBUS26 <sup>(34)</sup>                         | -                        | 37                       | 45       | IO   | IOBUS port Data Bit 26.                                    |

|               | IOBUS27 <sup>(34)</sup>                         |                          |                          |          |      |                                                            |

| 32            | IOBUS27 <sup>(34)</sup>                         | -                        | 38<br>41                 | 46<br>47 | IO   | IOBUS port Data Bit 27.  IOBUS port Data Bit 28.           |

| 34            | IOBUS29 <sup>(34)</sup>                         | -                        | 41                       | 48       | IO   | IOBUS port Data Bit 29.                                    |

| 35            | GND                                             | -                        | -                        | -        | 10   | 10003 port Data Dit 25.                                    |

| 36            | IOBUS30 <sup>(34)</sup>                         | -                        | 43                       | 49       | IO   | IOBUS port Data Bit 30.                                    |

| 37            | IOBUS31 <sup>(34)</sup>                         | -                        | 44                       | 50       | IO   | IOBUS port Data Bit 30.                                    |

| 38            | IOBUS32 <sup>(34)</sup>                         | 29                       | 15                       | 51       | IO   | IOBUS port Data Bit 32.                                    |

| 39            | IOBUS33 <sup>(34)</sup>                         | 30                       | 16                       |          | IO   | IOBUS port Data Bit 32.                                    |

| 40            | IOBUS34 <sup>(34)</sup>                         | 31                       | 18                       | 52       | IO   | ·                                                          |

|               | IOBUS35 <sup>(34)</sup>                         |                          |                          | 55       |      | IOBUS port Data Bit 34.                                    |

| 41            | 1000333                                         | 32                       | 19                       | 56       | IO   | IOBUS port Data Bit 35.                                    |

# Document Reference No.: FT\_000247 V2-EVAL Vinculum II Evaluation Board Datasheet Version 1.0

Clearance No.: FTDI#148

| 42 | IOBUS36 <sup>(34)</sup> | -  | -  | 57 | IO | IOBUS port Data Bit 36.                                 |

|----|-------------------------|----|----|----|----|---------------------------------------------------------|

| 43 | IOBUS37 <sup>(34)</sup> | -  | -  | 58 | IO | IOBUS port Data Bit 37.                                 |

| 44 | IOBUS38 <sup>(34)</sup> | =  | -  | 59 | IO | IOBUS port Data Bit 38.                                 |

| 45 | IOBUS39 <sup>(34)</sup> | ı  | ı  | 60 | IO | IOBUS port Data Bit 39.                                 |

| 46 | IOBUS40 <sup>(34)</sup> | =  | 20 | 61 | IO | IOBUS port Data Bit 40.                                 |

| 47 | IOBUS41 <sup>(34)</sup> | -  | 21 | 62 | IO | IOBUS port Data Bit 41.                                 |

| 48 | GND                     | -  | -  | -  | -  | Ground pin                                              |

| 49 | PROG#                   | 9  | 10 | 10 | I  | VNC2 PROG# pin                                          |

| 50 | RESET#                  | 10 | 9  | 9  | I  | VNC2 RESET# pin                                         |

| 51 | IOBUS42 <sup>(35)</sup> | ı  | 22 | 63 | -  | IOBUS port Data Bit 42.                                 |

| 52 | IOBUS43 <sup>(35)</sup> | -  | 23 | 64 | -  | IOBUS port Data Bit 43.                                 |

| 53 | 3.3V <sup>(33)</sup>    | -  | -  | -  | -  | 3.3V power rail. Can be used to power external devices  |

| 54 | 5V <sup>(32)</sup>      | -  | -  | -  | -  | 5V power rail.<br>Can be used to power external devices |

| 55 | GND                     | -  | -  | -  | -  | Ground pin                                              |

- (32) This pin is connected to the board's 5V power rail. External device can draw no more than 250mA when board is powered from power supply and no more than 50mA when the board is powered from USB power bus.

- (33) This pin is connected to 3.3V regulator output.

- (34) The IOBUS signal labels on the PCB silk screen do directly relate to the IOBUS signal names for the VNC2 device on the daughterboard. See VNC2 pin number for signal mapping on the device.

- (35) The following pins are only accessible when the onboard multiplexer select input is high. See section 6.4 for details.

Table 5.10 Prototyping Area Pinout.

## 5.7 USB1 interface CN1

Figure 5.12 USB1 Interface CN1.

VNC2 USB1 transceiver pins are brought on this connector. Depending on the firmware version this port can be configured as host or slave port.

|                    | Connector     | Connector        |            | VCN2 pin number |            |                                                      |                                        |  |

|--------------------|---------------|------------------|------------|-----------------|------------|------------------------------------------------------|----------------------------------------|--|

| Signal<br>name     | pin<br>number | VCN2 pin<br>name | 32-<br>PIN | 48-<br>PIN      | 64-<br>PIN | IO<br>type                                           | Description                            |  |

| 5V <sup>(36)</sup> | 1             | -                | -          |                 | ı          | 5V power rail. Can be used to power external devices |                                        |  |

| USB1-DM            | 2             | USB1 DM          | 17         | 25              | 33         | IO                                                   | USB1 transceiver, data line Minus      |  |

| USB1-DP            | 3             | USB1 DP          | 18         | 26              | 34         | IO                                                   | USB1 transceiver, data line Plus       |  |

| GND                | 4             | -                | -          |                 | -          | Ground pin                                           |                                        |  |

| Shield             | 5, 6          | -                | -          | -               |            | -                                                    | Connector shield. Connected to ground. |  |

Table 5.11 USB1 Host/Slave Connector CN1.

<sup>(36)</sup> This pin is connected to the board's 5V power rail. External device can draw no more than 250mA when board is powered from power supply and no more than 50mA when the board is powered from USB power bus.

5.8 USB2 interface CN2.

Figure 5.13 USB2 Interface CN2.

VNC2 USB2 transceiver pins are brought on this connector. Depending on the version of the firmware running on the device, the port can be configured as host or slave port.

|                    | Connector     |                  | VCN2 pin number |            |            |                                                         |                                        |  |

|--------------------|---------------|------------------|-----------------|------------|------------|---------------------------------------------------------|----------------------------------------|--|

| Signal<br>name     | pin<br>number | VCN2 pin<br>name | 32-<br>PIN      | 48-<br>PIN | 64-<br>PIN | IO<br>type                                              | Description                            |  |

| 5V <sup>(37)</sup> | 1             | -                | -               |            | -          | 5V power rail.<br>Can be used to power external devices |                                        |  |

| USB2-DM            | 2             | USB2 DM          | 20              | 28         | 36         | IO                                                      | USB2 transceiver, data line Minus      |  |

| USB2-DP            | 3             | USB2 DP          | 21              | 29         | 37         | IO                                                      | USB2 transceiver, data line Plus       |  |

| GND                | 4             | =                | -               |            | -          | Ground pin                                              |                                        |  |

| Shield             | 5, 6          | =                |                 | -          | •          | -                                                       | Connector shield. Connected to ground. |  |

Table 5.12 USB2 Host / Slave connector CN2.

<sup>(37)</sup> This pin is connected to the board's 5V power rail. External device can draw no more than 250mA when board is powered from power supply and no more than 50mA when the board is powered from USB power bus.

## 5.9 GPIO Jumpers JP1, JP2

Figure 5.14 GPIO Jumper pins, JP1, JP2.

JP1 and JP2 jumpers are available for use as jumper select inputs to the VNC2.

| Jumpan | VNC2 Pin Numb | er / Signal Name | VNC2 Signal Name              |  |  |  |

|--------|---------------|------------------|-------------------------------|--|--|--|

| Jumper | 48-PIN        | 64-PIN           | Comments                      |  |  |  |

| JP1    | 46 / IOBUS25  | 29 / IOBUS18     | Signal also connected to LED5 |  |  |  |

| JP2    | 47 / IOBUS26  | -                |                               |  |  |  |

#### Notes:

(38) The use of these pins for GPIO is set by the IOMUX on the VNC2 device. The pins are shared by other connectors on the board. Care should be taken to ensure that pins are not driven from other headers on the board.

Table 5.13 GPIO jumpers JP1, JP2.

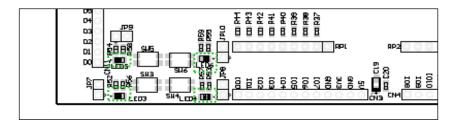

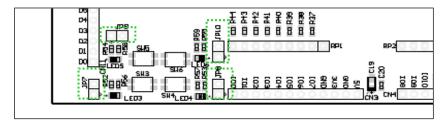

### 5.10 User LEDs. LED3 - LED6.

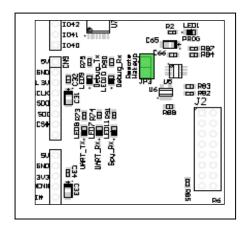

Figure 5.15 User LEDs.

Four LEDs is provided on board. The LEDs enabled or disabled via jumpers JP7 – JP10. The LEDs are controlled by the IOBUS signals on the VNC2.

Note - LED5 is also connected to jumper JP1 on the board. Care should be taken to ensure that LED is not being driven by JP1 when controlling the LED from the VNC2.

|        | VCN2 pin number |                                |  |  |  |  |  |  |

|--------|-----------------|--------------------------------|--|--|--|--|--|--|

| 32-PIN | 48-PIN          | 64-PIN                         |  |  |  |  |  |  |

| 12     | 12              | 12                             |  |  |  |  |  |  |

| 14     | 13              | 13                             |  |  |  |  |  |  |

| -      | 46              | 29                             |  |  |  |  |  |  |

| -      | 45              | 31                             |  |  |  |  |  |  |

|        | 12<br>14<br>-   | 32-PIN 48-PIN 12 12 14 13 - 46 |  |  |  |  |  |  |

Notes:

Table 5.14 User LEDs connections.

## 5.11 LED enable/disable jumpers JP10 - JP14.

Figure 5.16 LED Enable/Disable jumpers.

Every user-defined LED have an enable/disable jumper. When jumper is closed LED will be illuminate when driven low by one of the VNC2 pins. When jumper is opened LED is disconnected from the VCN2 pin.

| Designator | LED affected |

|------------|--------------|

| JP7        | LED3         |

| JP8        | LED4         |

| JP9        | LED5         |

| JP10       | LED6         |

Table 5.15 LED Enable/Disable Jumpers.

<sup>(39)</sup> LED5 is also connected to jumper JP1 on the board. Care should be taken to ensure that LED is not being driven by JP1 when controlling the LED from the VNC2.

## 5.12 User push button switches

Figure 5.17 User Push Button Switches.

Push button switches connected straight to VNC2 pins. When the switch is pressed down, a logic LOW appears on the corresponding VNC2 pin.

| Designator          | VNC2 Pin Number |        |        |  |  |  |  |  |  |

|---------------------|-----------------|--------|--------|--|--|--|--|--|--|

|                     | 32-PIN          | 48-PIN | 64-PIN |  |  |  |  |  |  |

| SW3 <sup>(40)</sup> | 15              | 14     | 14     |  |  |  |  |  |  |

| SW4 <sup>(40)</sup> | -               | 48     | 32     |  |  |  |  |  |  |

| SW5 <sup>(40)</sup> | -               | 42     | 48     |  |  |  |  |  |  |

| SW6 <sup>(40)</sup> | -               | 43     | 49     |  |  |  |  |  |  |

Notes:

Table 5.16 User Switches

## 5.13 Host USB power jumpers JP4, JP5.

Figure 5.18 USB Power Enable Jumpers JP4 and JP5.

When either USB1 and/or USB2 ports are used as a host ports, the jumpers JP4 and/or JP5 accordingly should be closed to allow peripheral devices to draw power from board's +5V power rail.

#### Warning!

When using USB1 and USB2 ports as a USB slave ports, remove the shunts from jumpers JP4 and JP5. Failure to do so could cause damage to the USB host or to the V2-EVAL board.

<sup>(40)</sup> The IOBUS pins are shared by other connectors on the board. Care should be taken to ensure that operation of the switches does not interfere with pins used by other headers on the board.

5.14 Remote Wakeup jumper JP3.

Figure 5.19 Remote Wakeup Jumper.

The remote wakeup jumper enables any firmware running on the VNC2 to support Suspend Monitor (SUM) mode, allowing the device to reduce power consumption when idle. The VNC2 device can be configured to wakeup when any data arrives on the receive data (RXD) pin, by connecting the RXD pin to ring indicator (RI#) input via jumper JP3. When RI# pin is driven low, VNC2 will resume from the SUM mode immediately. The remote wakeup feature is only available when using the UART interface on the VNC2. The feature can be enabled when a jumper is present on jumper JP3.

## 5.15 Reset Push-button Switch

Figure 5.20 Reset Switch

A 'RESET' push button switch is provided on switch SW2, to enable manual resetting of the VNC2 device.

## 5.16 'PROG' LED

Figure 5.21 'PROG' LED

LED1 (red) is provided to indicate when VNC2 device is in Flash programming mode.

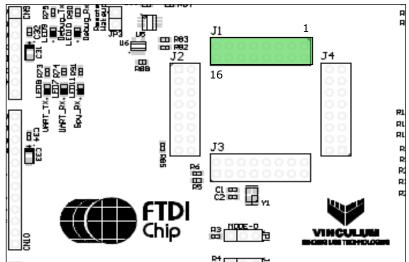

## 5.17 VNC2 Daughterboard Connector – J1

Figure 5.22 VNC2 Daughterboard Connector J1.

| Schematic                   | Connector | VCN2 Pin No |        |        | 10   |                                                        |

|-----------------------------|-----------|-------------|--------|--------|------|--------------------------------------------------------|

| Signal Name <sup>(41)</sup> |           | 32-PIN      | 48-PIN | 64-PIN | type | Description                                            |

| 3.3V                        | 1         | -           | -      | -      | -    | 3.3V power rail.                                       |

| 3.3V                        | 2         | -           | -      | -      | -    | 3.3V power rail.                                       |

| GND                         | 3         | -           | -      | -      | -    | Ground pin.                                            |

| USB1DP                      | 4         | 17          | 25     | 33     | IO   | USB1 transceiver, data line positive connected to CN1. |

| USB1DM                      | 5         | 18          | 26     | 34     | IO   | USB1 transceiver, data line minus connected to CN1.    |

| SPI_S0_CLK                  | 6         | 29          | 15     | 51     | IO   | Connected to P1 pin 38 / CN7 pin 1.                    |

| SPI_S0_MOSI                 | 7         | 30          | 16     | 52     | IO   | Connected to P1 pin 39 / CN7 pin 2.                    |

| SPI_SO_MISO                 | 8         | 31          | 18     | 55     | IO   | Connected to P1 pin 40 / CN7 pin 3.                    |

| SPI_S0_CS#                  | 9         | 32          | 19     | 56     | IO   | Connected to P1 pin 40 / CN7 pin 4.                    |

| USB2DP                      | 10        | 20          | 28     | 36     | IO   | USB2 transceiver, data line positive connected to CN2. |

| USB2DM                      | 11        | 21          | 29     | 37     | IO   | USB2 transceiver, data line minus connected to CN2.    |

| V_TXD                       | 12        | 23          | 31     | 39     | IO   | Connected to P1 pin 25 / CN10 pin 1 / CN5 pin 5.       |

| V_RXD                       | 13        | 24          | 32     | 40     | IO   | Connected to P1 pin 26 / CN10 pin 2 / CN5 pin 6.       |

| V_RTS#                      | 14        | 25          | 33     | 41     | IO   | Connected to P1 pin 27 / CN10 pin 3 / CN5 pin 7.       |

| V_CTS#                      | 15        | 26          | 34     | 42     | IO   | Connected to P1 pin 28 / CN10 pin 4 / CN5 pin 8.       |

| V_DTR#                      | 16        | -           | 35     | 43     | IO   | Connected to P1 pin 29 / CN10 pin 5 / CN6 pin 1.       |

Table 5.17 Connector J1 Pinout.

<sup>(41)</sup> The signal names relate to the labels used on pages 1 & 2 of the V2-EVAL base board schematic. Unless otherwise stated, the function of the IO signals is be set by the user application running on the VNC2.

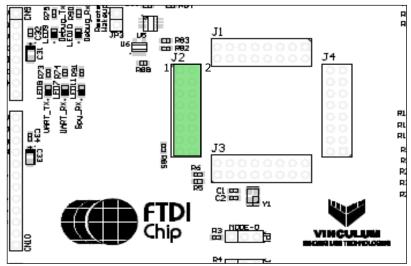

## 5.18 VNC2 Daughterboard Connector – J2

Figure 5.23 VNC2 Daughterboard Connector J2.

| Schematic                   | Connector | VCN2 Pin No |        |        | 10   |                                                  |

|-----------------------------|-----------|-------------|--------|--------|------|--------------------------------------------------|

| Signal Name <sup>(42)</sup> | Pin       | 32-PIN      | 48-PIN | 64-PIN | type | Description                                      |

| V_DSR#                      | 1         | =           | 36     | 44     | IO   | Connected to P1 pin 30 / CN10 pin 6 / CN6 pin 2. |

| V_DCD#                      | 2         | -           | 37     | 45     | IO   | Connected to P1 pin 31 / CN10 pin 7 / CN6 pin 3. |

| V_RI#                       | 3         | -           | 38     | 46     | IO   | Connected to P1 pin 32 / CN10 pin 8 / CN6 pin 4. |

| V_TXDEN                     | 4         | -           | 41     | 47     | IO   | Connected to P1 pin 33 / CN10 pin 9 / CN6 pin 5. |

| 3.3V                        | 5         | -           | -      | -      | -    | 3.3V power rail.                                 |

| 3.3V                        | 6         | -           | -      | -      | -    | 3.3V power rail.                                 |

| GPIO7                       | 7         | -           | 42     | 48     | IO   | Connected to P1 pin 34 / CN6 pin 6.              |

| GPIO8                       | 8         | -           | 43     | 49     | IO   | Connected to P1 pin 36 / CN6 pin 7.              |

| GPIO9                       | 9         | -           | 44     | 50     | IO   | Connected to P1 pin 37 / CN6 pin 8.              |

| SPI_S1_CLK                  | 10        | -           | -      | 57     | IO   | Connected to P1 pin 42 / CN7 pin 5.              |

| SPI_S1_MOSI                 | 11        | -           | -      | 58     | IO   | Connected to P1 pin 43 / CN7 pin 6.              |

| SPI_S1_MISO                 | 12        | -           | -      | 59     | IO   | Connected to P1 pin 44 / CN7 pin 7.              |

| GND                         | 13        | -           | -      | -      | -    | Ground pin.                                      |

| SPI_S1_CS#                  | 14        | -           | -      | 60     | IO   | Connected to P1 pin 45 / CN7 pin 8.              |

| DEBUG_IF                    | 15        | 11          | 11     | 11     | IO   | Debug pin. Connected to P1 pin 4 / CN3 pin 1.    |

| GND                         | 16        | -           | -      | -      | -    | Ground pin.                                      |

Table 5.18 Connector J2 Pinout.

<sup>(42)</sup> The signal names relate to the labels used on pages 1 & 2 of the V2-EVAL base board schematic. Unless otherwise stated, the function of the IO signals is set by the user application running on the VNC2.

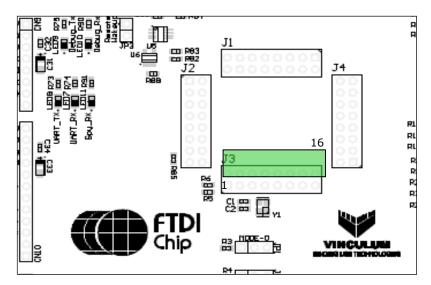

## 5.19 VNC2 Daughterboard Connector – J3

Figure 5.24 VNC2 Daughterboard Connector J3.

| Schematic                   | Connector | VCN2 Pin No |        |        | 10     |                                                     |

|-----------------------------|-----------|-------------|--------|--------|--------|-----------------------------------------------------|

| Signal Name <sup>(43)</sup> |           | 32-PIN      | 48-PIN | 64-PIN | type   | Description                                         |

| PROG#                       | 1         | 9           | 10     | 10     | Input  | PROG# input to VNC2. Connected via multiplexer U4.  |

| RESET#                      | 2         | 10          | 9      | 9      | Input  | RESET# input to VNC2. Connected via multiplexer U4. |

| SPI_M_CS#                   | 3         | -           | 23     | 64     | IO     | Connected to P1 pin 52 / CN9 pin 7/ CN8 pin 4.      |

| SPI_M_MISO                  | 4         | -           | 22     | 63     | IO     | Connected to P1 pin 51 / CN9 pin 6/ CN8 pin 3.      |

| SPI_M_MOSI                  | 5         | -           | 21     | 62     | IO     | Connected to P1 pin 47 / CN9 pin 5/ CN8 pin 2.      |

| SPI_M_CLK                   | 6         | -           | 20     | 61     | IO     | Connected to P1 pin 46 / CN9 pin 4/ CN8 pin 1.      |

| XTOUT                       | 7         | 5           | 5      | 5      | Output | Output from 12MHz oscillator cell on VNC2.          |

| XTIN                        | 8         | 4           | 4      | 4      | Input  | Input to 12MHz oscillator cell on VNC2.             |

| GPIO2                       | 9         | 14          | 13     | 13     | IO     | Connected to P1 pin 6 / CN3 pin 3.                  |

| GPIO1                       | 10        | 12          | 12     | 12     | IO     | Connected to P1 pin 5 / CN3 pin 2.                  |

| FIFO_DATA0                  | 11        | -           | -      | 15     | IO     | Connected to P1 pin 8/CN3 pin 5 /CN11 pin 1.        |

| GPIO3                       | 12        | 15          | 14     | 14     | IO     | Connected to P1 pin 7 / CN3 pin 4.                  |

| FIFO_DATA2                  | 13        | -           | -      | 17     | IO     | Connected to P1 pin 10/CN3 pin 7 /CN11 pin 3.       |

| FIFO_DATA1                  | 14        | -           | -      | 16     | IO     | Connected to P1 pin 9/CN3 pin 6 /CN11 pin 2.        |

| GND                         | 15        | -           | -      | -      | -      | Ground pin.                                         |

| GND                         | 16        | -           | -      | -      | -      | Ground pin.                                         |

Table 5.19 Connector J3 Pinout.

<sup>(43)</sup> The signal names relate to the labels used on pages 1 & 2 of the V2-EVAL base board schematic. Unless otherwise stated, the function of the IO signals is set by the user application running on the VNC2.

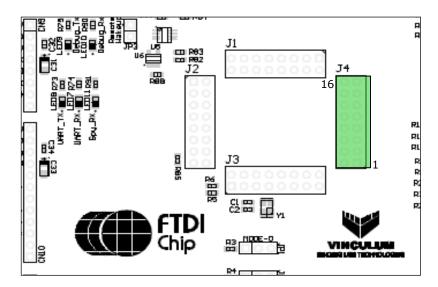

# 5.20 VNC2 Daughterboard Connector – J4

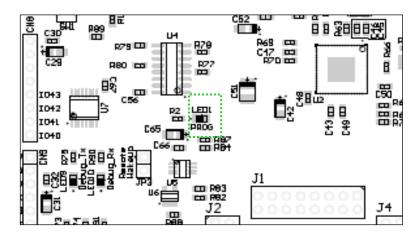

Figure 5.25 VNC2 Daughterboard Connector J4.

| Schematic                   | Connector<br>Pin | VCN2 Pin No |        |        | IO   |                                                   |

|-----------------------------|------------------|-------------|--------|--------|------|---------------------------------------------------|

| Signal Name <sup>(44)</sup> |                  | 32-PIN      | 48-PIN | 64-PIN | type | Description                                       |

| FIFO_DATA4                  | 1                | -           | -      | 19     | IO   | Connected to P1 pin 12 / CN4 pin 1/ CN11 pin 5.   |

| FIFO_DATA3                  | 2                | -           | -      | 18     | IO   | Connected to P1 pin 11 / CN3 pin 8/ CN11 pin 4.   |

| FIFO_DATA6                  | 3                | -           | -      | 22     | IO   | Connected to P1 pin 14 / CN4 pin 3/ CN11 pin 7.   |

| FIFO_DATA5                  | 4                | -           | -      | 20     | IO   | Connected to P1 pin 13 / CN4 pin 2/ CN11 pin 6.   |