# 3 Phase Motor Driver-IC for Automotive Safety Applications

Check for Samples: DRV3201-Q1

## **FEATURES**

- **Qualified for Automotive Applications**

- **AEC-Q100 Test Guidance With the Following** Results:

- Device Temperature Grade 1: –40°C to 125°C Ambient Operating Temperature

- Device HBM ESD Classification Level H2

- Device CDM ESD Classification Level C2

- 3 Phase Bridge Driver for Motor Control

- **Drives 6 Separate N-Channel Power MOSFETs** up to 250 nC Gate Charge

- Programmable 140 mA-1 A Gate Current Drive (Source/Sink) for Easy Output Slope **Adjustment**

- -7 V to 40 V Compliance on All FET Driver Pins to Handle Inductive Under/Overshooting

- **Separate Control Input for Each Power MOSFET**

- PWM Frequency up to 30 kHz

- **Supports 100% Duty Cycle Operation**

- Operating Voltage: 4.75 to 30 V

- **Proper Low Supply Voltage Operation Due to Integrated Boost Converter for Gate-Driver Voltage Generation**

- Logic Functional Down to 3 V

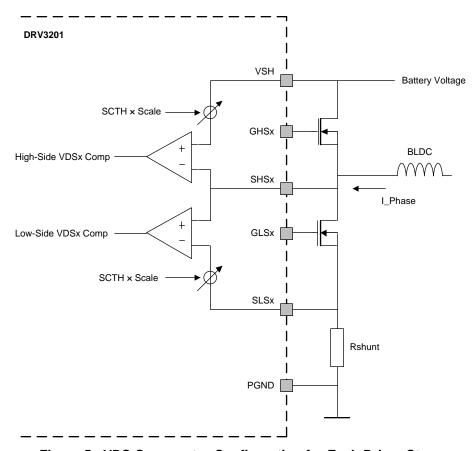

- **Short Circuit Protection With VDS-Monitoring** and Adjustable Detection Level

- **Two Integrated High Accuracy Current Sense** Amplifiers With Two Gain-Programmable Second Stage for Higher Resolution at Low **Load Current Operation**

- **Over and Undervoltage Protection**

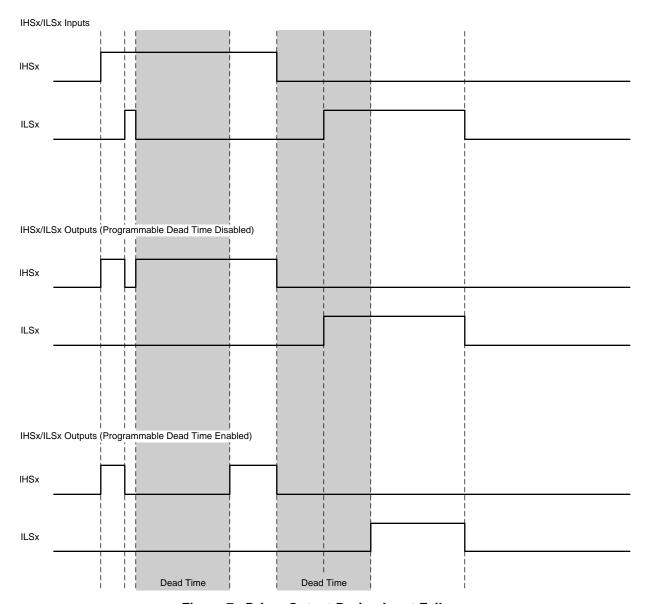

- **Shoot Through Protection With Programmable Dead Time**

- **Three Real Time Phase Comparators**

- **Over Temperature Warning and Shut Down**

- Sophisticated Failure Detection and Handling Through SPI Interface

- **Sleep Mode Function**

- **Reset and Enable Function**

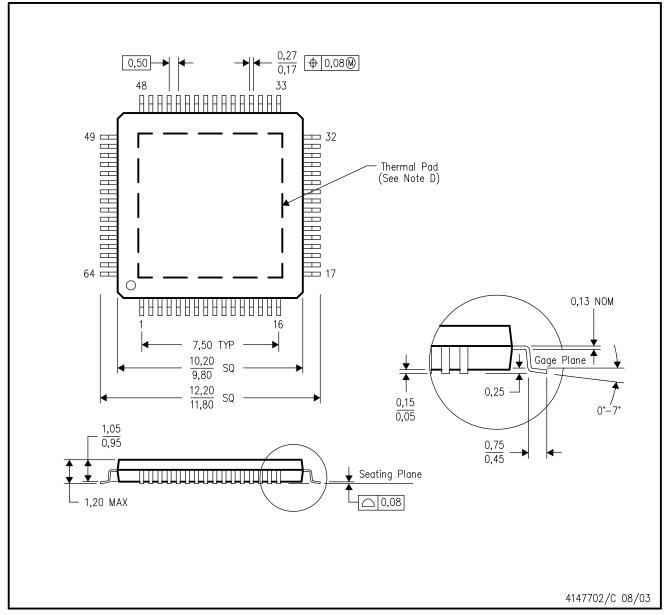

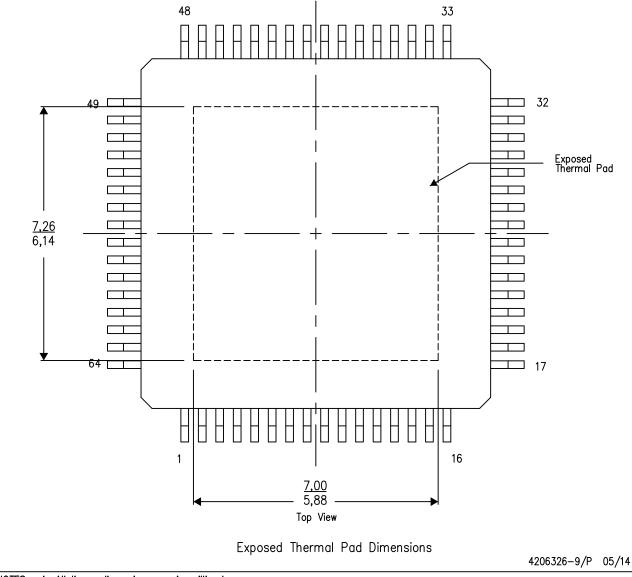

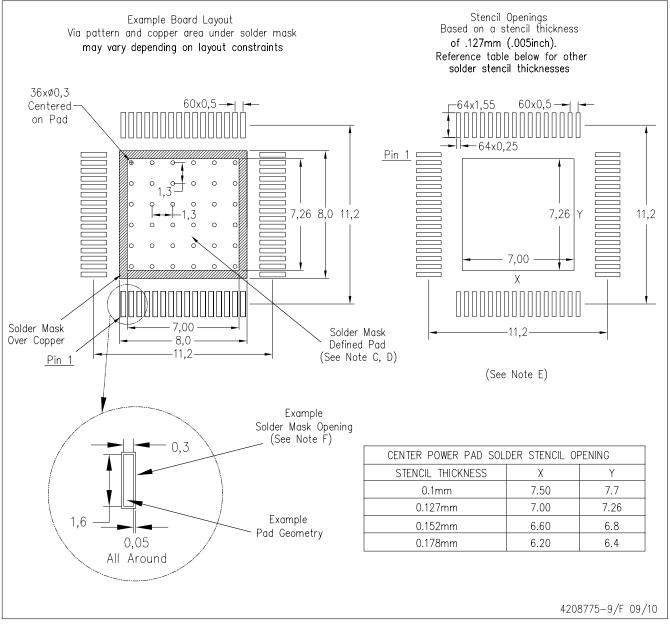

- Package: 64-pin HTQFP PowerPAD™

## APPLICATIONS

- **Automotive Safety Critical Motor-Control Applications**

- Electrical Power Steering (EPS, EHPS)

- **Electrical Brake/Brake Assist**

- **Transmission**

- Oil-Pump

- **Industrial Safety Critical Motor-Control Applications**

## DESCRIPTION

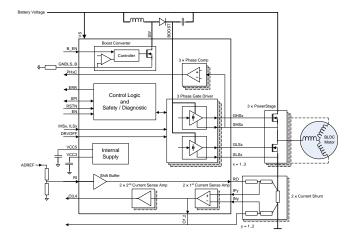

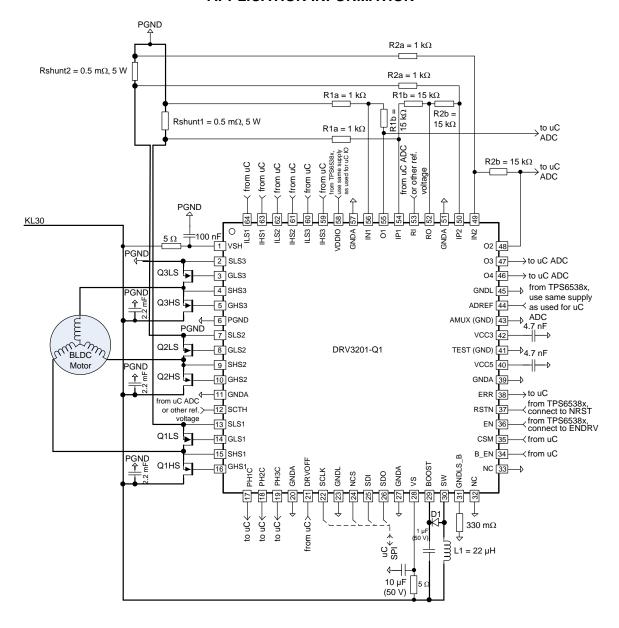

The bridge driver is dedicated to automotive 3 phase brushless DC motor control including safety relevant applications. It provides six dedicated drivers for normal level N-Channel MOSFET transistors. The driver capability is designed to handle gate charges of 250 nC, and the driver source/sink currents are programmable for easy output slope adjustment. The device also incorporates sophisticated diagnosis, protection and monitoring features through an SPI interface. A boost converter with integrated FET provides the overdrive voltage, allowing full control on the power-stages even for low battery voltage down to 4.75 V.

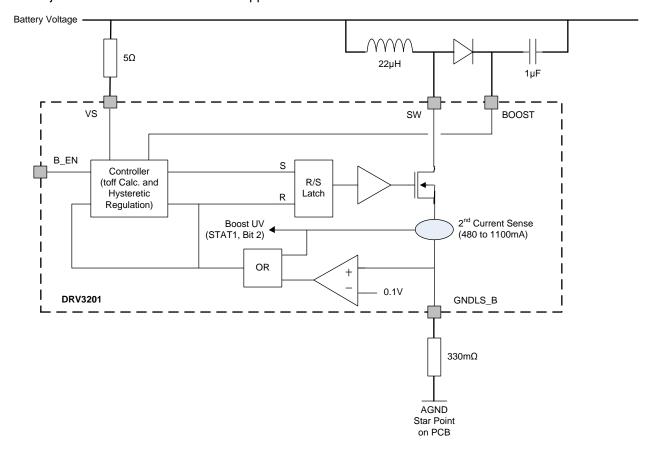

Figure 1. Typical Application Diagram

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD is a trademark of Texas Instruments.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## THERMAL INFORMATION

|                  |                                              | DRV3201       |      |

|------------------|----------------------------------------------|---------------|------|

|                  | THERMAL METRIC <sup>(1)</sup>                | HTQFP         | UNIT |

|                  |                                              | PAP - 64 PINS |      |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 21.6          |      |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 10.9          |      |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 4.5           | °C/M |

| ΨЈТ              | Junction-to-top characterization parameter   | 0.1           | °C/W |

| ΨЈВ              | Junction-to-board characterization parameter | 4.4           |      |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 0.3           |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# ABSOLUTE MAXIMUM RATINGS(1)(2)

over operating temperature  $T_1 = -40$ °C to 150°C

| SYMBOL                                                       | PARAMETER                                       | CONDITIONS                                                                                    | VA         | UNIT          |      |

|--------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------|------------|---------------|------|

|                                                              |                                                 |                                                                                               | MIN        | MAX           |      |

| VS, VSH                                                      | DC                                              | VS, negative voltages with minimum serial resistor 5 $\Omega$                                 | -5         | 38            | ٧    |

|                                                              |                                                 | VS, negative voltages with external protection NMOS                                           | -1         | 38            | V    |

| ve ven                                                       | Cumply vallage transient to                     | VS, negative voltages with minimum serial resistor 5 $\boldsymbol{\Omega}$                    | <b>-</b> 5 | 42            | V    |

| VS, VSH                                                      | Supply voltage, transient 1s                    | VS, negative voltages with external protection NMOS driven by device internal circuit         | -1         | 42            | V    |

| GHSx                                                         | Gate high-side voltage                          |                                                                                               | -7         | 47            | V    |

| SHSx                                                         | Source high-side voltage                        |                                                                                               | -7         | 42            | V    |

| GHSx-SHSx                                                    | Gate-source high-side voltage difference        | External driven, internal limited (see V <sub>GS,HS,high</sub> in ELECTRICAL CHARACTERISTICS) | -0.3       | 15            | V    |

| GLSx                                                         | Gate low-side voltage                           |                                                                                               | -7         | 20            | V    |

| SLSx                                                         | Source low-side voltage                         |                                                                                               | -7         | 7             | V    |

| GLSx-SLSx                                                    | Gate-source low-side voltage difference         | External driven, internal limited (see V <sub>GS,LS,high</sub> in ELECTRICAL CHARACTERISTICS) | -0.3       | 15            | V    |

| BOOST, SW                                                    | Boost converter                                 | Negative voltage with minimum serial resistor 5 $\boldsymbol{\Omega}$                         | -0.3       | 60            | V    |

|                                                              |                                                 | Negative voltage with external protection NMOS                                                | -1         | 60            | V    |

| INx, IPx                                                     | Current sense input voltage                     |                                                                                               | -0.3       | 42            | V    |

| INx, IPx clamping current                                    | Current sense input current                     | Clamping current                                                                              | <b>-</b> 5 | 5             | mA   |

| Ox                                                           | Current sense output voltage                    |                                                                                               | -0.3       | ADREF<br>+0.3 | V    |

| Ox forced input current                                      |                                                 |                                                                                               | -10        | 10            | mA   |

| VDDIO, ADREF                                                 | Analog input voltage                            |                                                                                               | -0.3       | 8             | V    |

| ILSx,IHSx, EN, DRVOFF,<br>SCLK, NCS, SDI, RSTN,<br>CSM, B_EN | Digital input voltage                           |                                                                                               | -0.3       | 18            | V    |

| SCTH                                                         | Analog input voltage                            |                                                                                               | -0.3       | 18            | V    |

| GNDA, GNDL, GNDLS_B, PGND, NC                                | Difference one GND or NC to any other GND or NC |                                                                                               | -0.3       | 0.3           | V    |

| T <sub>J</sub>                                               | Operating virtual junction temperature range    |                                                                                               | -40        | 150           | °C   |

| T <sub>S</sub>                                               | Storage temperature range                       |                                                                                               | -40        | 165           | °C   |

| ESD all pins                                                 | ESD performance of all pins to any other pin    | HBM model AEC-Q100-002D Classification Level H2                                               | -2         | 2             | kV   |

| ESD pin SHSx                                                 | ESD performance of SHSx to SHSx and GND         | HBM model AEC-Q100-002D Classification Level H2                                               | -4         | 4             | kV   |

| ESD all pin                                                  | ESD performance of all pins to any other pin    | CDM Model AEC-Q100-011B Classification Level C2                                               | -500       | 500           | V    |

| SR <sub>SHS</sub>                                            | Maximum slew rate of SHSx pins                  |                                                                                               | -150       | 150           | V/µs |

| ERR, SDO, PHxC, RO                                           | Analog/digital output voltages                  |                                                                                               | -0.3       | 8             | V    |

| ERR, SDO, PHxC, RO                                           | Forced input/output current                     |                                                                                               | -10        | 10            | mA   |

| TEST, AMUX, NC                                               | Unused pins. Connect to GND                     |                                                                                               | -0.3       | 0.3           | V    |

| RI                                                           | Analog input voltage                            |                                                                                               | -0.3       | 18            | V    |

| VCC5                                                         | Internal supply voltage                         |                                                                                               | -0.3       | 8             | V    |

| I_VCC5                                                       | Short-to-ground current                         | Internal current limit                                                                        |            | 40            | mA   |

| VCC3                                                         | Internal supply voltage                         |                                                                                               | -0.3       | 3.6           | V    |

| VCC3                                                         | Short-to-ground current                         | Limited by VCC5                                                                               |            | 40            | mA   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> All voltages are with respect to network ground terminal, unless otherwise specified.

## RECOMMENDED OPERATING CONDITIONS

Over operating temperature  $T_J$  = -40°C to 150°C. Over recommended operating conditions VS = 4.75 to 30 V,  $f_{PWM}$  < 30 kHz (unless otherwise noted)

|                                                                       |                                                                                                                 | MIN   | NOM | MAX | UNIT |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------|-----|-----|------|

| Supply voltage, normal voltage operation, VS                          | Full device functionality. Operation at VS = 4.75V only when coming from higher VS. Min. VS for startup = 4.85V | 4.75  |     | 30  | V    |

| Supply voltage, logic operation, VSLO                                 | Logic functional (during battery cranking after coming from full device functionality)                          | 3     |     | 40  | V    |

| Supply voltage for digital IOs, VDDIO                                 |                                                                                                                 | 2.7   |     | 5.5 | V    |

| Duty cycle of bridge drivers, D                                       |                                                                                                                 | 0     |     | 100 | %    |

| PWM switching frequency, f <sub>PWM</sub>                             |                                                                                                                 | 0     |     | 30  | kHz  |

| Junction temperature, T <sub>J</sub>                                  |                                                                                                                 | -40   |     | 150 | °C   |

| Operating ambient free-air temperature, T <sub>A</sub>                | With proper thermal connection                                                                                  | -40   |     | 125 | °C   |

| Current sense input voltage range, V <sub>INx</sub> ,V <sub>IPx</sub> | Relative to GNDA                                                                                                | -0.14 |     | 1.6 | V    |

| Clamping voltage for current sense amplifier outputs O                | 1/ 2/ 3/ 4, ADREF                                                                                               | 0.7   |     | 5   | V    |

| VCC3 output current, I_VCC3                                           | Intended for MCU ADC input                                                                                      | 0     |     | 100 | μA   |

| VCC3 decoupling capacitance, C_VCC3                                   |                                                                                                                 | 1     | 4.7 | 22  | nF   |

| VCC5 output current, I_VCC5                                           | Intended for MCU ADC input                                                                                      | 0     |     | 100 | μA   |

| VCC5 decoupling capacitance, C_VCC5                                   |                                                                                                                 | 1     | 4.7 | 470 | nF   |

4

## **ELECTRICAL CHARACTERISTICS**

over operating temperature  $T_J = -40^{\circ}\text{C}$  to 150°C and recommended operating conditions, VS = 4.75 to 30 V,  $f_{PWM} < 30 \text{ kHz}$  (unless otherwise noted)

|                          | PARAMETER                                                                              | TEST CONDITIONS                                                                                                                        | MIN        | TYP | MAX  | UNIT |

|--------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------|-----|------|------|

| Power Suppl              |                                                                                        | 1201 00112110110                                                                                                                       |            |     | 1    |      |

| I <sub>VSq</sub>         | VS quiescent current shut down (sleep mode)                                            | VS = 14 V, no operation, T <sub>J</sub> < 85°C EN = low, RSTN = high <sup>(1)</sup> total leakage current on all supply connected pins |            |     | 30   | μA   |

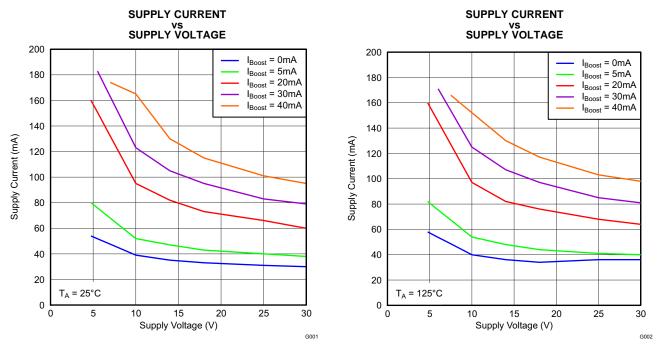

| I <sub>VSn</sub>         | VS quiescent current normal operation (boost converter enabled, drivers not switching) | See Figure 18 and Figure 19.                                                                                                           |            | 65  | 90   | mA   |

| VCC5                     | Internal supply voltage                                                                | VS > 6 V, external load current < 100µA. Decoupling capacitance is typically 4.7nF.                                                    | 4.7        |     | 5.3  | V    |

| VCC3                     | Internal supply voltage                                                                | VS > 3 V, external load current < 100µA. Decoupling capacitance is typically 4.7nF.                                                    | 2.1 (2)    |     | 3.6  | V    |

|                          |                                                                                        | VS >4.75 V, external load current < 100µA. Decoupling capacitance is typically 4.7nF.                                                  | 3.15       |     | 3.45 | V    |

| Current Sens             | e Amplifier First Stages                                                               |                                                                                                                                        |            |     |      |      |

| V <sub>off1/2</sub>      | Initial input offset of amplifiers at T <sub>J</sub> = 25°C                            |                                                                                                                                        | -1         | 0   | 1    | mV   |

| V <sub>off1/2_d</sub>    | Temperature and aging offset                                                           |                                                                                                                                        | -1         | 0   | 1    | mV   |

|                          | Input lookage current INV ID:                                                          | 0 V < INx, IPx < 1 V pin-to-pin and pin-to-ground                                                                                      | -0.5       |     | 0.5  | μA   |

| I <sub>leak,INxIPx</sub> | Input leakage current INx, IPx                                                         | -0.3 V < INx, IPx < 0 V pin-to-pin and pin-to-ground                                                                                   | -50        |     | 0.5  | μA   |

| G <sub>01/2</sub>        | DC open loop gain                                                                      | See Note (3)                                                                                                                           | 80         |     |      | dB   |

| V <sub>O1/2_N</sub>      | Nominal output voltage range                                                           | Normal voltage operation, VS ≥ 6 V, ADREF = 5 V; 0.5 mA load current                                                                   | 0.5        |     | 4.5  | V    |

| V <sub>O1/2_L</sub>      | Output voltage range during low voltage operation                                      | Low voltage operation, 4.75 V ≤ VS ≤ 6 V, ADREF = 5 V; 0.5 mA load current                                                             | 0.5        |     | 4    | V    |

| GBP <sub>1/2</sub>       | Gain bandwidth product (GBP)                                                           | 0.5 V ≤ O1/2 ≤ 4.5 V <sup>(3)</sup>                                                                                                    | 5          |     |      | MHz  |

| SR <sub>1/2</sub>        | Slew rate                                                                              | 0.5 V ≤ O1/2 ≤ 4.5 V, cap load = 25 pF                                                                                                 | 2.9        |     | 15   | V/µs |

| PSRR <sub>1/2</sub>      | Power supply rejection ratio                                                           | VS to O1/2. Decoupling capacitance is typically 4.7 nF on VCC5 and VCC3. (3)                                                           |            | 80  |      | dB   |

| CMRR <sub>1/2</sub>      | Common mode rejection ratio                                                            | IN1/2 or IP1/2 to O1/2 (3)                                                                                                             |            | 80  |      | dB   |

| Current Sens             | se Amplifier Second Stages                                                             |                                                                                                                                        |            |     |      |      |

| V <sub>off3/4</sub>      | Initial input offset of amplifiers at T <sub>J</sub> = 25 °C                           | VRO = 2.5V                                                                                                                             | <b>-</b> 5 | 0   | 5    | mV   |

| V <sub>off3/4_d</sub>    | Temperature and aging offset                                                           |                                                                                                                                        | -3         | 0   | 3    | mV   |

| V <sub>O3/4_N</sub>      | Nominal output voltage range                                                           | Normal voltage operation, VS ≥ 6 V, ADREF = 5 V; 0.5 mA load current                                                                   | 0.5        |     | 4.5  | V    |

| V <sub>O3/4_L</sub>      | Output voltage range during low voltage operation                                      | Low voltage operation, 4.75 V ≤ VS ≤ 6 V, ADREF = 5 V; 0.5 mA load current                                                             | 0.5        |     | 4    | V    |

| GBP <sub>3/4</sub>       | Gain bandwidth product (GBP)                                                           | 0.5 V ≤ O3/4 ≤ 4.5 V, gain = 8 <sup>(3)</sup>                                                                                          | 5          |     |      | MHz  |

| SR <sub>3/4</sub>        | Slew rate                                                                              | 0.5 V ≤ O3/4 ≤ 4.5 V, cap load = 25 pF                                                                                                 | 2.9        |     | 15   | V/µs |

| G1                       | Gain1                                                                                  |                                                                                                                                        | 1.98       | 2   | 2.02 | V/V  |

| G2                       | Gain2                                                                                  |                                                                                                                                        | 3.96       | 4   | 4.04 | V/V  |

| G3                       | Gain3                                                                                  |                                                                                                                                        | 5.82       | 6   | 6.18 | V/V  |

| G4                       | Gain4                                                                                  |                                                                                                                                        | 7.84       | 8   | 8.16 | V/V  |

| PSRR <sub>3/4</sub>      | Power supply rejection ratio                                                           | VS to O3/4 decoupling capacitance is typically 4.7 nF on VCC5 and VCC3. (3)                                                            |            | 80  |      | dB   |

| Shift Buffer             |                                                                                        |                                                                                                                                        |            |     |      | 1    |

| VRI                      | Shift input voltage range                                                              |                                                                                                                                        | 0.1        |     | 2.6  | ٧    |

| VRO                      | Shift output voltage range                                                             |                                                                                                                                        | 0.1        |     | 2.6  | V    |

| VR <sub>offset</sub>     | Shift voltage offset                                                                   |                                                                                                                                        | <b>–</b> 5 |     | 5    | mV   |

| I <sub>RO</sub>          | Shift output current capability                                                        |                                                                                                                                        | <u>–</u> 5 |     | 5    | mA   |

| NO.                      |                                                                                        | VRI = 2.5 V, pin-to-ground                                                                                                             | -0.2       |     | -    | 1    |

<sup>(1)</sup> The DRV3201 can only enter Sleep Mode when EN is set to low while RSTN is kept high. Once the device is in Sleep Mode (100 µs after EN has been set low), the RSTN pin can be set low without affecting the Sleep Mode.

<sup>(2)</sup> Lower limit of functional range dependent of internal PowerOnReset level for internal digital logic. It is specified by VS > 3 V the internal digital logic is operational and not put into PowerOnReset.

<sup>(3)</sup> Specified by design

# **ELECTRICAL CHARACTERISTICS (continued)**

over operating temperature  $T_J = -40$ °C to 150°C and recommended operating conditions, VS = 4.75 to 30 V,  $f_{PWM} < 30$  kHz (unless otherwise noted)

|                         | PARAMETER                                                                   | TEST CONDITIONS                                                                                                  | MIN      | TYP  | MAX  | UNIT |

|-------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------|------|------|------|

| ADREF                   |                                                                             |                                                                                                                  |          | 1    | 1    |      |

| V <sub>oxm</sub>        | Maximum DC voltage of O1/2/3/4 relative to ADREF                            | ADREF = 3.3/ 5 V; Ox-ADREF                                                                                       | -0.25    | 0.03 | 0.25 | V    |

| V <sub>oxos</sub>       | Overshoot of O1/2/3/4 over ADREF                                            | Ox-ADREF; for < 1 $\mu$ s; never higher than 5 V over GND <sup>(3)</sup>                                         |          |      | 1.2  | V    |

| I <sub>ADREF</sub>      | Bias current for voltage clamping circuit                                   | ADREF = 3.3/5V, pin-to-ground                                                                                    |          |      | 150  | μΑ   |

| Gate-Driver             |                                                                             | · · ·                                                                                                            |          |      |      | 1    |

| V <sub>GS,low</sub>     | Gate-source voltage low high/low-side driver                                | Active pulldown, I <sub>load</sub> = -2 mA                                                                       | 0        |      | 0.2  | ٧    |

| R <sub>GSp</sub>        | Passive gate-source resistance                                              | V <sub>qs</sub> ≤ 200 mV                                                                                         | 80       | 500  | 700  | kΩ   |

| R <sub>GSsa</sub>       | Semi-active gate-source resistance                                          | In sleep mode, V <sub>qs</sub> > 2 V                                                                             |          | 7    | 8    | kΩ   |

| R <sub>GSa2</sub>       | Active gate-source resistance                                               | V <sub>gs</sub> < 1 V, gate driven low by gate-driver, Regyx = 100                                               |          |      | 2.3  | Ω    |

| R <sub>GSa1</sub>       | Active gate-source resistance                                               | V <sub>qs</sub> < 1 V, gate driven low by gate-driver, Regyx = 010                                               |          |      | 4.5  | Ω    |

| R <sub>GSa0</sub>       | Active gate-source resistance                                               | V <sub>gs</sub> < 1 V, gate driven low by gate-driver, Regyx = 001                                               |          |      | 9    | Ω    |

| V <sub>GS,HS,high</sub> | high-side output voltage                                                    | $I_{load} = -2 \text{ mA}$                                                                                       | 9        |      | 12.8 | V    |

| V <sub>GS,LS,high</sub> | low-side output voltage                                                     | I <sub>load</sub> = -2 mA                                                                                        | 9        |      | 12.8 | V    |

| IGC2C                   | Gate charge current high/low-side driver 2                                  | 2V ≤ (VGLSx-VSLSx) ≤ 5V, Regyx = 100, if not disabled in CFG1                                                    | 0.4      | 0.57 | 0.74 | Α    |

| IGC1C                   | Gate charge current high/low-side driver 1                                  | $2V \le (VGLSx-VSLSx) \le 5V$ , Regyx = 010, if not disabled in CFG1                                             | 0.2      | 0.29 | 0.37 | Α    |

| IGC0C                   | Gate charge current high/low-side driver 0                                  | 2V ≤ (VGLSx-VSLSx) ≤ 5V, Regyx = 001, if not disabled in CFG1                                                    | 0.1 0.14 |      | 0.18 | Α    |

| IGD2D                   | Gate discharge current high/low-side driver 2                               | 2V ≤ (VGLSx-VSLSx) ≤ 5V, Regyx = 100, if not disabled in CFG1                                                    | 0.4      | 0.57 | 0.74 | Α    |

| IGD1D                   | Gate discharge current high/low-side driver 1                               | $2V \le (VGLS-VSLS) \le 5V$ , Regyx = 010, if not disabled in CFG1                                               | 0.2      | 0.29 | 0.37 | Α    |

| IGD0D                   | Gate discharge current high/low-side driver 0                               | $2V \le (VGLS-VSLS) \le 5V$ , Regyx = 001, if not disabled in CFG1                                               | 0.1      | 0.14 | 0.18 | А    |

| $t_{Don}$               | Propagation on delay time                                                   | After ILx/IHx rising edge                                                                                        |          | 200  | 250  | ns   |

| $t_{Dondif}$            | Propagation on delay time difference                                        | LSx to LSy and HSx to HSy                                                                                        |          |      | 70   | ns   |

| $t_{Doff}$              | Propagation off delay time                                                  | After ILx/IHx falling edge                                                                                       |          | 200  | 350  | ns   |

| t <sub>Doffdiff</sub>   | Propagation off delay time difference                                       | LSx to LSy and HSx to HSy                                                                                        |          |      | 50   | ns   |

| $t_{Don\_Doff\_diff}$   | Difference between propagation on delay time and propagation off delay time | For each Gate-Driver in each channel                                                                             |          |      | 150  | ns   |

| t <sub>DRVoff</sub>     | Propagation off (DRVOFF) delay time                                         | After rising edge on DRVOFF                                                                                      |          | 200  | 400  | ns   |

| t <sub>ENoff</sub>      | Propagation off (EN) deglitching time                                       | After falling edge on EN                                                                                         |          | 6    |      | μs   |

| t <sub>SD</sub>         | Time until device enters shutdown                                           | After falling edge on EN                                                                                         | 20       |      | 35   | μs   |

| t <sub>RSTNoff</sub>    | Propagation off (RSTN) delay time                                           | After falling edge on RSTN                                                                                       |          | 200  | 400  | ns   |

| A <sub>dt</sub>         | Accuracy of dead time                                                       | If not disabled in CFG1                                                                                          | -15      |      | 15   | %    |

| Boost Conve             | rter                                                                        |                                                                                                                  |          |      |      |      |

| I <sub>BOOSTn</sub>     | BOOST pin quiescent current normal operation (drivers not switching)        | 4.75 V < VS <32 V                                                                                                |          |      | 20   | mA   |

| I <sub>BOOST,sw</sub>   | BOOST pin additional load current due to switching gate-drivers             | Without external power FETS (pure internal switching current, 30kHz all gate-drivers switching at the same time) |          |      | 3    | mA   |

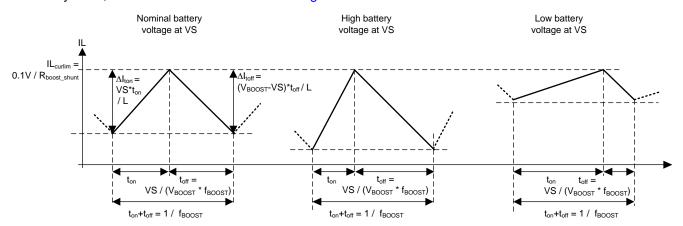

| V <sub>BOOST</sub>      | Boost output voltage                                                        | BOOST-VS voltage                                                                                                 | 13.8     | 15   | 16   | V    |

| I <sub>BOOST</sub>      | Output current capability                                                   | For device internal use only                                                                                     | 40       |      |      | mA   |

| f <sub>BOOST</sub>      | Switching frequency                                                         | BOOST-VS > V <sub>BOOSTUV</sub> (4)                                                                              | 2        | 2.5  | 3    | MHz  |

| V <sub>BOOSTUV</sub>    | Undervoltage shutdown Level                                                 | BOOST-VS voltage                                                                                                 | 11       |      | 11.9 | V    |

| t <sub>BCSD</sub>       | Filter time for undervoltage shutdown                                       |                                                                                                                  | 5        |      | 6    | μs   |

| $V_{GNDLS\_B,off}$      | Voltage at GNDLS_B pin at which boost FET switches off due to current limit |                                                                                                                  | 70       | 100  | 130  | mV   |

|                         |                                                                             |                                                                                                                  |          |      |      |      |

During startup when BOOST-VS < V<sub>BOOSTUV</sub> , f<sub>BOOST</sub> is typically 1.25 MHz. (4)

6

# **ELECTRICAL CHARACTERISTICS (continued)**

over operating temperature  $T_J = -40^{\circ}\text{C}$  to 150°C and recommended operating conditions, VS = 4.75 to 30 V,  $f_{PWM} < 30 \text{ kHz}$  (unless otherwise noted)

|                       | PARAMETER                                                      | TEST CONDITIONS                                                         | MIN             | TYP             | MAX             | UNIT |

|-----------------------|----------------------------------------------------------------|-------------------------------------------------------------------------|-----------------|-----------------|-----------------|------|

| t <sub>SW,off</sub>   | Delay of the GNDLS_B current limit comparator                  | See Note <sup>(5)</sup>                                                 |                 |                 | 20              | ns   |

| I <sub>SW,fail</sub>  | Internal second level current limit                            |                                                                         | 420             |                 | 700             | mA   |

| R <sub>DS(on)</sub>   | Resistance BOOST FET                                           |                                                                         | 0.48            |                 | 1.2             | Ω    |

| Digital Input         | ts                                                             |                                                                         |                 |                 |                 |      |

| INL                   | Input low threshold                                            | All digital inputs: RSTN, B_EN, NCS, DRVOFF, ILSx, IHSx, CSM, SDI, SCLK |                 |                 | 0.9             | V    |

| ENL                   | EN input low threshold                                         |                                                                         |                 | 0.27            | x VDDIO         | V    |

| INH                   | Input high threshold                                           | All digital inputs: RSTN, B_EN, NCS, DRVOFF, ILSx, IHSx, CSM, SDI, SCLK | 2.3             |                 |                 | V    |

| ENH                   | EN input high threshold                                        |                                                                         | 0.65 x VDDI     | )               |                 | V    |

| Inhys                 | Input hysteresis                                               | All digital inputs: RSTN, B_EN, NCS, DRVOFF, ILSx, IHSx, CSM, SDI, SCLK | 0.3             | 0.8             | 1               | V    |

| EN Inhys              | EN input hysteresis                                            |                                                                         | 0.18 x<br>VDDIO | 0.25 x<br>VDDIO | 0.48 x<br>VDDIO | V    |

| $R_{\text{pd,EN}}$    | Input pull down resistor at EN pin                             | EN                                                                      | 170             | 200             | 300             | kΩ   |

| t <sub>deg,ENon</sub> | Power-up time after EN pin high from sleep mode to active mode | After rising edge on EN, time until logic out-of-reset                  |                 | 1               |                 | ms   |

| $R_{\text{pullup}}$   | Input pull up resistance                                       | RSTN, B_EN, NCS, DRVOFF                                                 | 100             | 140             | 200             | kΩ   |

| R <sub>pulldown</sub> | Input pull down resistance                                     | ILSx, IHSx, CSM, SDI                                                    | 100             | 140             | 200             | kΩ   |

| Digital Outp          | uts                                                            |                                                                         |                 |                 |                 |      |

| ОН                    | Output high voltage                                            | All digital outputs: ERR, SDO, PHxC, I = ±2 mA;                         | VDDIO -0.2      |                 |                 | V    |

| OL                    | Output low voltage                                             | VDDIO in functional range <sup>(6)</sup>                                |                 |                 | 0.2             | V    |

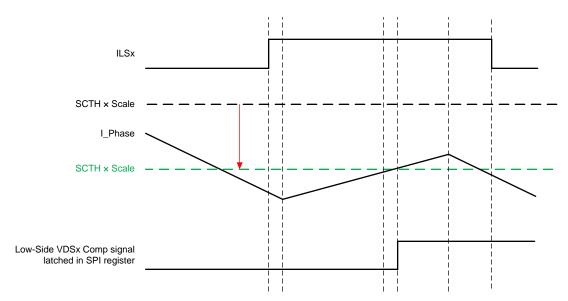

| VDS Monitor           | ring                                                           |                                                                         | ·               |                 |                 |      |

| V <sub>SCTH</sub>     | VDS short circuit threshold input range                        | If not disabled in CFG1                                                 | 0               |                 | 2.5             | V    |

| A <sub>vds</sub>      | Accuracy of VDS monitoring                                     |                                                                         | -250            |                 | 250             | mV   |

| t <sub>VDS</sub>      | Detection filter time                                          | Only rising edge of VDS comparators are filtered                        |                 | 5               |                 | μs   |

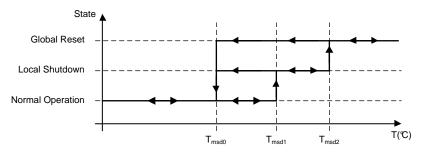

| THERMAL S             | SHUTDOWN                                                       |                                                                         | ·               |                 |                 |      |

| T <sub>msd0</sub>     | Thermal recovery                                               |                                                                         | 140             | 150             |                 | °C   |

| T <sub>msd1</sub>     | Thermal warning                                                | C N-4-(7)                                                               | 160             | 170             |                 | °C   |

| T <sub>msd2</sub>     | Thermal global reset                                           | See Note <sup>(7)</sup>                                                 | 175             | 190             | 205             | °C   |

| T <sub>hmsd</sub>     | Thermal shutdown hysteresis                                    |                                                                         |                 | 40              |                 | °C   |

| t <sub>TSD</sub>      | Thermal warning filter time                                    |                                                                         | 40              | 45              | 50              | μs   |

| t <sub>TSD</sub>      | Thermal shutdown filter time                                   |                                                                         | 40              | 45              | 50              | μs   |

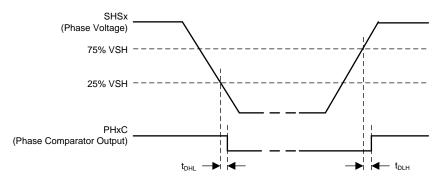

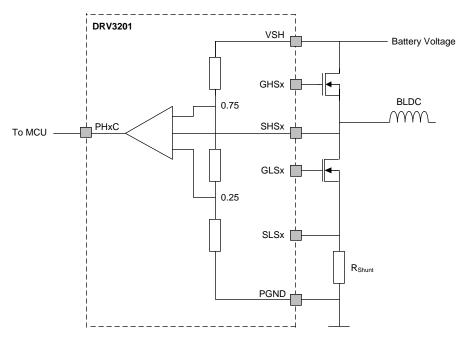

| Phase Comp            | parator                                                        |                                                                         |                 |                 |                 |      |

| $V_{PCHth}$           | Phase comparator high threshold                                |                                                                         | 0.65 x<br>VSH   |                 | 0.88 x<br>VSH   |      |

| $V_{PCLth}$           | Phase comparator low threshold                                 |                                                                         | 0.15 x<br>VSH   |                 | 0.4 x<br>VSH    |      |

| t <sub>DHL</sub>      | Delay time high-low                                            | C <sub>out</sub> = 50 pF                                                |                 | 80              | 120             | ns   |

| t <sub>DLH</sub>      | Delay time low-high                                            | C <sub>out</sub> = 50 pF                                                |                 | 80              | 120             | ns   |

|                       | Matching between two channels                                  |                                                                         | -30             | -               | 30              | ns   |

| t <sub>D</sub>        | Matching between rising and falling edge for each channel      |                                                                         | -30             |                 | 30              | ns   |

| R <sub>VSH</sub>      | Resistance of internal voltage divider to ground               |                                                                         | 170             |                 | 330             | kΩ   |

| VS Monitorii          | ng                                                             |                                                                         |                 |                 |                 |      |

|                       | Overvoltage shutdown level, OV = OFF                           |                                                                         | 29.3            |                 | 30.7            | V    |

| $V_{VSOV}$            | Recovery level from Overvoltage shutdown, OV = ON              | If not disabled in CFG1                                                 | 27.5            |                 | 29.3            | V    |

|                       |                                                                |                                                                         |                 |                 |                 |      |

<sup>(5)</sup> Specified by design

<sup>(6)</sup> All digital outputs have a push-pull output stage between VDDIO and ground.

<sup>(7)</sup> Specified by design

# **ELECTRICAL CHARACTERISTICS (continued)**

over operating temperature  $T_J = -40^{\circ}\text{C}$  to 150°C and recommended operating conditions, VS = 4.75 to 30 V,  $f_{PWM} < 30 \text{ kHz}$  (unless otherwise noted)

|                     | PARAMETER                                          | TEST CONDITIONS                    | MIN | TYP | MAX              | UNIT |

|---------------------|----------------------------------------------------|------------------------------------|-----|-----|------------------|------|

|                     | Undervoltage shutdown level, UV = OFF              | When coming from higher VS voltage | 4.5 |     | 4.75             | V    |

| $V_{VSUV}$          | Recovery level form Undervoltage shutdown, UV = ON | Min. VS for device startup         | 4.6 |     | 4.85             | ٧    |

| Lhie                | Overvoltage hysteresis                             |                                    | 1.2 |     | 1.8              | V    |

| Hys                 | Under voltage hysteresis                           |                                    | 50  |     | 300              | mV   |

| t <sub>VS,SHD</sub> | Filter time for voltage shutdown                   |                                    | 5   |     | 6                | μs   |

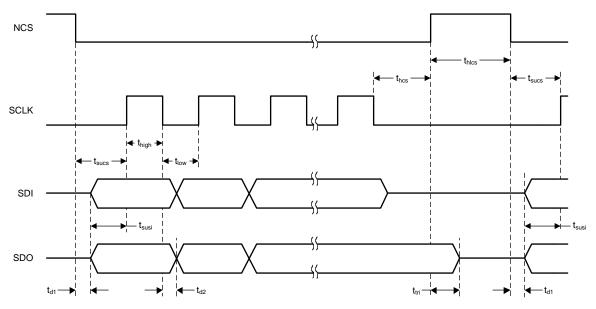

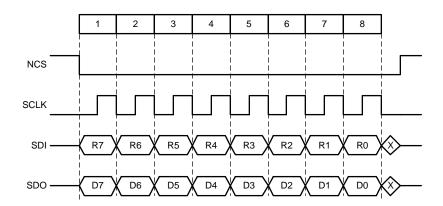

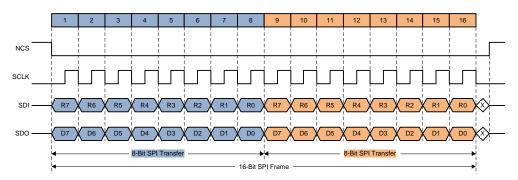

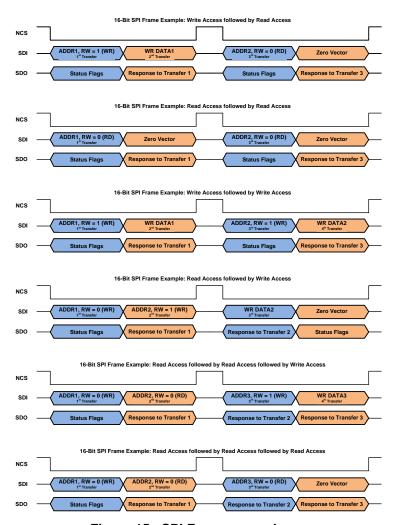

| Serial Peri         | ipheral Interface Timing                           |                                    | ·   |     |                  |      |

| f <sub>SPI</sub>    | SPI clock (SCLK) frequency                         |                                    |     |     | 4 <sup>(8)</sup> | MHz  |

| T <sub>SPI</sub>    | SPI clock period                                   |                                    | 250 |     |                  | ns   |

| t <sub>high</sub>   | High time: SCLK logic high duration                | 90                                 |     |     | ns               |      |

| t <sub>low</sub>    | Low time: SCLK logic low duration                  |                                    | 90  |     |                  | ns   |

| t <sub>sMCUs</sub>  | Setup time NCS: time between falling edg           | ge of NCS and rising edge of SCLK  | 90  |     |                  | ns   |

| t <sub>d1</sub>     | Delay time: time delay from falling edge of        | of NCS to data valid at SDO        |     |     | 60               | ns   |

| t <sub>susi</sub>   | Setup time at SDI: setup time of SDI befo          | ore the rising edge of SCLK        | 30  |     |                  | ns   |

| t <sub>d2</sub>     | Delay time: time delay from falling edge of        | 0                                  |     | 45  | ns               |      |

| t <sub>hcs</sub>    | Hold time: time between the falling edge of        | 45                                 |     |     | ns               |      |

| t <sub>hlcs</sub>   | SPI transfer inactive time: time between to        | 250                                |     |     | ns               |      |

| t <sub>tri</sub>    | 3-state delay time: time between rising ed         |                                    |     | 15  | ns               |      |

|                     |                                                    |                                    |     |     |                  |      |

## (8) MAX SPI clock tolerance is ± 10%.

Figure 2. SPI Timing Parameters

8

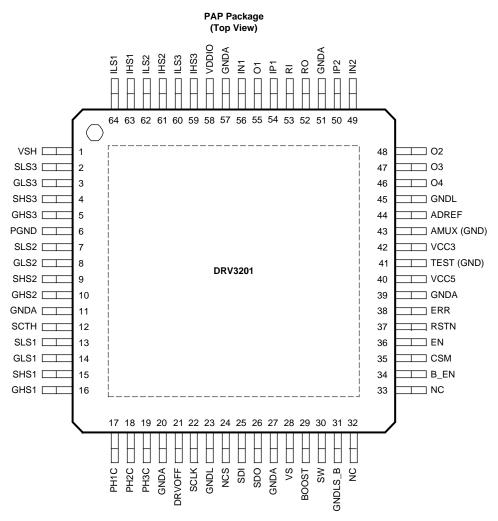

#### PIN FUNCTIONS

Figure 3. Pin Assignment (HTQFP-64 Package)

#### **PIN FUNCTIONS**

| PIN TYPE |       | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                             |  |  |  |

|----------|-------|---------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | E NO. |                     |                                                                                                         |  |  |  |

| VSH      | 1     | HVI_A               | Sense high-side, sensing VS connection of the external power MOSFETs for VDS monitoring.                |  |  |  |

| SLS3     | 2     | PWR                 | Source low-side 3, connected to external power MOSFET for gate discharge and VDS monitoring.            |  |  |  |

| GLS3     | 3     | PWR                 | Gate low-side 3, connected to gate of external power MOSFET.                                            |  |  |  |

| SHS3     | 4     | PWR                 | Source high-side 3, connected to external power MOSFET for gate discharge and VDS monitoring.           |  |  |  |

| GHS3     | 5     | PWR                 | Gate high-side 3, connected to gate of external power MOSFET.                                           |  |  |  |

| PGND     | 6     | GND                 | Sense low-side (ground), sensing ground connection of the external power MOSFETs for phase comparators. |  |  |  |

| SLS2     | 7     | PWR                 | Source low-side 2, connected to external power MOSFET for gate discharge and VDS monitoring.            |  |  |  |

| GLS2     | 8     | PWR                 | Gate low-side 2, connected to gate of external power MOSFET.                                            |  |  |  |

| SHS2     | 9     | PWR                 | Source high-side 2, connected to external power MOSFET gate discharge and VDS monitoring.               |  |  |  |

| GHS2     | 10    | PWR                 | Gate high-side 2, connected to gate of external power MOSFET.                                           |  |  |  |

<sup>(1)</sup> Description of pin type: GND = Ground, HVI\_A = High-Voltage Input Analog, HVI\_D = High-Voltage Input Digital, LVI\_A = Low-Voltage Input Analog, LVO\_A = Low-Voltage Output Analog, LVO\_D = Low-Voltage Output Digital, NC = NoConnect, PWR = Power Output, Supply = Supply Input.

# **PIN FUNCTIONS (continued)**

| PIN           | 1   | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                        |  |

|---------------|-----|---------------------|--------------------------------------------------------------------------------------------------------------------|--|

| NAME          | NO. |                     |                                                                                                                    |  |

| GNDA          | 11  | GND                 | Analog ground                                                                                                      |  |

| SCTH          | 12  | HVI_A               | Short circuit threshold, reference input voltage for VDS monitoring.                                               |  |

| SLS1          | 13  | PWR                 | Source low-side 1, connected to external power MOSFET for gate discharge and VDS monitoring.                       |  |

| GLS1          | 14  | PWR                 | Gate low-side 1, connected to gate of external power MOSFET.                                                       |  |

| SHS1          | 15  | PWR                 | Source high-side 1, connected to external power MOS transistor for gate discharge and VDS monitoring.              |  |

| GHS1          | 16  | PWR                 | Gate high-side 1, connected to gate of external power MOS transistor.                                              |  |

| PH1C          | 17  | LVO_D               | Phase comparator output1                                                                                           |  |

| PH2C          | 18  | LVO_D               | Phase comparator output2                                                                                           |  |

| PH3C          | 19  | LVO_D               | Phase comparator output3                                                                                           |  |

| GNDA          | 20  | GND                 | Analog ground                                                                                                      |  |

| DRVOFF        | 21  | HVI_D               | Driver OFF (high active), secondary bridge driver disable                                                          |  |

| SCLK          | 22  | HVI_D               | SPI clock                                                                                                          |  |

| GNDL          | 23  | GND                 | Logic ground                                                                                                       |  |

| NCS           | 24  | HVI_D               | SPI chip select                                                                                                    |  |

| SDI           | 25  | HVI_D               | SPI data input                                                                                                     |  |

| SDO           | 26  | LVO_D               | SPI data output                                                                                                    |  |

| GNDA          | 27  | GND                 | Analog ground                                                                                                      |  |

| VS            | 28  | Supply              | Power supply voltage                                                                                               |  |

| BOOST         | 29  | Supply              | Boost output voltage, used as supply for the gate-drivers.                                                         |  |

| SW            | 30  | PWR                 | Boost converter switching node connected to external coil and external diode.                                      |  |

| GNDLS_B       | 31  | GND                 | Boost GND to set current limit. Boost switching current goes through this pin via exterior resistor to GND.        |  |

| NC            | 32  | NC                  | NC pin, connected to GND during normal application.                                                                |  |

| NC            | 33  | NC                  | NC pin, connected to GND during normal application.                                                                |  |

| B_EN          | 34  | HVI_D               | Boost enable. Enable boost operation or disable during e.g. sensitive measurement.                                 |  |

| CSM           | 35  | HVI_D               | Configurable safety mode (high active), defines the level of safety.                                               |  |

| EN            | 36  | HVI_D               | Enable (high active) of the device                                                                                 |  |

| RSTN          | 37  | HVI_D               | Reset (low active)                                                                                                 |  |

| ERR           | 38  | LVO_D               | Error (low active). Error pin to indicate detected error.                                                          |  |

| GNDA          | 39  | GND                 | Ground analog                                                                                                      |  |

| VCC5          | 40  | LVO_A               | VCC5 regulator, for internal use only. Recommended external decoupling capacitance: 4.7 nF. External load < 100 μA |  |

| TEST          | 41  | HVI_A               | TEST mode input, connected to GND during normal application.                                                       |  |

| VCC3          | 42  | LVO_A               | VCC3 regulator, for internal use only. Recommended external decoupling capacitance: 4.7 nF. External load < 100 μA |  |

| AMUX<br>(GND) | 43  | LVO_A               | Analog TEST output MUX, connected to GND during normal application.                                                |  |

| ADREF         | 44  | LVI_A               | ADC reference of MCU, used as maximum voltage clamp for O1-O4.                                                     |  |

| GNDL          | 45  | GND                 | Logic ground                                                                                                       |  |

| O4            | 46  | LVO_A               | Output second stage current sense amplifier 2                                                                      |  |

| O3            | 47  | LVO_A               | Output second stage current sense amplifier 1                                                                      |  |

| 02            | 48  | LVO_AO              | Output first stage current sense amplifier 2                                                                       |  |

| IN2           | 49  | HVI_A               | Current sense input N 2                                                                                            |  |

| IP2           | 50  | HVI_A               | Current sense input P 2                                                                                            |  |

| GNDA          | 51  | GND                 | Ground analog                                                                                                      |  |

| RO            | 52  | LVO_A               | Current sense reference output for the shift voltage.                                                              |  |

| RI            | 53  | HVI_A               | Current sense reference output for the shift voltage.                                                              |  |

| NI            | აა  | ⊓vI_A               | Current sense reference input for the shift voltage.                                                               |  |

10

# **PIN FUNCTIONS (continued)**

| PIN TYPE <sup>(1)</sup> |     | TYPE <sup>(1)</sup> | DESCRIPTION                                                               |  |

|-------------------------|-----|---------------------|---------------------------------------------------------------------------|--|

| NAME                    | NO. |                     |                                                                           |  |

| IP1                     | 54  | HVI_A               | Current sense input P 1                                                   |  |

| O1                      | 55  | LVO_A               | Output first stage current sense amplifier 1                              |  |

| IN1                     | 56  | HVI_A               | Current sense input N 1                                                   |  |

| GNDA                    | 57  | GND                 | Ground analog                                                             |  |

| VDDIO                   | 58  | Supply              | IO supply voltage, defines the interface voltage of digital I/O e.g. SPI. |  |

| IHS3                    | 59  | HVI_D               | Input HS 3, digit input to drive the HS3                                  |  |

| ILS3                    | 60  | HVI_D               | Input LS 3, digit input to drive the LS3                                  |  |

| IHS2                    | 61  | HVI_D               | Input HS 2, digit input to drive the HS2                                  |  |

| ILS2                    | 62  | HVI_D               | Input LS 2, digit input to drive the LS2                                  |  |

| IHS1                    | 63  | HVI_D               | nput HS 1, digit input to drive the HS1                                   |  |

| ILS1                    | 64  | HVI_D               | Input LS 1, digit input to drive the LS1                                  |  |

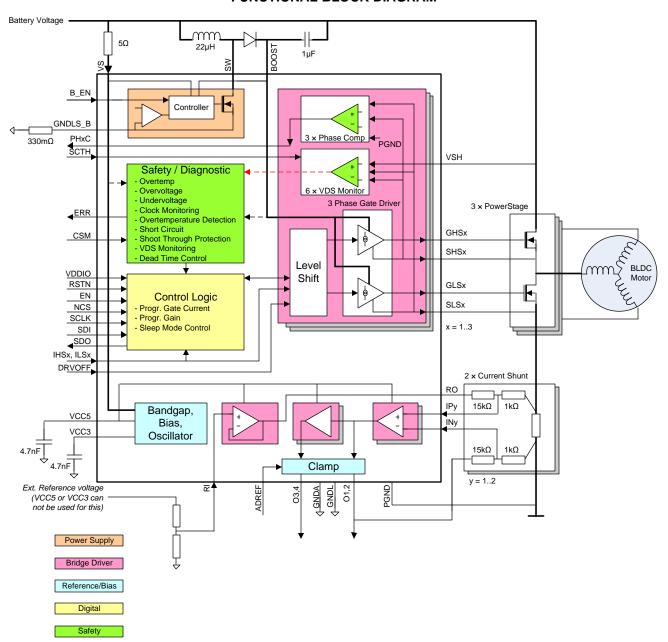

## **FUNCTIONAL BLOCK DIAGRAM**

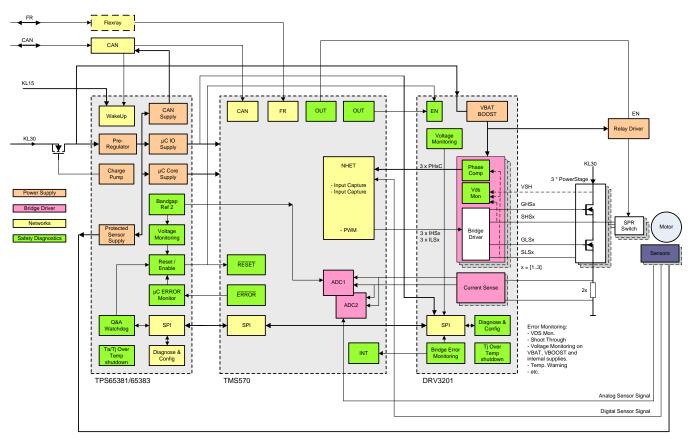

Figure 4. DRV3201-Q1 Functional Block Diagram

#### **DETAILED DESCRIPTION**

The DRV3201-Q1 is designed to control 3 phase brushless DC motors in automotive applications using pulse width modulation. Three high-side and three low-side gate-drivers can be switched individually with low propagation delay. The input logic prevents simultaneous activation of high and low-side driver of the same channel. A configuration and status register can be accessed through the SPI communication interface.

#### SUPPLY CONCEPT

The battery voltage functional operation range for the DRV3201-Q1 is between 4.85 V and 30 V. The DRV3201-Q1 operates with either 3.3 V or 5 V MCUs, which can be achieved by connecting the IO voltage of the MCU to the VDD\_IO pin of the DRV3201-Q1, and by connecting the ADC reference voltage of the MCU to the ADREF pin of the DRV3201-Q1. All digital outputs are related to VDDIO, and all analog outputs are related (clamped) to ADREF. All digital inputs are related to the internal supply VCC3, except the EN pin. The gate-drivers for the external power FETs operate even during battery voltage drops down to 4.75V when coming from full functional battery voltage range. For supply voltage falling below 4.75 V, the gates of the external FETs are pulled down actively. For supply voltage below 3 V, these gates are pulled down semi-actively. The minimum start-up battery voltage for the gate-drivers and the internal logic is 4.85 V.

Coming from full functional battery voltage range (that is, between 4.85 V and 30 V) the internal logic, including the SPI interface, operates even during battery voltage drops down to 3 V. When the battery drops below 3 V, the DRV3201-Q1 triggers a complete internal reset, clearing all internal status bits and registers. Also, the SPI communication to the MCU is disabled when the DRV3201-Q1 logic is put in reset.

The VCC5 is an internal supply for the current sense amplifiers and other internal analog circuitry. The VCC5 pin needs to be externally decoupled with a typical 4.7 nF capacitance. The VCC5 has an internal current limit to avoid any internal damage due to an external short-to-ground on the VCC5 pin.

The VCC3 is an internal supply for the internal logic. The VCC3 pin needs to be externally decoupled with a typical 4.7 nF capacitance. Since the VCC3 is supplied from the VCC5 regulator, its output is current limited by the VCC5 current limit so any internal damage is avoided in case of an external short-to-ground on the VCC3 pin. In case of a short-to-ground on either the VCC5 pin or the VCC3 pin, the internal logic is put in reset, which is detectable by the MCU because of disabled SPI communication. In this situation it is strongly recommended that the MCU takes necessary action to bring down the EN pin and shut off the DRV3201-Q1 to avoid VCC5 and/or VCC3 overloading for too long.

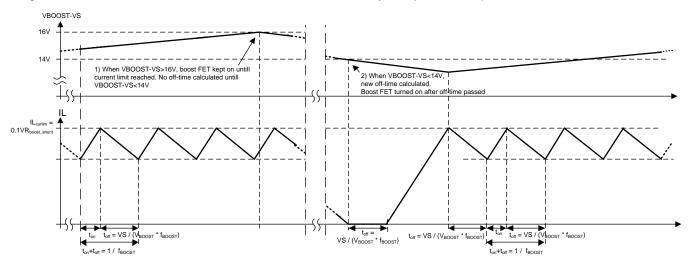

## **Boost Converter**

The boost converter is configured to supply an add-on voltage to the supply voltage. The boost converter requires an external inductance, capacitor, Schottky-diode, and a series resistance in its ground for current sensing. Both the high-side and the low-side gate-drivers are supplied from the boost converter. This allows the DRV3201-Q1 to achieve full-range gate-source driving voltage for all external power FETs even at battery voltage down to 4.75 V. The boost converter has a separate B\_EN pin to enable/disable. When the device is put in sleep mode, the boost converter cannot be enabled.

#### Sleep Mode, Active Mode

The EN (Enable) pin puts the device into sleep mode, in which it consumes less than 35  $\mu$ A. At the falling edge on the EN pin, after a typical 6  $\mu$ s deglitch time, the gates of the external power FETs are actively pulled low by the gate-drivers. Afterwards (min 20  $\mu$ s, max 35  $\mu$ s later) the internal supplies VCC5, VCC3, the boost converter, and the current sense amplifiers are switched off and the gates of the external power FETs are pulled low with a semi-active pulldown resistor (see Semi-Active Pull-Down Resistor). The internal logic is put in reset state, and all internal registers are cleared. No diagnostic information is available during sleep mode. When putting the device into Sleep Mode, the RSTN pin must be kept high. Once the device is in Sleep Mode (100  $\mu$ s after EN has been set low), the RSTN pin can be set low without affecting the Sleep Mode.

A rising edge on the EN pin puts the device in active mode after typically 3 ms power-up time. In active mode, the supplies VCC5 and VCC3 are present, and the boost converter can be enabled or disabled with the B\_EN pin. Since all internal registers are cleared in sleep mode, the MCU must program the DRV3201-Q1 in the desired settings after each wake-up from sleep mode to active mode.

## **DIGITAL INPUT, OUTPUT PINS**

All digital input pins (marked HVI\_D in terminal function table), except the EN pin, have a threshold voltage related to the internal VCC3 supply. Therefore, the state of these input pins is effective regardless of whether the VDDIO level is out of limits. These digital input pins have a fail-safe ESD structure with only a reverse diode path to ground, and no reverse diode path to any supply voltage. Depending on the function, these input pins have an internal passive pulldown or pullup. All digital output pins (marked LVO\_D) have a push-pull stage between VDDIO and ground. Therefore, the logic high-levels are related to VDDIO.

#### RESET

The DRV3201-Q1 can be reset by switching the RSTN to low. When RSTN is low, all status bits and register settings are cleared, the boost converter and the current sense amplifiers are off, and the gate-driver outputs are actively pulled low with the maximum setting for the sink current, hence turning off the external power FETs. The internal supplies VCC3 and VCC5 are still active when RSTN is forced low. The input high and low thresholds of RSTN are related to VCC3, and therefore independent of VDDIO, hence the state of the RSTN pin is effective regardless of whether the VDDIO level is out of limits. Once the RSTN pin has been set low, the device cannot enter Sleep Mode.

### **GATE-DRIVERS**

The DRV3201-Q1 has three high-side and low-side gate-drivers. Each high-side and low-side gate-driver contains a programmable sourcing and sinking current to charge and discharge the gate of the external power FETs.

The digital logic prevents the simultaneous activation of high and low-side gate-driver of one power-stage. If a command from the MCU for simultaneous activation is detected, the failure is flagged in the status register.

## **Gate-Driver Slope Control**

The DRV3201-Q1 has been designed to support adaptive slope control by programmable sink and source currents to charge and discharge the gates of the external power FETs. Table 1 gives the slope registers which are supported to program the sink and source currents of the gate-drivers.

**Table 1. Slope Configuration Registers**

| Affected Gate-Drivers | Register                        | Slope        | Current Range | Number of steps |

|-----------------------|---------------------------------|--------------|---------------|-----------------|

| HS1 and HS2           | HS1/2 Slope Register (CURR0)    | Rising Edge  | 140mA–1A      | 8               |

| HS1 and HS2           | HS1/2 Slope Register (CURR0)    | Falling Edge | 140mA–1A      | 8               |

| LS1 and LS2           | LS1/2 Slope Register<br>(CURR1) | Rising Edge  | 140mA–1A      | 8               |

| LS1 and LS2           | LS1/2 Slope Register<br>(CURR1) | Falling Edge | 140mA–1A      | 8               |

| HS3                   | HS3 Slope Register<br>(CURR2)   | Rising Edge  | 140mA-1A      | 8               |

| HS3                   | HS3 Slope Register<br>(CURR2)   | Falling Edge | 140mA-1A      | 8               |

| LS3                   | LS3 Slope Register<br>(CURR3)   | Rising Edge  | 140mA-1A      | 8               |

| LS3                   | LS3 Slope Register<br>(CURR3)   | Falling Edge | 140mA-1A      | 8               |

www.ti.com

To reduce the risk of a distorted slope due to changing the slope setting, a new slope setting for a rising edge only becomes active after the next falling edge of the affected gate-driver and vice versa for the falling edge. This does not apply directly after wake-up to active mode. As long as no low-side or high-side gate-driver has been switched after wake-up to active mode, the programmed slope settings are active immediately.

To allow a high scalability of the output FETs and switching speed, there is also one general reduced current mode setting, in which all gate charge/discharge currents are 25% of the programmed settings. Furthermore it is possible to set the drivers to switching mode by setting bit 7 in configuration register 1 (CFG1) to 1. In this setting the drivers are not current limited and limiting the switching speed can be done externally with resistors in the gate lines. In this mode it is strongly recommended to set the slope registers (CURR0–3) to 0x3F to get the maximum current setting and have the current limiting only from the external resistors.

## **Direct Mode (6 x Inputs Operation)**

The direct mode is the default operation mode after each wake-up from sleep mode to active mode. In direct mode, all gate-drivers can be controlled individually via the digital input pins IHSx/ILSx.

## **PWM Mode (3 x Inputs Operation)**

Alternatively, the gate-drivers can be operated in PWM mode by setting bit 6 in Configuration Register 1 (CFG1) to 1. PWM Mode controls all six gate-drivers with only three PWM signals. The valid controls in PWM mode are the IHSx inputs. The low-side controls are derived from the corresponding IHSx signals while all safety features remain active. In PWM mode, the ILSx inputs may be used as SPI-readable general purpose inputs.

#### **DRVOFF Gate-Driver Shutoff**

When the DRVOFF pin is high, the gate-driver outputs are actively pulled low with the programmed setting for the sink current to turn off the external power FETs. Meanwhile, the IHSx/ILSx inputs can be read back through SPI. The VDS comparators, and flag errors (if VDS is too high) are enabled which can be used to ensure functionality of these blocks. The boost converter, the current sense amplifiers, and the internal VCC3 and VCC5 supplies are still active when DRVOFF is forced low. The input high and low thresholds of DRVOFF are related to VCC3, and are independent of VDDIO, so the state of the DRVOFF pin is effective regardless of whether the VDDIO level is out of limits.

#### **Active Pulldown**

When the external power FETs need to be turned off and the DRV3201-Q1 is in active mode (either by normal control signal, DRVOFF signal, RSTN signal or by any error handling), the gate-drivers provide a low-ohmic active pulldown. Once the gate-source voltage of the power FETs reaches less than 2 V, the programmed current sink behavior changes into an Rdson behavior to increase the pulldown strength.

## Semi-Active Pull-Down Resistor

Each high and low-side driver has a typical 500 k $\Omega$  resistor from gate to source acting as passive pulldown to keep the external power FET turned off in unsupplied conditions. In addition a semi-active pulldown circuit is reducing the gate impedance at a typical voltage of 2 V to about 7 k $\Omega$ . This semi-active pulldown circuit is turned off in normal operation to avoid higher DC current consumption for the gate-driver.

## **Gate-Driver Shutoff Paths**

Table 2 summarizes the possible states of the EN, RSTN and DRVOFF pins and the effect on the gate-drivers.

Copyright © 2012–2013, Texas Instruments Incorporated

#### Table 2. Gate-Driver Shutoff Paths

| EN                   | RSTN | DRVOF<br>F | Any Non-Masked<br>Error | Gate-Driver Shutoff                                                                            | Logic                                                          |

|----------------------|------|------------|-------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Unpowered device (1) |      |            | evice <sup>(1)</sup>    | Semi-active pulldown + passive pulldown                                                        |                                                                |