# 155Mbps to 2.5Gbps Burst-Mode Laser Driver

## **General Description**

The MAX3643 burst-mode laser driver provides bias and modulation current drive for PON burst-mode ONT applications. It is specifically designed for use with a low-cost external controller for the APC (and if desired, AMC) loop. A high-speed differential burst-enable input enables the driver to switch the laser from a dark (output off) condition to full on-condition in less than 2ns. When BEN is inactive, typical modulation and bias currents are 5µA each.

Laser modulation current can be set from 10mA to 85mA and bias current can be set from 1mA to 70mA using the MODSET and BIASSET inputs. A sample-andhold circuit is provided to capture the monitor diode output during short PON bursts, if needed, and the BEN high-speed signal is mirrored on an LVCMOS output to be used by the controller operating the APC/AMC loop.

The MAX3643 burst-mode laser driver is packaged in a 4mm x 4mm, 24-pin thin QFN package. It operates from -40°C to +85°C.

## **Applications**

A/B/G/XGPON ONT Modules Up to 2.5Gbps 1.25Gbps IEEE EPON ONT Modules

#### **Features**

- 10mA to 85mA Modulation Current

- ♦ 1mA to 70mA Bias Current

- ♦ Monitor Diode Sample and Hold

- ◆ 45ps Output Transition Time

- ♦ 2ns Turn-On/-Off Time

- ♦ Reference Voltage Generator

- **♦ LVPECL High-Speed Inputs (Data, Burst Enable)**

## **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX3643ETG  | -40°C to +85°C | 24 TQFN-EP* |

| MAX3643ETG+ | -40°C to +85°C | 24 TQFN-EP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Pin Configuration appears at end of data sheet.

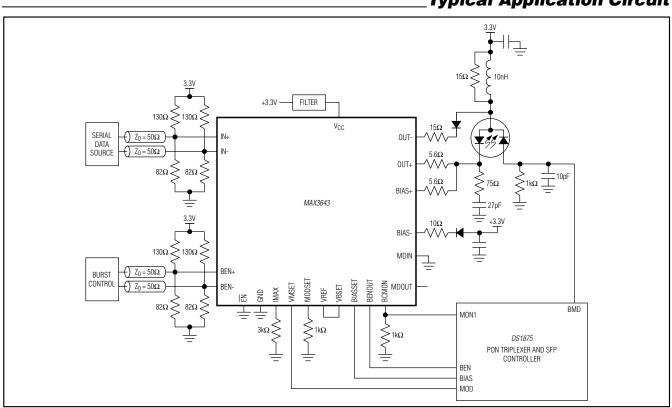

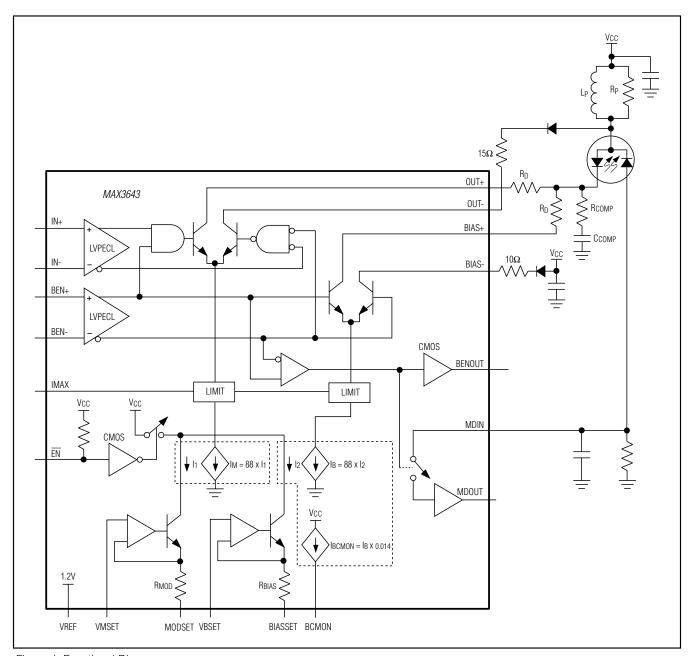

## Typical Application Circuit

<sup>\*</sup>EP = Exposed paddle.

# 155Mbps to 2.5Gbps Burst-Mode Laser Driver

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage V <sub>CC</sub> 0.5V to +4.0V Current into BIAS-, BIAS+, OUT-, OUT+20mA to +150mA Voltage at VMSET, VBSET, IN+, IN-, BEN+, BEN-, EN, MDIN, | Operating Temperature Range40°C to +85°C Storage Temperature Range55°C to +150°C Lead Temperature (soldering, 10s)+300°C |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| MDOUT, BENOUT, BCMON                                                                                                                                      | Soldering Temperature (reflow)                                                                                           |

| Voltage at MODSET, BIASSET, VREF, IMAX0.5V to +3.0V                                                                                                       | Lead(Pb)-free+260°C                                                                                                      |

| Voltage at OUT-, OUT+, BIAS-, BIAS++0.3V to (VCC + 0.5V)                                                                                                  | Containing lead(Pb)+240°C                                                                                                |

| Continuous Power Dissipation (T <sub>A</sub> = +85°C)                                                                                                     |                                                                                                                          |

| 24-Pin TQFN, Multilayer Board                                                                                                                             |                                                                                                                          |

| (derate 27.8mW/°C above +85°C)1807mW                                                                                                                      |                                                                                                                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **OPERATING CONDITIONS**

| PARAMETER               | SYMBOL | CONDITIONS | MIN   | TYP | MAX  | UNITS |

|-------------------------|--------|------------|-------|-----|------|-------|

| Supply Turn-On Time     |        | 10% to 90% | 0.001 |     | 1000 | ms    |

| Ambient Temperature     |        |            | -40   |     | +85  | °C    |

| Data Rate               |        |            |       |     | 2500 | Mbps  |

| Voltage at VMSET, VBSET |        |            | 0     |     | 1.4  | V     |

| Voltage at BCMON        |        |            | 0     |     | 1.4  | V     |

| Voltage at MDIN         |        |            | 0     |     | 2.56 | V     |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 3.0V \text{ to } 3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}.$  Typical values are at  $V_{CC} = 3.3V, T_A = +25^{\circ}\text{C}, I_{BIAS} = 20\text{mA}, I_{MOD} = 30\text{mA}, unless otherwise noted.)$  (Note 1)

| PARAMETER                           | SYMBOL                                                    | CONDITIONS                                                                                       |                        | TYP                       | MAX                                      | UNITS             |

|-------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------|---------------------------|------------------------------------------|-------------------|

| Supply Current                      | Icc                                                       | Excluding laser bias and mode currents, max at I <sub>MOD</sub> = 85mA, I <sub>BIAS</sub> = 70mA |                        | 51                        | mA                                       |                   |

| I/O SPECIFICATIONS                  | •                                                         |                                                                                                  |                        |                           |                                          |                   |

| LVPECL Differential Input           | VIN                                                       | $V_{IN} = (V_{IN+}) - (V_{IN-})$                                                                 | 200                    |                           | 1600                                     | mV <sub>P-P</sub> |

| LVPECL Common-Mode Input<br>Voltage | V <sub>CM</sub>                                           |                                                                                                  | V <sub>CC</sub> - 1.49 | V <sub>CC</sub> -<br>1.32 | V <sub>CC</sub> -<br>V <sub>IN</sub> / 4 | V                 |

| LVCMOS Output High Voltage          |                                                           | I <sub>OH</sub> = -100μA                                                                         | V <sub>CC</sub> - 0.2  |                           |                                          | V                 |

| LVCMOS Output Low Voltage           |                                                           | I <sub>OL</sub> = 100µA                                                                          |                        |                           | 0.2                                      | V                 |

| BENOUT Propagation Delay            | T <sub>d</sub>                                            | C <sub>L</sub> = 20pF, from BEN zero crossing to 67%<br>CMOS level                               |                        | 30                        |                                          | ns                |

| LVCMOS Input Pullup                 |                                                           |                                                                                                  | 75                     |                           |                                          | kΩ                |

| LVCMOS Input Current                | V <sub>IN</sub> = 0V or V <sub>IN</sub> = V <sub>CC</sub> |                                                                                                  |                        |                           | 50                                       | μΑ                |

| LVCMOS Input High Voltage           |                                                           |                                                                                                  |                        |                           | Vcc                                      | V                 |

| LVCMOS Input Low Voltage            | LVCMOS Input Low Voltage                                  |                                                                                                  | 0.2                    |                           | 0.8                                      | V                 |

| BIAS GENERATOR SPECIFICAT           | TIONS                                                     |                                                                                                  |                        |                           |                                          |                   |

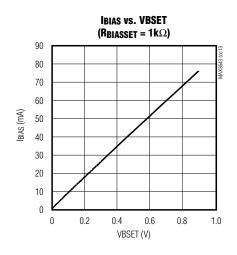

| Bias Current Range                  | IBIAS                                                     | V <sub>BIAS+</sub> , V <sub>BIAS-</sub> ≥ 0.6V                                                   | 1                      |                           | 70                                       | mA                |

| Bias Current, Burst Off             | IBIAS, OFF                                                | BEN = low or EN = high                                                                           |                        | 5                         | 50                                       | μΑ                |

|                                     |                                                           | 1mA ≤ I <sub>BIAS</sub> < 2mA, VBSET = VREF                                                      |                        | 88                        |                                          |                   |

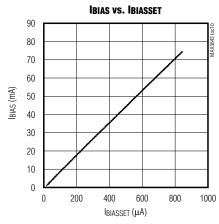

| BIASSET Current Gain                | G <sub>BIAS</sub>                                         | 2mA ≤ I <sub>BIAS</sub> < 10mA, VBSET = VREF                                                     | 70                     | 88                        | 110                                      | mA/mA             |

|                                     |                                                           | 10mA ≤ I <sub>BIAS</sub> < 70mA, VBSET = VREF                                                    | 82.5                   | 88                        | 94.5                                     |                   |

## **ELECTRICAL CHARACTERISTICS (continued)**

( $V_{CC} = 3.0V$  to 3.6V,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC} = 3.3V$ ,  $T_A = +25^{\circ}C$ ,  $I_{BIAS} = 20mA$ ,  $I_{MOD} = 30mA$ , unless otherwise noted.) (Note 1)

| PARAMETER SYMBO                |                  | CONDITIONS                                                  | MIN   | TYP | MAX   | UNITS    |  |

|--------------------------------|------------------|-------------------------------------------------------------|-------|-----|-------|----------|--|

| BIASSET Current Gain Stability |                  | 5mA ≤ I <sub>BIAS</sub> ≤ 70mA (Note 13)                    | -4.4  |     | +4.4  | %        |  |

| BIASSET Current Gain Linearity |                  | 5mA ≤ I <sub>BIAS</sub> ≤ 70mA (Note 14)                    | -3.75 |     | +3.75 | %        |  |

| Bias Current Overshoot         |                  | V <sub>CC</sub> turn-on/-off < 1s                           |       |     | 10    | %        |  |

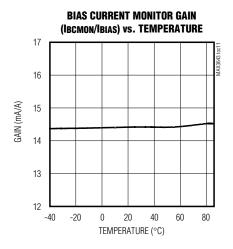

| Bias Current Monitor Gain      | G <sub>BSM</sub> | 2mA ≤ I <sub>BIAS</sub> ≤ 70mA, VBSET = VREF                | 11    | 14  | 17    | mA/A     |  |

| Bias Current Monitor Gain      |                  | 1mA ≤ I <sub>BIAS</sub> < 5mA                               |       | ±4  |       | 0/       |  |

| Stability                      |                  | 5mA ≤ I <sub>BIAS</sub> ≤ 70mA                              | -5    |     | +5    | %        |  |

| BIASSET Resistor               | RBIAS            |                                                             | 40    | 50  | 60    | Ω        |  |

| MODULATOR SPECIFICATIONS       |                  |                                                             |       |     |       |          |  |

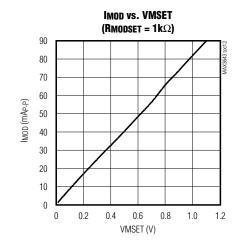

| Modulation Current Range       | IMOD             |                                                             | 10    |     | 85    | mA       |  |

| Modulation Current Off         | IMOD, OFF        | $BEN = low or \overline{EN} = high or V_{IN} = low$         |       | 5   | 120   | μΑ       |  |

|                                |                  | 10mA ≤ I <sub>MOD</sub> < 60mA                              | 0.6   |     |       | ,        |  |

| Instantaneous Voltage at OUT+  |                  | 60mA ≤ I <sub>MOD</sub> ≤ 85mA                              | 0.75  |     |       | V        |  |

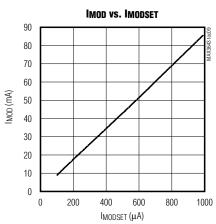

| MODSET Current Gain            | GMOD             | 10mA < I <sub>MOD</sub> < 85mA, VMSET = VREF                | 82.5  | 88  | 94.5  | mA/mA    |  |

| MODSET Current Gain Stability  | 02               | (Note 13)                                                   | -4.4  |     | +4.4  | %        |  |

| MODSET Current Gain Linearity  |                  | (Note 14)                                                   | -2.2  |     | +2.2  | %        |  |

| ,                              |                  | IBIASSET = 0.15mA, IMODSET = 0.7mA                          |       | 0.5 |       |          |  |

| MODSET, BIASSET Gain           |                  | IMODSET = IBIASSET = 0.15mA                                 |       |     | 1.7   | <b>-</b> |  |

| Matching (Note 15)             |                  | IMODSET = IBIASSET = 0.4mA                                  |       |     | 1     | - %      |  |

|                                |                  | IMODSET = IBIASSET = 0.55mA                                 |       |     | 1     |          |  |

| Modulation Current Rise Time   | t <sub>R</sub>   | 20% to 80%                                                  |       | 45  | 85    | ps       |  |

| Modulation Current Fall Time   | tF               | 20% to 80%                                                  |       | 45  | 85    | ps       |  |

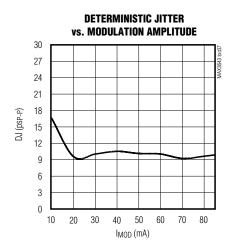

| Deterministic Jitter           |                  | (Note 3)                                                    |       | 17  | 45    | psp-p    |  |

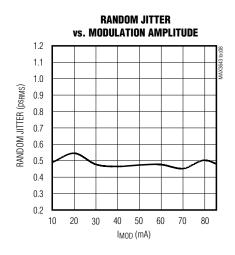

| Random Jitter                  |                  | (Note 4)                                                    |       | 0.8 | 1.4   | psRMS    |  |

| MODSET Resistor                | RMOD             |                                                             | 40    | 50  | 60    | Ω        |  |

| MODSET, BIASSET OPERATION      |                  | ER SPECIFICATIONS                                           |       |     |       |          |  |

| MODSET, BIASSET Voltage        |                  |                                                             | 0.005 |     |       | .,       |  |

| Range                          |                  |                                                             | 0.005 |     | 1.4   | V        |  |

| Voltage Error                  |                  | (Note 5)                                                    |       |     | ±5    | mV       |  |

| Input Leakage                  |                  | VMSET and VBSET pins                                        |       | 0.1 | 1.5   | μΑ       |  |

| TURN-OFF/-ON SPECIFICATIONS    | 3                |                                                             |       |     |       |          |  |

| Burst-Enable Time              |                  | (Notes 2, 6, 7)                                             |       |     | 2.3   | ns       |  |

| Burst-Disable Time             |                  | (Notes 2, 6, 8)                                             |       |     | 2.0   | ns       |  |

| SAMPLE/HOLD SPECIFICATION      | IS               |                                                             |       |     |       |          |  |

| MDIN Voltage Range             |                  |                                                             | 0.05  |     | 2.56  | V        |  |

| MDOUT Settling                 |                  | Relative to final value at 3µs, C <sub>L</sub> < 20pF       |       |     | ±1    | mV       |  |

| Sample/Hold Droop              |                  | After 100µs (Note 9)                                        |       |     | ±2.56 | mV       |  |

|                                |                  | V <sub>CC</sub> turn-on/-off < 1s, I <sub>BIAS</sub> ≥ 20mA |       |     | 10    | %        |  |

| Bias Current Overshoot         |                  | I <sub>BIAS</sub> < 20mA                                    |       |     | 2     | mA       |  |

# 155Mbps to 2.5Gbps Burst-Mode Laser Driver

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 3.0 \text{V to } 3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values are at } V_{CC} = 3.3 \text{V}, T_A = +25 ^{\circ}\text{C}, I_{BIAS} = 20 \text{mA}, I_{MOD} = 30 \text{mA}, unless otherwise noted.})$  (Note 1)

| PARAMETER                                | SYMBOL                                   | CONDITIONS MIN TY                                                      |       | TYP   | MAX   | UNITS |  |

|------------------------------------------|------------------------------------------|------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Sampling Error                           |                                          | Final value measured after 10µs<br>(MDOUT - MDIN), burst width > 576ns |       | 3     | ±14   | mV    |  |

| BANDGAP VOLTAGE REFEREN                  | BANDGAP VOLTAGE REFERENCE SPECIFICATIONS |                                                                        |       |       |       |       |  |

| VREF Output                              |                                          | $R_L > 10 k\Omega$ , $C_L < 50 pF$                                     | 1.175 | 1.235 | 1.295 | V     |  |

| MODULATION/BIAS CURRENT D                | ISABLE                                   |                                                                        |       |       |       |       |  |

| Enable Time                              |                                          | 5mA < I <sub>BIAS</sub> , 10mA < I <sub>MOD</sub> (Note 10)            |       |       | 5.5   | μs    |  |

| Disable Time                             |                                          | (Notes 2, 11)                                                          |       |       | 375   | ns    |  |

| R <sub>IMAX</sub> Range                  |                                          |                                                                        | 3     |       | 15    | kΩ    |  |

|                                          | IBIAS+IMOD                               | $R_{IMAX} = 3k\Omega$                                                  | 155   |       |       |       |  |

| Current Limit (Tested with IBIAS = IMOD) |                                          | $R_{IMAX} = 5k\Omega$                                                  | 100   |       | 150   | mA    |  |

|                                          |                                          | $R_{IMAX} = 10k\Omega$                                                 | 50    |       | 75    |       |  |

| OPTICAL EVALUATION                       |                                          |                                                                        |       |       |       |       |  |

|                                          |                                          | 155.52Mbps                                                             |       | 49    |       |       |  |

| Eye Margin (Note 12)                     |                                          | 622.08Mbps                                                             | 45    |       | %     |       |  |

|                                          |                                          | 1.24416Gbps                                                            | 38    |       |       |       |  |

|                                          |                                          | 2.48832Gbps                                                            |       | 18    | ·     |       |  |

- **Note 1:** Electrical specifications are production tested at TA = +25°C. Specifications over the entire operating temperature range are guaranteed by design and characterization. Typical specifications are at TA = +25°C, 3.3V.

- **Note 2:** For  $10\text{mA} \le I_{MOD} \le 85\text{mA}$  and  $4\text{mA} \le I_{BIAS} \le 70\text{mA}$ .

- **Note 3:** Deterministic jitter measured with a continuous pattern of 2<sup>7</sup>-1 PRBS, 80 ones, 2<sup>7</sup>-1 PRBS, 80 zeros at 1.25Gbps, and both LVPECL inputs terminated by the network shown in Figure 3.

- Note 4: Random jitter, rise time, fall time measured with 0000011111 pattern at 1.25Gbps.

- **Note 5:** Voltage difference between VMSET and MODSET or VBSET and BIASSET excluding IR drops. The maximum operating voltage at VMSET or VBSET must be less than 1.4V for proper operation.

- Note 6: Turn-on/-off time is when the BEN+/BEN- LVPECL inputs are used to control modulation and bias currents.

- **Note 7:** Burst-enable delay is measured between the time at which the rising edge of the differential burst-enable input reaches the midpoint, and the time at which the combined output currents (bias plus modulation) reach 90% of their final level.

- **Note 8:** Burst-disable delay is measured between the time at which the falling edge of the differential burst-enable input reaches the midpoint, and the time at which the combined output currents (bias plus modulation) fall below 10% of the bias-on current.

- Note 9: Droop measured with sample/hold output load of  $10M\Omega$ .

- Note 10: Enable delay is measured between the time at which the falling edge of the EN input reaches ≤ 0.8V, and the time at which the combined output currents (bias plus modulation) reach 90% of their final level.

- Note 11: Disable delay is measured between the time at which the rising edge of the EN input reaches ≥ 2V, and the time at which the combined output currents (bias plus modulation) fall below 10% of the bias-on current.

- Note 12: Excelight SLT2886-LR laser.

- Note 13: Current gain stability = [(Gain nominal Gain) / nominal Gain], nominal Gain at  $V_{CC} = 3.3V$ ,  $T_{A} = +25^{\circ}C$ .

- Note 14: Gain linearity =  $(\underline{Gainmax Gainmin})$ , Gainavg =  $\underline{Gainmax + Gainmin}$  $\underline{Gainavg}$  2

- Note 15: Gain matching = Gainmod / Gainbias Gainmodnom / Gainbiasnom , nominal at VCC = 3.3V, TA = +25°C.

## Typical Operating Characteristics

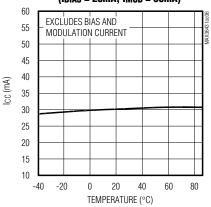

(Typical values are at  $V_{CC} = 3.3V$ ,  $T_A = +25^{\circ}C$ , data pattern =  $2^{7}$ -1 PRBS + 80 ones +  $2^{7}$ -1 PRBS + 80 zeros, unless otherwise noted.)

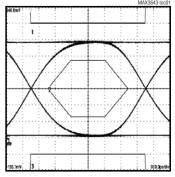

#### OPTICAL EYE DIAGRAM (155.52Mbps, 117MHz FILTER, PATTERN = 2<sup>23</sup> - 1 PRBS)

EXCELIGHT SLT2886-LR LASER AVERAGE OPTICAL POWER = -6dBm EXTINCTION RATIO = 15dB MASK MARGIN = 49%

#### OPTICAL EYE DIAGRAM (622.08Mbps, 467MHz FILTER, PATTERN = 2<sup>23</sup> - 1 PRBS)

EXCELIGHT SLT2886-LR LASER AVERAGE OPTICAL POWER = -6dBm EXTINCTION RATIO = 15dB MASK MARGIN = 45%

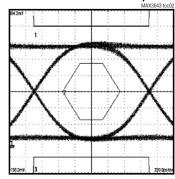

#### OPTICAL EYE DIAGRAM (1.24416Gbps, 933MHz FILTER, PATTERN = 2<sup>23</sup> - 1 PRBS)

EXCELIGHT SLT2886-LR LASER AVERAGE OPTICAL POWER = -6dBm EXTINCTION RATIO = 14dB MASK MARGIN = 38%

#### OPTICAL EYE DIAGRAM (2.48832Gbps, 2.3GHz FILTER, PATTERN = 2<sup>23</sup> - 1 PRBS)

EXCELIGHT SLT2886-LR LASER AVERAGE OPTICAL POWER = -6dBm EXTINCTION RATIO = 10dB MASK MARGIN = 18%

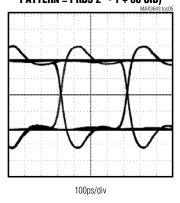

#### ELECTRICAL EYE DIAGRAM (2.5Gbps, I<sub>MOD</sub> = 30mA, PATTERN = PRBS 2<sup>7</sup> - 1 + 80 CID)

# SUPPLY CURRENT vs. TEMPERATURE (IBIAS = 20mA, IMOD = 30mA)

# 155Mbps to 2.5Gbps Burst-Mode Laser Driver

## Typical Operating Characteristics (continued)

(Typical values are at  $V_{CC} = 3.3V$ ,  $T_A = +25^{\circ}C$ , data pattern =  $2^{7}$ -1 PRBS + 80 ones +  $2^{7}$ -1 PRBS + 80 zeros, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(Typical values are at  $V_{CC} = 3.3V$ ,  $T_A = +25^{\circ}C$ , data pattern =  $2^{7}$ -1 PRBS + 80 ones +  $2^{7}$ -1 PRBS + 80 zeros, unless otherwise noted.)

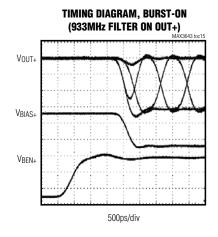

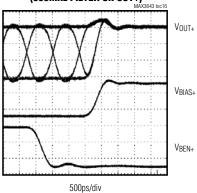

TIMING DIAGRAM, BURST-OFF (933MHz FILTER ON OUT+)

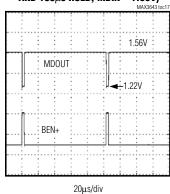

SAMPLE/HOLD (10M $\Omega$  Load, 2.8 $\mu$ s Sample and 100 $\mu$ s Hold, Mdin = 1.56V)

# 155Mbps to 2.5Gbps Burst-Mode Laser Driver

## **Pin Description**

| PIN    | NAME    | FUNCTION                                                                                                                                         |

|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|        |         |                                                                                                                                                  |

| 1      | VCCA    | Analog Supply Voltage                                                                                                                            |

| 2      | IN+     | Noninverted Data Input, LVPECL Compatible                                                                                                        |

| 3      | IN-     | Inverted Data Input, LVPECL Compatible                                                                                                           |

| 4      | Vccs    | Signal Supply Voltage                                                                                                                            |

| 5      | BEN+    | Noninverted Burst-Enable Input, LVPECL Compatible                                                                                                |

| 6      | BEN-    | Inverted Burst-Enable Input, LVPECL Compatible                                                                                                   |

| 7      | BENOUT  | Burst-Enable Output, LVCMOS. Signal replicates BEN input.                                                                                        |

| 8      | ĒN      | Enable Input LVCMOS. Active low enables BIAS± and OUT± outputs.                                                                                  |

| 9      | BCMON   | Bias Current Monitor. Current out of this pin develops a ground-referenced voltage across an external resistor proportional to the bias current. |

| 10     | IMAX    | Current-Limit Reference. Connect a resistor from IMAX to GND to set maximum IBIAS plus IMOD.                                                     |

| 11     | MDOUT   | Monitor Diode Out. Analog Output for sample/hold.                                                                                                |

| 12     | MDIN    | Monitor Diode In. Analog Input for sample/hold.                                                                                                  |

| 13     | BIAS-   | Connect BIAS- to V <sub>CC</sub> Through a 10Ω Resistor and Switching Diode                                                                      |

| 14     | BIAS+   | Laser Bias Current Output. Modulation current flows into this pin when BEN input is high.                                                        |

| 15, 18 | Vcco    | Output Supply Voltage                                                                                                                            |

| 16     | OUT+    | Laser Modulation Current Output. Modulation current flows into this pin when both BEN and IN inputs are high.                                    |

| 17     | OUT-    | Connect OUT- to Laser Diode Anode Through a 15Ω Resistor and Switching Diode                                                                     |

| 19     | GND     | Supply Ground. This pin must be connected to ground.                                                                                             |

| 20     | MODSET  | Modulation Current Set. Current from this pin to ground sets the laser modulation current.                                                       |

| 21     | VMSET   | MODSET Reference. A ground-referenced voltage at this point establishes the MODSET reference.                                                    |

| 22     | VREF    | Reference Voltage Output. May be used for VMSET, VBSET.                                                                                          |

| 23     | VBSET   | BIASSET Reference. A ground-referenced voltage at this point establishes the BIASSET reference.                                                  |

| 24     | BIASSET | Bias Current Set. Current from this pin to ground sets the laser bias current.                                                                   |

| _      | EP      | Exposed Paddle (Ground). The exposed pad must be soldered to the circuit board ground for proper thermal and electrical operation.               |

Figure 1. Functional Diagram

## **Detailed Description**

The MAX3643 laser driver includes a bias current generator, bias current monitor, modulation current generator, laser drive outputs, and monitor diode sample and hold. LVPECL-compatible inputs are provided for both high-speed data and burst enable. The high-speed burst-enable input signal is replicated on an LVCMOS output for use by the controller.

#### Laser Diode Modulation and Bias Current Generators

Laser diode modulation current amplitude is controlled by the current out of the MODSET pin, and bias current by the current out of the BIASSET pin, according to:

> IMOD = IMODSET x 88 IBIAS = IBIASSET x 88

A voltage source and two op amps are provided to enable IMODSET and IBIASSET to be set using either a resistor to ground or a current digital-to-analog converter (DAC). The high-impedance op amp reference input can be externally controlled, so that the modulation and bias currents can also be set using voltage DACs.

#### Laser Diode Modulation and Bias Current Limiter

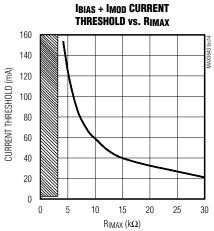

Typical laser diodes have an absolute maximum rating of 150mA. To reduce the possibility of laser damage, the modulation current and bias current are shut off if the sum I<sub>MOD</sub> + I<sub>BIAS</sub> attempts to exceed the limit set by R<sub>IMAX</sub>; see the *Typical Operating Characteristics*.

#### **Bias Current Monitor**

The laser diode bias current can be monitored by measuring the voltage across an external load resistor connected from BCMON to ground. For example, a  $1k\Omega$  resistor from BCMON to ground gives the following relationship:

$V_{BCMON} = I_{BIAS} \times G_{BSM} \times 1k\Omega$

The voltage at BCMON must be below 1.4V for proper operation.

#### **Output Drivers**

The modulation current ranges from 10mA to 85mA, as set by the current through MODSET. The laser modulation current output OUT+ is optimized to drive a  $15\Omega$  load, and must be DC-coupled. A series damping resistor, RD, provides impedance matching to the laser diode. The combined value of the series damping resistor and the laser diode equivalent series resistance

should be close to  $15\Omega$ . An RC shunt compensation network, RCOMP/CCOMP, connected between the laser diode cathode and ground should also be provided to reduce optical output aberrations and duty-cycle distortion caused by laser diode parasitic inductance. The values of RCOMP and CCOMP can be adjusted to match the laser diode and PCB layout characteristics for optimal optical eye performance (refer to Application Note 274: HFAN-02.0: Interfacing Maxim Laser Drivers with Laser Diodes). The OUT- pin is connected through a  $15\Omega$  resistor and switching diode to the laser diode anode. The switching diode at OUT- improves the optical output eye and burst-enable delay by better matching the laser diode characteristics.

For data rates greater than 1Gbps, a parallel RL peaking network, Rp/Lp, connected between the laser diode anode and V<sub>CC</sub> is recommended. This network creates a differential drive for the laser diode to improve rise/fall times and reduce jitter. The values of Rp and Lp are also adjusted to match the laser diode and PCB layout characteristics for optimal optical eye performance.

The bias current ranges from 1mA to 70mA, as set by the current through BIASSET. Current in the BIAS output switches at high speed when bursting; therefore, the BIAS+ pin should be connected directly through a resistor, equal to RD as determined above, to the laser cathode. The BIAS- pin is connected through a  $10\Omega$  resistor and switching diode to VCC.

When the BEN input is high, the laser driver sinks bias and modulation current according to the settings at MODSET and BIASSET. When the BEN input is low, the BIAS+ and OUT+ currents both shut off within 2ns. Note that when BEN is low, the bias current is shunted through the BIAS- output and the modulation current through the OUT- output.

#### **Monitor Diode Sample and Hold**

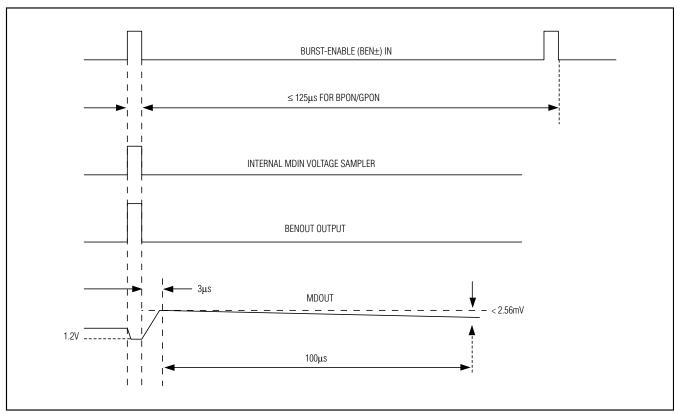

Laser monitor diode current is only generated when there is an optical output (BEN is active). When BEN is inactive, the monitor current is zero, reflecting the fact that the laser is off. A sample-and-hold circuit, triggered by the state of the BEN input, is provided in the MAX3643. During the burst-enable active period, the voltage present at MDIN is stored on an internal sample-and-hold capacitor; and during the burst-enable inactive period, that voltage is output on MDOUT; see the timing diagram in Figure 2.

While the internal sample-and-hold is sampling (BEN active), MDOUT voltage takes a 1.2V reference level.

Figure 2. Sample-and-Hold Timing Diagram

#### **Enable Input**

An LVCMOS input,  $\overline{\text{EN}}$ , is provided to disable both bias and modulation currents under external control. The maximum time to disable laser current with the  $\overline{\text{EN}}$  control is 375ns.

#### **Setting the Current Limit**

A current limiter is provided to protect the laser diode by shutting down both bias and modulation currents when total current exceeds a value set by the resistor connected from IMAX to ground. Do not use less than  $3k\Omega$  RIMAX. See the IBIAS + IMOD Current Threshold vs. RIMAX graph in the <code>Typical Operating Characteristics</code>.

# Programming the MODSET and BIASSET Inputs

To program the laser modulation current using a current DAC, connect VMSET to VREF, attach the DAC to the MODSET pin and set the current according to:

To program the laser modulation current using a resistor or digital potentiometer, connect VMSET to VREF, attach a resistor from the MODSET pin to ground, and set the current according to:

$$I_{MOD} = \frac{1.2V}{R_{MODSET} + R_{MOD}} \times 88$$

To program the laser modulation current using a PWM voltage DAC (requiring a high-impedance load), attach a DAC output to the VMSET pin, connect a resistor from the MODSET pin to ground as shown in the *Typical Applications Circuit*, and set the current according to:

$$I_{MOD} = \frac{V_{DAC}}{R_{MODSET} + R_{MOD}} \times 88$$

# 155Mbps to 2.5Gbps Burst-Mode Laser Driver

This approach can also be used for a conventional voltage DAC output, if desired. In all cases, the voltage at MODSET must be kept  $\leq$  1.4V, which limits the range of acceptable values for RMODSET depending on the maximum modulation current.

Laser diode bias current is set in the same manner as modulation current.

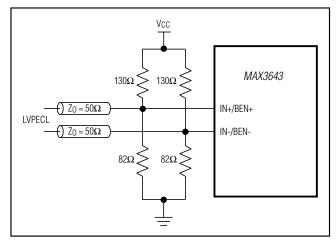

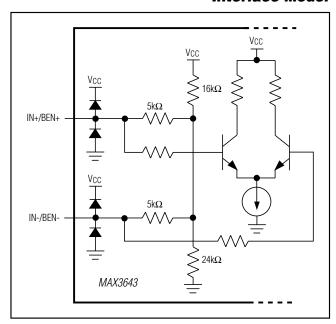

#### LVPECL Data/Burst-Enable Inputs

The MAX3643 data and BEN inputs are biased with an on-chip, high-impedance network. When DC-coupled, the MAX3643 operates properly with signals that meet the EC table input-swing and common-mode requirements, including LVPECL and most CML.

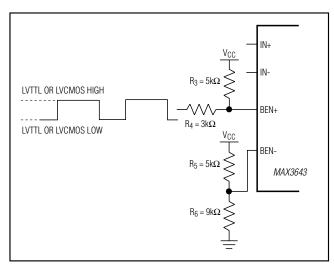

See Figure 3 for a termination network that can be used to connect the data and BEN inputs to LVPECL data outputs. Other termination networks may also be used, as long as both the input swing and common limits are met.

#### Sample-and-Hold Operation

When the MAX3643 internal sample-and-hold is not required, the MDIN pin should be connected to ground and the MDOUT pin unconnected. If the internal sample-and-hold is required, then it is necessary to ensure that the time constant resulting from the monitor diode load resistance and the total load capacitance is compatible with the desired minimum burst interval. It is also necessary to make certain that the load at MDOUT does not exceed the capability of the MDOUT pin.

Because the voltage at MDIN is not reflected to MDOUT until after the end of the laser burst, systems using the internal sample-and-hold alone cannot support continuous mode operation, often a required feature for module calibration. In this case, the voltage at MDIN can also be connected directly to a controller mux input. As long as the total capacitance (including monitor diode intrinsic capacitance, MDIN capacitance, mux off-capacitance, and wiring parasitics) is less than 50pF, and the monitor diode load resistor is less than  $2k\Omega$ , then the sample-and-hold captures a 576ns minimum burst. The MAX3643 typical MDIN capacitance is 5pF, typical monitor diode maximum capacitance is 25pF, and the typical capacitance of a mux input in the off-state is 3pF to 5pF. When the mux is in the on-state, the capacitance at the input is typically 10pF to 20pF.

Figure 3. LVPECL High-Speed Inputs

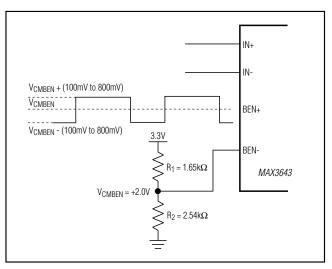

Figure 4. Single-Ended Biasing for Burst Enable

If the minimum burst duration is longer than 576ns, it may be useful to connect an external capacitor in parallel with the monitor diode load to limit the effects of the data pattern on the monitor diode output.

## **Applications Information**

#### **Running Burst-Enable Single-Ended**

See Figure 5 for setting up the single-ended LVTTL or LVCMOS biasing for burst enable.

#### **Layout Considerations**

To minimize inductance, keep the connections between the MAX3643 output pins and laser diode as close as possible. Place a bypass capacitor as close as possible to each VCC connection. Take extra care to minimize stray parasitic capacitance on the BIAS and MDIN pins. Use good high-frequency layout techniques and multilayer boards with uninterrupted ground planes to minimize EMI and crosstalk.

#### Laser Safety and IEC 825

Using the MAX3643 laser driver alone does not ensure that a transmitter design is compliant with IEC 825. The entire transmitter circuit and component selections must be considered. Each user must determine the level of fault tolerance required by the application, recognizing that Maxim products are neither designed nor authorized for use as components in systems intended for surgical implant into the body, for applications intended to support or sustain life, or for any other application in which the failure of a Maxim product could create a situation where personal injury or death can occur.

#### **Exposed-Paddle Package**

The exposed paddle on the 24-pin TQFN provides a very low thermal resistance path for heat removal from the IC. The pad is also electrical ground on the MAX3643 and must be soldered to the circuit board ground for proper thermal and electrical performance. Refer to Maxim Application Note 862: *HFAN-08.1:* Thermal Considerations of QFN and Other Exposed-Paddle Packages for additional information.

Figure 5. Single-Ended LVCMOS or LVTTL Biasing for Burst Enable

#### Interface Model

Figure 6. Simplified Input Circuit Schematic

# 155Mbps to 2.5Gbps Burst-Mode Laser Driver

## **Pin Configuration**

#### TOP VIEW 18 17 16 15 14 13 GND MDIN MDOUT MODSET 10 VMSET IMAX MAX3643 BCMON VREF 8 ĒΝ VBSET BENOUT BIASSET THIN QFN (4mm x 4mm) \*THE EXPOSED PAD MUST BE CONNECTED TO GROUND FOR PROPER THERMAL AND ELECTRICAL PERFORMANCE.

## \_Chip Information

TRANSISTOR COUNT: 2771 PROCESS: SiGe BiPOLAR

## Package Information

For the latest package outline information and land patterns, go to <a href="www.maximintegrated.com/package">www.maximintegrated.com/package</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE | OUTLINE | LAND        |

|------------|---------|---------|-------------|

| TYPE       | CODE    | NO.     | PATTERN NO. |

| 24 TQFN-EP | T2444-3 | 21-0139 | 90-0021     |

# 155Mbps to 2.5Gbps Burst-Mode Laser Driver

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |

|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 0                  | 11/05            | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                         |

|                    |                  | Added "155Mbps to 2.5Gbps" to the data sheet/part title.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | All                       |

|                    | 10/00            | Updated the Applications section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                         |

| 1 10/08            |                  | In the Operating Conditions table, changed the data rate from 1250Mbps to 2500Mbps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2                         |

|                    |                  | In the Typical Operating Characteristics, added the Electrical Eye Diagram graph.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                         |

| 2                  | 7/10             | Replaced the <i>Typical Application Circuit</i> ; added the soldering temperature to the <i>Absolute Maximum Ratings</i> section; updated the optical eye mask margins in the <i>Electrical Characteristics</i> table; corrected equation in Note 14; added the optical eye diagrams to the <i>Typical Operating Characteristics</i> section; updated the pin descriptions for the pins with diodes (13, 17) in the <i>Pin Description</i> table; updated Figure 1; updated the <i>Output Drivers</i> section; updated the <i>Layout Considerations</i> section; added the land pattern number to the <i>Package Information</i> table. | 1, 2, 4–10,<br>12, 13, 14 |

| 3                  | 5/12             | Updated Typical Application Circuit, Electrical Characteristics table, and Typical Operating Characteristics global conditions, and added bias current overshoot parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1–7                       |

| 4                  | 12/12            | Updated Note 1 in the Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                         |

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# AMEYA360 Components Supply Platform

# **Authorized Distribution Brand:**

## Website:

Welcome to visit www.ameya360.com

## Contact Us:

## > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

## > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

## Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com