## PGA202/203

# Digitally Controlled Programmable-Gain INSTRUMENTATION AMPLIFIER

#### **FEATURES**

- DIGITALLY PROGRAMMABLE GAINS: DECADE MODEL—PGA202 GAINS OF 1, 10, 100, 1000 BINARY MODEL—PGA203 GAINS OF 1, 2, 4, 8

- LOW BIAS CURRENT: 50pA max

FAST SETTLING: 2µs to 0.01%

LOW NON-LINEARITY: 0.012% max

- HIGH CMRR: 80dB min

- NEW TRANSCONDUCTANCE CIRCUITRY

- LOW COST

#### **APPLICATIONS**

- DATA ACQUISITION SYSTEMS

- AUTO-RANGING CIRCUITS

- DYNAMIC RANGE EXPANSION

- REMOTE INSTRUMENTATION

- TEST EQUIPMENT

#### DESCRIPTION

The PGA202 is a monolithic instrumentation amplifier with digitally controlled gains of 1, 10, 100, and 1000. The PGA203 provides gains of 1, 2, 4, and 8. Both have TTL or CMOS-compatible inputs for easy microprocessor interface. Both have FET inputs and a new transconductance circuitry that keeps the bandwidth nearly constant with gain. Gain and offsets are laser trimmed to allow use without any external components. Both amplifiers are available in ceramic or plastic packages. The ceramic package is specified over the full industrial temperature range while the plastic package covers the commercial range.

Covered by U.S. PATENT #4,883,422

International Airport Industrial Park

• Mailing Address: PO Box 11400

• Tucson, AZ 85734

• Street Address: 6730 S. Tucson Blvd.

• Tucson, AZ 85706

Tel: (520) 746-1111

• Twx: 910-952-1111

• Cable: BBRCORP

• Telex: 066-6491

• FAX: (520) 889-1510

• Immediate Product Info: (800) 548-6132

## **SPECIFICATIONS**

#### **ELECTRICAL**

At +25°C,  $V_{CC} = \pm 15V$  unless otherwise noted.

|                                                                                                                              |                                                                                              | PG/                  | \202/203 <i>i</i>                               | AG(1)                            | PG/   | A202/203I        | 3G <sup>(1)</sup>                  | PG              | A202/203I          | (P(1)           |                                                    |

|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------|----------------------------------|-------|------------------|------------------------------------|-----------------|--------------------|-----------------|----------------------------------------------------|

| PARAMETER                                                                                                                    | CONDITION                                                                                    | MIN                  | TYP                                             | MAX                              | MIN   | TYP              | MAX                                | MIN             | TYP                | MAX             | UNITS                                              |

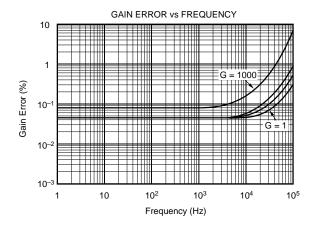

| GAIN<br>Error <sup>(2)</sup><br>Nonlinearity<br>Gain vs Temperature                                                          | G < 1000<br>G = 1000<br>G < 1000<br>G = 1000<br>G < 100                                      |                      | 0.05<br>0.1<br>0.002<br>0.02<br>3               | 0.25<br>1<br>0.015<br>0.06<br>25 |       | * 0.08<br>*<br>* | 0.15<br>0.5<br>0.012<br>0.04<br>15 |                 | * * * * *          | * * *           | %<br>%<br>%<br>%<br>ppm/°C                         |

| Can vs Temperature                                                                                                           | G = 100<br>G = 1000                                                                          |                      | 40<br>100                                       | 120<br>300                       |       | *                | 60<br>150                          |                 | *                  |                 | ppm/°C<br>ppm/°C                                   |

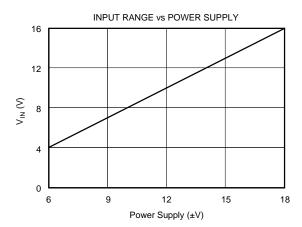

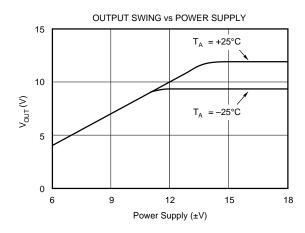

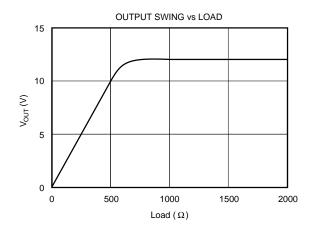

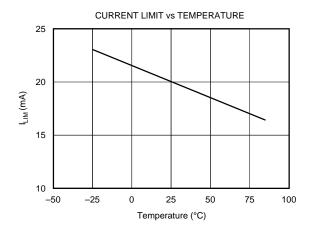

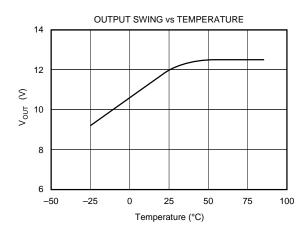

| RATED OUTPUT Voltage Over Specified Temperature Current Impedance                                                            | $ I_{OUT}  \le 5mA$<br>See Typical Perf. Curve $ V_{OUT}  \le 10V$                           | ±10<br>±5            | ±12<br>±9<br>±10<br>0.5                         |                                  | *     | * * *            |                                    | *               | *<br>±10<br>*<br>* |                 | V<br>V<br>mA<br>Ω                                  |

| ANALOG INPUTS Common-Mode Range Absolute Max Voltage <sup>(3)</sup> Impedance, Differential Common-Mode                      | No Damage                                                                                    | ±10                  | ±13 10    3 10    1                             | ±V <sub>CC</sub>                 | *     | *                | *                                  | *               | * *                | *               | V<br>V<br>GΩ    pF<br>GΩ    pF                     |

| OFFSET VOLTAGE (RTI) Initial Offset at 25°C (4)  vs Temperature                                                              |                                                                                              |                      | ±(0.5 + 5/G)<br>±(3 + 50/G)                     | ±(2 + 24/G)<br>±(24 + 240/G)     |       | *                | ±(1 +<br>12/G)<br>±(12 +<br>120/G) |                 | *                  | *               | mV<br>μV/°C                                        |

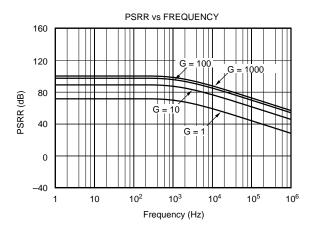

| Offset vs Time<br>Offset vs Supply                                                                                           | 10 ≤ V <sub>CC</sub> ≤ 15                                                                    |                      | 50<br>10 +<br>250/G                             | 100 +<br>900/G                   |       | *                | 50 +<br>450/G                      |                 | *                  | *               | μV/Month<br>μV/V                                   |

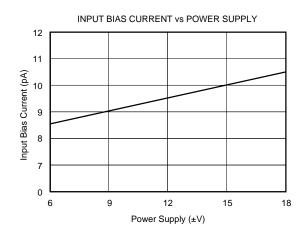

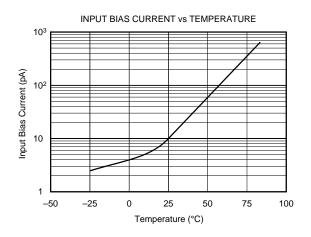

| INPUT BIAS CURRENT Initial Bias Current: at 25°C at 85°C Initial Offset Current: at 25°C at 85°C                             |                                                                                              |                      | 10<br>640<br>5<br>320                           | 50<br>3200<br>25<br>1600         |       | * * *            | *<br>*<br>*                        |                 | *<br>*<br>*        | * * *           | pA<br>pA<br>pA<br>pA                               |

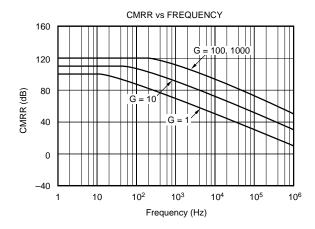

| COMMON-MODE REJECTION F                                                                                                      |                                                                                              |                      |                                                 |                                  |       |                  |                                    |                 |                    |                 |                                                    |

|                                                                                                                              | G = 1<br>G = 10<br>G = 100<br>G = 1000                                                       | 80<br>86<br>92<br>94 | 100<br>110<br>120<br>120                        |                                  | * * * | * * *            |                                    | *<br>*<br>*     | *<br>*<br>*        |                 | dB<br>dB<br>dB<br>dB                               |

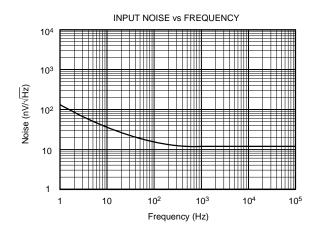

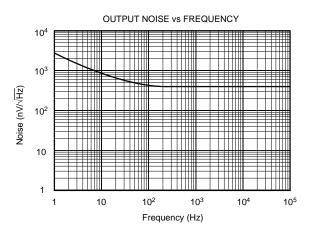

| INPUT NOISE  Noise Voltage 0.1 to 10Hz  Noise Density at 10kHz (5)                                                           |                                                                                              |                      | 1.7<br>12                                       |                                  |       | *                |                                    |                 | *                  |                 | μVp-p<br>nV/√Hz                                    |

| OUTPUT NOISE  Noise Voltage 0.1 to 10Hz  Density at 1kHz (5)                                                                 |                                                                                              |                      | 32<br>400                                       |                                  |       | *                |                                    |                 | *                  |                 | μVp <u>-p</u><br>nV/√Hz                            |

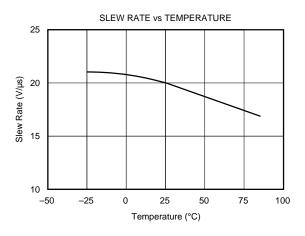

| Frequency Response Full Power Bandwidth Slew Rate Settling Time (0.01%) <sup>(7)</sup> Overload Recovery Time <sup>(7)</sup> | G < 1000<br>G = 1000<br>G < 1000<br>G = 1000<br>G < 1000<br>G = 1000<br>G < 1000<br>G = 1000 | 10                   | 1000<br>250<br>400<br>100<br>20<br>2<br>10<br>5 |                                  | 15    | * * * * * * *    |                                    | *               | * * * * * * * * *  |                 | kHz<br>kHz<br>kHz<br>kHz<br>V/µs<br>µs<br>µs<br>µs |

| DIGITAL INPUTS Digital Common Range Input Low Threshold (6) Input Low Current Input High Voltage Input High Current          |                                                                                              | -V <sub>CC</sub>     |                                                 | V <sub>CC</sub> - 8<br>0.8<br>10 | *     |                  | * * *                              | *               |                    | * * *           | V<br>V<br>μΑ<br>V<br>μΑ                            |

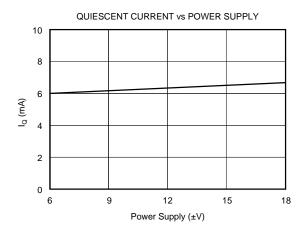

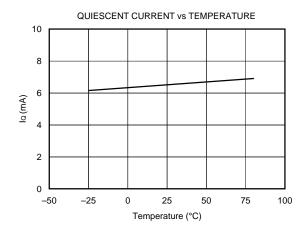

| POWER SUPPLY Rated Voltage Voltage Range Quiescent Current                                                                   |                                                                                              | ±6                   | ±15<br>6.5                                      | ±18                              | *     | *                | *                                  | *               | *                  | *               | V<br>V<br>mA                                       |

|                                                                                                                              |                                                                                              | -25<br>-55<br>-65    | 100                                             | 85<br>125<br>150                 | * *   | *                | * *                                | 0<br>-25<br>-40 | *                  | 70<br>85<br>100 | ۸۲۵<br>۲۵<br>۲۵<br>۲۵<br>۲۵                        |

$<sup>^{\</sup>star}$  Same as the PGA202/203AG

$NOTES: (1) All \ specifications \ apply \ to \ both \ the \ PGA 202 \ and \ the \ PGA 203. \ Values \ given \ for \ a \ gain \ of \ 10 \ are \ the \ same \ for \ a \ gain \ of \ 8 \ and \ other \ values \ may \ be \ interpolated.$

<sup>(6)</sup> Threshold voltages are referenced to Digital Common. (7) From input change or gain change.

<sup>(2)</sup> Measured with a 10k load. (3) The analog inputs are internally diode clamped. (4) Adjustable to zero. (5)  $V_{NOISE\,(RTI)} = \sqrt{(V_{N\,INPUT})^2 + (V_{N\,OUTPUT}/Gain)^2}$ .

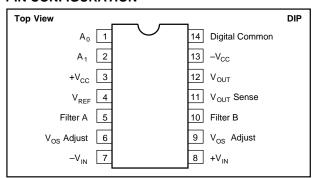

#### **PIN CONFIGURATION**

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage                    | ±18V                      |

|-----------------------------------|---------------------------|

| Internal Power Dissipation        | 750mW                     |

| Analog and Digital Inputs         | ±(V <sub>CC</sub> + 0.5V) |

| Operating Temperature Range:      |                           |

| G Package                         | 55°C to +125°C            |

| P Package                         | 40°C to +100°C            |

| Lead Temperature (soldering, 10s) | 300°C                     |

| Output Short Circuit Duration     | Continuous                |

| Junction Temperature              | 175°C                     |

|                                   |                           |

#### **PACKAGE INFORMATION**

| MODEL    | PACKAGE            | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|--------------------|------------------------------------------|

| PGA202KP | 14-Pin Plastic DIP | 010                                      |

| PGA202AG | 14-Pin Ceramic DIP | 169                                      |

| PGA202BG | 14-Pin Ceramic DIP | 169                                      |

| PGA203KP | 14-Pin Plastic DIP | 010                                      |

| PGA203AG | 14-Pin Ceramic DIP | 169                                      |

| PGA203BG | 14-Pin Ceramic DIP | 169                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

#### **ORDERING INFORMATION**

|                                  |                                                        |                                           | TEMPERATURE                                      | OFFSET VOLTAGE                            |  |  |

|----------------------------------|--------------------------------------------------------|-------------------------------------------|--------------------------------------------------|-------------------------------------------|--|--|

| MODEL                            | GAINS                                                  | PACKAGE                                   | RANGE                                            | MAX (mV)                                  |  |  |

| PGA202KP<br>PGA202AG<br>PGA202BG | 1, 10, 100, 1000<br>1, 10, 100, 1000<br>1, 10, 100, 10 | Plastic DIP<br>Ceramic DIP<br>Ceramic DIP | 0°C to +70°C<br>-25°C to +85°C<br>-25°C to +85°C | ±(2 + 24/G)<br>±(2 + 24/G)<br>±(1 + 12/G) |  |  |

| PGA203KP<br>PGA203AG<br>PGA203BG | 1, 2, 4, 8<br>1, 2, 4, 8<br>1, 2, 4, 8                 | Plastic DIP<br>Ceramic DIP<br>Ceramic DIP | 0°C to +70°C<br>-25°C to +85°C<br>-25°C to +85°C | ±(2 + 24/G)<br>±(2 + 24/G)<br>±(1 + 12/G) |  |  |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

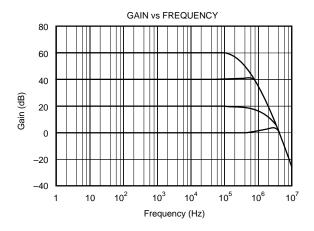

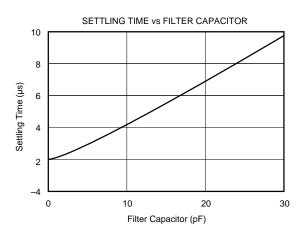

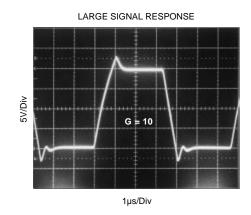

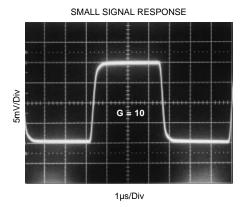

# **TYPICAL PERFORMANCE CURVES**

$T_A = +25^{\circ}C$ ,  $V_S = \pm 15V$  unless otherwise noted.

# TYPICAL PERFORMANCE CURVES (CONT)

$T_A$  = +25°C,  $V_S$  = ±15V unless otherwise noted.

# **TYPICAL PERFORMANCE CURVES (CONT)**

$T_A = +25$ °C,  $V_S = \pm 15$ V unless otherwise noted.

# TYPICAL PERFORMANCE CURVES (CONT)

$T_A = +25$ °C,  $V_{CC} = \pm 15$ V unless otherwise noted.

# DISCUSSION OF PERFORMANCE

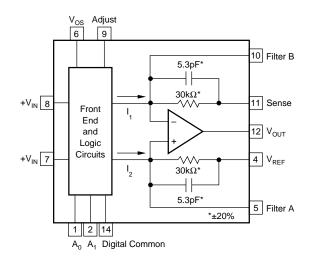

A simplified diagram of the PGA202/203 is shown on the first page. The design consists of a digitally controlled, differential transconductance front end stage using precision FET buffers and the classical transimpedance output stage. Gain switching is accomplished with a novel current steering technique that allows for fast settling when changing gains. The result is a high performance, programmable instrumentation amplifier with excellent speed and gain accuracy.

The input stage uses a new circuit topology that includes FET buffers to give extremely low input bias currents. The differential input voltage is converted into a differential output current with the transconductance gain selected by steering the input stage bias current between four identical input stages differing only in the value of the gain setting resistor. Each input stage is individually laser-trimmed for input offset, offset drift, and gain.

The output stage is a differential transimpedance amplifier. Unlike the classical difference amplifier output stage, the common-mode rejection is not limited by the resistor matching. However, the output resistors are laser-trimmed to help minimize the output offset and drift.

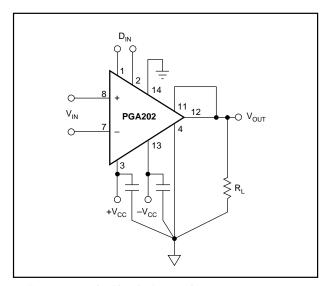

#### **BASIC CONNECTIONS**

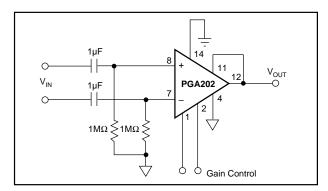

Figure 1 shows the proper connections for power supply and signal. The power supplies should be decoupled with  $1\mu F$  tantalum capacitors placed as close to the amplifier as possible for maximum performance. To avoid gain and CMR errors introduced by the external components, you should connect the grounds as indicated. Any resistance in the sense line (pin 11) or the  $V_{REF}$  line (pin 4) will lead to a gain error, so these lines should be kept as short as possible. To also maintain stability, avoid capacitance from the output to the input or the offset adjust pins.

FIGURE 1. Basic Circuit Connections.

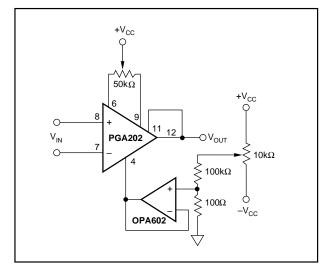

#### **OFFSET ADJUSTMENT**

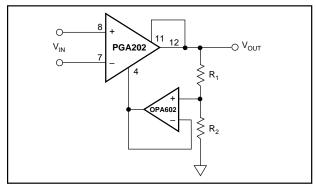

Figure 2 shows the offset adjustment circuits for the PGA202/203. The input offset and the output offset are both separately adjustable. Notice that because the PGA202/203 change between four different input stages to change gain, the input offset voltage will change slightly with gain. For systems using computer autozeroing techniques, neither offset nor drift is a major concern, but it should be noted that since the input offset does change with gain, these systems should perform an autozero cycle after each gain change for optimum performance.

In the output offset adjustment circuit, the choice of the buffering op amp is very important. The op amp needs to have low output impedance and a wide bandwidth to maintain full accuracy over the entire frequency range of the PGA202/203. For these reasons we recommend the OPA602 as an excellent choice for this application.

FIGURE 2. Offset Adjustment Circuits.

#### **GAIN SELECTION**

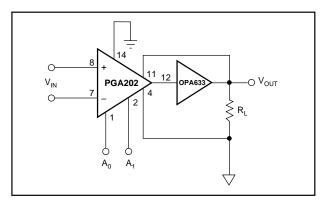

Gain selection is accomplished by the application of a 2-bit digital word to the gain select inputs. Table I shows the gains for the different possible values of the digital input word. The logic inputs are referred to their own separate digital common pin, which can be connected to any voltage between the minus supply and 8V below the positive supply. The gains are all internally trimmed to an initial accuracy of better than 0.1%, so no external gain adjustment is required. However, if necessary the gains can be increased by the use of an external attenuator around the output stage as shown in Figure 3. Recommended resistor values for certain selected output gains are given in Table II.

|                |                | PGA202 |       | PGA  | 203   |

|----------------|----------------|--------|-------|------|-------|

| A <sub>1</sub> | A <sub>0</sub> | GAIN   | ERROR | GAIN | ERROR |

| 0              | 0              | 1      | 0.05% | 1    | 0.05% |

| 0              | 1              | 10     | 0.05% | 2    | 0.05% |

| 1              | 0              | 100    | 0.05% | 4    | 0.05% |

| 1              | 1              | 1000   | 0.10% | 8    | 0.05% |

TABLE I. Software Gain Selection.

| OUTPUT GAIN | R <sub>1</sub> | R <sub>2</sub> |

|-------------|----------------|----------------|

| 2           | 5kΩ            | 5kΩ            |

| 5           | 2kΩ            | 8kΩ            |

| 10          | 1kΩ            | 9kΩ            |

TABLE II. Output Stage Gain Control.

FIGURE 3. Gain Increase with Buffered Attenuator.

#### **COMMON-MODE INPUT RANGE**

Unlike the classical three op amp type of circuit, the input common-mode range of the PGA202/203 does not depend on the differential input and the gain. In the standard three op amp circuit, the input common-mode signal must be kept below the maximum output voltage of the input amplifier minus 1/2 the final output voltage. If, for example, these amplifiers can swing ±12V, then to get 12V at the output you must restrict the input common-mode voltage to only 6V. The circuitry of the PGA202/203 is such that the common-mode input range applies to either input pin regardless of the output voltage.

#### **OUTPUT SENSE**

An output sense has been provided to allow greater accuracy in connecting the load. By attaching this feedback point to the load at the load site, IR drops due to the load currents are eliminated since they are inside the feedback loop. Proper connection is shown in Figure 1. When more current is required, a power booster can be placed in the feedback loop as shown in Figure 4. Buffer errors are minimized by the loop gain of the output amplifier.

FIGURE 4. Current Boosting the Output.

#### **OUTPUT FILTERING**

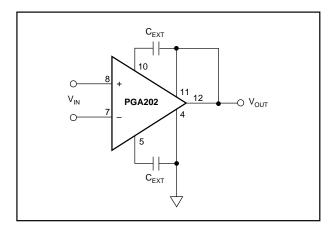

The summing nodes of the output amplifier have also been made available to allow for output filtering. By placing matched capacitors in parallel with the existing internal capacitors as shown in Figure 5, you can lower the frequency response of the output amplifier. This will reduce the noise of the amplifier, at the cost of a slower response. The nominal frequency responses for some selected values of capacitor are shown in Table III.

FIGURE 5. Output Filtering.

| CUTOFF FREQUENCY | C <sub>1</sub> AND C <sub>2</sub> |  |  |

|------------------|-----------------------------------|--|--|

| 1MHz             | None                              |  |  |

| 100kHz           | 47pF                              |  |  |

| 10kHz            | 525pF                             |  |  |

TABLE III. Output Frequency vs Filter Capacitors.

#### INPUT CHARACTERISTICS

Because the PGA202/203 have FET inputs, the bias currents drawn through input source resistors have a negligible effect on DC accuracy. The picoamp currents produce no more than microvolts through megohm sources. The inputs are also internally diode clamped to the supplies. Thus, input filtering and input series protection are easily achievable.

A return path for the input bias currents must always be provided to prevent the charging of any stray capacitance. Otherwise, the amplifier could wander and saturate. A  $1M\Omega$  to  $10M\Omega$  resistor from the input to common will return floating sources such as thermocouples and AC-coupled inputs (see Applications Section, Figures 8 and 9.)

#### **DYNAMIC PERFORMANCE**

The PGA202 and the PGA203 are fast-settling FET input programmable gain instrumentation amplifiers. Careful attention to minimize stray capacitance is necessary to achieve specified performance. High source resistance will interact with the input capacitance to reduce speed and overall bandwidth. Also, to maintain stability, avoid capacitance from the output to the input or the offset adjust pins.

Applications with balanced source impedance will provide the best performance. In some applications, mismatched source impedances may be required. If the impedance in the negative input exceeds that in the positive input, stray capacitance from the output will create a net negative feedback and improve the stability of the circuit. If, however, the impedance in the positive input is greater, then the feedback due to stray capacitance will be positive and instability may result. The degree of positive feedback will, of course, depend on the source impedance imbalance as well as the board layout and the operating gain. The addition of a small bypass capacitor of about 5 to 50pF directly across the input terminals of the PGIA will generally eliminate any instability arising from these stray capacitances. CMR errors due to the source imbalance will also be reduced by the addition of this capacitor.

The PGA202 and the PGA203 are designed for fast settling in response to changes in either the input voltage or the gain. The bandwidth and the settling times are mostly determined by the output stage and are therefore independent of gain, except at the highest gain of the PGA202 where other factors in the input stage begin to dominate.

#### **APPLICATIONS**

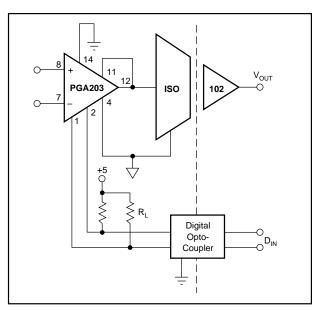

In addition to general purpose applications, the PGA202/203 are designed to handle two important and demanding classes of applications: inputs with high source impedances, and rapid scanning data acquisition systems requiring fast settling time. Because the user has access to output sense and output common pins, current sources can also be constructed with a minimum of external components. Some basic application circuits are shown in Figures 6 through 12.

FIGURE 6. Isolated Programmable Gain Instrumentation Amplifier.

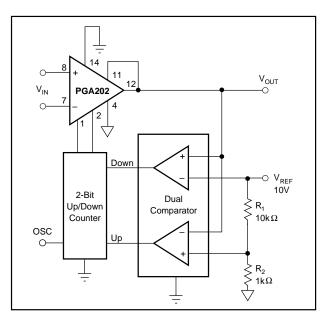

FIGURE 7. Auto Gain Ranging.

FIGURE 8. AC-Coupled Differential Amplifier for Frequencies Above 0.16Hz.

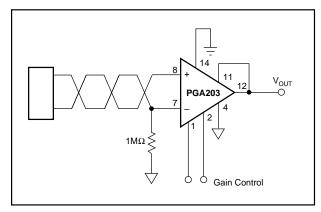

FIGURE 9. Floating Source Programmable Gain Instrumentation Amplifier.

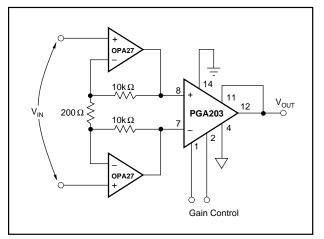

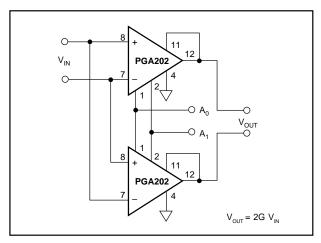

FIGURE 10. Low Noise Differential Amplifier with Gains of 100, 200, 400, 800.

FIGURE 11. Programmable Differential In/Differential Out Amplifier.

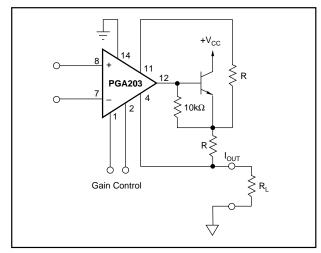

FIGURE 12. Programmable Current Source.

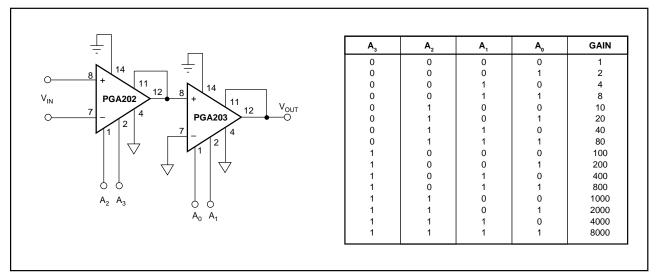

FIGURE 13. Cascaded Amplifiers.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated

# AMEYA360 Components Supply Platform

# **Authorized Distribution Brand:**

#### Website:

Welcome to visit www.ameya360.com

#### Contact Us:

## > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

#### > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

## Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com