Automotive Power

#### Edition 2006-04-05

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany © Infineon Technologies AG 2005.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics. Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## **High Speed CAN-Transceiver with Wake Detection**

#### **TLE 6251 G**

#### **Features**

- CAN data transmission rate up to 1 Mbaud

- Compatible to ISO/DIS 11898

- Supports 12 V and 24 V automotive applications

- Low power modes with local wake-up input and remote wake-up via CAN bus

- Very low power consumption in sleep mode

- Wake-up input

- Wake-up source recognition

- Inhibit output to control an external power supply

- Diagnosis output

- RxD only mode for node failure analysis

- Split termination to stabilize the recessive level

- TxD time-out function with diagnosis

- RxD recessive clamping handler with diagnosis

- TxD to RxD short circuit handler with diagnosis

- Bus line short circuit diagnosis

- Bus dominant clamping diagnosis

- Undervoltage detection at  $V_{CC}$ ,  $V_{I/O}$  and  $V_{BAT}$

- Cold start diagnosis (first battery connection)

- Adaptive to host logic supply levels (3.3 and 5 V)

- Wide common mode range for electromagnetic immunity (EMI)

- Low electromagnetic emission (EME)

- Short circuit proof to ground, battery and  $V_{CC}$

- Overtemperature protection

- Protected against automotive transients

- +/- 6kV ESD Robustness according to IEC 61000-4-2

| Туре       | Ordering Code | Package     |

|------------|---------------|-------------|

| TLE 6251 G | SP000069400   | P-DSO-14-13 |

### **Description**

The CAN-transceiver TLE 6251 G is a monolithic integrated circuit in a P-DSO-14-13 package for high speed differential mode data transmission (up to 1 Mbaud) and reception in automotive and industrial applications. It works as an interface between the CAN protocol controller and the physical bus lines compatible to ISO/DIS 11898.

As a successor to the first generation of HS CAN, the TLE 6251 G is designed to provide an excellent passive behavior when the transceiver is switched off (mixed networks, clamp15/30 applications). The current consumption can be reduced, due to the low power modes. This supports networks with partially powered down nodes.

The TLE 6251 G offers two low power modes as well as a receive-only mode to support software diagnosis functions. A wake-up from the low power mode is possible via a message on the bus or via the bi-level sensitive wake input. An external voltage supply IC can be controlled by the inhibit output. So, the  $\mu$ C can be powered down and the TLE 6251 G still reacts to wake-up activities on the CAN bus or local wake input.

A diagnosis output allows mode dependent enhanced diagnosis of bus failures and wake-up source. A  $V_{\rm BAT}$  fail flag reports an power-on condition at the battery supply input.

The TLE 6251 G is designed to withstand the severe conditions of automotive applications and to support 12 V and 24 V applications.

The IC is based on the Smart Power Technology SPT® which allows bipolar and CMOS control circuitry in accordance with DMOS power devices existing on the same monolithic circuit.

Final Data Sheet 4 Rev. 3.2, 2006-04-05

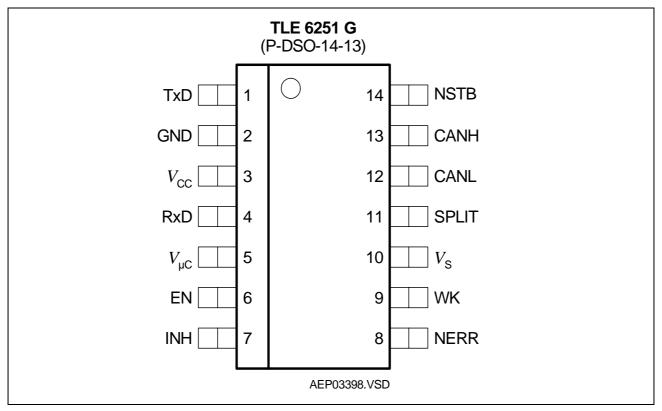

## **Pin Configuration**

Figure 1 Pin Configuration (top view)

**Table 1 Pin Definitions and Functions**

| Pin No. | Symbol         | Function                                                                                                                                                                                                       |

|---------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | TxD            | <b>CAN transmit data input;</b> 20 kΩ pull-up, LOW in dominant state                                                                                                                                           |

| 2       | GND            | Ground                                                                                                                                                                                                         |

| 3       | $V_{\rm CC}$   | 5 V supply input; block to GND with 100 nF ceramic capacitor                                                                                                                                                   |

| 4       | RxD            | CAN receive data output; LOW in dominant state, push-pull output stage                                                                                                                                         |

| 5       | $V_{ m \mu C}$ | <b>Logic voltage level adapter input;</b> connect to pin $V_{\rm CC}$ for 5 V microcontroller, connect to additional supply voltage for other logic voltage levels, block to GND with 100 nF ceramic capacitor |

| 6       | EN             | Mode control input 1; internal pull-down, see Figure 6                                                                                                                                                         |

| 7       | INH            | Control output; set HIGH to activate voltage regulator; open drain                                                                                                                                             |

| 8       | NERR           | <b>Diagnosis output 1;</b> error and power on indication output, push-pull output stage                                                                                                                        |

| 9       | WK             | Wake-up input; bi-level sensitive                                                                                                                                                                              |

Final Data Sheet 5 Rev. 3.2, 2006-04-05

## Table 1 Pin Definitions and Functions (cont'd)

| Pin No. | Symbol     | Function                                                                                                 |

|---------|------------|----------------------------------------------------------------------------------------------------------|

| 10      | $V_{ m S}$ | Battery voltage supply input; block to GND with 100 nF ceramic capacitor                                 |

| 11      | SPLIT      | <b>Termination output;</b> to support the recessive voltage level of the bus lines (see <b>Table 2</b> ) |

| 12      | CANL       | Low line output; LOW in dominant state                                                                   |

| 13      | CANH       | High line output; HIGH in dominant state                                                                 |

| 14      | NSTB       | Mode control input 2; internal pull-down, see Figure 6                                                   |

Final Data Sheet 6 Rev. 3.2, 2006-04-05

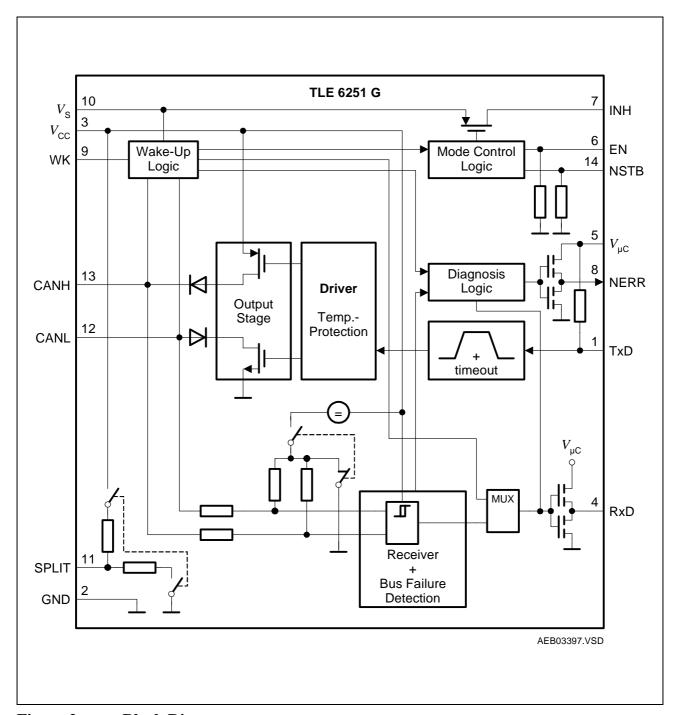

## **Functional Block Diagram**

Figure 2 Block Diagram

#### **Application Information**

As a successor to the first generation of HS CAN, the TLE 6251 G is designed to provide an excellent passive behavior when the transceiver is switched off (mixed networks, terminal 15/30 applications). The current consumption can be reduced, due to the low power modes. This supports networks with partially powered down nodes.

A wake-up from the low power modes is possible via a message on the bus or via the bi-level sensitive wake input WK. An external voltage supply IC can be controlled by the inhibit output INH. So, the  $\mu$ C can be powered down and the TLE 6251 G still reacts to wake-up activities on the CAN bus or local wake input activities.

A diagnosis output pin NERR, allows mode dependent enhanced diagnosis of bus failures and wake-up source. A  $V_{\rm BAT}$  fail flag reports a power-on condition at the battery supply input. The  $V_{\rm BAT}$  fail flag will be resetted after the first transition into normal mode.

The TLE 6251 G has four operation modes, the normal, the receive only, the standby mode and the sleep mode. These modes can be controlled with the two control pins EN and NSTB pin (see **Figure 6**, **Table 2**). Both, EN and NSTB, have an implemented pull-down, so if there is no signal applied to EN and NSTB, the transceiver automatically changes to the standby mode.

#### **Normal Mode**

To transfer the TLE 6251 G into the normal mode, NSTB and EN have to be switched to HIGH level. This mode is designed for the normal data transmission/reception within the HS-CAN network.

#### **Transmission**

The signal from the  $\mu$ C is applied to the TxD input of the TLE 6251 G. Now the bus driver switches the CANH/L output stages to transfer this input signal to the CAN bus lines.

#### **TxD Time-out Feature**

If the TxD signal is dominant for a time  $t > t_{\rm TxD}$ , the TxD time-out function deactivates the transmission of the signal at the bus. This is realized to prevent the bus from being blocked permanently due to an error.

The transmission is released again, after a mode state change.

#### **TxD to RxD Short Circuit Feature**

Similar to the TxD time-out, a TxD to RxD short circuit would also drive a permanent dominant signal at the bus and so block the communication. To avoid this, the TLE 6251 G has a TxD to RxD short circuit detection.

Final Data Sheet 8 Rev. 3.2, 2006-04-05

#### **Reduced Electromagnetic Emission**

The bus driver has an implemented control to reduce the electromagnetic emission (EME). This is achieved by controlling the symmetry of the slope, resp. of CANH and CANL.

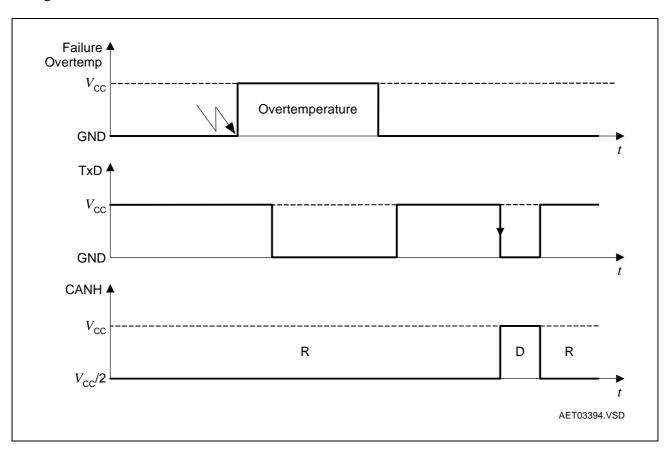

#### Overtemperature

The driver stages are protected against overtemperature. Exceeding the shutdown temperature results in deactivation of the driving stages at CANH/L. To avoid a bit failure after cooling down, the signals can be transmitted again only after a dominant to recessive edge at TxD.

**Figure 3** shows the way how the transmission stage is deactivated and activated again. First an overtemperature condition causes the transmission stage to deactivate. After the overtemperature condition is no longer present, the transmission is only possible after the TxD bus signal has changed to recessive level.

Figure 3 Release of the Transmission after Overtemperature

Final Data Sheet 9 Rev. 3.2, 2006-04-05

## Reception

The analog CAN bus signals are converted into a digital signal at RxD via the differential input receiver.

In normal mode and RxD only, the split pin is used to stabilize the recessive common mode signal.

#### **Permanent Recessive Clamping**

If the RxD signal is permanent recessive, although there is a message sent on the bus, the host  $\mu C$  of this transceiver could start a message at any time, because the bus seems to be idle. To prevent this node to disturb the communication on the bus, the TLE 6251 G offers a so called permanent RxD recessive clamping. If the RxD signal is permanent recessive, an error flag is set and the transmitter is deactivated as long as the error occurs

#### Receive Only Mode (RxOnly Mode)

In the RxOnly mode, the transmission stage is deactivated but the reception of signals via the CAN bus is still possible. This mode is implemented to support hardware and software diagnosis functions.

If there is an hardware error on the transmission part of a node (e.g. bubbling idiot failure), in the RxOnly mode, the bus is no longer blocked and the  $\mu$ C can still receive the messages on the bus.

It is also possible to make a network analysis of the interconnections between the nodes. A connection between two nodes (in a network) is checked if both nodes are in the normal mode and all others are in RxOnly mode. If a message from one node is sent to the other, this has to be acknowledged. If there is no acknowledge of the message, the connection between the two nodes has an error.

The RxD pin also works as an diagnosis flag, which is described more in detail in Table 2.

Final Data Sheet 10 Rev. 3.2, 2006-04-05

#### **Standby Mode**

In the standby mode, transmission and reception of signals is deactivated. This is the first step of reducing the current consumption. The internal voltage regulator control pin (INH) is still active, so all external (INH controlled) powered devices are also activated.

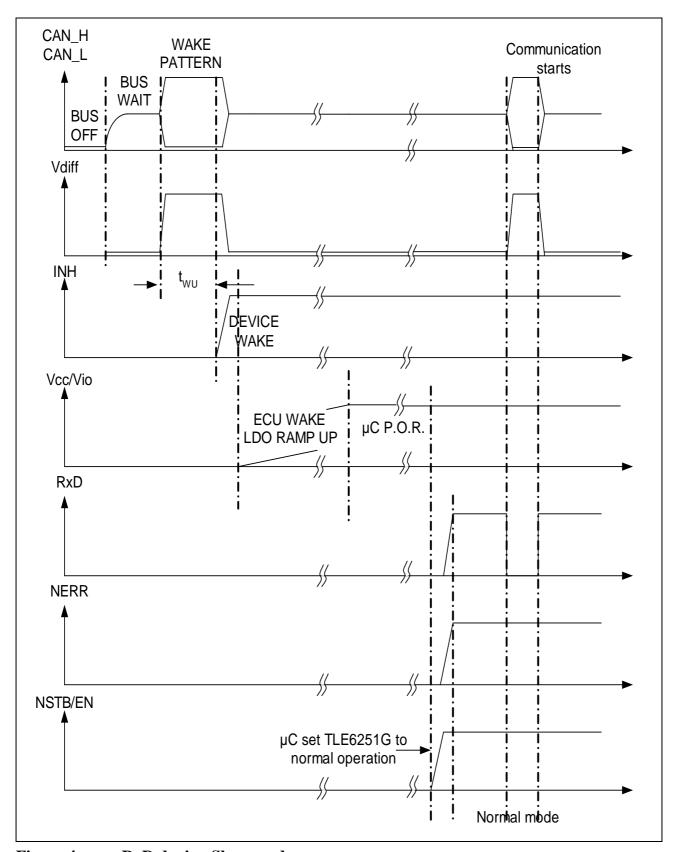

#### Wake-Up

The wake-up is possible via WK-pin (filtering time  $t > t_{\rm WK}$ ) or CAN message (filtering time  $t > t_{\rm WU}$ ) and sets the RxD/NERR pins to LOW, see **Figure 4**. Now the  $\mu$ C is able to detect this change at RxD and switch the transceiver into the normal mode. Once the wake-up flag is set (= LOW), it remains in this state, as long as the transceiver is not transferred into the normal mode. The detection of the wake-up source is possible during the first 4 recessive to dominant edges at TxD in the normal mode.

#### **Go-to Sleep Mode**

The go-to sleep mode is used to have an intermediate step between the sleep mode and all other modes. This mode has to control if the sleep command (EN = 1, NSTB = 0) is activated for a minimum hold time  $t > t_{\rm hSLP}$ . Afterwards the TLE 6251 G automatically transfers into the sleep mode. The activated features in go-to sleep mode are similar to the standby mode.

#### **Sleep Mode**

In the sleep mode, transmission and reception of signals is deactivated. This is the second step of reducing the current consumption. The internal voltage regulator control pin (INH) is deactivated.

#### Transition into other Modes during Sleep Mode

Transition from sleep into other modes is possible if  $V_{\rm CC}$  and  $V_{\mu \rm C}$  active. Selection of the modes can be done by the mode control inputs.

#### Wake-Up

The wake-up is possible via WK-pin (filtering time  $t > t_{\rm WK}$ ) or CAN message (filtering time  $t > t_{\rm WU}$ ) and automatically transfers the TLE 6251 G into the standby mode and sets the RxD/NERR pins to LOW, see **Figure 4**. Once the TLE 6251 G has been set to the standby mode, the system voltage regulator is activated by the inhibit output INH, and the  $\mu$ C restarts. Now the  $\mu$ C is able to detect this change at RxD and switch the transceiver into the normal mode. Once the wake-up flag is set (= LOW), it remains in this state, as long as the transceiver is not transferred into the normal mode. The detection of the wake-up source is possible during the first 4 recessive to dominant edges at TxD in the normal mode.

Final Data Sheet 11 Rev. 3.2, 2006-04-05

Figure 4 RxD during Sleep mode

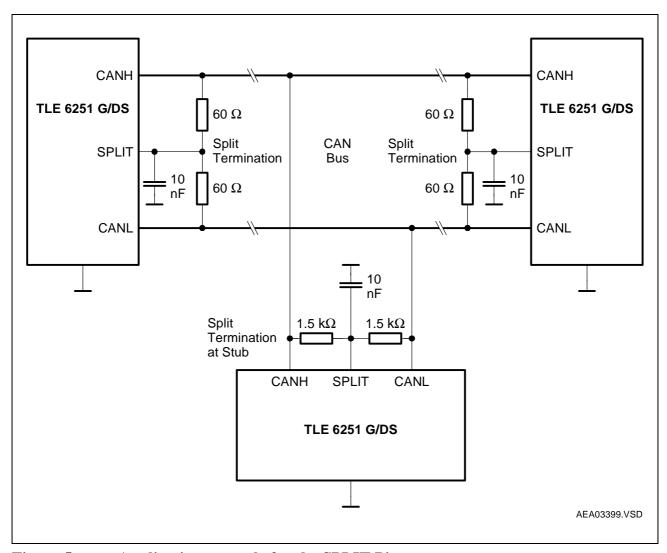

#### **Split Circuit**

The split circuitry is activated during normal and RxOnly mode and deactivated (SPLIT pin high ohmic) during sleep and standby mode. The SPLIT pin is used to stabilize the recessive common mode signal in normal mode and RxOnly mode. This is realized with a stabilized voltage of 0.5  $V_{\rm CC}$  at SPLIT.

Figure 5 Application example for the SPLIT Pin

A correct application of the SPLIT pin is shown in **Figure 5**. The split termination for the left and right node is realized with two 60  $\Omega$  resistances and one 10 nF capacitor. The center node in this example is a stub node and the recommended value for the split resistances is 1.5 k $\Omega$ .

#### Diagnosis-Flags at NERR and RxD

#### Power-Up Flag

• Task: to signalize a power-up state at  $V_{

m BAT}$

- Indicator: NERR = LOW in RxOnly mode

- Remarks: Power-up flag is cleared when entering the normal mode

#### Wake-Up Flag

- Task: to signalize a wake-up condition at the WK pin (filtering time  $t > t_{WK}$ ) or via CAN bus message (filtering time  $t > t_{WIJ}$ )

- Indicator: RxD or NERR = LOW in sleep/stand-by mode immediately after wake-up

- Remarks: Flag is cleared on entering the RxOnly mode

#### **Wake-Up Source Flag**

- Task: to distinguish between the two wake-up sources

- Indicator: NERR = LOW in normal mode = wake-up via WK pin

- Remarks: only available if the power-up flag is cleared. After four recessive to dominant edges on TxD in normal mode, the flag is cleared. Leaving the normal mode clears the wake-up source flag.

#### **Bus Failure Flag**

- Task: to signalize a bus line short circuit condition to GND,  $V_{\rm S}$  or  $V_{\rm CC}$

- Indicator: NERR = LOW in normal mode

- Remarks: flag is set after four consecutive recessive to dominant cycles on pin TxD when trying to drive the bus dominant. The bus failure flag is cleared if the normal mode is reentered or 4 recessive to dominant edges at TxD without failure condition.

#### **Local Failure Flag**

- Task: to signalize one of the five local failure conditions described in Local Failure-Flags and -Detection

- Indicator: NERR = LOW in RxOnly mode (local failure flag is set)

- Remarks: the flag is cleared when entering the normal mode from RxOnly mode or when RxD is dominant while TxD is recessive.

Final Data Sheet 14 Rev. 3.2, 2006-04-05

#### **Local Failure-Flags and -Detection**

#### **TxD Dominant Failure Detection**

- Effect: permanent dominant signal for  $t > t_{TxD}$  at TxD

- Indicator: NERR = LOW in RxOnly mode (local failure flag is set)

- Action: disabling of the transmitter stage

- Remarks: release of the transmitter stage only after transition into RxOnly mode (failure diagnosis) and transition into normal mode.

#### **RxD Permanent Recessive Clamping**

- Effect: internal RxD signal does not match signal at RxD pin because the RxD pin is pulled to HIGH (permanent HIGH)

- Indicator: NERR = LOW in RxOnly mode (local failure flag is set)

- Action: disabling of the receiver stage

- Remarks: the flag is cleared by changing from RxOnly (failure diagnosis) into normal mode or RxD gets dominant.

#### **TxD to RxD Short Circuit**

- Effect: short circuit between RxD and TxD

- Indicator: NERR = LOW in RxOnly mode (local failure flag is set)

- Action: disabling of the transmitter stage

- Remarks: the flag is cleared by changing from RxOnly (failure diagnosis) into normal mode.

#### **Bus Dominant Clamping**

- Effect: permanent dominant signal at the CAN bus for  $t > t_{BUS}$

- Indicator: NERR = LOW in RxOnly mode (local failure flag is set)

- Action: noneRemarks: none

#### **Overtemperature Detection**

- Effect: junction temperature at the driving stages exceeded

- Indicator: NERR = LOW in RxOnly mode (local failure flag is set)

- Action: disabling of the transmitter stage

- Remarks: the flag is cleared by changing from RxOnly (failure diagnosis) into normal mode or RxD gets dominant. Bus only released after the next dominant bit in TxD.

Final Data Sheet 15 Rev. 3.2, 2006-04-05

#### **Other Features**

## $V_{\text{IIC}}$ -level Adapter

The advantage of the adaptive  $\mu$ C logic is the ratiometrical scaling of the I/O levels depending on the input voltage at the  $V_{\mu C}$  pin. So it can be ensured that the I/O voltage of the  $\mu$ C fits to the internal logic levels of the TLE 6251 G.

#### **WAKE Input**

The wake-up input pin is a bi-level sensitive input. This means that both transitions, HIGH to LOW and LOW to HIGH, result in a wake-up.

## $V_{\rm CC},\,V_{ m uC}$ Undervoltage Detection

If an undervoltage condition at  $V_{\rm CC}$ ,  $V_{\mu\rm C}$  is detected for longer than  $t=t_{\rm UV,t}$ , the TLE 6251 G automatically transfers into the sleep mode and the undervoltage flag is set. This flag is an internal flag and not available via NERR or RxD. The flag is cleared again, after setting the power on or wake flag (power-up or wake-up).

#### $V_{\rm S}$ Undervoltage Detection

If an undervoltage condition at  $V_{\rm S}$  is detected, the TLE 6251 G immediately transfers into the standby mode and the undervoltage flag is set. This flag is an internal flag and not available via NERR or RxD. The flag is cleared again, after the supply voltage  $V_{\rm S}$  has reached the nominal value.

Final Data Sheet 16 Rev. 3.2, 2006-04-05

Figure 6 Mode State Diagram

Table 2Truth Table

| NSTB | EN | INH                | Mode                | Event                                                                                                                | NERR     | RxD                    | SPLIT |

|------|----|--------------------|---------------------|----------------------------------------------------------------------------------------------------------------------|----------|------------------------|-------|

| 1    | 1  |                    |                     | 1                                                                                                                    | LOW: bus | ON                     |       |

|      |    |                    |                     | CAN bus failure <sup>1)</sup>                                                                                        | 0        | dominant,              |       |

|      |    |                    |                     | CANH/CANL driver off <sup>2)</sup>                                                                                   | 1        | HIGH: bus recessive    |       |

|      |    |                    |                     | Wake-up via CAN bus/no wake-up request detected                                                                      | 1        |                        |       |

|      |    |                    |                     | Wake-up via pin WK <sup>3)</sup>                                                                                     | 0        |                        |       |

| 1    | 0  | HIGH               | RECEIVE             | No $V_{\rm BAT}$ fail detected <sup>4)</sup>                                                                         | 1        | LOW: bus               | ON    |

|      |    |                    | ONLY                | $V_{\rm BAT}$ fail detected <sup>4)</sup>                                                                            | 0        | dominant,              |       |

|      |    |                    |                     | No TxD time-out,<br>overtemperature, RxD<br>recessive clamping or bus<br>dominant time out<br>detected <sup>5)</sup> | 1        | HIGH: bus<br>recessive |       |

|      |    |                    |                     | TxD time-out,<br>overtemperature, RxD<br>recessive clamping or bus<br>dominant time out<br>detected <sup>5)</sup>    | 0        |                        |       |

| 0    | 0  | HIGH               | STAND               | Wake-up request detected <sup>6)</sup>                                                                               | 0        | 0                      | OFF   |

|      |    |                    | BY                  | No Wake up request detected <sup>6)</sup>                                                                            | 1        | 1                      |       |

| 0    | 1  | HIGH <sup>7)</sup> | GO TO               | Wake-up request detected <sup>6)</sup>                                                                               | 0        | 0                      | OFF   |

|      |    |                    | SLEEP               | No wake-up request detected <sup>6)</sup>                                                                            | 1        | 1                      |       |

| 0    | 0  | floating           | SLEEP <sup>8)</sup> | Wake-up request detected <sup>6)</sup>                                                                               | 0        | 0                      | OFF   |

|      |    |                    |                     | No wake-up request detected <sup>6)</sup>                                                                            | 1        | 1                      |       |

<sup>1)</sup> Only valid AFTER at least four recessive to dominant edges at TxD after entering the normal mode.

Final Data Sheet 18 Rev. 3.2, 2006-04-05

<sup>2)</sup> Due to an thermal overtemperature shutdown or TxD time-out.

<sup>3)</sup> Only valid BEFORE four recessive to dominant edges at TxD after entering the normal mode.

<sup>4)</sup> Power on situation, valid if  $V_{\rm CC}$  and  $V_{\rm \mu C}$  is active and transition from sleep, stand-by or goto sleep command.

<sup>5)</sup> Transition from normal mode.

<sup>6)</sup> Only valid if  $V_{\rm CC}$  and  $V_{\rm \mu C}$  are active.

<sup>7)</sup> If this mode is selected for a time longer than the hold time of the go-to sleep command  $(t > t_{hSLP})$ , INH is floating.

8) Transition into the sleep mode only if go-to sleep command was selected for a time longer than the hold time of the go-to sleep command  $(t > t_{hSLP})$ .

Final Data Sheet 19 Rev. 3.2, 2006-04-05

Table 3

Absolute Maximum Ratings

| Parameter                                                       | Symbol Limit Values |           | Unit              | Remarks |                                                                                                                                              |  |

|-----------------------------------------------------------------|---------------------|-----------|-------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                 |                     | Min. Max. |                   |         |                                                                                                                                              |  |

| Voltages                                                        | l                   | 1         | -1                | •       |                                                                                                                                              |  |

| Supply voltage                                                  | $V_{ m S}$          | -0.3      | 40                | V       | _                                                                                                                                            |  |

| 5 V supply voltage                                              | $V_{\rm CC}$        | -0.3      | 5.5               | V       | _                                                                                                                                            |  |

| Logic supply voltage                                            | $V_{\mu  m C}$      | -0.3      | 5.5               | V       | _                                                                                                                                            |  |

| CAN bus voltage (CANH,<br>CANL)                                 | $V_{ m CANH/L}$     | -27       | 40                | V       | _                                                                                                                                            |  |

| Differential voltage CANH,<br>CANL, SPLIT, WK                   | $V_{ m diffESD}$    | -40       | 40                | V       | CANH - CANL <  40 V ;<br>CANH - SPLIT <  40 V <br>CANL - SPLIT <  40 V ;<br>CANL - WK <  40 V ;<br>CANH - WK <  40 V ;<br>Split - WK <  40 V |  |

| $V_{ m SPLIT}$ input voltage                                    | $V_{ m SPLIT}$      | -27       | 40                | V       | _                                                                                                                                            |  |

| Input voltage at WK                                             | $V_{ m WK}$         | -27       | 40                | V       | _                                                                                                                                            |  |

| Input voltage at INH                                            | $V_{ m INH}$        | -0.3      | $V_{\rm S} + 0.3$ | V       | _                                                                                                                                            |  |

| Logic voltages at EN, NSTB, NERR, TxD, RxD                      | $V_{ m I}$          | -0.3      | $V_{ m \mu C}$    | V       | $0 \text{ V} < V_{\mu\text{C}} < 5.5 \text{ V}$                                                                                              |  |

| Electrostatic discharge voltage at SPLIT                        | $V_{ m ESD}$        | -1        | 1                 | kV      | human body model<br>(100 pF via 1.5 kΩ)                                                                                                      |  |

| Electrostatic discharge<br>voltage at CANH, CANL,<br>WK vs. GND | $V_{ m ESD}$        | -6        | 6                 | kV      | human body model<br>(100 pF via 1.5 kΩ)                                                                                                      |  |

| Electrostatic discharge voltage for all pin except SPLIT        | $V_{ m ESD}$        | -2        | 2                 | kV      | human body model<br>(100 pF via 1.5 kΩ)                                                                                                      |  |

| Electrostatic discharge voltage at CANH, CANL vs.               | $V_{ m ESD}$        | -6        | 6                 | kV      | According to IEC61000-4-2 (150 pF via $330\Omega$ )<br>See <b>Figure 10</b> <sup>1)</sup>                                                    |  |

| Temperatures                                                    | •                   | •         | •                 |         |                                                                                                                                              |  |

| Storage temperature                                             | $T_{\rm j}$         | -40       | 150               | °C      | _                                                                                                                                            |  |

<sup>1)</sup> application circuits with and without terminated SPLIT pin

Note: Maximum ratings are absolute ratings; exceeding any one of these values may cause irreversible damage to the integrated circuit.

Table 4Operating Range

| Parameter                               | Symbol         | Limit Values |      | Unit | Remarks |  |  |  |  |

|-----------------------------------------|----------------|--------------|------|------|---------|--|--|--|--|

|                                         |                | Min.         | Max. |      |         |  |  |  |  |

| Supply voltage                          | $V_{ m S}$     | 5            | 40   | V    | _       |  |  |  |  |

| 5 V supply voltage                      | $V_{\rm CC}$   | 4.75         | 5.25 | V    | _       |  |  |  |  |

| Logic supply voltage                    | $V_{\mu  m C}$ | 3.0          | 5.25 | V    | _       |  |  |  |  |

| Junction temperature                    | $T_{\rm j}$    | -40          | 150  | °C   | _       |  |  |  |  |

| Thermal Resistances                     |                |              |      |      |         |  |  |  |  |

| Junction ambient                        | $R_{ m thj-a}$ | _            | 120  | K/W  | 1)      |  |  |  |  |

| Thermal Shutdown (junction temperature) |                |              |      |      |         |  |  |  |  |

| Thermal shutdown temp.                  | $T_{ m jSD}$   | 150          | 190  | °C   | _       |  |  |  |  |

| Thermal shutdown hyst.                  | $\Delta T$     | _            | 10   | K    | _       |  |  |  |  |

<sup>1)</sup> Calculation of the junction temperature  $T_{\rm j} = T_{\rm amb} + P \times R_{\rm thj-a}$

Final Data Sheet 21 Rev. 3.2, 2006-04-05

#### Table 5 Electrical Characteristics

4.75 V <  $V_{\rm CC}$  < 5.25 V; 3.0 V <  $V_{\rm \mu C}$  < 5.25 V; 6.0 V <  $V_{\rm S}$  < 40 V;  $R_{\rm L}$  = 60  $\Omega$ ; normal mode; -40 °C <  $T_{\rm j}$  < 150 °C; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                             | Symbol                          | Li   | mit Va | lues | Unit | <b>Test Condition</b>                                                                                               |  |

|-------------------------------------------------------|---------------------------------|------|--------|------|------|---------------------------------------------------------------------------------------------------------------------|--|

|                                                       |                                 | Min. | Typ.   | Max. |      |                                                                                                                     |  |

| <b>Current Consumption</b>                            | 1                               | •    |        |      |      |                                                                                                                     |  |

| Current consumption normal mode                       | $I_{\mathrm{CC}+\mu\mathrm{C}}$ | _    | 6      | 10   | mA   | recessive state;<br>TxD = high                                                                                      |  |

|                                                       | $I_{\mathrm{CC+\mu C}}$         | _    | 50     | 80   | mA   | dominant state;<br>TxD = low                                                                                        |  |

| Current consumption RxD Only mode                     | $I_{\mathrm{CC}+\mu\mathrm{C}}$ | _    | 6      | 10   | mA   | receive only mode                                                                                                   |  |

| Current consumption stand-by mode                     | $I_{ m VS}$                     | _    | 25     | 50   | μΑ   | stand-by mode; $V_{\rm S} = {\rm WK} = 12 {\rm V}$                                                                  |  |

|                                                       | $I_{	ext{CC}+\mu	ext{C}}$       | _    | 25     | 60   | μΑ   | stand-by mode;<br>$V_{\rm S} = {\rm WK} = 12~{\rm V}$<br>$V_{\rm CC} = V_{\rm \mu C} = 5{\rm V}$                    |  |

| Current consumption sleep mode                        | $I_{ m VS}$                     | _    | 25     | 35   | μΑ   | sleep mode, $V_{\rm S} = 12 \text{ V},$ $T_{\rm j} < 85 \text{ °C},$ $V_{\rm CC} = V_{\rm \mu C} = 0 \text{ V}$     |  |

|                                                       | $I_{\mathrm{CC+\mu C}}$         | _    | 2.5    | 10   | μΑ   | sleep mode, $V_{\rm S} = 12 \text{ V},$ $T_{\rm j} < 85 ^{\circ}\text{C},$ $V_{\rm CC} = V_{\rm \mu C} = 5\text{V}$ |  |

| <b>Supply Resets</b>                                  | 1                               | •    | 1      | 1    | •    | ·                                                                                                                   |  |

| $\overline{V_{ m CC}}$ undervoltage detection         | $V_{ m CC,UV}$                  | 2    | 3      | 4    | V    | _                                                                                                                   |  |

| $\overline{V_{\mu \Gamma}}$ undervoltage detection    | $V_{\mu  m C,UV}$               | 0.4  | 1.2    | 1.8  | V    | _                                                                                                                   |  |

| $\overline{V_{\mathrm{S}}}$ power ON detection level  | $V_{ m S,Pon}$                  | 2    | 4      | 5    | V    | _                                                                                                                   |  |

| $\overline{V_{\mathrm{S}}}$ power OFF detection level | $V_{ m S,Poff}$                 | 2    | 3.5    | 5    | V    | _                                                                                                                   |  |

| Receiver Output RxD                                   |                                 |      |        |      |      |                                                                                                                     |  |

| HIGH level output current                             | $I_{ m RD,H}$                   | _    | -4     | -2   | mA   | $V_{\mathrm{RD}} = 0.8 \times V_{\mathrm{\mu C}}$                                                                   |  |

| LOW level output current                              | $I_{ m RD,L}$                   | 2    | 4      | _    | mA   | $V_{\mathrm{RD}} = 0.2 \times V_{\mathrm{\mu C}}$                                                                   |  |

| Short circuit current                                 | $I_{ m SC,RxD}$                 | _    | 70     | 84   | mA   | $V_{\mu C} = 5.25 \text{ V},$<br>RxD = LOW                                                                          |  |

Final Data Sheet 22 Rev. 3.2, 2006-04-05

4.75 V <  $V_{\rm CC}$  < 5.25 V; 3.0 V <  $V_{\rm \mu C}$  < 5.25 V; 6.0 V <  $V_{\rm S}$  < 40 V;  $R_{\rm L}$  = 60  $\Omega$ ; normal mode; -40 °C <  $T_{\rm j}$  < 150 °C; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter             | Symbol          | Limit Values |      |      | Unit | <b>Test Condition</b>                     |

|-----------------------|-----------------|--------------|------|------|------|-------------------------------------------|

|                       |                 | Min.         | Тур. | Max. |      |                                           |

| Short circuit current | $I_{ m SC,RxD}$ | _            | 35   | 45   | mA   | $V_{\mu C} = 3.3 \text{ V},$<br>RxD = LOW |

Final Data Sheet 23 Rev. 3.2, 2006-04-05

4.75 V <  $V_{\rm CC}$  < 5.25 V; 3.0 V <  $V_{\rm \mu C}$  < 5.25 V; 6.0 V <  $V_{\rm S}$  < 40 V;  $R_{\rm L}$  = 60  $\Omega$ ; normal mode; -40 °C <  $T_{\rm j}$  < 150 °C; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| <b>Test Condition</b>             |  |

|-----------------------------------|--|

|                                   |  |

|                                   |  |

| state                             |  |

| t state                           |  |

| ect to<br>on test<br>I by design. |  |

| ,<br>μC                           |  |

|                                   |  |

|                                   |  |

|                                   |  |

|                                   |  |

| ect to<br>on test<br>l by design. |  |

| $_{\mathrm{TB}} = 0\mathrm{V}$    |  |

|                                   |  |

|                                   |  |

| 100 μΑ                            |  |

| .25 mA                            |  |

| 25 V                              |  |

| 3 V                               |  |

| 1                                 |  |

Final Data Sheet 24 Rev. 3.2, 2006-04-05

4.75 V <  $V_{\rm CC}$  < 5.25 V; 3.0 V <  $V_{\rm \mu C}$  < 5.25 V; 6.0 V <  $V_{\rm S}$  < 40 V;  $R_{\rm L}$  = 60  $\Omega$ ; normal mode; -40 °C <  $T_{\rm j}$  < 150 °C; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                                              | Symbol            | Li                      | Limit Values            |                         |    | <b>Test Condition</b>                                               |  |

|------------------------------------------------------------------------|-------------------|-------------------------|-------------------------|-------------------------|----|---------------------------------------------------------------------|--|

|                                                                        |                   | Min.                    | Typ.                    | Max.                    |    |                                                                     |  |

| <b>Termination Output SPLIT</b>                                        | ,                 |                         | JI                      | 1                       |    |                                                                     |  |

| Split output voltage                                                   | $V_{ m SPLIT}$    | $0.3 \times V_{\rm CC}$ | $0.5 \times V_{\rm CC}$ | $0.7 \times V_{\rm CC}$ | V  | normal mode;<br>-500 $\mu$ A $<$ $I_{\rm SPLIT}$ $<$<br>500 $\mu$ A |  |

|                                                                        | $V_{ m SPLIT}$    | $V_{\rm CC}$            | $0.5 \times V_{\rm CC}$ | $V_{\rm CC}$            | V  | normal mode;<br>no load                                             |  |

| Leakage current                                                        | $I_{ m SPLIT}$    | -5                      | 0                       | 5                       | μΑ | sleep mode $V_{\rm CC} = V_{\mu \rm C} = 0 \ { m V}$                |  |

| Output resistance                                                      | $R_{ m SPLIT}$    | _                       | 600                     | _                       | Ω  | _                                                                   |  |

| Wake Input WK                                                          |                   | •                       | •                       | •                       |    |                                                                     |  |

| Wake-up threshold voltage                                              | $V_{ m WK,th}$    | $V_{ m S}$ - 4          | V <sub>S</sub> - 2.5    | V <sub>S</sub> - 2      | V  | $V_{ m NSTB} = 0 \  m V$                                            |  |

| HIGH level input current                                               | $I_{ m WKH}$      | _                       | 5                       | 10                      | μΑ | $V_{ m WK} = V_{ m WK,th} + 1$                                      |  |

| LOW level current                                                      | $I_{ m WKL}$      | -10                     | -5                      | _                       | μΑ | $V_{ m WK} = V_{ m WK,th}$ - 1                                      |  |

| Inhibit Output INH                                                     | ·                 |                         |                         |                         |    | •                                                                   |  |

| HIGH level voltage drop $\Delta V_{\rm H} = V_{\rm S}$ - $V_{\rm INH}$ | $\Delta V_{ m H}$ | _                       | 0.4                     | 0.8                     | V  | $I_{\text{INH}} = -1 \text{ mA}$                                    |  |

| Leakage current                                                        | $I_{ m INH,lk}$   | _                       | _                       | 5                       | μΑ | sleep mode; $V_{\text{INH}} = 0 \text{ V}$                          |  |

| <b>Bus Transmitter</b>                                                 |                   |                         |                         |                         |    | •                                                                   |  |

| CANL/CANH recessive output voltage                                     | $V_{ m CANL/H}$   | 2.0                     | _                       | 3.0                     | V  | no load                                                             |  |

| CANH, CANL recessive output voltage difference                         | $V_{ m diff}$     | -500                    | _                       | 50                      | mV | $V_{ m TxD} = V_{ m \mu C};$ no load                                |  |

| CANL dominant output voltage                                           | $V_{ m CANL}$     | 0.5                     | _                       | 2.25                    | V  | $V_{\text{TxD}} = 0 \text{ V};$                                     |  |

| CANH dominant output voltage                                           | $V_{ m CANH}$     | 2.75                    | _                       | 4.5                     | V  | $V_{\mathrm{TxD}} = 0 \mathrm{\ V}$                                 |  |

| CANH, CANL dominant output voltage difference                          | $V_{ m diff}$     | 1.5                     | _                       | 3.0                     | V  | $V_{\mathrm{TxD}} = 0 \mathrm{\ V}$                                 |  |

Final Data Sheet 25 Rev. 3.2, 2006-04-05

4.75 V <  $V_{\rm CC}$  < 5.25 V; 3.0 V <  $V_{\rm \mu C}$  < 5.25 V; 6.0 V <  $V_{\rm S}$  < 40 V;  $R_{\rm L}$  = 60  $\Omega$ ; normal mode; -40 °C <  $T_{\rm j}$  < 150 °C; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                                | Symbol                  | Li    | mit Val | lues | Unit | <b>Test Condition</b>                                                                                                 |

|----------------------------------------------------------|-------------------------|-------|---------|------|------|-----------------------------------------------------------------------------------------------------------------------|

|                                                          |                         | Min.  | Typ.    | Max. |      |                                                                                                                       |

| CANL short circuit current                               | $I_{\mathrm{CANLsc}}$   | 50    | 80      | 200  | mA   | $V_{\rm CANLshort} = 18 \text{ V}$                                                                                    |

| CANH short circuit current                               | $I_{\mathrm{CANHsc}}$   | -200  | -80     | -50  | mA   | $V_{\text{CANHshort}} = 0 \text{ V}$                                                                                  |

| Leakage current                                          | $I_{\mathrm{CANHL,lk}}$ | -5    | 0       | 5    | μΑ   | $V_{\rm S} = V_{\mu \rm C} = V_{\rm CC} = 0 \ { m V}; \ 0 \ { m V} < V_{ m CANH,L} < 5 \ { m V}$                      |

| Bus Receiver                                             |                         |       |         |      |      | OV V CANH,L V J                                                                                                       |

| Differential receiver threshold                          | $V_{ m diff,rdN}$       | _     | 0.8     | 0.9  | V    | see CMR                                                                                                               |

| voltage,<br>normal mode                                  | $V_{ m diff,drN}$       | 0.5   | 0.6     | _    | V    | see CMR                                                                                                               |

| Differential receiver threshold,                         | $V_{ m diff,rdLP}$      |       | 0.9     | 1.15 | V    | recessive to dominant                                                                                                 |

| low power mode                                           | $V_{ m diff,drLP}$      | 0.4   | 0.8     |      | V    | dominant to recessive                                                                                                 |

| Common Mode Range                                        | CMR                     | -12   | _       | 12   | V    | $V_{\rm CC} = 5 \text{ V}$                                                                                            |

| Differential receiver hysteresis                         | $V_{ m diff,hys}$       | _     | 200     | _    | mV   | _                                                                                                                     |

| CANH, CANL input resistance                              | $R_{\rm i}$             | 10    | 20      | 30   | kΩ   | recessive state                                                                                                       |

| Differential input resistance                            | $R_{ m diff}$           | 20    | 40      | 60   | kΩ   | recessive state                                                                                                       |

| <b>Dynamic CAN-Transceiver C</b>                         | Characteri              | stics |         |      |      |                                                                                                                       |

| Min. hold time go to sleep command                       | $t_{ m hSLP}$           | 8     | 25      | 50   | μs   | _                                                                                                                     |

| Min. wake-up time on pin WK                              | $t_{ m WK}$             | 5     | 10      | 20   | μs   | _                                                                                                                     |

| Min. dominant time for bus wake-up                       | $t_{ m WU}$             | 0.75  | 3       | 5    | μs   | _                                                                                                                     |

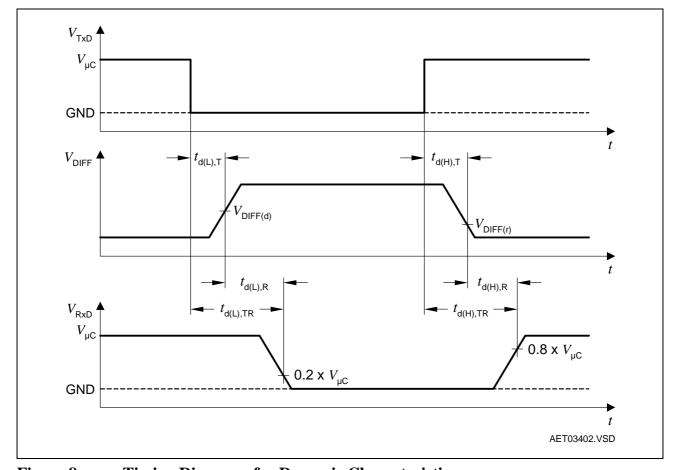

| Propagation delay TxD-to-RxD LOW (recessive to dominant) | $t_{ m d(L),TR}$        | _     | 150     | 255  | ns   | $C_{\rm L}$ = 47 pF;<br>$R_{\rm L}$ = 60 $\Omega$ ;<br>$V_{\rm CC}$ = $V_{\mu \rm C}$ = 5 V;<br>$C_{\rm RxD}$ = 15 pF |

Final Data Sheet 26 Rev. 3.2, 2006-04-05

4.75 V <  $V_{\rm CC}$  < 5.25 V; 3.0 V <  $V_{\rm \mu C}$  < 5.25 V; 6.0 V <  $V_{\rm S}$  < 40 V;  $R_{\rm L}$  = 60  $\Omega$ ; normal mode; -40 °C <  $T_{\rm j}$  < 150 °C; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                                 | Symbol           | Limit Values |      |      | Unit | <b>Test Condition</b>                                                                                                 |  |

|-----------------------------------------------------------|------------------|--------------|------|------|------|-----------------------------------------------------------------------------------------------------------------------|--|

|                                                           |                  | Min.         | Typ. | Max. |      |                                                                                                                       |  |

| Propagation delay TxD-to-RxD HIGH (dominant to recessive) | $t_{ m d(H),TR}$ | _            | 150  | 255  | ns   | $C_{\rm L}$ = 47 pF;<br>$R_{\rm L}$ = 60 $\Omega$ ;<br>$V_{\rm CC}$ = $V_{\mu \rm C}$ = 5 V;<br>$C_{\rm RxD}$ = 15 pF |  |

| Propagation delay TxD LOW to bus dominant                 | $t_{ m d(L),T}$  | _            | 50   | 105  | ns   | $C_{\rm L}$ = 47 pF;<br>$R_{\rm L}$ = 60 $\Omega$ ;<br>$V_{\rm CC}$ = $V_{\mu \rm C}$ = 5 V                           |  |

| Propagation delay TxD HIGH to bus recessive               | $t_{ m d(H),T}$  | _            | 50   | 105  | ns   | $C_{\rm L}$ = 47 pF;<br>$R_{\rm L}$ = 60 $\Omega$ ;<br>$V_{\rm CC}$ = $V_{\mu \rm C}$ = 5 V                           |  |

| Propagation delay bus dominant to RxD LOW                 | $t_{ m d(L),R}$  | -            | 50   | 150  | ns   | $C_{\rm L}$ = 47 pF;<br>$R_{\rm L}$ = 60 $\Omega$ ;<br>$V_{\rm CC}$ = $V_{\mu \rm C}$ = 5 V;<br>$C_{\rm RxD}$ = 15 pF |  |

| Propagation delay bus recessive to RxD HIGH               | $t_{ m d(H),R}$  | -            | 100  | 150  | ns   | $C_{\rm L}$ = 47 pF;<br>$R_{\rm L}$ = 60 $\Omega$ ;<br>$V_{\rm CC}$ = $V_{\mu \rm C}$ = 5 V;<br>$C_{\rm RxD}$ = 15 pF |  |

| TxD permanent dominant disable time                       | $t_{ m TxD}$     | 0.3          | 0.6  | 1.0  | ms   | _                                                                                                                     |  |

| Bus permanent time-out                                    | $t_{ m Bus,t}$   | 0.3          | 0.6  | 1.0  | ms   | _                                                                                                                     |  |

| $V_{\rm CC},V_{\rm \mu C}$ undervoltage filter time       | $t_{ m UV,t}$    | 50           | 80   | 120  | ms   | _                                                                                                                     |  |

Final Data Sheet 27 Rev. 3.2, 2006-04-05

## **Diagrams**

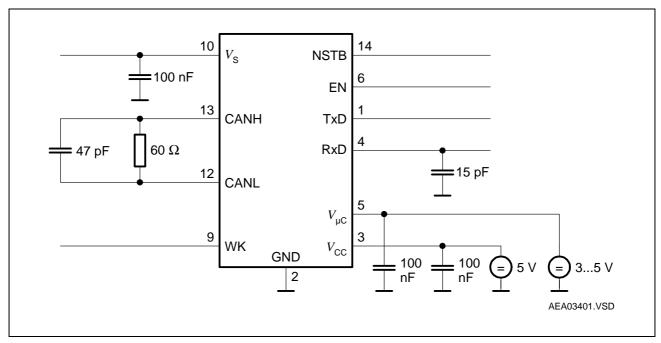

Figure 7 Test Circuit for Dynamic Characteristics

Figure 8 Timing Diagrams for Dynamic Characteristics

Final Data Sheet 28 Rev. 3.2, 2006-04-05

## **Application**

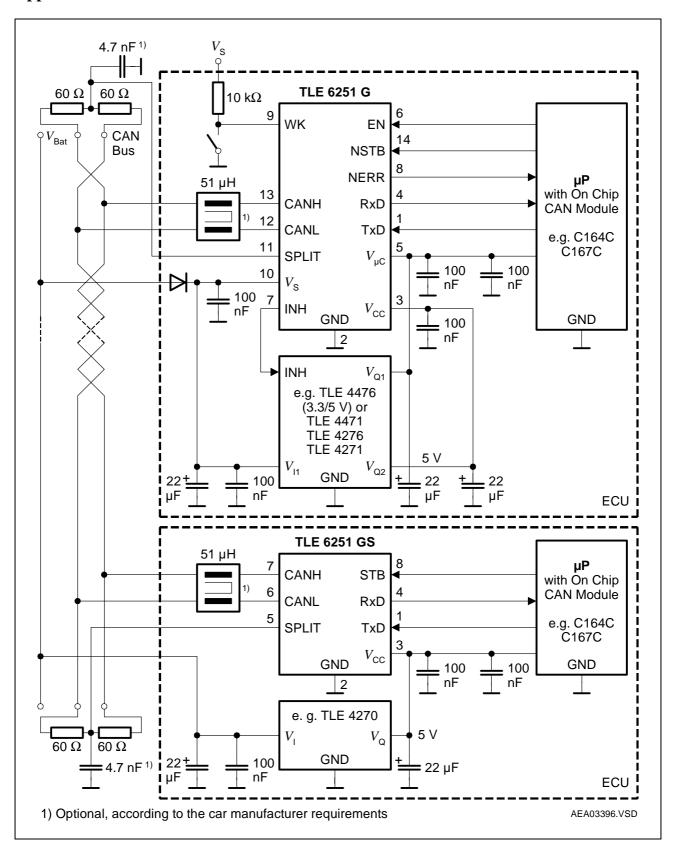

Figure 9 Application Circuit Example

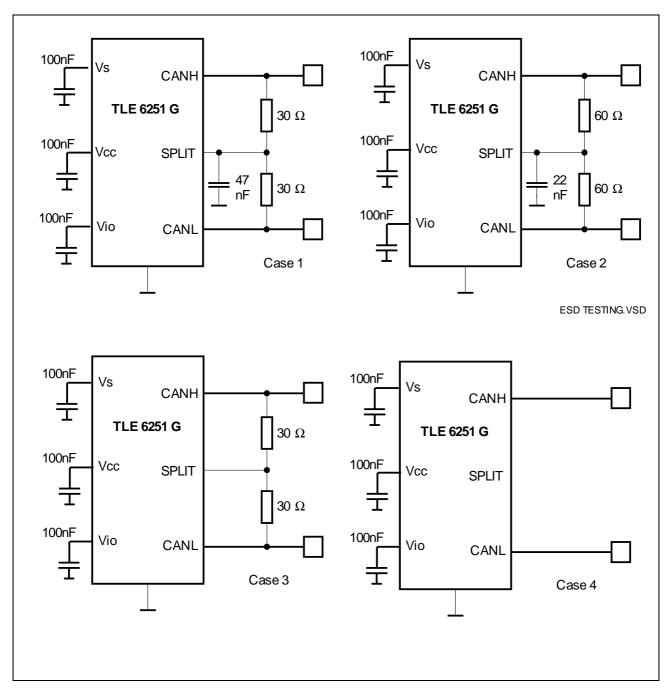

Figure 10 ESD test for conformance to IEC 61000-4-2

The 100nF decoupling capacitors on Vs, Vio and Vcc are situated 5mm from the pins.

The distance between the fixpoint where the Gun is applied and the pin CAN\_H and CAN\_L are 20mm. The test has been realized with NoiseKen ESS2000.

## **Package Outlines**

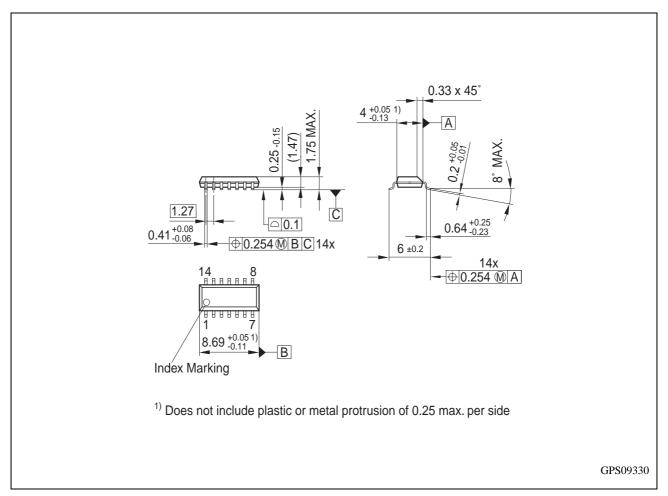

Figure 11 P-DSO-14-13 (Plastic Dual Small Outline)

You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": http://www.infineon.com/products.

SMD = Surface Mounted Device

Dimensions in mm

# AMEYA360 Components Supply Platform

## **Authorized Distribution Brand:**

## Website:

Welcome to visit www.ameya360.com

#### Contact Us:

## > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

#### > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

## Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com