# LC898111AXA LC898111AXB

## CMOS LSI OIS Controller & Driver

#### Overview

The LC898111AXA and the LC898111AXB are image stabilization system control LSIs for smartphone camera modules.

The LSIs have built-in digital signal processing circuits, such as a 2ch saturation H-Bridge Driver and a Flexible Filter circuit, and control VCM type actuators.

The LC898111AXA and the LC898111AXB are identical LSIs except for the dimensions, i.e. XA has WLP thickness, max. 0.33 mm without back coat (B/C) and XB has WLP thickness, max. 0.69 mm with B/C.

#### Function

- Digital signal processing LSI (Logic LSI)

- Built-in digital servo circuit

- Built-in Gyro filter

- AD converter

- 12-bit

- input 5ch

- Equipped with a sample-hold circuit

- DA converter

- 8-bit

- Output 2ch (Constant current Bias : max 7mA)

- Built-in Serial I/F circuit (2-wire I<sup>2</sup>C-Bus or 4-wire SPI Bus interface)

- Built-in Hall Bias circuit

- Built-in Hall Amp (Gain of Opamp : x25, x50, x75, x100, x150, x200)

- Built-in OSC (Oscillator)

- $48MHz \pm 5\%$  (Frequency adjustment function)

- External Clock input is possible from TSTCLK ( $48MHz \pm 5\%$ )

- Built-in LDO (Low Drop-Out regulator)

- Digital Gyro I/F for the companies (SPI Bus)

- (Please refer for the details)

- Support Hall sensor and Photo Reflector as means to detect a position

- Motor Driver

- Saturation-drive H bridge x2ch

- IO max : 220mA

- Package

- LC898111AXA : WLP48J

- (2.57mm x 3.22mm, thickness max 0.33mm, without B/C) • LC898111AXB : WLP48

- LC898111AXB : WL

- (2.57mm x 3.22mm, thickness max 0.69mm, with B/C)

- Pb-free

- Halogen Free

- Power supply voltage

- Logic : DVDD30 = 2.6 to 3.6 V

- Driver : VM = 2.6 to 3.6 V

\* I<sup>2</sup>C Bus is a trademark of Philips Corporation.

WLP48J

WLP48

**ORDERING INFORMATION**

See detailed ordering and shipping information on page 7 of this data sheet.

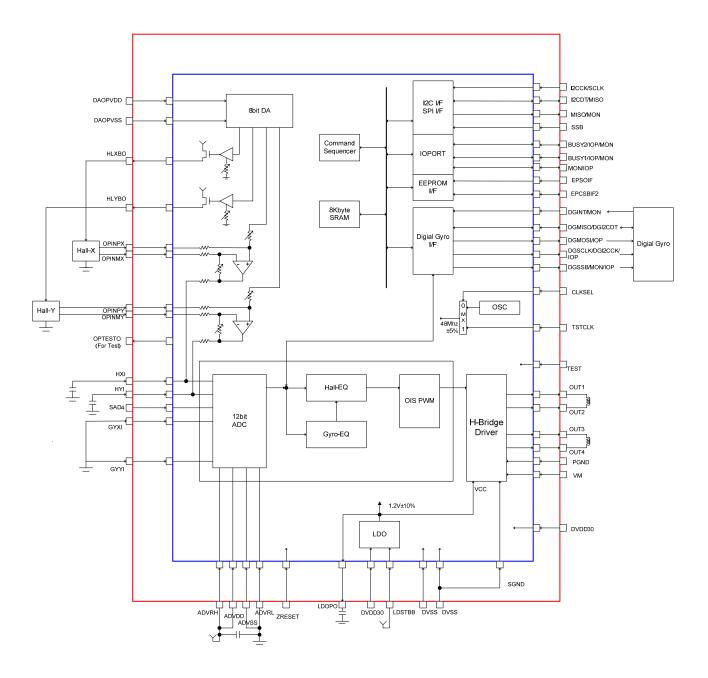

#### **Block Diagram**

Figure 3.1 Example of wiring diagram (Hall) in LC898111AXA/XB

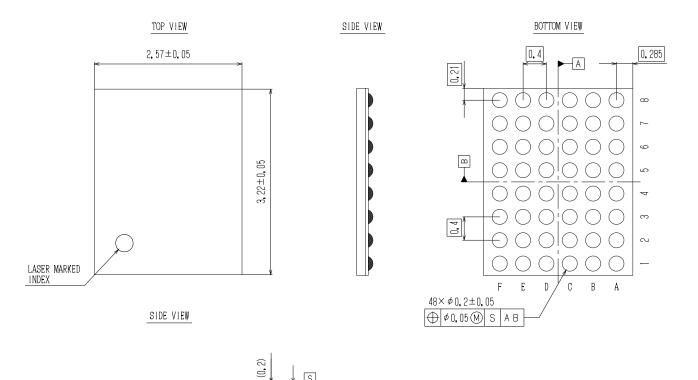

#### LC898111AXA

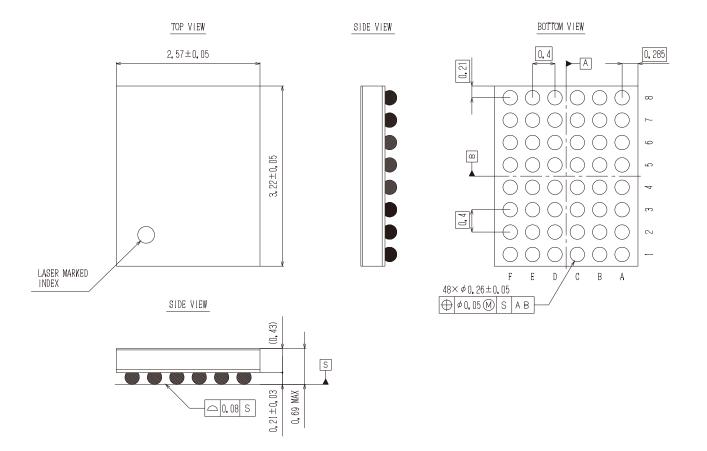

#### PACKAGE DIMENSIONS WLP48J(3.22X2.57)

S

0.33 MAX 0,08±0,05

•.• •

□ 0,08 S

#### LC898111AXB

#### PACKAGE DIMENSIONS WLP48(3.22X2.57)

### Pin Assign (WLP48J/WLP48)

Top View

| 1 | OPTESTO                                                                                               | OPINPY  | ADVDD  | ADVSS  | GYYI     | нхі    |  |

|---|-------------------------------------------------------------------------------------------------------|---------|--------|--------|----------|--------|--|

| 2 | HLXBO                                                                                                 | OPINMY  | ADVRH  | GYXI   | DVSS     | I2CDT  |  |

| 3 | EPSOIF                                                                                                | DAOPVDD | ADVRL  | HYI    | EPCSBIF2 | I2CCK  |  |

| 4 | DVDD30                                                                                                | DAOPVSS | OPINPX | SAD4   | SSB      | MISO   |  |

| 5 | BUSY2                                                                                                 | HLYBO   | OPINMX | ZRESET | LDOPO    | DVDD30 |  |

| 6 | BUSY1                                                                                                 | TEST    | DVSS   | TSTCLK | LDSTBB   | DGSCLK |  |

| 7 | VM                                                                                                    | MON     | CLKSEL | DGMOSI | DGMISO   | DGINT  |  |

| 8 | OUT4                                                                                                  | OUT3    | OUT2   | OUT1   | PGND     | DGSSB  |  |

|   | F                                                                                                     | E       | D      | С      | В        | A      |  |

|   | Driver EEPROM i/f<br>DAC Logic GND<br>OpAmp IO VDD (2.6V to 3.6V)<br>ADC Logic Core VDD (1.14 to 1.26 |         |        |        |          |        |  |

### LC898111AXA, LC898111AXB

| <tvp>I : INPUT.</tvp> | O: OUTPUT. | B: BIDIRECTION, | P : Power, GND |

|-----------------------|------------|-----------------|----------------|

|                       | 0.00.00,   | D. DIDINEOTION, |                |

| Ball<br>No | Pin Name         | type | Description                                                                                                                  |  |  |

|------------|------------------|------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| F8         | OUT4             | 0    | Driver Output                                                                                                                |  |  |

| F7         | VM               | Р    | Driver VDD (2.6V to 3.6V)                                                                                                    |  |  |

| F6         | BUSY1            | В    | EEPROM I/F (at I <sup>2</sup> C type EEPROM ) / BUSY1(O)                                                                     |  |  |

| 55         | DUCVO            |      | / General-purpose IOPORT(B) / inner signal Monitor(O)                                                                        |  |  |

| F5         | BUSY2            | B    | BUSY2(O) / General-purpose IOPORT(B) / inner signal Monitor(O)                                                               |  |  |

| F4         | DVDD30           | P    | Logic IO VDD (2.6V to 3.6V)                                                                                                  |  |  |

| F3<br>F2   | EPSOIF           |      | EEPROM I/F                                                                                                                   |  |  |

| F2<br>F1   | HLXBO<br>OPTESTO | 0    | Hall-X Bias (Current Drive) OpAmp Test out                                                                                   |  |  |

| E8         | OUT3             | 0    | Driver output                                                                                                                |  |  |

| E7         | MON              | B    | inner signal monitor / General-purpose IOPORT                                                                                |  |  |

| E6         | TEST             |      | SPI & External clock case sets "1" other cases set "0"                                                                       |  |  |

| E5         | HLYBO            | 0    | Hall-Y Bias (Current Drive)                                                                                                  |  |  |

| E4         | DAOPVSS          | P    | DA&Opamp VSS                                                                                                                 |  |  |

| E3         | DAOPVDD          | P    | DA&Opamp VDD (2.6V to 3.6V)                                                                                                  |  |  |

| E2         | OPINMY           |      | Hall-Y OpAmp input-                                                                                                          |  |  |

| E1         | OPINPY           |      | Hall-Y OpAmp input+                                                                                                          |  |  |

| D8         | OUT2             | 0    | Driver Output                                                                                                                |  |  |

| D7         | CLKSEL           | 1    | change pin of OSC(0) and External clock(1)                                                                                   |  |  |

| D6         | DVSS             | P    | Logic GND                                                                                                                    |  |  |

| D5         | OPINMX           |      | Hall-X OpAmp input-                                                                                                          |  |  |

| D4         | OPINPX           |      | Hall-X OpAmp input+                                                                                                          |  |  |

| D3         | ADVRL            |      | ADC Reference Voltage Low input                                                                                              |  |  |

| D2         | ADVRH            | -    | ADC Reference Voltage High input                                                                                             |  |  |

| D1         | ADVDD            | P    | AD VDD (2.6V to 3.6V)                                                                                                        |  |  |

| C8         | OUT1             | 0    | Driver Output                                                                                                                |  |  |

| C7         | DGMOSI           | В    | Digital Gyro (4-wire)IF data(O) / HPS Control(O) / General-purpose IOPORT(B)                                                 |  |  |

| C6         | TSTCLK           | I    | CLKSEL=1 : External Clock, CLKSEL=0 : change pin of I <sup>2</sup> C(0) and SPI(1)                                           |  |  |

| C5         | ZRESET           | 1    | Hard Wafer Reset                                                                                                             |  |  |

| C4         | SAD4             | Ι    | General-purpose AD input                                                                                                     |  |  |

| C3         | HYI              | Ι    | Hall-Y AD input                                                                                                              |  |  |

| C2         | GYXI             | Ι    | Gyro-X AD input                                                                                                              |  |  |

| C1         | ADVSS            | Р    | AD GND                                                                                                                       |  |  |

| B8         | PGND             | Р    | Driver GND                                                                                                                   |  |  |

| B7         | DGMISO           | В    | Digital Gyro SPI IF Data( I ) / Digital Gyro I <sup>2</sup> C IF Data(B)                                                     |  |  |

| B6         | LDSTBB           | Ι    | LDO Standby (0 : Standby On, 1 : Standby Off)                                                                                |  |  |

| B5         | LDOPO            | Р    | LDO Power supply out (Logic Core VDD (1.14V to 1.26V))                                                                       |  |  |

| B4         | SSB              | Ι    | SPI I/F Chip Select / VDD fix at I <sup>2</sup> C i/f                                                                        |  |  |

| B3         | EPCSBIF2         | В    | EEPROM I/F                                                                                                                   |  |  |

| B2         | DVSS             | Р    | Logic GND                                                                                                                    |  |  |

| B1         | GYYI             | Ι    | Gyro-Y AD input                                                                                                              |  |  |

| A8         | DGSSB            | В    | Digital Gyro SPI IF Chip Select(O) / inner signal monitor(O) / General-purpose<br>IOPORT(B)                                  |  |  |

| A7         | DGINT            | В    | Digital Gyro SPI IF Data Busy( I ) / inner signal monitor(O) / General-purpose<br>IOPORT(B)                                  |  |  |

| A6         | DGSCLK           | В    | Digital Gyro SPI IF clock (O) / Digital Gyro I <sup>2</sup> C IF clock(O) /<br>HPS Control 1(O) / General-purpose IOPORT (B) |  |  |

| A5         | DVDD30           | Р    | Logic IO VDD (2.6V to 3.6V) and power supply to LDO                                                                          |  |  |

| A4         | MISO             | 0    | SPI I/F Data / General-purpose IOPORT / inner signal monitor                                                                 |  |  |

| A3         | I2CCK            | Ι    | I <sup>2</sup> C_IF clock / SPI IF clock                                                                                     |  |  |

| A2         | I2CDT            | В    | I <sup>2</sup> C_IF Data(B) / SPI IF Data                                                                                    |  |  |

| A1         | HXI              | Ι    | Hall-X AD input                                                                                                              |  |  |

#### ORDERING INFORMATION

| Device         | Package                                       | Shipping (Qty / Packing) |  |

|----------------|-----------------------------------------------|--------------------------|--|

| LC898111AXA-MH | WLP48J(3.22X2.57)<br>(Pb-Free / Halogen Free) | 5000 / Tape & Reel       |  |

| LC898111AXB-MH | WLP48(3.22X2.57)<br>(Pb-Free / Halogen Free)  | 5000 / Tape & Reel       |  |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affimative Action Employeer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **AMEYA360** Components Supply Platform

### Authorized Distribution Brand :

### Website :

Welcome to visit www.ameya360.com

### Contact Us :

### > Address :

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

### > Sales :

- Direct +86 (21) 6401-6692

- Email amall@ameya360.com

- QQ 800077892

- Skype ameyasales1 ameyasales2

### **Customer Service** :

Email service@ameya360.com

### > Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com