# **Dual Input Reset Generator**

#### Description

CAT871, CAT872 are dual input reset generators designed to restart microprocessor and microcontroller based systems when the watchdog timer or other resetting mechanisms have become disabled or failed.

CAT871, CAT872 monitor two inputs and output an active low reset pulse after both inputs have been active (logic low) for a factory preset minimum time. The reset pulse width is 2.2 ms for CAT871 and 70 ms for CAT872. Releasing either input from its active state before the minimum timeout period resets the internal timer and both inputs must return to being active before the timer will restart with a fresh count down.

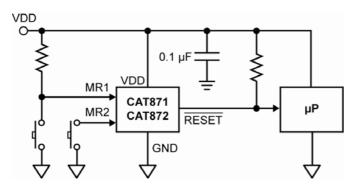

CAT871, CAT872's open drain output is capable of sinking up to 3 mA of current and may be wire-OR'd with other open drain devices to drive a common reset input.

#### **Features**

- Operate on 1.65 V to 5.5 V Power Supplies

- Ultra Low Quiescent Current: 10 nA (typical)

- Schmitt Trigger Inputs

- 8 Factory Preset Delay Times from 0.5 s to 5 s to Choose From

- Small µLLGA-6 Package: 1.45 x 1.0 x 0.4 mm

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

## **Typical Applications**

- Mobile Phones

- PDAs

- MP3 Players

- Personal Navigation Devices

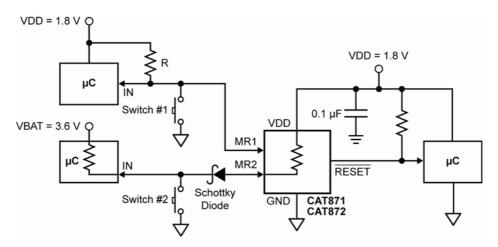

Figure 1. Application Schematic

## ON Semiconductor®

http://onsemi.com

#### **MARKING DIAGRAM**

X = Specific Device Code (J = CAT871, K = CAT872) M = Date Code

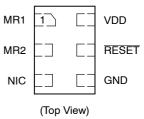

#### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 9 of this data sheet.

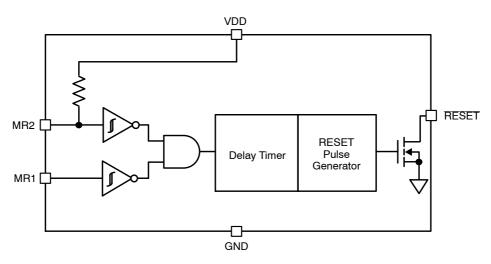

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Functional Block Diagram

**Table 1. PIN FUNCTION DESCRIPTION**

| Pin No. | Pin Name | Description                                                                                              |

|---------|----------|----------------------------------------------------------------------------------------------------------|

| 1       | MR1      | Manual reset input #1. CMOS input.                                                                       |

| 2       | MR2      | Manual reset input #2. CMOS input.                                                                       |

| 3       | NIC      | No Internal Connection. A voltage or signal applied to this pin will have no effect on device operation. |

| 4       | GND      | System Ground.                                                                                           |

| 5       | RESET    | Reset Output. Active-low open drain output.                                                              |

| 6       | VDD      | Positive Power Supply.                                                                                   |

**Table 2. ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                            | Symbol              | Value                                                    | Unit |

|-----------------------------------------------------------------------------------|---------------------|----------------------------------------------------------|------|

| Input Voltage Range                                                               | $V_{DD}$            | -0.3 to 6                                                | V    |

| Output Voltage Range                                                              | V <sub>OUT</sub>    | -0.3 to 6 or (V <sub>DD</sub> + 0.3), whichever is lower | V    |

| Input Voltage; MR2, MR1                                                           | V <sub>IN</sub>     | -0.3 to 6 or (V <sub>DD</sub> + 0.3), whichever is lower | V    |

| Maximum Junction Temperature                                                      | T <sub>J(max)</sub> | 150                                                      | °C   |

| Output Current; RESET                                                             | I <sub>OUT</sub>    | 10                                                       | mA   |

| Storage Temperature Range                                                         | T <sub>STG</sub>    | -65 to 150                                               | °C   |

| ESD Capability, Human Body Model (Note 1)                                         | ESD <sub>HBM</sub>  | 2                                                        | kV   |

| ESD Capability, Machine Model (Note 1)                                            | ESD <sub>MM</sub>   | 200                                                      | V    |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only), Pb-Free Versions (Note 2) | T <sub>SLD</sub>    | 260                                                      | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

- ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

Latch-up Current Maximum Rating: ≤150 mA per JEDEC standard: JESD78

- 2. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

**Table 3. RECOMMENDED OPERATING CONDITIONS**

| Rating                  | Symbol           | Min  | Max      | Unit |

|-------------------------|------------------|------|----------|------|

| Input Voltage; VDD      | $V_{DD}$         | 1.65 | 5.5      | V    |

| Input Voltage; MR1, MR2 | V <sub>IN</sub>  | 0    | $V_{DD}$ | V    |

| Output Current; RESET   | I <sub>OUT</sub> | 0    | 3        | mA   |

| Ambient Temperature     | T <sub>A</sub>   | -40  | 85       | °C   |

## Table 4. ELECTRICAL OPERATING CHARACTERISTICS

$(V_{DD}$  = 1.65 V to 5.5 V. For typical values  $T_A$  = 25°C, for min/max values  $T_A$  = -40°C to +85°C unless otherwise noted.)

| Parameter                                    | Test Conditions                                                                                                                                                                                                         | Symbol                 | Min                   | Тур  | Max                  | Unit |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|------|----------------------|------|

| POWER                                        |                                                                                                                                                                                                                         |                        |                       |      |                      |      |

| V <sub>DD</sub> Supply Voltage               |                                                                                                                                                                                                                         | $V_{DD}$               | 1.65                  |      | 5.5                  | V    |

| Quiescent Supply Current                     | $MR1 = MR2 = V_{DD}$ .                                                                                                                                                                                                  | I <sub>DD</sub>        |                       | 10   | 1000                 | nA   |

| Operating Supply Current                     | Supply Current $ \begin{array}{ll} \text{MR1} = \text{MR2} = 0 \text{ V} \\ \text{Measured during setup period. Measurement includes current through internal 200 k} \\ \text{pull-up resistor on MR2} \\ \end{array} $ |                        |                       |      | 50                   | μΑ   |

| LOGIC INPUTS AND OUTPU                       | its                                                                                                                                                                                                                     |                        |                       |      |                      |      |

| Input Voltage; HIGH                          | MR1, MR2                                                                                                                                                                                                                | V <sub>IH</sub>        | 0.7 x V <sub>DD</sub> |      |                      | V    |

| Input Voltage; LOW                           | MR1, MR2                                                                                                                                                                                                                | V <sub>IL</sub>        |                       |      | 0.25xV <sub>DD</sub> | V    |

| Hysteresis                                   |                                                                                                                                                                                                                         | V <sub>HYS</sub>       | -                     | 250  |                      | mV   |

| Input Current                                | MR1 = 0 V; V <sub>DD</sub> = 5 V (no internal pull-up)                                                                                                                                                                  | I <sub>PU</sub>        |                       | 50   | 300                  | nA   |

| Input Current                                | MR2 = 0 V; $V_{DD}$ = 5 V (internal 200 kΩ pull–up resistor)                                                                                                                                                            | I <sub>PU</sub>        |                       | 25   |                      | μΑ   |

| Output Voltage; HIGH                         | External 10 k $\Omega$ pull–up resistor to $V_{DD}$                                                                                                                                                                     | V <sub>OH</sub>        | V <sub>DD</sub> – 0.1 |      |                      | V    |

| Output Voltage; LOW                          | I <sub>SINK</sub> = 3 mA, V <sub>DD</sub> = 1.8 V                                                                                                                                                                       | V <sub>OL</sub>        |                       | 0.1  | 0.4                  | V    |

| TIMING                                       |                                                                                                                                                                                                                         |                        |                       |      |                      |      |

| Timeout                                      | CAT87x-05                                                                                                                                                                                                               | t <sub>LOW_DELAY</sub> | 0.41                  | 0.50 | 0.59                 | s    |

|                                              | CAT87x-10                                                                                                                                                                                                               |                        | 0.82                  | 1.00 | 1.18                 | S    |

|                                              | CAT87x-15                                                                                                                                                                                                               |                        | 1.23                  | 1.50 | 1.77                 | S    |

|                                              | CAT87x-20                                                                                                                                                                                                               |                        | 1.64                  | 2.00 | 2.36                 | S    |

|                                              | CAT87x-25                                                                                                                                                                                                               |                        | 2.05                  | 2.50 | 2.95                 | S    |

|                                              | CAT87x-30                                                                                                                                                                                                               |                        | 2.46                  | 3.00 | 3.54                 | S    |

|                                              | CAT87x-40                                                                                                                                                                                                               |                        | 3.28                  | 4.00 | 4.72                 | S    |

|                                              | CAT87x-50                                                                                                                                                                                                               |                        | 4.1                   | 5.00 | 5.9                  | S    |

| Reset Output Pulse Width                     | CAT871                                                                                                                                                                                                                  | t <sub>R</sub>         | 1.8                   | 2.2  | 2.6                  | ms   |

|                                              | CAT872                                                                                                                                                                                                                  |                        | 57                    | 70   | 83                   |      |

| <b>TEST MODE</b> (at $T_A = 25^{\circ}C$ ) ( | Note 3)                                                                                                                                                                                                                 |                        |                       |      |                      |      |

| Start TEST window                            |                                                                                                                                                                                                                         | t <sub>ST</sub>        |                       |      | 35                   | μs   |

| Test Mode delay                              | MR1=0 V, MR2→8 cycles, delay measured after 8 <sup>th</sup> rising edge of the MR2 clock pulse                                                                                                                          | t <sub>D</sub>         |                       | 250  |                      | μ\$  |

| Test Mode Clock Frequency                    | Clock applied to MR2                                                                                                                                                                                                    | f <sub>tm</sub>        |                       | 1    |                      | MHz  |

| MR2 Test mode clock setup time               | 2 Test mode clock setup Measured from MR1 falling edge to first                                                                                                                                                         |                        | 1                     |      |                      | μs   |

| MR2 Input Voltage; LOW                       | MR2, Test mode operation                                                                                                                                                                                                | V <sub>IL_TM</sub>     |                       |      | 0.2xV <sub>DD</sub>  | V    |

| MR2 Pulse Width                              |                                                                                                                                                                                                                         | t <sub>pw</sub>        |                       | 500  |                      | ns   |

<sup>3. &</sup>quot;Test Mode" parameters are not tested in production.

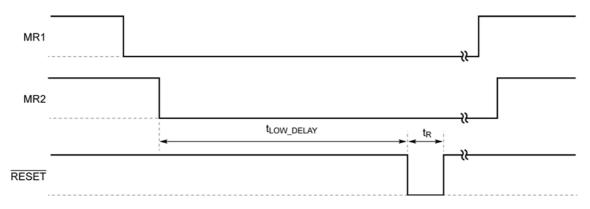

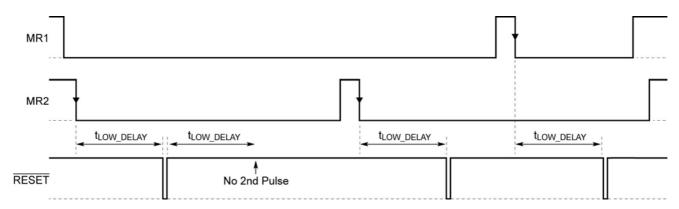

#### TIMING WAVEFORMS (Note 4)

Figure 3. Timing Waveforms

4. The order of the MR inputs going low does not matter. The last input to go low marks the beginning of  $t_{LOW\ DELAY}$

# **TYPICAL CHARACTERISTICS**

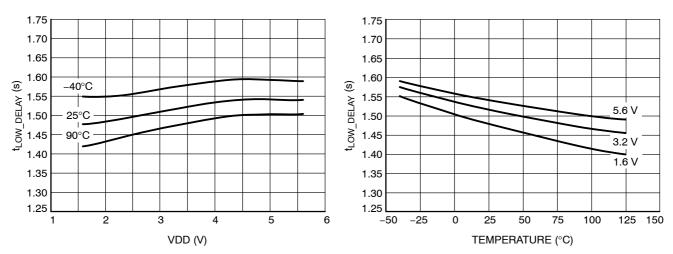

Figure 4. t<sub>LOW DELAY</sub> vs. VDD (CAT87x-1.5)

Figure 5. t<sub>LOW\_DELAY</sub> vs. Temperature (CAT87x-1.5)

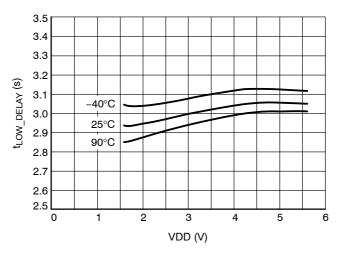

Figure 6. t<sub>LOW\_DELAY</sub> vs. VDD (CAT87x-3.0)

# **TYPICAL CHARACTERISTICS**

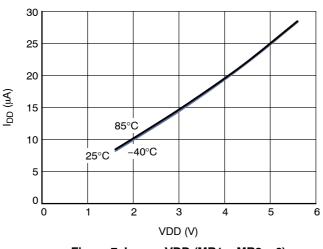

Figure 7. I<sub>DD</sub> vs. VDD (MR1 = MR2 = 0)

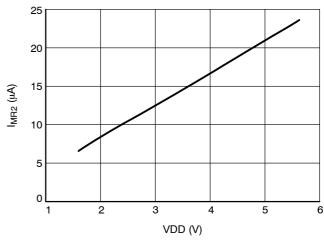

Figure 8. I<sub>MR2</sub> @ MR2 = 0

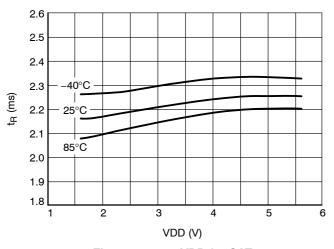

Figure 9. t<sub>R</sub> vs. VDD for CAT871

Figure 10. t<sub>R</sub> vs. Temperature for CAT871

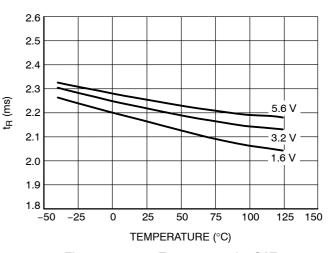

Figure 11. Reset Pulse Width for CAT872

#### SYSTEM DESCRIPTION AND APPLICATIONS INFORMATION

#### General

CAT871, CAT872 are designed for the manual resetting of microprocessors and microcontrollers when normal resetting mechanisms have failed. To prevent accidental resets, CAT871, CAT872 require both manual reset inputs be held low for a prescribed period before a reset pulse is issued to the system processor.

#### **Manual Reset Inputs**

MR1 and MR2 are Schmitt trigger CMOS inputs. Both inputs must go low and stay low for a predetermined period ( $t_{LOW\_DELAY}$ ) to generate a single reset pulse on the output. MR1 and MR2 operate independently and may be brought low at any time and in any order. The last input to reach 0 V starts the delay timer.

MR1 is a standard CMOS input and MR2 is also a CMOS input with an internal 200 k $\Omega$  pull-up resistor, thus MR2 can be left floating whereas MR1 must be biased by a pull-up resistor, powered switch or some other means external to the IC. (Consult factory for other input biasing options)

#### **Delay Timer**

When both MR1 and MR2 go low, an internal timing cycle is initiated. If any input goes high before the countdown timer has concluded its cycle, the timer will reset and will restart from the beginning when MR1 and MR2 return to being low.

If both manual reset inputs (MR1 and MR2) remain low after a reset pulse is issued, no second reset pulse will be issued after that.

#### **Reset Output**

CAT871, CAT872 provide an active-low open drain output to be wire-OR'd with other open drain reset devices. This output will sink up to 3 mA and as such will not be loaded down by low value (strong) pull-up resistors. The reset pulse is typically 2 ms long for CAT871 and 70 ms long for CAT872 and is issued at the conclusion of the delay timer's countdown sequence.

CAT871, CAT872 will not generate a reset pulse at power-up.

#### **Delay Timer Testing**

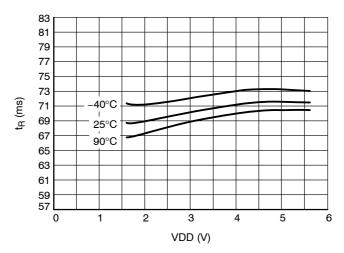

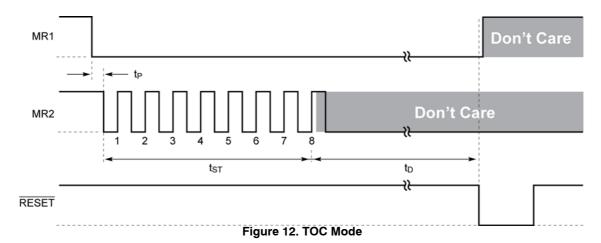

To aid in-circuit testing of the delay timer, a special test function has been included in CAT871, CAT872. This test mode, TOC, allows the delay timer to clock at an accelerated rate. Upon the conclusion of the countdown a standard width reset pulse will be issued and the chip will exit test mode.

To initiate TOC, MR1 $\rightarrow$  0 V and a fast external CLK (typically 1 MHz) is applied on MR2, with the falling edge of the first clock pulse on MR2 delayed with tP from MR1 $\rightarrow$  0 V. CAT871, CAT872 look for 8 sequential pulses to appear on MR2 within 35  $\mu$ s to confirm TOC is desired. After the rising edge of the 8'th pulse, there will be a delay of 250  $\mu$ s typical followed by a standard reset pulse at the reset output. This delay is independent of the normal timeout delay setting.

After issuing the reset pulse, CAT871, CAT872 exit TOC mode and returns to normal operation. If at any time during TOC both MR1 and MR2 are HIGH, CAT871, CAT872 will immediately exit TOC mode.

#### **APPLICATION INFORMATION**

#### **Reset Pulse Operation**

When both MR1 and MR2 inputs are kept low, a single reset pulse is generated after the delay t<sub>LOW\_DELAY</sub>. Even with both MR1 and MR2 maintained low continuously after that time, no second reset pulse will be generated. The delay timer restarts if either MR1 or MR2 (or both) input transitions from high to low, as shown in the timing diagram in Figure 13.

#### System with Two Different Power Supply Voltages

The reset generator can be used in a system where the supply VDD is different than the MR1, MR2 input logic. Figure 14 shows an application schematic where the microcontroller uses a supply VBAT (3.6 V) that is higher

than the VDD rail (1.8 V). MR1 and MR2 inputs are activated here by two separate switches connected to GND and pulling the inputs low when pressed. The Schottky diode provides the supply isolation needed between the CAT871/CAT872 (VDD) and the microcontroller (VBAT).

# Operation with Low VDD Voltage and Brownout Condition

The CAT871, CAT872 reset generators require a minimum supply voltage VDD of 1.65 V to guarantee the normal operation within the specification. To prevent small VDD supply glitch, a small ceramic capacitor can be added between the VDD pin and GND.

Figure 13. Reset Timing Diagram

Figure 14. Application Schematic in Dual Supply System

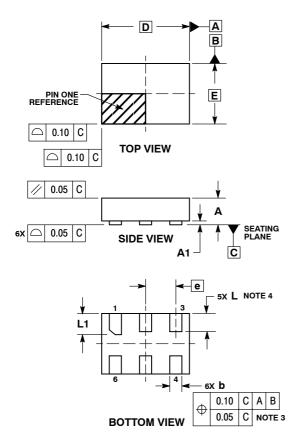

#### PACKAGE DIMENSIONS

ULLGA6, 1.45x1.0, 0.5P CASE 613AF-01 **ISSUE A**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION & APPLIES TO PLATED TERMINAL

AND IS MEASURED BETWEEN 0.15 AND

0.30 mm FROM THE TERMINAL TIP.

4. A MAXIMUM OF 0.05 PULL BACK OF THE

PLATED TERMINAL FROM THE EDGE OF THE

PACKAGE IS ALLOWED. PACKAGE IS ALLOWED.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN MAX     |      |  |  |

| Α   | 0.40        |      |  |  |

| A1  | 0.00        | 0.05 |  |  |

| b   | 0.15        | 0.25 |  |  |

| D   | 1.45        | BSC  |  |  |

| Е   | 1.00 BSC    |      |  |  |

| е   | 0.50 BSC    |      |  |  |

| L   | 0.25        | 0.35 |  |  |

| L1  | 0.30 0.40   |      |  |  |

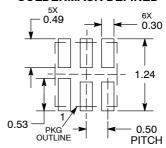

#### **MOUNTING FOOTPRINT** SOLDERMASK DEFINED\*

DIMENSIONS: MILLIMETERS

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

**Table 5. ORDERING INFORMATION**

| Device                  | Timeout (s) | Reset Pulse Width (ms) | Marking | Package   | Shipping (Note 5)   |

|-------------------------|-------------|------------------------|---------|-----------|---------------------|

| CAT871-05ULGT3 (Note 6) | 0.5         | 70                     |         |           |                     |

| CAT871-10ULGT3 (Note 6) | 1           |                        |         |           |                     |

| CAT871-15ULGT3 (Note 6) | 1.5         |                        |         |           |                     |

| CAT871-20ULGT3 (Note 6) | 2           |                        |         |           |                     |

| CAT871-25ULGT3 (Note 6) | 2.5         |                        | JM      |           |                     |

| CAT871-30ULGT3 (Note 6) | 3           |                        |         |           |                     |

| CAT871-40ULGT3 (Note 6) | 4           |                        |         |           |                     |

| CAT871-50ULGT3 (Note 6) | 5           |                        |         | - μLLGA–6 | 3,000 / Tape & Reel |

| CAT872-05ULGT3 (Note 6) | 0.5         |                        |         |           |                     |

| CAT872-10ULGT3 (Note 6) | 1           |                        |         |           |                     |

| CAT872-15ULGT3          | 1.5         |                        |         |           |                     |

| CAT872-20ULGT3 (Note 6) | 2           |                        | IZNA    |           |                     |

| CAT872-25ULGT3 (Note 6) | 2.5         |                        | KM      |           |                     |

| CAT872-30ULGT3          | 3           |                        |         |           |                     |

| CAT872-40ULGT3 (Note 6) | 4           |                        |         |           |                     |

| CAT872-50ULGT3 (Note 6) | 5           |                        |         |           |                     |

For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

<sup>6.</sup> Contact Factory for availability.

# AMEYA360 Components Supply Platform

# **Authorized Distribution Brand:**

# Website:

Welcome to visit www.ameya360.com

# Contact Us:

# > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

# > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

# Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com