# FDMF6706B - Extra-Small, High-Performance, High-Frequency DrMOS Module

#### **Benefits**

- Ultra-Compact 6x6 mm PQFN, 72% Space-Saving Compared to Conventional Discrete Solutions

- Fully Optimized System Efficiency

- Clean Switching Waveforms with Minimal Ringing

- High-Current Handling

#### **Features**

- Over 93% Peak-Efficiency

- High-Current Handling of 45 A

- High-Performance PQFN Copper-Clip Package

- 3-State 3.3 V PWM Input Driver

- Skip-Mode SMOD# (Low-Side Gate Turn Off) Input

- Thermal Warning Flag for Over-Temperature Condition

- Driver Output Disable Function (DISB# Pin)

- Internal Pull-Up and Pull-Down for SMOD# and DISB# Inputs, Respectively

- Fairchild PowerTrench® Technology MOSFETs for Clean Voltage Waveforms and Reduced Ringing

- Fairchild SyncFET™ (Integrated Schottky Diode)

Technology in the Low-Side MOSFET

- Integrated Bootstrap Schottky Diode

- Adaptive Gate Drive Timing for Shoot-Through Protection

- Under-Voltage Lockout (UVLO)

- Optimized for Switching Frequencies up to 1MHz

- Low-Profile SMD Package

- Fairchild Green Packaging and RoHS Compliance

- Based on the Intel® 4.0 DrMOS Standard

# Description

The XS™ DrMOS family is Fairchild's next-generation, fully optimized, ultra-compact, integrated MOSFET plus driver power stage solution for high-current, high-frequency, synchronous buck DC-DC applications. The FDMF6706B integrates a driver IC, two power MOSFETs, and a bootstrap Schottky diode into a thermally enhanced, ultra-compact 6x6 mm PQFN package.

With an integrated approach, the complete switching power stage is optimized for driver and MOSFET dynamic performance, system inductance, and power MOSFET  $R_{DS(ON)}$ .  $XS^{TM}$  DrMOS uses Fairchild's high-performance PowerTrench® MOSFET technology, which dramatically reduces switch ringing, eliminating the snubber circuit in most buck converter applications.

A new driver IC with reduced dead times and propagation delays further enhances performance. A thermal warning function warns of potential overtemperature situations. FDMF6706B also incorporates features such as Skip Mode (SMOD) for improved lightload efficiency, along with a Three-state 3.3 V PWM input for compatibility with a wide range of PWM controllers.

#### **Applications**

- High-Performance Gaming Motherboards

- Compact Blade Servers, V-Core and Non-V-Core DC-DC Converters

- Desktop Computers, V-Core and Non-V-Core DC-DC Converters

- Workstations

- High-Current DC-DC Point-of-Load (POL) Converters

- Networking and Telecom Microprocessor Voltage Regulators

- Small Form-Factor Voltage Regulator Modules

# **Ordering Information**

| Part Number | Current Rating | Package                                               | Top Mark  |

|-------------|----------------|-------------------------------------------------------|-----------|

| FDMF6706B   | 45 A           | 40-Lead, Clipbond PQFN DrMOS, 6.0 mm x 6.0 mm Package | FDMF6706B |

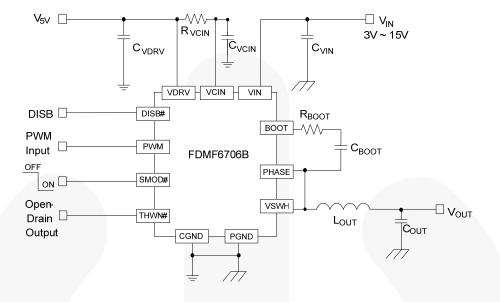

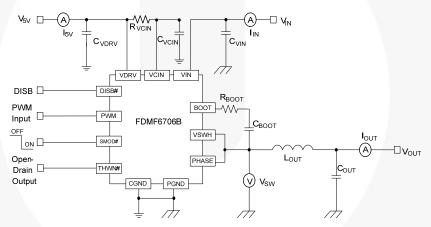

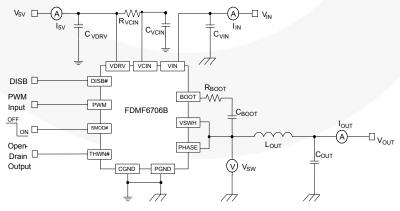

# **Typical Application Circuit**

Figure 1. Typical Application Circuit

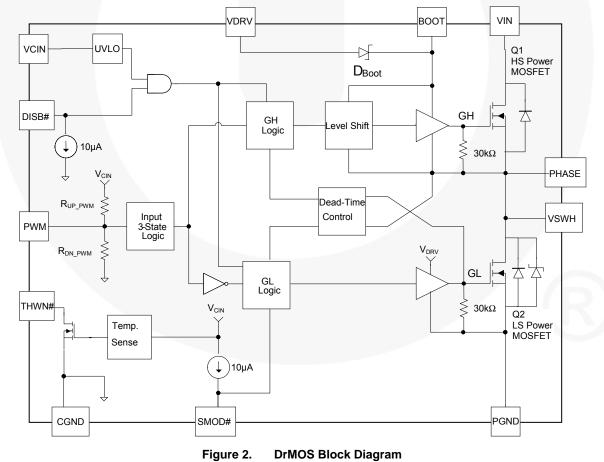

# **DrMOS Block Diagram**

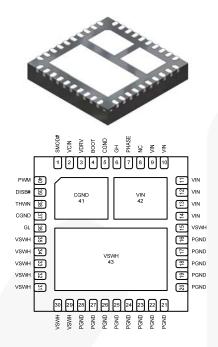

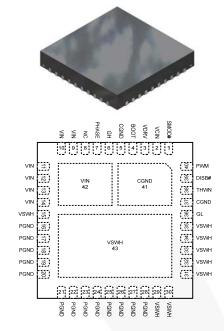

# **Pin Configuration**

Figure 3. Bottom View

Figure 4. Top View

# **Pin Definitions**

| Pin #              | Name  | Description                                                                                                                                                                                                        |  |

|--------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                  | SMOD# | When SMOD#=HIGH, the low-side driver is the inverse of PWM input. When SMOD#=LOW, the low-side driver is disabled. This pin has a 10 $\mu$ A internal pull-up current source. Do not add a noise filter capacitor. |  |

| 2                  | VCIN  | IC bias supply. Minimum 1 μF ceramic capacitor is recommended, from this pin to CGND.                                                                                                                              |  |

| 3                  | VDRV  | Power for gate driver. Minimum 1 $\mu$ F ceramic capacitor is recommended connected as close as possible from this pin to CGND.                                                                                    |  |

| 4                  | воот  | Bootstrap supply input. Provides voltage supply to the high-side MOSFET driver. Connect a bootstrap capacitor from this pin to PHASE.                                                                              |  |

| 5, 37, 41          | CGND  | IC ground. Ground return for driver IC.                                                                                                                                                                            |  |

| 6                  | GH    | For manufacturing test only. This pin must float; must not be connected to any pin.                                                                                                                                |  |

| 7                  | PHASE | Switch node pin for bootstrap capacitor routing. Electrically shorted to VSWH pin.                                                                                                                                 |  |

| 8                  | NC    | No connect. The pin is not electrically connected internally, but can be connected to VIN for convenience.                                                                                                         |  |

| 9 - 14, 42         | VIN   | Power input. Output stage supply voltage.                                                                                                                                                                          |  |

| 15, 29 -<br>35, 43 | VSWH  | Switch node input. Provides return for high-side bootstrapped driver and acts as a sense point for the adaptive shoot-through protection.                                                                          |  |

| 16 – 28            | PGND  | Power ground. Output stage ground. Source pin of the low-side MOSFET.                                                                                                                                              |  |

| 36                 | GL    | For manufacturing test only. This pin must float; must not be connected to any pin.                                                                                                                                |  |

| 38                 | THWN# | THWN# Thermal warning flag, open collector output. When temperature exceeds the trip limit, the output is pulled LOW. THWN# does not disable the module.                                                           |  |

| 39                 | DISB# | Output disable. When LOW, this pin disables the power MOSFET switching (GH and GL are held LOW). This pin has a 10 µA internal pull-down current source. Do not add a noise filter capacitor.                      |  |

| 40                 | PWM   | PWM signal input. This pin accepts a Three-state 3.3 V PWM signal from the controller.                                                                                                                             |  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol             | Pa                                 | rameter                                                                | Min. | Max. | Unit |

|--------------------|------------------------------------|------------------------------------------------------------------------|------|------|------|

| $V_{CIN}$          | Supply Voltage                     | Referenced to CGND                                                     | -0.3 | 6.0  | V    |

| $V_{DRV}$          | Drive Voltage                      | Referenced to CGND                                                     | -0.3 | 6.0  | V    |

| V <sub>DISB#</sub> | Output Disable                     | Referenced to CGND                                                     | -0.3 | 6.0  | V    |

| $V_{PWM}$          | PWM Signal Input                   | Referenced to CGND                                                     | -0.3 | 6.0  | V    |

| V <sub>SMOD#</sub> | Skip Mode Input                    | Referenced to CGND                                                     | -0.3 | 6.0  | V    |

| $V_{GL}$           | Low Gate Manufacturing Test Pin    | Referenced to CGND                                                     | -0.3 | 6.0  | V    |

| V <sub>THWN#</sub> | Thermal Warning Flag               | Referenced to CGND                                                     | -0.3 | 6.0  | V    |

| V <sub>IN</sub>    | Power Input                        | Referenced to PGND, CGND                                               | -0.3 | 25.0 | V    |

|                    | Do atataa a Osaa ah                | Referenced to VSWH, PHASE                                              | -0.3 | 6.0  | V    |

| $V_{BOOT}$         | Bootstrap Supply                   | Referenced to CGND                                                     | -0.3 | 25.0 | V    |

|                    | High Gate Manufacturing Test Pin   | Referenced to VSWH, PHASE                                              | -0.3 | 6.0  | V    |

| $V_{GH}$           |                                    | Referenced to CGND                                                     | -0.3 | 25.0 | V    |

| V <sub>PHS</sub>   | PHASE                              | Referenced to CGND                                                     | -0.3 | 25.0 | V    |

| .,                 | O. Hall Marketon                   | Referenced to PGND, CGND (DC Only)                                     | -0.3 | 25.0 | V    |

| $V_{SWH}$          | Switch Node Input                  | Referenced to PGND, <20 ns                                             | -8.0 | 25.0 | V    |

| V Building         | Do atataa a Osaa ah                | Referenced to VDRV                                                     |      | 22   | V    |

| $V_{BOOT}$         | Bootstrap Supply                   | Referenced to VDRV, <20 ns                                             |      | 25   | V    |

| I <sub>THWN#</sub> | THWN# Sink Current                 |                                                                        | -0.1 | 7.0  | mA   |

|                    | 0.1.10(1)                          | f <sub>SW</sub> =300 kHz, V <sub>IN</sub> =12 V, V <sub>O</sub> =1.0 V |      | 45   |      |

| $I_{O(AV)}$        | Output Current <sup>(1)</sup>      | f <sub>SW</sub> =1 MHz, V <sub>IN</sub> =12 V, V <sub>O</sub> =1.0 V   |      | 40   | A    |

| Ө <sub>ЈРСВ</sub>  | Junction-to-PCB Thermal Resistance |                                                                        |      | 3.5  | °C/W |

| T <sub>A</sub>     | Ambient Temperature Range          |                                                                        | -40  | +125 | °C   |

| $T_J$              | Maximum Junction Temperature       |                                                                        |      | +150 | °C   |

| T <sub>STG</sub>   | Storage Temperature Range          |                                                                        | -55  | +150 | °C   |

|                    | Electronic Discharge Design        | Human Body Model, JESD22-A114                                          | 2000 |      | V ,, |

| ESD                | Electrostatic Discharge Protection | Charged Device Model, JESD22-C101                                      | 1000 |      | - V  |

#### Note:

1.  $I_{O(AV)}$  is rated using Fairchild's DrMOS evaluation board,  $T_A = 25^{\circ}$ C, natural convection cooling. This rating is limited by the peak DrMOS temperature,  $T_J = 150^{\circ}$ C, and varies depending on operating conditions and PCB layout. This rating can be changed with different application settings.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol          | Parameter                         |     | Тур. | Max.                | Unit |

|-----------------|-----------------------------------|-----|------|---------------------|------|

| $V_{CIN}$       | Control Circuit Supply Voltage    |     | 5.0  | 5.5                 | V    |

| $V_{DRV}$       | Gate Drive Circuit Supply Voltage | 4.5 | 5.0  | 5.5                 | V    |

| V <sub>IN</sub> | Output Stage Supply Voltage       | 3.0 | 12.0 | 15.0 <sup>(2)</sup> | V    |

#### Note:

2. Operating at high V<sub>IN</sub> can create excessive AC overshoots on the VSWH-to-GND and BOOT-to-GND nodes during MOSFET switching transients. For reliable DrMOS operation, VSWH-to-GND and BOOT-to-GND must remain at or below the Absolute Maximum Ratings shown in the table above. *Refer to the "Application Information" and "PCB Layout Guidelines" sections of this datasheet for additional information.*

# **Electrical Characteristics**

Typical values are  $V_{IN}$  = 12 V,  $V_{CIN}$  = 5 V,  $V_{DRV}$  = 5 V, and  $T_A$  = +25°C unless otherwise noted.

| Symbol                   | Parameter                                    | Condition                                                                       | Min. | Тур. | Max. | Unit |

|--------------------------|----------------------------------------------|---------------------------------------------------------------------------------|------|------|------|------|

| Basic Oper               | ation                                        |                                                                                 | •    | •    | •    | -    |

| IQ                       | Quiescent Current                            | I <sub>Q</sub> =I <sub>VCIN</sub> +I <sub>VDRV</sub> , PWM=LOW or HIGH or Float |      |      | 2    | mA   |

| UVLO                     | UVLO Threshold                               | V <sub>CIN</sub> Rising                                                         | 2.9  | 3.1  | 3.3  | V    |

| UVLO_ <sub>Hyst</sub>    | UVLO Hysteresis                              |                                                                                 |      | 0.4  |      | V    |

| PWM Input                | $(V_{CIN} = V_{DRV} = 5 V \pm 10\%)$         |                                                                                 |      |      |      |      |

| R <sub>UP_PWM</sub>      | Pull-Up Impedance                            |                                                                                 |      | 26   |      | kΩ   |

| R <sub>DN_PWM</sub>      | Pull-Down Impedance                          |                                                                                 |      | 12   |      | kΩ   |

| $V_{\text{IH\_PWM}}$     | PWM High Level Voltage                       |                                                                                 | 1.88 | 2.25 | 2.61 | V    |

| $V_{TRI\_HI}$            | 3-State Upper Threshold                      |                                                                                 | 1.84 | 2.20 | 2.56 | V    |

| $V_{TRI\_LO}$            | 3-State Lower Threshold                      |                                                                                 | 0.70 | 0.95 | 1.19 | >    |

| $V_{\text{IL\_PWM}}$     | PWM Low Level Voltage                        |                                                                                 | 0.62 | 0.85 | 1.13 | V    |

| t <sub>D_HOLD-OFF</sub>  | 3-State Shut-off Time                        |                                                                                 |      | 160  | 200  | ns   |

| $V_{HiZ\_PWM}$           | 3-State Open Voltage                         |                                                                                 | 1.40 | 1.60 | 1.90 | V    |

| PWM Input                | $(V_{CIN} = V_{DRV} = 5 \text{ V } \pm 5\%)$ |                                                                                 |      |      |      |      |

| R <sub>UP_PWM</sub>      | Pull-Up Impedance                            |                                                                                 |      | 26   |      | kΩ   |

| R <sub>DN_PWM</sub>      | Pull-Down Impedance                          |                                                                                 |      | 12   |      | kΩ   |

| $V_{\text{IH\_PWM}}$     | PWM High Level Voltage                       |                                                                                 | 2.00 | 2.25 | 2.50 | V    |

| $V_{TRI\_HI}$            | 3-State Upper Threshold                      |                                                                                 | 1.94 | 2.20 | 2.46 | V    |

| $V_{TRI\_LO}$            | 3-State Lower Threshold                      |                                                                                 | 0.75 | 0.95 | 1.15 | >    |

| $V_{IL\_PWM}$            | PWM Low Level Voltage                        |                                                                                 | 0.66 | 0.85 | 1.09 | ٧    |

| $t_{\text{D\_HOLD-OFF}}$ | 3-State Shut-off Time                        |                                                                                 |      | 160  | 200  | ns   |

| $V_{\text{HiZ\_PWM}}$    | 3-State Open Voltage                         |                                                                                 | 1.45 | 1.60 | 1.80 | V    |

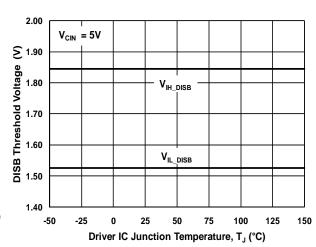

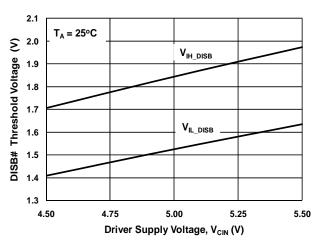

| DISB# Inpu               | t                                            |                                                                                 |      |      |      |      |

| $V_{\text{IH\_DISB}}$    | High-Level Input Voltage                     |                                                                                 | 2    |      |      | V    |

| $V_{IL\_DISB}$           | Low-Level Input Voltage                      |                                                                                 |      |      | 0.8  | V    |

| I <sub>PLD</sub>         | Pull-Down Current                            |                                                                                 |      | 10   |      | μΑ   |

| t <sub>PD_DISBL</sub>    | Propagation Delay                            | PWM=GND, Delay Between DISB# from HIGH to LOW to GL from HIGH to LOW            |      | 25   |      | ns   |

| t <sub>PD_DISBH</sub>    | Propagation Delay                            | PWM=GND, Delay Between DISB# from LOW to HIGH to GL from LOW to HIGH            |      | 25   |      | ns   |

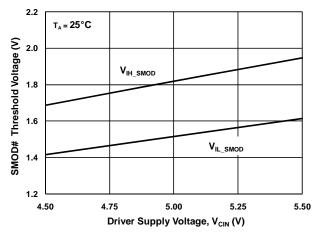

| SMOD# Inp                | ut                                           |                                                                                 |      |      |      |      |

| V <sub>IH_SMOD</sub>     | High-Level Input Voltage                     |                                                                                 | 2    |      |      | V    |

| V <sub>IL_SMOD</sub>     | Low-Level Input Voltage                      |                                                                                 |      |      | 0.8  | V    |

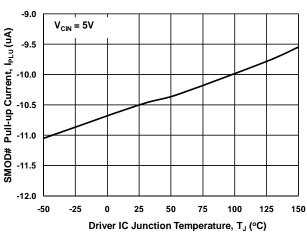

| I <sub>PLU</sub>         | Pull-Up Current                              |                                                                                 |      | 10   |      | μΑ   |

| t <sub>PD_SLGLL</sub>    | Propagation Delay                            | PWM=GND, Delay Between SMOD# from HIGH to LOW to GL from HIGH to LOW            |      | 10   |      | ns   |

| t <sub>PD_SHGLH</sub>    | Propagation Delay                            | PWM=GND, Delay Between SMOD# from LOW to HIGH to GL from LOW to HIGH            |      | 10   |      | ns   |

Continued on the following page...

# **Electrical Characteristics**

Typical values are  $V_{IN}$  = 12 V,  $V_{CIN}$  = 5 V,  $V_{DRV}$  = 5 V, and  $T_A$  = +25°C unless otherwise noted.

| Symbol                 | Parameter                                      | Condition                                                                     | Min. | Тур. | Max. | Unit |

|------------------------|------------------------------------------------|-------------------------------------------------------------------------------|------|------|------|------|

| Thermal Wa             | arning Flag                                    |                                                                               | 1    |      |      | I    |

| T <sub>ACT</sub>       | Activation Temperature                         |                                                                               |      | 150  |      | °C   |

| T <sub>RST</sub>       | Reset Temperature                              |                                                                               |      | 135  |      | °C   |

| R <sub>THWN</sub>      | Pull-Down Resistance                           | I <sub>PLD</sub> =5 mA                                                        |      | 30   |      | Ω    |

| 250ns Time             | out Circuit                                    |                                                                               | •    |      |      | •    |

| t <sub>D_TIMEOUT</sub> | Timeout Delay                                  | SW=0 V, Delay Between GH from HIGH to LOW and GL from LOW to HIGH             |      | 250  |      | ns   |

| High-Side [            | Driver                                         |                                                                               |      |      |      |      |

| R <sub>SOURCE_GH</sub> | Output Impedance, Sourcing                     | Source Current=100 mA                                                         |      | 1    |      | Ω    |

| R <sub>SINK_GH</sub>   | Output Impedance, Sinking                      | Sink Current=100 mA                                                           |      | 0.8  |      | Ω    |

| t <sub>R_GH</sub>      | Rise Time                                      | GH=10% to 90%, C <sub>LOAD</sub> =1.1 nF                                      |      | 6    |      | ns   |

| t <sub>F_GH</sub>      | Fall Time                                      | GH=90% to 10%, C <sub>LOAD</sub> =1.1 nF                                      |      | 5    |      | ns   |

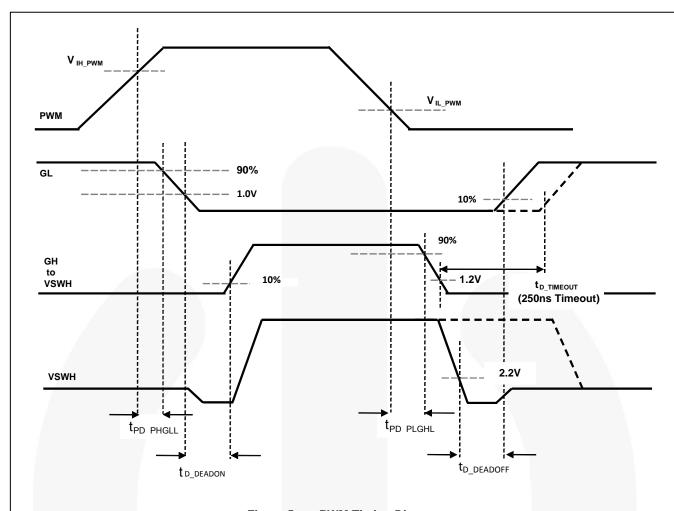

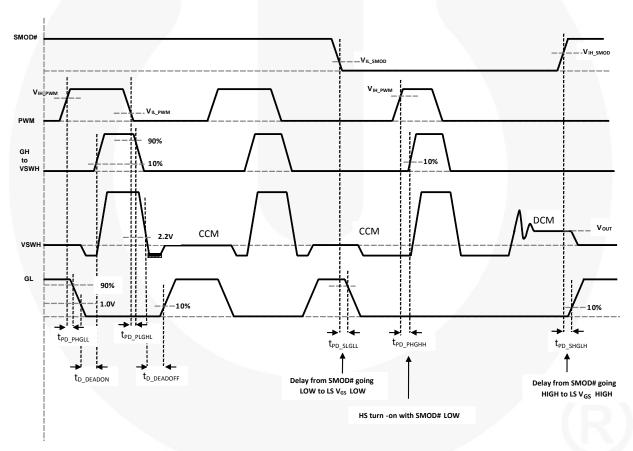

| t <sub>D_DEADON</sub>  | LS to HS Deadband Time                         | GL going LOW to GH going HIGH,<br>1 V GL to 10 % GH                           |      | 10   |      | ns   |

| t <sub>PD_PLGHL</sub>  | PWM LOW Propagation<br>Delay                   | PWM going LOW to GH going LOW, V <sub>IL_PWM</sub> to 90% GH                  |      | 16   | 30   | ns   |

| t <sub>PD_PHGHH</sub>  | PWM HIGH Propagation<br>Delay (SMOD# Held LOW) | PWM going HIGH to GH going HIGH,<br>V <sub>IH_PWM</sub> to 10% GH (SMOD#=LOW) |      | 30   |      | ns   |

| t <sub>PD_TSGHH</sub>  | Exiting 3-State Propagation Delay              | PWM (From 3-State) going HIGH to GH going HIGH, V <sub>IH_PWM</sub> to 10% GH |      | 30   |      | ns   |

| Low-Side D             | river                                          |                                                                               |      |      |      |      |

| R <sub>SOURCE_GL</sub> | Output Impedance, Sourcing                     | Source Current=100 mA                                                         |      | 1    |      | Ω    |

| R <sub>SINK_GL</sub>   | Output Impedance, Sinking                      | Sink Current=100 mA                                                           |      | 0.5  |      | Ω    |

| t <sub>R_GL</sub>      | Rise Time                                      | GL=10% to 90%, C <sub>LOAD</sub> =4.5 nF                                      |      | 14   |      | ns   |

| t <sub>F_GL</sub>      | Fall Time                                      | GL=90% to 10%, C <sub>LOAD</sub> =4.5 nF                                      |      | 10   |      | ns   |

| t <sub>D_DEADOFF</sub> | HS to LS Deadband Time                         | SW going LOW to GL going HIGH, 2.2 V SW to 10% GL                             |      | 12   |      | ns   |

| t <sub>PD_PHGLL</sub>  | PWM-HIGH Propagation<br>Delay                  | PWM going HIGH to GL going LOW,<br>V <sub>IH_PWM</sub> to 90% GL              |      | 9    | 25   | ns   |

| t <sub>PD_TSGLH</sub>  | Exiting 3-State Propagation Delay              | PWM (From 3-State) going LOW to GL going HIGH, V <sub>IL_PWM</sub> to 10% GL  |      | 20   |      | ns   |

| <b>Boot Diode</b>      |                                                |                                                                               |      |      |      |      |

| $V_{F}$                | Forward-Voltage Drop                           | I <sub>F</sub> =10 mA                                                         |      | 0.35 |      | V    |

| $V_{R}$                | Breakdown Voltage                              | I <sub>R</sub> =1 mA                                                          | 22   |      |      | V    |

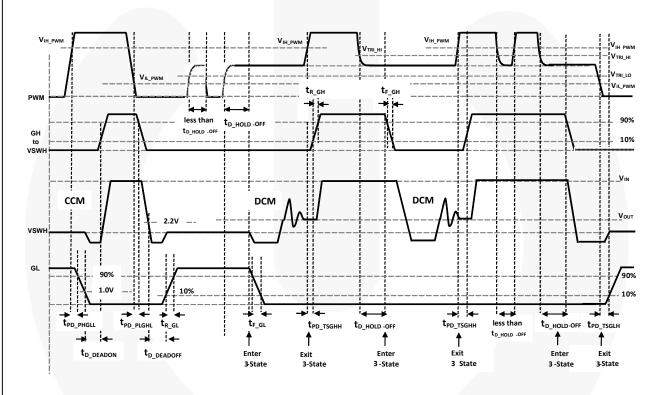

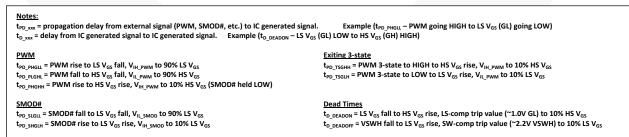

Figure 5. PWM Timing Diagram

# **Typical Performance Characteristics**

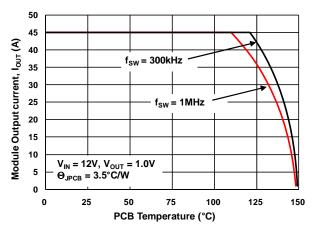

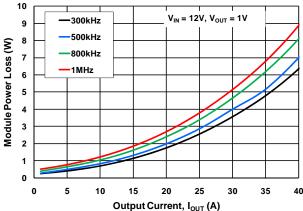

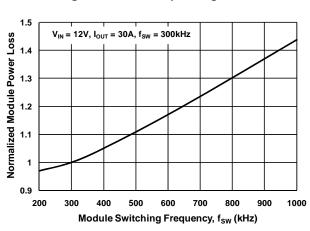

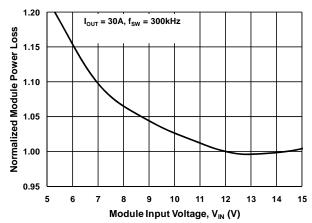

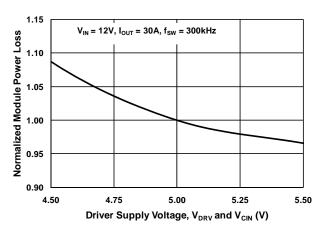

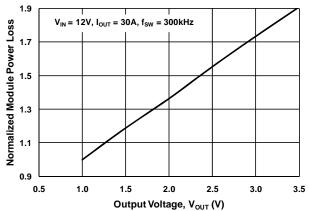

Test Conditions:  $V_{IN}=12 \text{ V}$ ,  $V_{OUT}=1.0 \text{ V}$ ,  $V_{CIN}=5 \text{ V}$ ,  $V_{DRV}=5 \text{ V}$ ,  $V_{OUT}=320 \text{ nH}$ ,  $V_{A}=25^{\circ}\text{C}$ , and natural convection cooling, unless otherwise specified.

Figure 6. Safe Operating Area

Figure 7. Module Power Loss vs. Output Current

Figure 8. Power Loss vs. Switching Frequency

Figure 9. Power Loss vs. Input Voltage

Figure 10. Power Loss vs. Driver Supply Voltage

Figure 11. Power Loss vs. Output Voltage

# Typical Performance Characteristics (Continued)

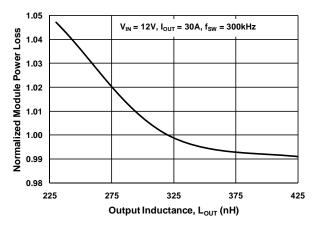

Test Conditions:  $V_{IN}$ =12 V,  $V_{OUT}$ =1.0 V,  $V_{CIN}$ =5 V,  $V_{DRV}$ =5 V,  $L_{OUT}$ =320 nH,  $T_A$ =25°C, and natural convection cooling, unless otherwise specified.

Figure 12. Power Loss vs. Output Inductance

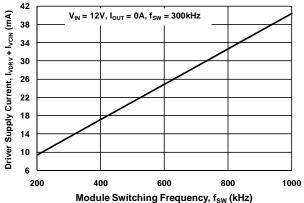

Figure 13. Driver Supply Current vs. Frequency

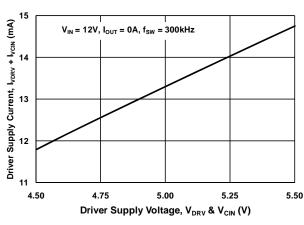

Figure 14. Driver Supply Current vs. Driver Supply Voltage

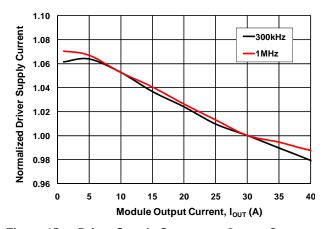

Figure 15. Driver Supply Current vs. Output Current

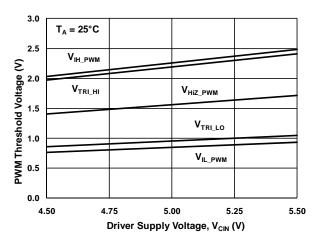

Figure 16. PWM Thresholds vs. Driver Supply Voltage

Figure 17. PWM Thresholds vs. Temperature

# Typical Performance Characteristics (Continued)

Test Conditions:  $V_{IN}$ =12 V,  $V_{OUT}$ =1.0 V,  $V_{CIN}$ =5 V,  $V_{DRV}$ =5 V,  $L_{OUT}$ =320 nH,  $T_A$ =25°C, and natural convection cooling, unless otherwise specified.

$V_{CIN} = 5V$ € <sup>1.9</sup> SMOD Threshold Voltage 7.1 1.1 1.1 8.1 8.1 VIH SMOD  $\mathbf{V}_{\mathsf{IL\_SMOD}}$ 1.3 -50 -25 0 25 50 75 100 125 150 Driver IC Junction Temperature (°C)

Figure 18. SMOD# Thresholds vs. Driver Supply Voltage

Figure 19. SMOD# Thresholds vs. Temperature

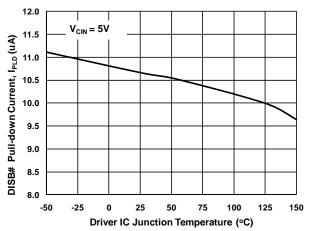

Figure 20. SMOD# Pull-Up Current vs. Temperature

Figure 21. Disable Thresholds vs. Driver Supply Voltage

Figure 22. Disable Thresholds vs. Temperature

Figure 23. Disable Pull-Down Current vs. Temperature

# **Functional Description**

The FDMF6706B is a driver-plus-FET module optimized for the synchronous buck converter topology. A single PWM input signal is all that is required to properly drive the high-side and the low-side MOSFETs. Each part is capable of driving speeds up to 1 MHz.

#### VCIN and Disable (DISB#)

The VCIN pin is monitored by an Under-Voltage Lockout (UVLO) circuit. When  $V_{\text{CIN}}$  rises above ~3.1 V, the driver is enabled. When  $V_{\text{CIN}}$  falls below ~2.7 V, the driver is disabled (GH, GL=0). The driver can also be disabled by pulling the DISB# pin LOW (DISB# <  $V_{\text{IL\_DISB}}$ ), which holds both GL and GH LOW regardless of the PWM input state. The driver can be enabled by raising the DISB# pin voltage HIGH (DISB# >  $V_{\text{IH\_DISB}}$ ).

Table 1. UVLO and Disable Logic

| UVLO | DISB# | Driver State          |

|------|-------|-----------------------|

| 0    | Х     | Disabled (GH, GL=0)   |

| 1    | 0     | Disabled (GH, GL=0)   |

| 1    | 1     | Enabled (See Table 2) |

| 1    | Open  | Disabled (GH, GL=0)   |

#### Note:

3. DISB# internal pull-down current source is 10  $\mu$ A.

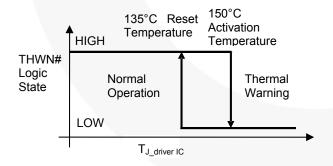

#### Thermal Warning Flag (THWN#)

The FDMF6706B provides a thermal warning flag (THWN#) to advise of over-temperature conditions. The thermal warning flag uses an open-drain output that pulls to CGND when the activation temperature (150°C) is reached. The THWN# output returns to high-impedance state once the temperature falls to the reset temperature (135°C). The THWN# output requires a pull-up resistor, which can be connected to VCIN. THWN# does NOT disable the DrMOS module.

Figure 24. THWN Operation

#### **Three-State PWM Input**

The FDMF6706B incorporates a three-state 3.3 V PWM input gate drive design. The Three-state gate drive has both logic HIGH level and LOW level, along with a 3-state shutdown window. When the PWM input signal enters and remains within the three-state window for a defined hold-off time ( $t_{D\_HOLD\text{-}OFF}$ ), both GL and GH are pulled LOW. This feature enables the gate drive to shut down both high-and low-side MOSFETs to support features such as phase shedding, a common feature on multi-phase voltage regulators.

#### **Exiting Three-State Condition**

When exiting a valid three-state condition, the FDMF6706B design follows the PWM input command. If the PWM input goes from three-state to LOW, the low-side MOSFET is turned on. If the PWM input goes from 3-state to HIGH, the high-side MOSFET is turned on, as illustrated in Figure 25. The FDMF6706B design allows for short propagation delays when exiting the three-state window (see Electrical Characteristics).

#### Low-Side Driver

The low-side driver (GL) is designed to drive a ground-referenced low  $R_{DS(ON)}$  N-channel MOSFET. The bias for GL is internally connected between VDRV and CGND. When the driver is enabled, the driver's output is 180° out of phase with the PWM input. When the driver is disabled (DISB#=0 V), GL is held LOW.

#### **High-Side Driver**

The high-side driver is designed to drive a floating Nchannel MOSFET. The bias voltage for the high-side driver is developed by a bootstrap supply circuit consisting of the internal Schottky diode and external bootstrap capacitor (CBOOT). During startup, VSWH is held at PGND, allowing  $C_{\text{BOOT}}$  to charge to  $V_{\text{DRV}}$  through the internal diode. When the PWM input goes HIGH, GH begins to charge the gate of the high-side MOSFET (Q1). During this transition, the charge is removed from CBOOT and delivered to the gate of Q1. As Q1 turns on,  $V_{\text{SWH}}$  rises to  $V_{\text{IN}}$ , forcing the BOOT pin to  $V_{IN}$  +  $V_{BOOT}$ , which provides sufficient  $V_{GS}$ enhancement for Q1. To complete the switching cycle, Q1 is turned off by pulling GH to  $V_{\text{SWH}}$ .  $C_{\text{BOOT}}$  is then recharged to V<sub>DRV</sub> when V<sub>SWH</sub> falls to PGND. GH output is in-phase with the PWM input. The high-side gate is held LOW when the driver is disabled or the PWM signal is held within the three-state window for longer than the three-state hold-off time, t<sub>D HOLD-OFF</sub>.

#### **Adaptive Gate Drive Circuit**

The driver IC design ensures minimum MOSFET dead time, while eliminating potential shoot-through (cross-conduction) currents. It senses the state of the MOSFETs and adjusts the gate drive adaptively to prevent simultaneous conduction. Figure 25 provides the relevant timing waveforms. To prevent overlap during the LOW-to-HIGH switching transition (Q2 off to Q1 on), the adaptive circuitry monitors the voltage at the GL pin. When the PWM signal goes HIGH, Q2 turns off after a propagation delay (tpD\_PHGLL). Once the GL pin is discharged below ~1 V, Q1 turns on after adaptive delay, tD DEADON.

To prevent overlap during the HIGH-to-LOW transition (Q1 off to Q2 on), the adaptive circuitry monitors the voltage at the VSWH pin. When the PWM signal goes LOW, Q1 turns off after a propagation delay ( $t_{\text{PD\_PLGHL}}$ ). Once the VSWH pin falls below ~2.2 V, Q2 turns on after adaptive delay  $t_{\text{D\_DEADOFF}}$ . Additionally,  $V_{\text{GS(Q1)}}$  is monitored. When  $V_{\text{GS(Q1)}}$  is discharged below ~1.2 V, a secondary adaptive delay is initiated that results in Q2 being driven on after  $t_{\text{D\_TIMEOUT}}$ , regardless of VSWH state. This function ensures  $C_{\text{BOOT}}$  is recharged each switching cycle in the event that the VSWH voltage does not fall below the 2.2 V adaptive threshold. Secondary delay,  $t_{\text{D\_TIMEOUT}}$  is longer than  $t_{\text{D\_DEADOFF}}$ .

Figure 25. PWM and 3-StateTiming Diagram

#### Skip Mode (SMOD)

The SMOD function allows higher converter efficiency under light-load conditions. During SMOD, the low-side FET gate signal is disabled (held LOW), preventing discharging of the output capacitors as the filter inductor current attempts reverse current flow – also known as Diode Emulation Mode.

When the SMOD# pin is pulled HIGH, the synchronous buck converter will work in Synchronous Mode. This mode allows for gating on the low-side FET. When the SMOD# pin is pulled LOW, the low-side FET is gated off. If the SMOD# pin is connected to the PWM controller, the controller can actively enable or disable SMOD when the controller detects light-load condition from output current sensing. This pin is active LOW. See Figure 26 for timing delays.

Table 2. SMOD Logic

| DISB# | PWM     | SMOD# | GH | GL |

|-------|---------|-------|----|----|

| 0     | Х       | Х     | 0  | 0  |

| 1     | 3-State | X     | 0  | 0  |

| 1     | 0       | 0     | 0  | 0  |

| 1     | 1       | 0     | 1  | 0  |

| 1     | 0       | 1     | 0  | 1  |

| 1     | 1       | 1     | 1  | 0  |

#### Note:

The SMOD feature is intended to have low propagation delay between the SMOD signal and the low-side FET V<sub>GS</sub> response time to control diode emulation on a cycle-by-cycle basis.

Figure 26. SMOD Timing Diagram

### **Application Information**

#### **Supply Capacitor Selection**

For the supply inputs (VDRV & VCIN), a local ceramic bypass capacitor is required to reduce noise and to supply peak transient currents during gate drive switching action. It is recommended to use a minimum capacitor value of 1  $\mu$ F X7R or X5R. Keep this capacitor close to the VCIN and VDRV pins and connect it to the GND plane with vias.

#### **Bootstrap Circuit**

The bootstrap circuit uses a charge storage capacitor ( $C_{BOOT}$ ), as shown in Figure 28. A capacitance of 100 nF X7R or X5R capacitor is typically adequate. A series bootstrap resistor may be needed for specific applications to improve switching noise immunity. The boot resistor ( $R_{BOOT}$ ) may be required when operating near the maximum rated  $V_{IN}$  and is effective at controlling the high-side MOSFET turn-on slew rate and VSHW overshoot. Typical  $R_{BOOT}$  values from 0.5 to 2.0 W are effective in reducing VSWH overshoot.

#### **VCIN Filter**

The VDRV pin provides power to the gate drive of the high-side and low-side power MOSFETs. In most cases, VDRV can be connected directly to VCIN, which supplies power to the logic circuitry of the gate driver. For additional noise immunity, an RC filter can be inserted between VDRV and VCIN. Recommended values of 10  $\Omega$  (R<sub>VCIN</sub>) placed between VDRV and VCIN and 1  $\mu$ F (C<sub>VCIN</sub>) from VCIN to CGND, Figure 27.

#### **Power Loss and Efficiency**

#### **Measurement and Calculation**

Refer to Figure 28 for power loss testing method. Power loss calculations are:

$$P_{IN} = (V_{IN} \times I_{IN}) + (V_{5V} \times I_{5V}) (W)$$

(1)

$$P_{SW}=V_{SW} \times I_{OUT} (W)$$

(2)

$$P_{OUT} = V_{OUT} \times I_{OUT} (W)$$

(3)

$$P_{LOSS\_MODULE} = P_{IN} - P_{SW} (W)$$

(4)

$$P_{LOSS\_BOARD} = P_{IN} - P_{OUT}(W)$$

(5)

$$EFF_{MODULE}=100 \times P_{SW}/P_{IN} (\%)$$

(6)

$$EFF_{BOARD}=100 \times P_{OUT}/P_{IN} (\%)$$

(7)

Figure 27. Block Diagram With V<sub>CIN</sub> Filter

Figure 28. Power Loss Measurement

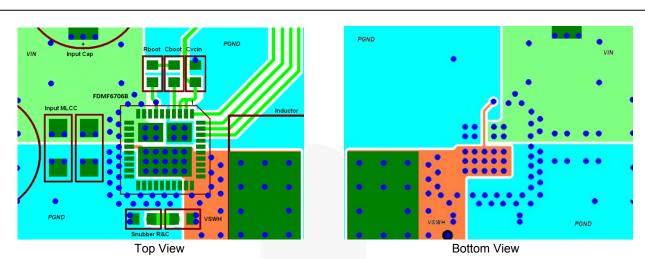

# **PCB Layout Guidelines**

Figure 29 provides an example of a proper layout for the FDMF6706B and critical components. All of the high-current paths, such as  $V_{\text{IN}}$ ,  $V_{\text{SWH}}$ ,  $V_{\text{OUT}}$ , and GND copper, should be short and wide for low inductance and resistance. This technique achieves a more stable and evenly distributed current flow, along with enhanced heat radiation and system performance.

The following guidelines are recommendations for the PCB designer:

- Input ceramic bypass capacitors must be placed close to the VIN and PGND pins. This helps reduce the high-current power loop inductance and the input current ripple induced by the power MOSFET switching operation.

- 2. The V<sub>SWH</sub> copper trace serves two purposes. In addition to being the high-frequency current path from the DrMOS package to the output inductor, it also serves as a heat sink for the low-side MOSFET in the DrMOS package. The trace should be short and wide enough to present a low-impedance path for the high-frequency, high-current flow between the DrMOS and inductor to minimize losses and temperature rise. Note that the VSWH node is a high-voltage and high-frequency switching node with high noise potential. Care should be taken to minimize coupling to adjacent traces. Since this copper trace also acts as a heat sink for the lower FET, balance using the largest area possible to DrMOS cooling improve while maintaining acceptable noise emission.

- An output inductor should be located close to the FDMF6706B to minimize the power loss due to the VSWH copper trace. Care should also be taken so the inductor dissipation does not heat the DrMOS.

- 4. PowerTrench® MOSFETs are used in the output stage. The power MOSFETs are effective at minimizing ringing due to fast switching. In most cases, no VSWH snubber is required. If a snubber is used, it should be placed close to the VSWH and PGND pins. The resistor and capacitor need to be of proper size for the power dissipation.

- VCIN, VDRV, and BOOT capacitors should be placed as close as possible to the VCIN to CGND, VDRV to CGND, and BOOT to PHASE pins to ensure clean and stable power. Routing width and length should be considered.

- 6. Include a trace from PHASE to VSWH to improve noise margin. Keep the trace as short as possible.

- The layout should include a place holder to insert a small-value series boot resistor (R<sub>BOOT</sub>) between the

boot capacitor ( $C_{BOOT}$ ) and DrMOS BOOT pin. The BOOT-to-VSWH loop size, including  $R_{BOOT}$  and  $C_{BOOT}$ , should be as small as possible. The boot resistor may be required when operating near the maximum rated  $V_{IN}$ . The boot resistor is effective at controlling the high-side MOSFET turn-on slew rate and VSHW overshoot.  $R_{BOOT}$  can improve noise operating margin in synchronous buck designs that may have noise issues due to ground bounce or high positive and negative VSWH ringing. However, inserting a boot resistance lowers the DrMOS efficiency. Efficiency versus noise trade-offs must be considered.  $R_{BOOT}$  values from 0.5 to 2.0  $\Omega$  are typically effective in reducing VSWH overshoot.

The VIN and PGND pins handle large current transients with frequency components >100 MHz. If possible, these pins should be connected directly to the VIN and board GND planes. The use of thermal relief traces in series with these pins is discouraged since this adds inductance to the power path. This added inductance in series with either the VIN or PGND pin degrades system noise immunity by increasing positive and negative VSWH ringing.

- GND pad and PGND pins should be connected to the GND plane copper with multiple vias for stable grounding. Poor grounding can create a noise transient offset voltage level between CGND and PGND. This could lead to faulty operation of the gate driver and MOSFETs.

- Ringing at the BOOT pin is most effectively controlled by close placement of the boot capacitor. Do not add an additional BOOT to the PGND capacitor. This may lead to excess current flow through the BOOT diode.

- 10. The SMOD# and DISB# pins have weak internal pull-up and pull-down current sources, respectively. These pins should not have any noise filter capacitors. Do not to float these pins unless absolutely necessary.

- 11. Use multiple vias on each copper area to interconnect top, inner, and bottom layers to help distribute current flow and heat conduction. Vias should be relatively large and of reasonably low inductance. Critical high-frequency components, such as R<sub>BOOT</sub>, C<sub>BOOT</sub>, the RC snubber, and bypass capacitors should be located as close to the respective DrMOS module pins as possible on the top layer of the PCB. If this is not feasible, they should be connected from the backside through a network of low-inductance vias.

Figure 29. PCB Layout Example

# **Physical Dimensions**

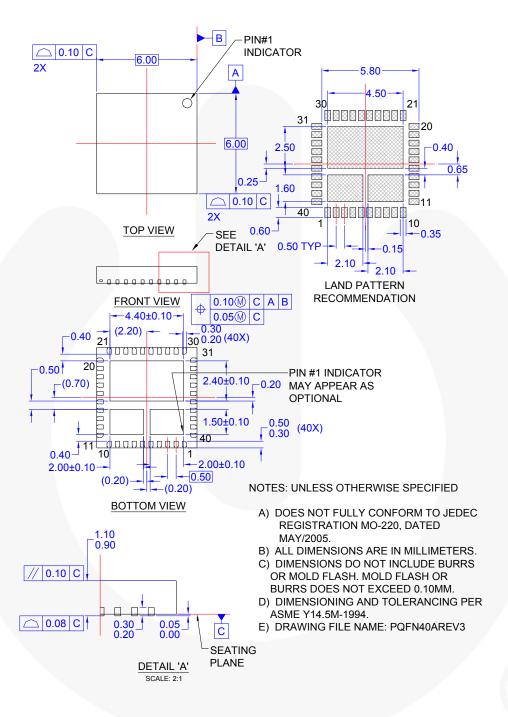

Figure 30. 40-Lead, Clipbond PQFN DrMOS, 6.0x6.0 mm Package

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>.

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

2CoolTM

AccuPowerTM

AX-CAP®\*

BitSiCTM

Build it NowTM

CorePLUSTM

CorePOWERTM

CROSSVOLTTM

CTLTM

Current Transfer Logic

CTL''''

Current Transfer Logic™

DEUXPEED®

Dual Cool™

EcoSPARK®

EfficientMax™

ESBC™ Fairchild®

Fairchild Semiconductor® FACT Quiet Series™ FACT®

FACT<sup>®</sup> FAST<sup>®</sup> Fast∨Core™ FETBench™ FPSTM F-PFSTM FRFET<sup>®</sup> Global Power Resource<sup>S</sup> GreenBridge<sup>TM</sup>

Green FPS™

Green FPS™ e-Series™

Gmax™

GTO™

IntelliMAX™ ISOPLANAR™

Making Small Speakers Sound Louder and Better™

MegaBuck™

MICROCOUPLER™

MicroFET™

MicroPak™

MicroPak™

MicroPak2!\*

MillerDrive\*\*

MotionMax\*\*

mWSaver\*\*

OptoHiT\*\*

OPTOLOGIC®

OPTOPLANAR®

PowerTrench<sup>®</sup> PowerXS™

Programmable Active Droop™

QS™ Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™ SignalWise™

SmartMax™

SMART START™

Solutions for Your Success™

SPM®

STEALTH™

SuperFET®

SuperSOT™-8

SuperSOT™-8

SuperSOT™-8

SuperMOS®

SyncETT™

Sync-Lock™

SYSTEM

GENERAL®

TinyBoost™

TinyBuck™

TinyCalc™

TinyLogic®

TINYOPTOT™

TinyPower™

TinyPWM™

TinyPWM™

TinyWire™

TranSiC™

TriFault Detect™

TRUECURRENT®\*

µSerDes™

VSerDes"

UHC

Ultra FRFET™

UniFET™

VCX™

VisualMax™

VoltagePlus™

XS™

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN, NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild straking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |  |  |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |

| Preliminary              | First Production      | Datasheet contains preliminary data, supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |  |  |

Rev. 164

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

# AMEYA360 Components Supply Platform

# **Authorized Distribution Brand:**

# Website:

Welcome to visit www.ameya360.com

# Contact Us:

# > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

# > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

# Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com