#### **FEATURES**

- Guaranteed AC performance over temperature and voltage:

- > 800MHz f<sub>MAX</sub> (typical)

- < 50ps within-device skew</li>

- Low voltage operation:

- LVPECL: +3.3V ±10%

LVECL: -3.3V ±10%

- Internal 75k $\Omega$  pull-down resistors

- Guaranteed over industrial temperature range:

- -40°C to +85°C

- Pin-for-pin, plug-in replacement for MC100LVE310

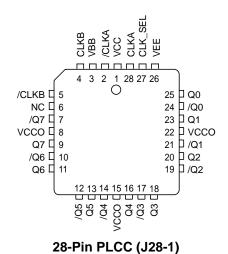

- Available in 28-pin PLCC package

#### **DESCRIPTION**

The SY100E310L is a 3.3V, precision 2:8 ECL/PECL fanout buffer optimized for precision low-skew clock distribution. The SY100E310L features fully differential clock paths to minimize both device and system skew resulting in skew performance of < 50ps. In addition, the device includes a 2:1 multiplexer input for redundant switchover applications.

The SY100E310L is optimized for low voltage +3.3V LVPECL or -3.3V LVECL applications.

Data sheets and support documentation can be found on Micrel's web site at www.micrel.com.

#### **APPLICATIONS**

- Communications clock distribution

- Redundant clock switchover

- High-end server clock distribution

#### **CROSS REFERENCE TABLE**

| Micrel Semiconductor | On Semiconductor |  |

|----------------------|------------------|--|

| SY100E310LJI         | MC100LVE310FN    |  |

| SY100E310LJITR       | MC100LVE310FNR2  |  |

#### **FUNCTIONAL BLOCK DIAGRAM**

## Q0 Q1 /O1 /Q2 CLKA Q3 /CLKA /Q3 **CLKB** Q4 /CLKB SEL Q5 /Q5 Q6 /Q6 Ω7

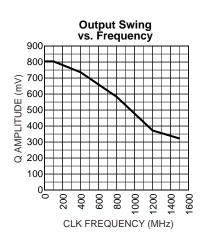

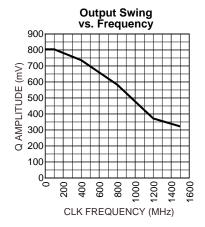

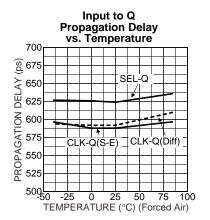

#### **TYPICAL PERFORMANCE**

Rev.: D Amendment: /1 Issue Date: July 2006

SY100E310L

## **PACKAGE/ORDERING INFORMATION**

# Ordering Information<sup>(1)</sup>

| Part Number                      | Package<br>Type | Operating<br>Range | Package<br>Marking                           | Lead<br>Finish |

|----------------------------------|-----------------|--------------------|----------------------------------------------|----------------|

| SY100E310LJI                     | J28-1           | Industrial         | SY100E310LJI                                 | Sn-Pb          |

| SY100E310LJITR <sup>(2)</sup>    | J28-1           | Industrial         | SY100E310LJI                                 | Sn-Pb          |

| SY100E310LJY <sup>(3)</sup>      | J28-1           | Industrial         | SY100E310LJY with Pb-Free bar-line indicator | Matte-Sn       |

| SY100E310LJYTR <sup>(2, 3)</sup> | J28-1           | Industrial         | SY100E310LJY with Pb-Free bar-line indicator | Matte-Sn       |

#### Notes:

- 1. Contact factory for die availability. Dice are guaranteed at  $T_A$  = 25°C, DC Electricals only.

- 2. Tape and Reel.

- 3. Pb-Free package is recommended for new designs.

#### PIN DESCRIPTION

| Pin Number                        | Pin Name                                 | Pin Function                                                                                                                                                                         |

|-----------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                 | VCC                                      | Positive Core Power Supply. Bypass with $0.1\mu F \parallel 0.01\mu F$ low ESR capacitors. Not internally connected to $V_{CCO}$ . Must be externally connected to $V_{CCO}$ on PCB. |

| 28, 2, 4, 5                       | CLKA, /CLKA<br>CLKB, /CLKB               | Differential Inputs: These input pairs are the differential data inputs to the device.                                                                                               |

| 3                                 | VBB                                      | Reference Voltage Output. Used for AC-coupled inputs or single-ended inputs.                                                                                                         |

| 6                                 | NC                                       | No Connect.                                                                                                                                                                          |

| 8, 15, 22                         | vcco                                     | Positive Power Supply. Bypass with $0.1\mu F  0.01\mu F $ low ESR capacitors. Not internally connected to $V_{CC}$ . Must be externally connected to $V_{CC}$ on PCB.                |

| 24, 21, 19,<br>17, 14, 12, 10, 7  | /Q0, /Q1, /Q2, /Q3<br>/Q4, /Q5, /Q6, /Q7 | Differential Outputs.                                                                                                                                                                |

| 25, 23, 20, 18,<br>16, 13, 11, 9, | Q0, Q1, Q2, Q3<br>Q4, Q5, Q6, Q7         | Differential Outputs.                                                                                                                                                                |

| 26                                | VEE                                      | Negative Supply.                                                                                                                                                                     |

| 27                                | CLK_SEL                                  | Single-Ended Clock Select.                                                                                                                                                           |

## **Absolute Maximum Ratings**(1)

| Supply Voltage (V <sub>CC</sub> )0.5V to +4.0V                     |

|--------------------------------------------------------------------|

| Input Voltage ( $V_{IN}$ ) $-0.5V$ to $V_{CC}$                     |

| Termination Current <sup>(3)</sup>                                 |

| Source or sink current on V <sub>BB</sub> (I <sub>BB</sub> )±0.5mA |

| Input Current                                                      |

| Source or sink current                                             |

| (CLKA, /CLKA, CLKB, /CLKB, CLK_SEL)±50mA                           |

| Lead Temperature (soldering, 20 sec.)+260°C                        |

| Storage Temperature ( $T_S$ ) $-65^{\circ}C$ to $+150^{\circ}C$    |

## Operating Ratings<sup>(2)</sup>

| Supply Voltage (V <sub>CC</sub> )       | +3.0V to +3.6V |

|-----------------------------------------|----------------|

| Ambient Temperature (T <sub>A</sub> ) – | 40°C to +85°C  |

| Package Thermal Resistance              |                |

| PLCC $(\theta_{JA})$                    |                |

| Still-Air                               | 63.5°C/W       |

| 500lfpm                                 | 43.5°C/W       |

## DC ELECTRICAL CHARACTERISTICS(4)

$T_A = -40^{\circ}C$  to +85°C; unless noted.

| Symbol          | Parameter    | Condition | Min | Тур | Max | Units |

|-----------------|--------------|-----------|-----|-----|-----|-------|

| V <sub>CC</sub> | Power Supply |           | 3.0 | 3.3 | 3.6 | V     |

## LVPECL DC ELECTRICAL CHARACTERISTICS(4, 5)

$V_{CC}$  = +3.3V,  $V_{EE}$  = 0V;  $T_A$  = -40°C to +85°C; unless noted.

| Symbol              | Parameter                                                                             | Condition                        | Min  | Тур  | Max  | Units |

|---------------------|---------------------------------------------------------------------------------------|----------------------------------|------|------|------|-------|

| I <sub>CC</sub>     | Power Supply Current                                                                  | No load, max. V <sub>CC</sub>    |      | 55   | 70   | mA    |

| V <sub>OH</sub>     | Output High Voltage<br>(Q0-Q7, /Q0-/Q7)                                               | $R_L = 50\Omega$ to $V_{CC}$ –2V | 2215 | 2345 | 2420 | mV    |

| V <sub>OL</sub>     | Output Low Voltage<br>(Q0-Q7, /Q0-/Q7)                                                | $R_L = 50\Omega$ to $V_{CC}$ –2V | 1470 | 1595 | 1680 | mV    |

| V <sub>IH</sub>     | Input High Voltage<br>(CLKA, /CLKA, CLKB, /CLKB, CLK_SEL)                             |                                  | 2135 |      | 2420 | mV    |

| V <sub>IL</sub>     | Input Low Voltage<br>(CLKA, /CLKA, CLKB, /CLKB, CLK_SEL)                              |                                  | 1490 |      | 1825 | mV    |

| V <sub>IHCMR</sub>  | Input High Voltage Common<br>Mode Range (Differential)<br>(CLKA, / CLKA, CLKB, /CLKB) | Note 6                           | 1.8  |      | 2.9  | V     |

| $\overline{V_{BB}}$ | Output Reference Voltage                                                              |                                  | 1.92 |      | 2.04 | V     |

| I <sub>IN</sub>     | Input HIGH Current<br>(CLKA, /CLKA, CLKB,/CLKB, CLK_SEL)                              |                                  |      |      | 150  | μА    |

| I <sub>IL</sub>     | Input LOW Current<br>(CLKA, /CLKA, CLKB, /CLKB, CLK_SEL)                              |                                  | 0.5  |      |      | μА    |

#### Notes:

- 1. Permanent device damage may occur if Absolute Maximum Ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

- 2. The data sheet limits are not guaranteed if the device is operated beyond the operating ratings.

- 3. Due to the limited drive capability use for input of the same package only.

- 4. The circuit is designed to meet the DC specifications shown in the above table after thermal equilibrium has been established.

- 5. Input and output parameters vary 1:1 with  $\rm V_{CC}.~V_{CC}$  can vary  $\pm 0.3 \rm V.$

- 6. V<sub>IHCMR</sub> is defined as the range within which the V<sub>IH</sub> level may vary with the device still meeting the propagation delay specification. The V<sub>IL</sub> level must be such that the peak-to-peak voltage is less than 1.0V and then greater than or equal to V<sub>PP</sub>(min).

SY100E310L

## LVNECL DC ELECTRICAL CHARACTERISTICS(7, 8)

$V_{CC}$  = +3.3V,  $V_{EE}$  = 0V;  $T_A$  = -40°C to +85°C; unless noted.

| Symbol             | Parameter                                                                             | Condition                        | Min   | Тур   | Max   | Units |

|--------------------|---------------------------------------------------------------------------------------|----------------------------------|-------|-------|-------|-------|

| V <sub>OH</sub>    | Output High Voltage<br>(Q0-Q7, /Q0-/Q7)                                               | $R_L = 50\Omega$ to $V_{CC}$ –2V | -1085 | -955  | -880  | mV    |

| V <sub>OL</sub>    | Output Low Voltage<br>(Q0-Q7, /Q0-/Q7)                                                | $R_L = 50\Omega$ to $V_{CC}$ –2V | -1830 | -1705 | -1620 | mV    |

| V <sub>IH</sub>    | Input High Voltage<br>(CLKA, /CLKA, CLKB, /CLKB, CLK_SEL)                             |                                  | -1165 |       | -880  | mV    |

| $V_{IL}$           | Input Low Voltage<br>(CLKA, /CLKA, CLKB, /CLKB, CLK_SEL)                              |                                  | -1810 |       | -1475 | mV    |

| V <sub>IHCMR</sub> | Input High Voltage Common<br>Mode Range (Differential)<br>(CLKA, / CLKA, CLKB, /CLKB) | Note 9                           | -1.5  |       | -0.4  | V     |

| $V_{BB}$           | Output Reference Voltage                                                              |                                  | -1.38 |       | -1.26 | V     |

| I <sub>IN</sub>    | Input HIGH Current<br>(CLKA, /CLKA, CLKB,/CLKB, CLK_SEL)                              |                                  |       |       | 150   | μА    |

| I <sub>IL</sub>    | Input LOW Current (CLKA, /CLKA, CLKB, /CLKB, CLK_SEL)                                 |                                  | 0.5   |       |       | μΑ    |

#### **AC ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = +3.0 to +3.6V and  $V_{EE}$  = 0V or  $V_{CC}$  = 0V and  $V_{EE}$  = -3.0 to -3.6V;  $T_A$  = -40°C to +85°C; unless noted.

| Symbol                          | Parameter                                                | Condition                | Min | Тур | Max       | Units             |

|---------------------------------|----------------------------------------------------------|--------------------------|-----|-----|-----------|-------------------|

| f <sub>MAX</sub>                | Maximum Operating Frequency                              | V <sub>OUT</sub> = 400mV |     | 800 |           | MHz               |

| t <sub>PD</sub>                 | Propagation Delay<br>CLKA-to-Q, CLKB-to-Q (Differential) | Note 10                  | 525 |     | 725       | ps                |

|                                 | CLKA-to-Q, CLKB-to-Q (Single-ended)                      | Note 11                  | 500 |     | 750       | ps                |

| t <sub>SKEW</sub>               | Within-Device Skew<br>Part-to-Part Skew (Differential)   | Note 12                  |     |     | 50<br>200 | ps<br>ps          |

| t <sub>JITTER</sub>             | Cycle-to-Cycle Jitter                                    |                          |     | 1   |           | ps <sub>RMS</sub> |

| $V_{PP}$                        | Input Swing                                              | Note 13                  | 500 |     | 1000      | mV                |

| t <sub>r</sub> , t <sub>f</sub> | Rise / Fall Time (20% to 80%)<br>(Q0-Q7, /Q0-/Q7)        |                          | 160 | 375 | 600       | ps                |

#### Notes:

- 7. The circuit is designed to meet the DC specifications shown in the above table after thermal equilibrium has been established.

- 8. Input and output parameters vary 1:1 with  $\rm V_{CC}.~V_{CC}$  can vary  $\pm 0.3 \rm V.$

- 9. V<sub>IHCMR</sub> is defined as the range within which the V<sub>IH</sub> level may vary with the device still meeting the propagation delay specification. The V<sub>IL</sub> level must be such that the peak-to-peak voltage is less than 1.0V and then greater than or equal to V<sub>PP</sub>(min).

- 10. The differential propagation delay is defined as the delay from the crossing points of the differential input signals to the crossing point of the differential output signals.

- 11. The single-ended propagation delay is defined as the delay from the 50% point of the input signal to the 50% point of the output signal.

- 12. The within-device skew is defined as the worst case difference between any two similar delay paths within a single device.

- 13. V<sub>PP</sub>(min) is defined as the minimum input differential voltage which will cause no increase in the propagation delay. The V<sub>PP</sub>(min) is AC limited for the E310L as a differential input as low as 50 mV will still produce full ECL levels at the output.

## **TYPICAL OPERATING CHARACTERISTICS**

$V_{CC} = 3.3V, T_A = 25^{\circ}C$

#### RELATED PRODUCT AND SUPPORT DOCUMENTATION

| Part Number   | Function                      | Data Sheet Link                                      |

|---------------|-------------------------------|------------------------------------------------------|

| HBW Solutions | New Products and Applications | www.micrel.com/product-info/products/solutions.shtml |

Micrel, Inc. SY100E310L

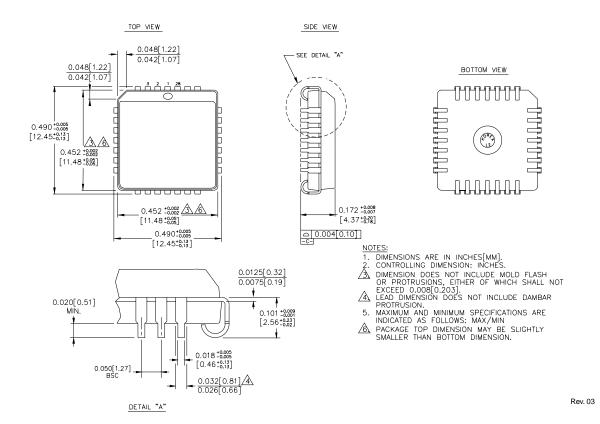

#### 28-PIN PLCC (J28-1)

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use.

Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2006 Micrel, Incorporated.

# AMEYA360 Components Supply Platform

## **Authorized Distribution Brand:**

## Website:

Welcome to visit www.ameya360.com

## Contact Us:

## > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

## > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

## Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com