# **inter<sub>sil</sub>**"

# QFN Packaged, ±15kV ESD Protected, +2.7V to +3.6V, 250kbps, RS-232 Transmitters/Receivers with Separate Logic Supply Pin

### **ISL3241E, ISL3243E**

The Intersil ISL324xE devices are 2.7V to 3.6V powered RS-232 transmitters/receivers which meet EIA/TIA-232 and V.28/V.24 specifications, even at V<sub>CC</sub> = 3.0V. Additionally, they provide  $\pm$ 15kV ESD protection (IEC61000-4-2 Air Gap and Human Body Model) on transmitter outputs and receiver inputs (RS-232 pins). Targeted applications are POS systems, and notebook and laptop computers where the low operational, and even lower standby, power consumption is critical. Efficient on-chip charge pumps, coupled with manual and automatic power-down functions, reduce the standby supply current to a 0.5µA trickle. Tiny 5mmx5mm **Quad Flat No-Lead** (QFN) packaging and the use of small, low value capacitors ensure board space savings as well. Data rates greater than 250kbps are guaranteed at worst case load conditions.

ISL324xE are 3 driver, 5 receiver devices that, coupled with the 5x5 QFN package, provide the industry's smallest, lowest power complete serial port. The 5x5 QFN requires 60% less board area than a 28 Ld TSSOP, and is nearly 20% thinner. These devices also include a noninverting always-active receiver for "wake-up" capability.

The **ISL3243E** features an *automatic powerdown* function that powers down the on-chip power supply and driver circuits. This occurs when an attached peripheral device is shut off or the RS-232 cable is removed, conserving system power automatically without changes to the hardware or operating system. It powers up again when a valid RS-232 voltage is applied to any receiver input.

The ISL324xE feature a V<sub>L</sub> pin that adjusts the logic pin (see "Pin Descriptions" on page 2) output levels and input thresholds to values compatible with the V<sub>CC</sub> powering the external logic (e.g., a UART).

Table 1 summarizes the features of the ISL324xE.

### **Features**

- V<sub>L</sub> Pin for Compatibility in Mixed Voltage Systems Adjusts Logic Output Levels and Input Thresholds for Compatibility with Lower Supply Voltage Logic

- Parameters Specified for 10% Tolerance Supplies and Full Industrial Temp Range

- Pb-free Small QFN (5mmx5mm) Package is 60% Smaller than a 28 Lead TSSOP

- ESD Protection for RS-232 I/O Pins to ±15kV (IEC61000)

- Meets EIA/TIA-232 and V.28/V.24 Specifications at 3V

- RS-232 Compatible with V<sub>CC</sub> = 2.7V

- On-Chip Voltage Converters Require Only Four External 0.1µF Capacitors

- Manual and Automatic Power-down Features

- · Receiver Hysteresis for Improved Noise Immunity

- Low Supply Current in Power-down State ...... 0.5µA

- Pb-Free (RoHS compliant)

### Applications

- Any Space Constrained System Requiring RS-232 Ports

- Battery Powered, Hand-Held, and Portable Equipment

- POS Systems and Scanners

- Laptop Computers, Notebooks

- GPS Receivers

- Mixed Voltage Serial Ports

### **Related Literature**

- Technical Brief <u>TB363</u> "Guidelines for Handling and Processing Moisture Sensitive Surface Mount Devices

- Technical Brief <u>TB379</u> "Thermal Characterization of Packages for ICs"

- Technical Brief <u>TB389</u> "PCB Land Pattern Design and Surface Mount Guidelines for QFN Packages"

| PART NUMBER | NO. OF<br>Tx. | NO. OF<br>Rx. | LOGIC SUPPLY<br>(V <sub>L</sub> ) PIN? | NO. OF<br>MONITOR Rx.<br>(R <sub>OUTB</sub> ) | DATA RATE<br>(kbps) | Rx. ENABLE<br>FUNCTION? | Pb-FREE? | MANUAL<br>POWER-<br>DOWN? | AUTOMATIC<br>POWERDOWN<br>FUNCTION? |

|-------------|---------------|---------------|----------------------------------------|-----------------------------------------------|---------------------|-------------------------|----------|---------------------------|-------------------------------------|

| ISL3241E    | 3             | 5             | YES                                    | 2                                             | 250                 | YES                     | YES      | YES                       | NO                                  |

| ISL3243E    | 3             | 5             | YES                                    | 1                                             | 250                 | NO                      | YES      | YES                       | YES                                 |

#### TABLE 1. SUMMARY OF FEATURES

### **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|--------------------------------|-----------------|---------------------|----------------------|----------------|

| ISL3241EIRZ                    | ISL3241 EIRZ    | -40 to +85          | 32 Ld 5X5 QFN        | L32.5x5B       |

| ISL3243EIRZ                    | ISL3243 EIRZ    | -40 to +85          | 32 Ld 5X5 QFN        | L32.5x5B       |

NOTES:

1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pbfree products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL3241E, ISL3243E</u>. For more information on MSL please see tech brief <u>TB363</u>.

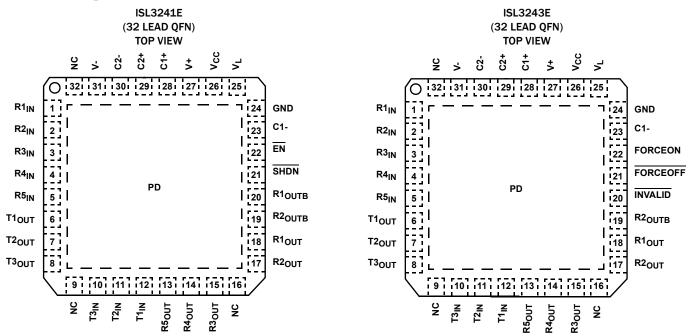

### **Pin Configurations**

### **Pin Descriptions**

| PIN NUMBER<br>ISL3241E | PIN NUMBER<br>ISL3243E | PIN NAME        | FUNCTION                                                                                                                                                                                                                                                                                                                                                             |

|------------------------|------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26                     | 26                     | v <sub>cc</sub> | System power supply input (2.7V to 3.6V).                                                                                                                                                                                                                                                                                                                            |

| 25                     | 25                     | V <sub>L</sub>  | Logic power supply. Sets the V <sub>OH</sub> of all the logic outputs and the switching point of all logic inputs. Keep V <sub>L</sub> greater than 1.6V (1.8V - 10%) and less than or equal to V <sub>CC</sub> . If V <sub>L</sub> isn't connected to the V <sub>cc</sub> supply, ensure that the V <sub>L</sub> supply powers up after the V <sub>cc</sub> supply. |

| 27                     | 27                     | V+              | Internally generated positive transmitter supply (typically +5.5V).                                                                                                                                                                                                                                                                                                  |

| 31                     | 31                     | V-              | Internally generated negative transmitter supply (typically -5.5V).                                                                                                                                                                                                                                                                                                  |

| 24                     | 24                     | GND             | Ground connection. This is also the potential of the thermal pad (PD).                                                                                                                                                                                                                                                                                               |

| 28                     | 28                     | C1+             | External capacitor (voltage doubler) is connected to this lead.                                                                                                                                                                                                                                                                                                      |

| 23                     | 23                     | C1-             | External capacitor (voltage doubler) is connected to this lead.                                                                                                                                                                                                                                                                                                      |

| 29                     | 29                     | C2+             | External capacitor (voltage inverter) is connected to this lead.                                                                                                                                                                                                                                                                                                     |

# Pin Descriptions (Continued)

| PIN NUMBER<br>ISL3241E | PIN NUMBER<br>ISL3243E | PIN NAME                                                                                        | FUNCTION                                                                                                                                                                           |

|------------------------|------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30                     | 30                     | C2-                                                                                             | External capacitor (voltage inverter) is connected to this lead.                                                                                                                   |

| 12, 11, 10             | 12, 11, 10             | ${\tt T1_{IN}, T2_{IN}, T3_{IN}}$                                                               | TTL/CMOS compatible transmitter inputs. The $V_L$ voltage sets the input switching point.                                                                                          |

| 6, 7, 8                | 6, 7, 8                | T1 <sub>OUT</sub> , T2 <sub>OUT</sub> ,<br>T3 <sub>OUT</sub>                                    | $\pm$ 15kV ESD Protected, RS-232 level (nominally $\pm$ 5.5V) transmitter outputs.                                                                                                 |

| 1, 2, 3, 4, 5          | 1, 2, 3, 4, 5          | R1 <sub>IN</sub> , R2 <sub>IN</sub> , R3 <sub>IN</sub> ,<br>R4 <sub>IN</sub> , R5 <sub>IN</sub> | ±15kV ESD Protected, RS-232 compatible receiver inputs.                                                                                                                            |

| 18, 17                 | 18, 17                 | R1 <sub>OUT</sub> , R2 <sub>OUT</sub>                                                           | TTL/CMOS level receiver outputs. Swings between GND and VL.                                                                                                                        |

| 20,19                  | 19                     | R1 <sub>OUTB,</sub> R2 <sub>OUTB</sub>                                                          | TTL/CMOS level, noninverting, always enabled receiver outputs. Swings between GND and $\mathrm{V}_{\mathrm{L}}.$                                                                   |

|                        | 20                     | INVALID                                                                                         | Active low output that indicates if no valid RS-232 levels are present on any receiver input. Swings between GND and $\rm V_L$                                                     |

|                        | 21                     | FORCEOFF                                                                                        | Active low to shut down transmitters and on-chip power supply. This overrides any automatic circuitry and FORCEON (see Table 2). The $V_L$ voltage sets the input switching point. |

|                        | 22                     | FORCEON                                                                                         | Active high input to override automatic powerdown circuitry thereby keeping transmitters active. (FORCEOFF must be high). The $V_L$ voltage sets the input switching point.        |

| 22                     |                        | EN                                                                                              | Active low receiver enable control. The $V_L$ voltage sets the input switching point.                                                                                              |

| 21                     |                        | SHDN                                                                                            | Active low input to shut down transmitters and on-board power supply, to place device in low power mode. The $V_L$ voltage sets the input switching point.                         |

| 9, 16, 32              | 9, 16, 32              | NC                                                                                              | No Connection                                                                                                                                                                      |

|                        |                        | PAD                                                                                             | Exposed Thermal Pad. Connect to GND.                                                                                                                                               |

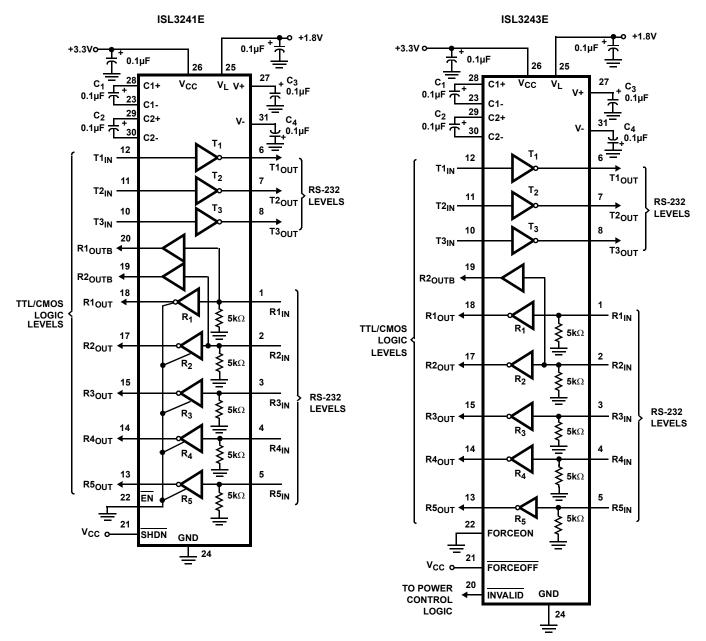

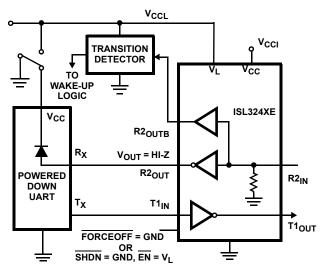

### **Typical Operating Circuits**

### ISL3241E, ISL3243E

#### **Absolute Maximum Ratings**

| V <sub>CC</sub> to Ground0.3V to 6V           |

|-----------------------------------------------|

| V <sub>L</sub> to Ground                      |

| V+ to Ground0.3V to 7V                        |

| V- to Ground                                  |

| V+ to V 14V                                   |

| Input Voltages                                |

| T <sub>IN</sub> , FORCEOFF, FORCEON, EN, SHDN |

| R <sub>IN</sub> ±25V                          |

| Output Voltages                               |

| T <sub>OUT</sub> ±13.2V                       |

| R <sub>OUT</sub> , INVALID                    |

| Short Circuit Duration                        |

| T <sub>OUT</sub> Continuous                   |

| ESD Rating See "ESD PERFORMANCE" on page 7    |

#### **Thermal Information**

| Thermal Resistance (Typical, Notes 4, 5) | θ <b>JA</b> (°C/W | /) θ <sub>JC</sub> (°C/W) |

|------------------------------------------|-------------------|---------------------------|

| 32 Ld QFN Package                        | 32                | 1.8                       |

| Maximum Junction Temperature             |                   | +150°C                    |

| Maximum Storage Temperature Range        |                   | -65°C to +150°C           |

| Pb-Free Reflow Profile                   |                   | see link below            |

| http://www.intersil.com/pbfree/Pb-FreeR  | eflow.asp         |                           |

#### **Operating Conditions**

| Temperature Range | -40°C to +85°C |

|-------------------|----------------|

|-------------------|----------------|

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief <u>TB379</u> for details.

- 5. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** Test Conditions:  $V_{CC} = 3V$  to 3.6V,  $V_L = 1.8V \pm 10\%$ ,  $C_1$  to  $C_4 = 0.1\mu$ F, Unless Otherwise Specified. Typicals are at  $T_A = +25$  °C,  $V_{CC} = 3.3V$ ,  $V_L = 1.8V$ , Unless Otherwise Specified. Boldface limits apply over the operating temperature range, -40 °C to +85 °C.

| PARAMETER                                            | TEST CONDITIONS                                                                                                    | TEMP<br>(°C)            | MIN<br>(Note 6) | ТҮР                   | MAX<br>(Note 6)      | UNITS |    |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|-----------------------|----------------------|-------|----|

| DC CHARACTERISTICS                                   |                                                                                                                    |                         | 1               |                       |                      |       |    |

| Operating Voltage Range                              |                                                                                                                    |                         | Full            | 2.7                   | -                    | 3.6   | v  |

| Supply Current, Automatic<br>Powerdown               | All R <sub>IN</sub> Open, FORCEON = GND, $\overline{FORCEOFF}$<br>V <sub>L</sub> = V <sub>CC</sub> (ISL3243E Only) | = V <sub>L</sub>        | Full            | -                     | 0.5                  | 3     | μA |

| Supply Current, Powerdown                            | All R <sub>IN</sub> Open, $\overline{FORCEOFF} = \overline{SHDN} = GND, V_L$                                       | = V <sub>CC</sub>       | Full            | -                     | 0.5                  | 3     | μA |

| Supply Current,                                      | All Outputs Unloaded,                                                                                              |                         | 25              | -                     | 0.3                  | 1.0   | mA |

| Automatic Powerdown Disabled                         | $FORCEON = \overline{FORCEOFF} = SHDN = V_L, V_{CC} =$                                                             | V <sub>L</sub> = 3.0V   | Full            | -                     | 0.3                  | 1.5   | mA |

| LOGIC AND TRANSMITTER INPU                           | ITS; RECEIVER AND LOGIC OUTPUTS                                                                                    |                         | 1               | 1                     | I.                   |       | r  |

| Input Logic Threshold Low                            | T <sub>IN</sub> , FORCEON, FORCEOFF, EN, SHDN                                                                      |                         | Full            | -                     | -                    | 0.5   | v  |

|                                                      |                                                                                                                    | $V_L = V_{CC} = 3V$     | Full            | -                     | -                    | 0.8   | v  |

| Input Logic Threshold High                           | T <sub>IN</sub> , FORCEON, FORCEOFF, EN, SHDN                                                                      |                         | Full            | 1.25                  | -                    | -     | v  |

|                                                      |                                                                                                                    | $V_{L} = V_{CC} = 3.6V$ | Full            | 2.0                   | -                    | -     | v  |

| Input Leakage Current                                | T <sub>IN</sub> , FORCEON, FORCEOFF, EN, SHDN                                                                      |                         | Full            | -                     | ±0.01                | ±1.0  | μA |

| Output Leakage Current                               | $\overline{\text{FORCEOFF}}$ = GND (ISL3243E) or $\overline{\text{EN}}$ = V <sub>L</sub> (IS                       | L3241E)                 | Full            | -                     | ±0.05                | ±10   | μA |

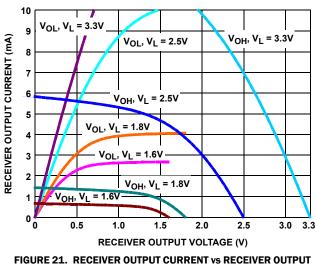

| Output Voltage Low                                   | I <sub>OUT</sub> = 250µA, R <sub>OUT</sub> , R <sub>OUTB</sub> , INVALID                                           |                         |                 | -                     | -                    | 0.45  | v  |

| (See Figure 21)                                      | $I_{OUT} = 1.6mA, V_L = V_{CC}, R_{OUT}, R_{OUTB}, \overline{INVA}$                                                | Full                    | -               | -                     | 0.4                  | v     |    |

| Output Voltage High                                  | I <sub>OUT</sub> = -250µA, R <sub>OUT</sub> , R <sub>OUTB</sub> , INVALID                                          |                         | Full            | V <sub>L</sub> - 0.25 | V <sub>L</sub> - 0.1 | -     | v  |

| (See Figure 21)                                      | $I_{OUT} = -1.0 \text{mA}, V_L = V_{CC}, R_{OUT}, R_{OUTB}, \overline{INVA}$                                       | LID                     | Full            | V <sub>L</sub> - 0.6  | V <sub>L</sub> -0.1  | -     | v  |

| AUTOMATIC POWERDOWN (ISL                             | 3243E Only, FORCEON = GND, FORCEOFF = \                                                                            | / <sub>L</sub> )        | 1               | 1                     |                      | 1     | 1  |

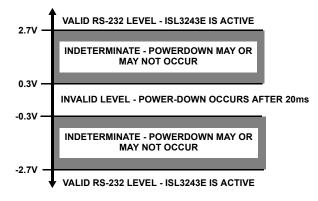

| Receiver Input Thresholds to<br>Enable Transmitters  | ISL3243E Powers Up (See Figure 10)                                                                                 |                         | Full            | -2.7                  | -                    | 2.7   | v  |

| Receiver Input Thresholds to<br>Disable Transmitters | ISL3243E Powers Down (See Figure 10)                                                                               |                         | Full            | -0.3                  | -                    | 0.3   | v  |

### ISL3241E, ISL3243E

**Electrical Specifications** Test Conditions:  $V_{CC} = 3V$  to 3.6V,  $V_L = 1.8V \pm 10\%$ ,  $C_1$  to  $C_4 = 0.1\mu$ F, Unless Otherwise Specified. Typicals are at  $T_A = +25$  °C,  $V_{CC} = 3.3V$ ,  $V_L = 1.8V$ , Unless Otherwise Specified. Boldface limits apply over the operating temperature range, -40 °C to +85 °C. (Continued)

| PARAMETER                                                                                | TEST CONDITIONS                                                                                   | TEMP<br>(°C)           | MIN<br>(Note 6) | ТҮР  | MAX<br>(Note 6) | UNITS |      |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------|-----------------|------|-----------------|-------|------|

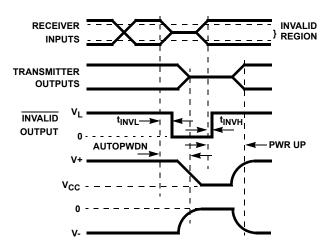

| Receiver Threshold to<br>Transmitters Enabled Delay (t <sub>WU</sub> )                   |                                                                                                   | 25                     | -               | 20   | -               | μs    |      |

| Receiver Positive or Negative<br>Threshold to INVALID High Delay<br>(t <sub>INVH</sub> ) |                                                                                                   |                        | 25              | -    | 0.7             | -     | μs   |

| Receiver Positive or Negative<br>Threshold to INVALID Low Delay<br>(t <sub>INVL</sub> )  |                                                                                                   |                        | 25              | -    | 20              | -     | μs   |

| RECEIVER INPUTS                                                                          | L                                                                                                 |                        |                 | 1    |                 | 1     |      |

| Input Voltage Range                                                                      |                                                                                                   |                        | Full            | -25  | -               | 25    | v    |

| Input Threshold Low                                                                      | V <sub>CC</sub> ≥ 2.7V                                                                            |                        | Full            | -    | -               | 0.6   | v    |

|                                                                                          | $V_{CC} \ge 3V$                                                                                   |                        | Full            | -    | -               | 0.8   | v    |

| Input Threshold High                                                                     |                                                                                                   | Full                   | 2.0             | 1.5  | -               | v     |      |

| Input Hysteresis                                                                         |                                                                                                   |                        | 25              | -    | 0.5             | -     | v    |

| Input Resistance                                                                         |                                                                                                   |                        | Full            | 3    | 5               | 7     | kΩ   |

| TRANSMITTER OUTPUTS                                                                      | t                                                                                                 |                        | L               | I    |                 |       | 1    |

| Output Voltage Swing (V <sub>O</sub> )                                                   | All Transmitter Outputs Loaded with $3k\Omega$ to                                                 |                        | Full            | ±5.0 | ±5.4            | -     | v    |

| ·                                                                                        | Ground                                                                                            | V <sub>CC</sub> = 2.7V | Full            | ±4.0 | ±4.7            | -     | v    |

| Output Resistance                                                                        | V <sub>CC</sub> = V <sub>L</sub> = V+ = V- = 0V, Transmitter Output                               |                        | Full            | 300  | 10M             | -     | Ω    |

| Output Short-Circuit Current                                                             |                                                                                                   | Full                   | -               | ±35  | ±60             | mA    |      |

| Output Leakage Current                                                                   | $V_{OUT} = \pm 12V$ , $V_{CC} = V_L = 0V$ or 3V to 3.6V,<br>Automatic Powerdown or FORCEOFF = SHD | Full                   | -               | -    | ±25             | μA    |      |

| TIMING CHARACTERISTICS                                                                   |                                                                                                   |                        |                 |      |                 |       |      |

| Maximum Data Rate                                                                        | $R_L = 3k\Omega$ , $C_L = 1000pF$ , One Transmitter Sv                                            | vitching               | Full            | 250  | 400             | -     | kbps |

|                                                                                          | $R_L = 3k\Omega C_L = 200pF, V_{CC} = 3.15V$ , One Tra                                            | Full                   | -               | 1.3  | -               | Mbp   |      |

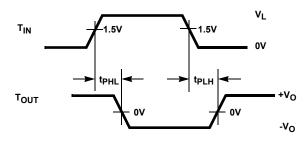

| Receiver Propagation Delay                                                               | Receiver Input to Receiver Output,                                                                | t <sub>PHL</sub>       | 25              | -    | 0.23            | 0.55  | μs   |

|                                                                                          | $C_L = 30pF, R_{IN} = \pm 3V$ (See Figure 2)                                                      |                        | Full            | -    | 0.26            | 0.6   | μs   |

|                                                                                          |                                                                                                   | t <sub>PLH</sub>       | 25              | -    | 0.16            | 0.55  | μs   |

|                                                                                          |                                                                                                   |                        | Full            | -    | 0.18            | 0.6   | μs   |

| Receiver Skew                                                                            | t <sub>PHL</sub> - t <sub>PLH</sub>                                                               | L.                     | 25              | -    | 70              | 300   | ns   |

|                                                                                          |                                                                                                   |                        | Full            | -    | 80              | 350   | ns   |

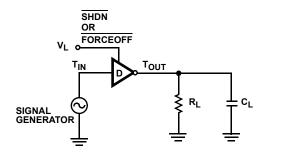

| Transmitter Propagation Delay                                                            | Transmitter Input to Transmitter Output,                                                          | t <sub>PHL</sub>       | 25              | -    | 0.7             | 1.5   | μs   |

|                                                                                          | $C_L = 1000 \text{pF}, R_L = 3 \text{k}\Omega \text{ (See Figure 1)}$<br>(Note 7)                 |                        | Full            | -    | 0.8             | 1.7   | μs   |

|                                                                                          |                                                                                                   | t <sub>PLH</sub>       | 25              | -    | 0.7             | 1.5   | μs   |

|                                                                                          |                                                                                                   |                        | Full            | -    | 0.8             | 1.7   | μs   |

| Transmitter Skew                                                                         | t <sub>PHL</sub> - t <sub>PLH</sub>                                                               | 1                      | 25              | -    | 20              | 500   | ns   |

|                                                                                          |                                                                                                   | Full                   | -               | 20   | 550             | ns    |      |

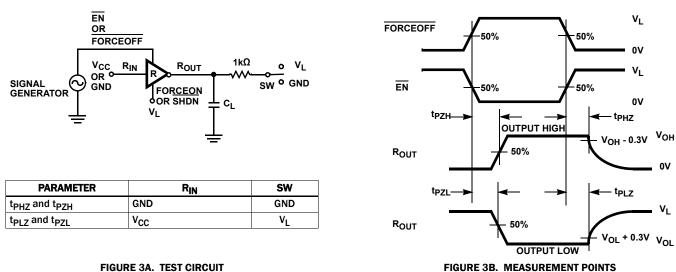

| Receiver Output Enable Time                                                              | From $\overline{EN}$ or $\overline{FORCEOFF}$ , $V_L = V_{CC}$ , $R_L = 1k\Omega$ ,               | 25                     | -               | 120  | -               | ns    |      |

| Receiver Output Disable Time                                                             | (See Figure 3)                                                                                    |                        | 25              | -    | 200             | -     | ns   |

| Transmitter Output Enable Time<br>From Powerdown                                         | From $\overline{\text{SHDN}}$ or $\overline{\text{FORCEOFF}}$ , $R_L = 3k\Omega$ , $C_L = 1$      | 000pF                  | 25              | -    | 20              | -     | μs   |

### ISL3241E, ISL3243E

**Electrical Specifications** Test Conditions:  $V_{CC} = 3V$  to 3.6V,  $V_L = 1.8V \pm 10\%$ ,  $C_1$  to  $C_4 = 0.1\mu$ F, Unless Otherwise Specified. Typicals are at  $T_A = +25$ °C,  $V_{CC} = 3.3V$ ,  $V_L = 1.8V$ , Unless Otherwise Specified. **Boldface limits apply over the operating temperature range, -40**°C to +85°C. (Continued)

| PARAMETER                                         | TEST CONDITIONS                                          | TEMP<br>(°C)              | MIN<br>(Note 6) | ТҮР  | MAX<br>(Note 6) | UNITS |      |

|---------------------------------------------------|----------------------------------------------------------|---------------------------|-----------------|------|-----------------|-------|------|

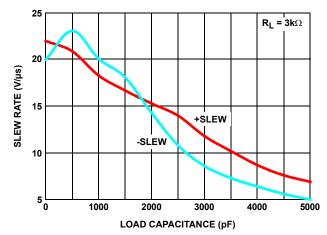

| Transition Region Slew Rate                       | $V_{CC}$ = 3V to 3.6V, R <sub>L</sub> = 3k\Omega to 7kΩ, | C <sub>L</sub> = 150pF to | 25              | 4    | 12              | 30    | V/µs |

|                                                   | Measured From 3V to -3V or -3V to 3V                     | 2500pF                    | Full            | 4    | 11              | 30    | V/µs |

|                                                   |                                                          | C <sub>L</sub> = 150pF to | 25              | 6    | 18              | 30    | V/µs |

|                                                   |                                                          | 1000pF                    | Full            | 6    | 17              | 30    | V/µs |

| ESD PERFORMANCE                                   |                                                          | I                         |                 | +    |                 |       |      |

| RS-232 Pins (T <sub>OUT</sub> , R <sub>IN</sub> ) | Human Body Model                                         | 25                        | -               | ±15  | -               | kV    |      |

|                                                   | IEC61000-4-2 Contact Discharge                           | 25                        | -               | ±8   | -               | kV    |      |

|                                                   | IEC61000-4-2 Air Gap Discharge                           | 25                        | -               | ±15  | -               | kV    |      |

| All Pins                                          | Human Body Model                                         | 25                        | -               | ±2   | -               | kV    |      |

|                                                   | Machine Model                                            | 25                        | -               | ±200 | -               | v     |      |

NOTES:

- 6. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

- 7. Transmitter propagation delays are measured at the transmitter output OV crossing points.

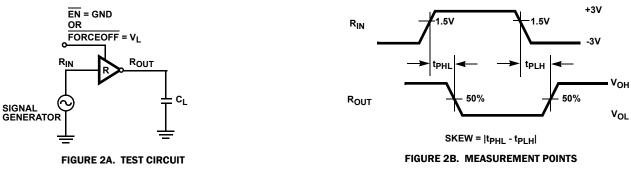

### **Test Circuits and Waveforms**

**FIGURE 1A. TEST CIRCUIT**

SKEW = |t<sub>PHL</sub> - t<sub>PLH</sub>|

FIGURE 1B. MEASUREMENT POINTS

FIGURE 1. DRIVER PROPAGATION DELAY AND SKEW

FIGURE 2. RECEIVER PROPAGATION DELAY AND SKEW

### Test Circuits and Waveforms (Continued)

**FIGURE 3A. TEST CIRCUIT**

### **Detailed Description**

The ISL324xE operate from a single +2.7V to +3.6V supply, guarantee a 250kbps minimum data rate, require only four small external 0.1µF capacitors, feature low power consumption, and meet all EIA RS-232 and V.28 specifications even with  $V_{CC}$  = 3.0V. The circuit is divided into three sections: The charge pump, the transmitters, and the receivers.

### **Charge-Pump**

Intersil's new ISL324xE devices utilize regulated on-chip dual charge pumps as voltage doublers, and voltage inverters to generate ±5.5V transmitter supplies from a V<sub>CC</sub> supply as low as 3.0V. This allows them to maintain RS-232 compliant output levels over the ±10% tolerance range of 3.3V powered systems. The efficient on-chip power supplies require only four small, external 0.1µF capacitors for the voltage doubler and inverter functions. The charge pumps operate discontinuously (i.e., they turn off as soon as the V+ and V- supplies are pumped up to the nominal values), resulting in significant power savings.

### **Transmitters**

The transmitters are proprietary, low dropout, inverting drivers that translate logic input levels to EIA/TIA-232 output levels. Coupled with the on-chip ±5.5V supplies, these transmitters deliver true RS-232 levels over a wide range of single supply system voltages.

All transmitter outputs disable and assume a high impedance state when the device enters the power-down mode (see Table 2). These outputs may be driven to F12V when disabled.

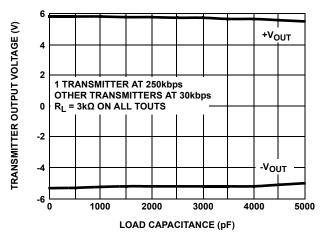

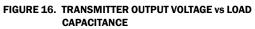

The devices guarantee a 250kbps data rate for full load conditions (3k $\Omega$  and 1000pF), V<sub>CC</sub>  $\geq$  3.0V, with one transmitter operating at full speed. Under more typical conditions of  $V_{CC} \ge$ 3.3V,  $R_I = 3k\Omega$  and  $C_I = 200pF$ , one transmitter easily operates at greater than 1Mbps.

The transmitter input switching threshold is set by the voltage applied to the  $V_L$  pin, so tying  $V_L$  to a voltage lower than  $V_{CC}$ reduces the Tx input VIH and VII to values compatible with logic ICs (e.g., UARTs and ucontrollers) powered by the V<sub>1</sub> voltage (see Figure 9 and Table 3). Transmitter inputs float if left unconnected (there are no pull-up resistors), and may cause supply current increases. Connect unused inputs to GND for the best performance.

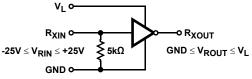

#### Receivers

All the ISL324xE devices contain standard inverting receivers that three-state via the EN or FORCEOFF control lines. Additionally, these products include noninverting "monitor" receivers (denoted by the ROUTB label) that are always active, regardless of the state of any control lines. All the receivers convert RS-232 signals to CMOS output levels, swinging between GND and VL, and accept inputs up to ±25V while presenting the required  $3k\Omega$  to  $7k\Omega$  input impedance (see Figure 4) even if the power is off (V<sub>CC</sub> = 0V). The receivers' Schmitt trigger input stage uses hysteresis to increase noise immunity and decrease errors due to slow input signal transitions.

FIGURE 4. INVERTING RECEIVER CONNECTIONS

The ISL3241E inverting receivers disable only when EN is driven high. ISL3243E receivers disable during forced (manual) powerdown, but not during automatic powerdown (see Table 2).

| RS-232<br>SIGNAL<br>PRESENT<br>AT<br>RECEIVER<br>INPUT? | SHDN OR<br>FORCEOFF<br>INPUT | FORCEON | EN<br>INPUT | TRANSMITTER<br>OUTPUTS | RECEIVER<br>OUTPUTS | R <sub>outb</sub><br>outputs | INVALID<br>OUTPUT | MODE OF OPERATION                             |

|---------------------------------------------------------|------------------------------|---------|-------------|------------------------|---------------------|------------------------------|-------------------|-----------------------------------------------|

| ISL3241E                                                |                              |         |             |                        |                     |                              |                   |                                               |

| N/A                                                     | L                            | N/A     | L           | High-Z                 | Active              | Active                       | N/A               | Manual Power-down                             |

| N/A                                                     | L                            | N/A     | н           | High-Z                 | High-Z              | Active                       | N/A               | Manual Power-down w/ Rcvr. Disabled           |

| N/A                                                     | н                            | N/A     | L           | Active                 | Active              | Active                       | N/A               | Normal Operation                              |

| N/A                                                     | н                            | N/A     | н           | Active                 | High-Z              | Active                       | N/A               | Normal Operation w/ Rcvr. Disabled            |

| ISL3243E                                                | 1                            |         | -           | •                      | •                   | •                            | •                 |                                               |

| NO                                                      | н                            | н       | N.A.        | Active                 | Active              | Active                       | L                 | Normal Operation<br>(Auto Powerdown Disabled) |

| YES                                                     | н                            | L       | N.A.        | Active                 | Active              | Active                       | н                 | Normal Operation<br>(Auto Power-down Enabled) |

| NO                                                      | н                            | L       | N.A.        | High-Z                 | Active              | Active                       | L                 | Power-down Due to Auto Power-down<br>Logic    |

| YES                                                     | L                            | х       | N.A.        | High-Z                 | High-Z              | Active                       | н                 | Manual Power-down                             |

| NO                                                      | L                            | Х       | N.A.        | High-Z                 | High-Z              | Active                       | L                 | Manual Power-down                             |

TABLE 2. POWER-DOWN AND ENABLE LOGIC TRUTH TABLE (NOTE: "H" =  $V_L$ )

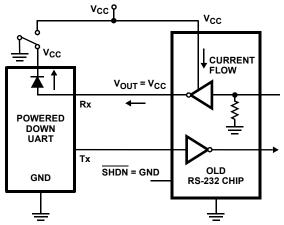

ISL324xE monitor receivers remain active even during manual powerdown, making them extremely useful for Ring Indicator monitoring. Standard receivers driving powered down peripherals must be disabled to prevent current flow through the peripheral's protection diodes (see Figures 5 and 6). This renders them useless for wake up functions, but the corresponding monitor receiver can be dedicated to this task as shown in Figure 6.

# **Low Power Operation**

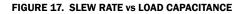

These 3V devices require a nominal supply current of 0.3mA, even at  $V_{CC}$  = 3.6V, during normal operation (not in power-down mode). This is considerably less than the 5mA to 11mA current required by comparable 5V RS-232 devices, allowing users to reduce system power simply by switching to this new family.

### **Power-down Functionality**

The already low current requirement drops significantly when the device enters powerdown mode. In powerdown, supply current drops to less than 1µA, because the on-chip charge pump turns off (V+ collapses to V<sub>CC</sub>, V- collapses to GND), and the transmitter outputs three-state. Inverting receiver outputs disable only in manual powerdown (ISL3243E) or when  $\overline{\text{EN}} = V_L$  (ISL3241E); refer to Table 2 for details. This micro-power mode makes the ISL324xE ideal for battery powered and portable applications.

FIGURE 5. POWER DRAIN THROUGH POWERED DOWN PERIPHERAL

FIGURE 6. DISABLED RECEIVERS PREVENT POWER DRAIN

#### **Software Controlled (Manual) Powerdown**

The devices in this family provide pins that allow the user to force the IC into the low power, standby state.

On the ISL3241E, the powerdown control is via a simple shutdown (SHDN) pin. Driving this pin high enables normal operation, while driving it low forces the IC into it's powerdown state. Connect SHDN to V<sub>L</sub> if the powerdown function isn't needed. Note that all the receiver outputs remain controlled by EN during shutdown (see Table 2). For the lowest power consumption during powerdown, the receivers should also be disabled by driving the EN input high (see next section, and Figures 5 and 6).

The ISL3243E utilizes a two pin approach where the FORCEON and FORCEOFF inputs determine the IC's mode. For always enabled operation, FORCEON and FORCEOFF are both strapped high. To switch between active and powerdown modes, under logic or software control, only the FORCEOFF input need be driven. The FORCEON state isn't critical, as FORCEOFF dominates over FORCEON. Nevertheless, if strictly manual control over powerdown is desired, the user must strap FORCEON high to disable the automatic powerdown circuitry. ISL3243E inverting (standard) receiver outputs also disable when the device is in manual powerdown, thereby eliminating the possible current path through a shutdown peripheral's input protection diode (see Figures 5 and 6).

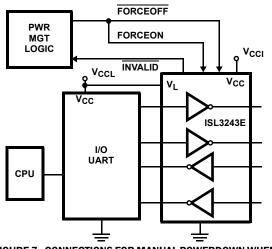

Connecting FORCEOFF and FORCEON together disables the automatic powerdown feature, enabling them to function as a manual SHUTDOWN input (see Figure 7).

FIGURE 7. CONNECTIONS FOR MANUAL POWERDOWN WHEN NO VALID RECEIVER SIGNALS ARE PRESENT

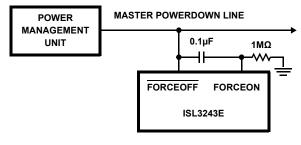

With any of the previous mentioned control schemes, the time required to exit powerdown, and resume transmission is only 20µs. A mouse, or other application, may need more time to wake up from shutdown. If automatic power-down is being utilized, the RS-232 device will reenter power-down if valid receiver levels aren't reestablished within 20µs of the ISL3243E powering up. Figure 8 illustrates a circuit that keeps the ISL3243E from initiating automatic power-down for 100ms after powering up. This gives the slow-to-wake peripheral circuit time to reestablish valid RS-232 output levels.

FIGURE 8. CIRCUIT TO PREVENT AUTO POWERDOWN FOR 100ms AFTER FORCED POWERUP

# V<sub>L</sub> Logic Supply Input

Note: If  $V_L$  isn't connected to the  $V_{cc}$  supply, power-up  $V_{cc}$  before powering up the  $V_L$  supply.

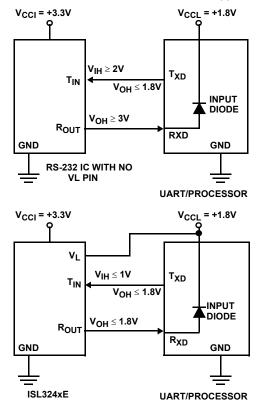

The ISL324xE feature a V<sub>L</sub> pin that powers the logic input and output pins. These pins interface with "logic" devices such as UARTs, ASICs, and µcontrollers, and today most of these devices use power supplies significantly lower than 3.3V. Thus, the logic device's low V<sub>OH</sub> might not exceed the V<sub>IH</sub> of a 3.3V powered ISL324xE logic input, or a 3.3V receiver output high level might overdrive and damage the input diodes on an input of a 1.8V powered logic device, as shown in Figure 9. Connecting the V<sub>L</sub> pin to the power supply of the logic device (see Figure 9) reduces the ISL324xE's logic input switching points, and limits the receiver output high voltage, to values compatible with the logic device's I/O levels. Tailoring the ISL324XE's logic pin input switching points and output levels

to the supply voltage of the UART, ASIC, or  $\mu controller$  eliminates the need for a level shifter/translator between the two ICs.

| TABLE 3. | VIH AND | V <sub>IL</sub> vs V <sub>L</sub> | FOR VC | <sub>C</sub> = 3.3V |

|----------|---------|-----------------------------------|--------|---------------------|

|----------|---------|-----------------------------------|--------|---------------------|

| V <sub>L</sub> (V) | V <sub>IH</sub> (V) | V <sub>IL</sub> (V) |

|--------------------|---------------------|---------------------|

| 1.6                | 0.85                | 0.8                 |

| 1.8                | 0.95                | 0.9                 |

| 2.5                | 1.25                | 1.2                 |

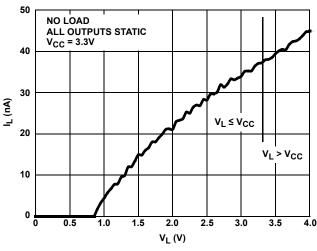

$V_L$  may range from 1.6V to  $V_{CC}$ , and Table 3 indicates the ISL324xE's typical  $V_{IH}$  and  $V_{IL}$  levels for several  $V_L$  values. Note that the  $V_L$  supply current increases significantly when  $V_L$  exceeds  $V_{CC}$  (see Figure 20).

If logic translation isn't required, connect  $V_L$  to  $V_{CC}$ .

FIGURE 9. USING V<sub>L</sub> PIN TO ADJUST LOGIC LEVELS

### **INVALID** Output (ISL3243E Only)

The INVALID output always indicates whether or not a valid RS-232 signal (see Figure 10) is present at any of the receiver inputs (see Table 2), giving the user an easy way to determine when the interface block should power down. Invalid receiver levels occur whenever the driving peripheral's outputs are shut off (powered down) or when the RS-232 interface cable is disconnected. In the case of a disconnected interface cable where all the receiver inputs are floating (but pulled to GND by the internal receiver pull down resistors), the INVALID logic detects the invalid levels and drives the output low. The power management logic then uses this indicator to power-down the interface block. Reconnecting the cable restores valid levels at

the receiver inputs, INVALID switches high, and the power management logic wakes up the interface block. INVALID can also be used to indicate the DTR or RING INDICATOR signal, as long as the other receiver inputs are floating, or driven to GND (as in the case of a powered down driver).

FIGURE 10. DEFINITION OF VALID RS-232 RECEIVER LEVELS

**INVALID** switches low after invalid levels have persisted on all of the receiver inputs for more than 20µs (see Figure 11). **INVALID** switches back high 1µs after detecting a valid RS-232 level on a receiver input. **INVALID** operates in all modes (forced or automatic power-down, or forced on), so it is also useful for systems employing manual power-down circuitry. When automatic powerdown is utilized, **INVALID** = 0 indicates that the ISL3243E is in powerdown mode.

FIGURE 11. AUTOMATIC POWERDOWN AND INVALID TIMING DIAGRAMS

### Automatic Power-down (ISL3243E Only)

Even greater power savings is available by using the ISL3243E which features an *automatic* power-down function. When no valid RS-232 voltages (see Figure 11) are sensed on any receiver input for 20 $\mu$ s, the charge pump and transmitters power-down, thereby reducing supply current to less than 1 $\mu$ A. Invalid receiver levels occur whenever the driving peripheral's outputs are shut off (powered down) or when the RS-232 interface cable is disconnected. The ISL3243E powers back up whenever it detects a valid RS-232 voltage level on any receiver input. This automatic power-down feature provides

additional system power savings without changes to the existing operating system.

Automatic power-down operates when the FORCEON input is low, and the FORCEOFF input is high. Tying FORCEON high disables automatic power-down, but manual powerdown is always available via the overriding FORCEOFF input. Table 2 summarizes the automatic power-down functionality.

The time to recover from automatic power-down mode is typically  $20 \mu s.$

# **Capacitor Selection**

The charge pumps require  $0.1\mu$ F, or greater, capacitors for proper operation. Increasing the capacitor values (by a factor of 2) reduces ripple on the transmitter outputs and slightly reduces power consumption.

When using minimum required capacitor values, make sure that capacitor values do not degrade excessively with temperature. If in doubt, use capacitors with a larger nominal value. The capacitor's equivalent series resistance (ESR) usually rises at low temperatures and it influences the amount of ripple on V+ and V-.

# **Power Supply Decoupling**

In most circumstances a  $0.1 \mu F$  bypass capacitor is adequate. In applications that are particularly sensitive to power supply noise, decouple  $V_{CC}$  and  $V_L$  to ground with a capacitor of the same value as the charge-pump capacitor  $C_1$ . Connect the bypass capacitor as close as possible to the IC.

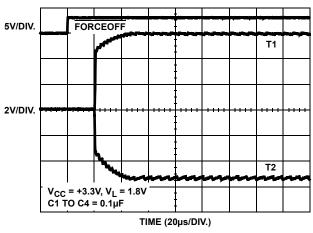

### Transmitter Outputs when Exiting Power-down

Figure 12 shows the response of two transmitter outputs when exiting powerdown mode. As they activate, the two transmitter outputs properly go to opposite RS-232 levels, with no glitching, ringing, nor undesirable transients. Each transmitter is loaded with  $3k\Omega$  in parallel with 1000pF. Note that the transmitters enable only when the magnitude of V+ and V-exceeds approximately 3V.

# **Operation Down to 2.7V**

ISL324xE transmitter outputs meet RS-562 levels ( $\pm$ 3.7V), at the full data rate, with V<sub>CC</sub> as low as 2.7V. RS-562 levels typically ensure inter operability with RS-232 devices.

# **High Data Rates**

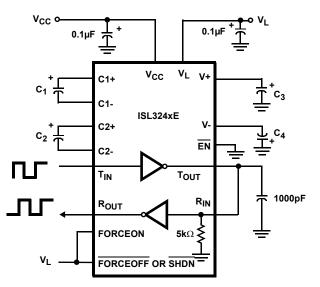

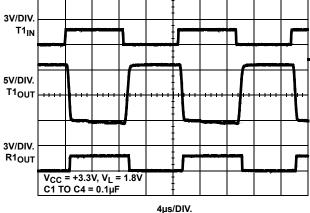

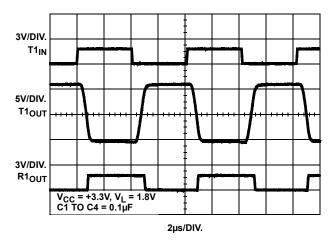

The ISL324xE maintain the RS-232 ±5V minimum transmitter output voltages even at high data rates. Figure 13 details a transmitter loopback test circuit, and Figure 14 illustrates the loopback test result at 120kbps. For this test, all transmitters were simultaneously driving RS-232 loads in parallel with 1000pF, at 120kbps. Figure 15 shows the loopback results for a single transmitter driving 1000pF and an RS-232 load at 250kbps. The static transmitters were also loaded with an RS-232 receiver.

FIGURE 14. LOOPBACK TEST AT 120kbps

FIGURE 15. LOOPBACK TEST AT 250kbps

# Interconnection to 1.8V, and 2.5V Logic

Standard 3.3V powered RS-232 devices interface well with 3V powered TTL compatible logic families (e.g., ACT and HCT).

The ISL324xE V<sub>L</sub> supply pin allows interconnection to 1.8V or 2.5V logic. By connecting V<sub>L</sub> to the same supply (1.8V or 2.5V) powering the logic device, the ISL324XE logic outputs will swing from GND to the logic V<sub>CC</sub>.

### ±15kV ESD Protection

All pins on ISL324xE devices include ESD protection structures, but the RS-232 pins (transmitter outputs and receiver inputs) incorporate advanced structures which allow them to survive ESD events up to  $\pm 15$ kV. The RS-232 pins are particularly vulnerable to ESD damage because they typically connect to an exposed port on the exterior of the finished product. Simply touching the port pins, or connecting a cable, can cause an ESD event that might destroy unprotected ICs. These new ESD structures protect the device whether or not it is powered up, protect without allowing any latchup mechanism to activate, and don't interfere with RS-232 signals as large as  $\pm 25$ V.

### Human Body Model (HBM) Testing

As the name implies, this test method emulates the ESD event delivered to an IC during human handling. The tester delivers the charge through a  $1.5k\Omega$  current limiting resistor, making the test less severe than the IEC61000 test which utilizes a 330 $\Omega$  limiting resistor. The HBM method determines an ICs ability to withstand the ESD transients typically present during handling and manufacturing. Due to the random nature of these events, each pin is tested with respect to all other pins. The RS-232 pins on "E" family devices can withstand HBM ESD events to  $\pm 15kV$ .

### IEC61000-4-2 Testing

The IEC61000 test method applies to finished equipment, rather than to an individual IC. Therefore, the pins most likely to suffer an ESD event are those that are exposed to the outside world (the RS-232 pins in this case), and the IC is tested in its typical application configuration (power applied) rather than testing each pin-to-pin combination. The lower current limiting resistor coupled with the larger charge storage capacitor yields a test that is much more severe than the HBM test. The extra ESD protection built into this device's RS-232 pins allows the design of equipment meeting level 4 criteria without the need for additional board level protection on the RS-232 port.

#### **AIR-GAP DISCHARGE TEST METHOD**

For this test method, a charged probe tip moves toward the IC pin until the voltage arcs to it. The current waveform delivered to the IC pin depends on approach speed, humidity, temperature, etc., so it is difficult to obtain repeatable results. The "E" device RS-232 pins withstand  $\pm 15$ kV air-gap discharges.

#### **CONTACT DISCHARGE TEST METHOD**

During the contact discharge test, the probe contacts the tested pin before the probe tip is energized, thereby eliminating the variables associated with the air-gap discharge. The result is a more repeatable and predictable test, but equipment limits prevent testing devices at voltages higher than ±8kV. All "E" family devices survive ±8kV contact discharges on the RS-232 pins.

### **Typical Performance Curves** $v_{CC} = 3.3V$ , $v_L = 1.8V$ , $T_A = +25°c$

FIGURE 20. VL SUPPLY CURRENT vs VL VOLTAGE

VOLTAGE

### **Die Characteristics**

#### SUBSTRATE AND QFN THERMAL PAD POTENTIAL (POWERED UP):

GND

#### **TRANSISTOR COUNT:**

464

#### **PROCESS:**

**SI GATE BICMOS**

For additional products, see <u>www.intersil.com/product\_tree</u>

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

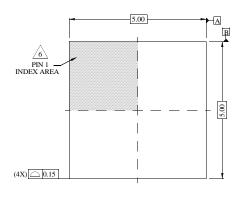

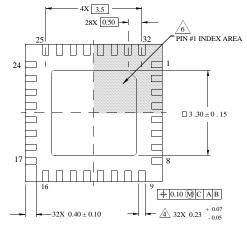

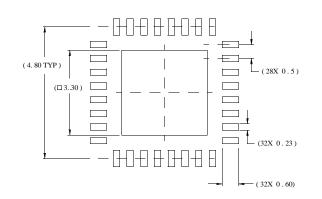

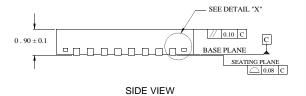

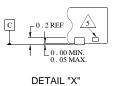

### **Package Outline Drawing**

### L32.5x5B

32 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 2, 11/07

BOTTOM VIEW

#### TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance: Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

# Authorized Distribution Brand :

### Website :

Welcome to visit www.ameya360.com

### Contact Us :

➤ Address :

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

- > Sales :

- Direct +86 (21) 6401-6692

- Email amall@ameya360.com

- QQ 800077892

- Skype ameyasales1 ameyasales2

### > Customer Service :

Email service@ameya360.com

### > Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com