### **General Description**

The MXL1344A contains six software-selectable, multiprotocol cable termination networks. Each network is capable of terminating V.11 (RS-422, RS-530, RS-530A, RS-449, V.36 and X.21) with a  $100\Omega$  differential load, V.35 with a T-network load, or V.28 (RS-232) and V.10 (RS-423) with an open-circuit load for use with transceivers having on-chip termination. The termination protocol can be selected by the serial interface cable wiring or by software control. The MXL1344A replaces discrete resistor termination networks and expensive relays required for multiprotocol termination, saving space and cost.

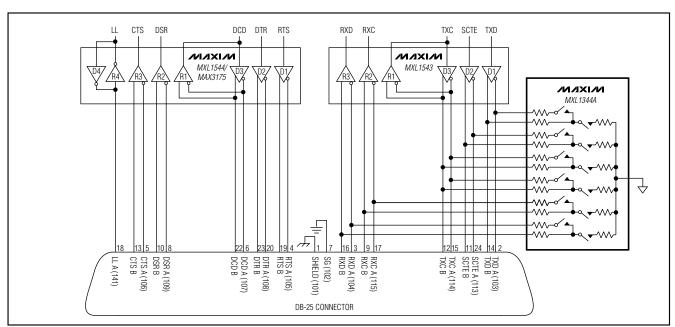

The MXL1344A terminator is designed to form a complete +5V cable- or software-selectable multiprotocol DCE/DTE interface port when used with the MXL1543 and MXL1544/MAX3175 transceiver ICs. The MXL1344A terminator can use the VEE power generated by the MXL1543 charge pump, simplifying system design. The MXL1344A, MXL1543, and MXL1544/MAX3175 are pinfor-pin compatible with the LTC1344A, LTC1543, and LTC1544, but for proper operation the entire Maxim chipset must be used without substituting other manufacturer's parts on a chip-by-chip basis.

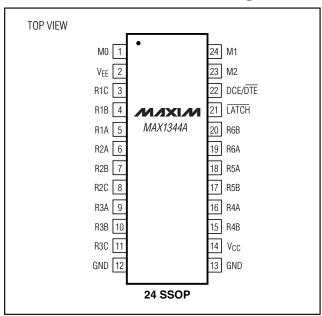

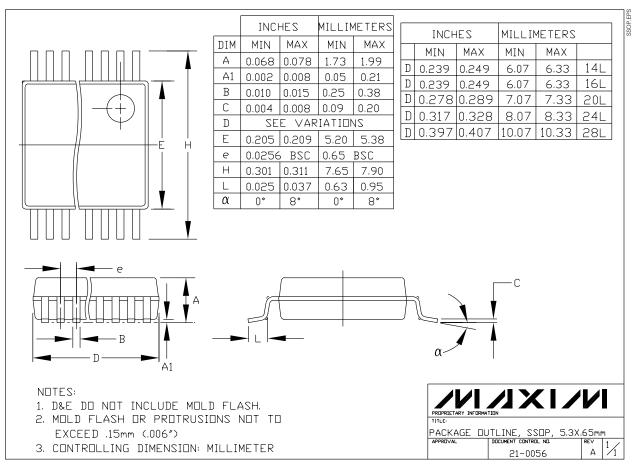

The MXL1344A is available in a 24-pin SSOP package and is specified for the 0°C to +70°C commercial temperature range.

#### Features

- ♦ Certified TBR-1 and TBR-2-Compliant Chipset (NET1 and NET2)—Pending Completion of **Testing**

- ♦ Supports V.10 (RS-423), V.11 (RS-422, RS-530, RS-530A, RS-449, V.36, and X.21), V.28 (RS-232) and V.35 Termination

- **♦** Cable- or Software-Selectable Termination

- ♦ Cable- or Software-Selectable DTE/DCE

- ♦ Replaces Discrete Resistor Termination Networks and Expensive Relays

- ♦ Available in Small 24-Pin SSOP Package

### **Applications**

Data Networking **PCI Cards** CSU and DSU Telecommunication Equipment **Data Routers Data Switches**

### Ordering Information

| PART        | TEMP. RANGE  | PIN-PACKAGE |  |  |

|-------------|--------------|-------------|--|--|

| MXL1344ACAG | 0°C to +70°C | 24 SSOP     |  |  |

Pin Configuration appears at end of data sheet.

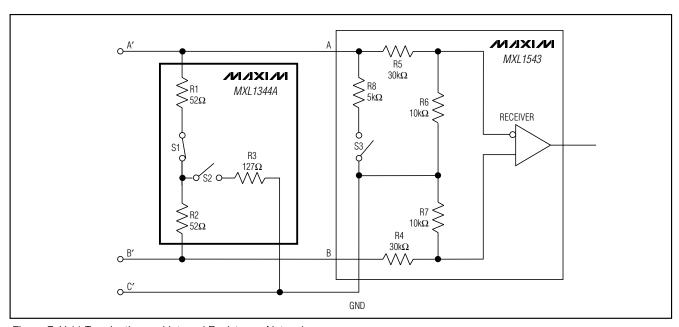

# **Typical Operating Circuit**

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| All Voltages to GND Unless Otherwise Noted Supply Voltages |             |

|------------------------------------------------------------|-------------|

| V <sub>CC</sub>                                            | 0.3V to +6V |

| VEE                                                        |             |

| Logic Input Voltages                                       |             |

| MO, M1, M2, DČE/DTE, LATCH                                 | 0.3V to +6V |

| Termination Network Inputs                                 |             |

| R_A, R_B                                                   | 15V to +15V |

| R_A to R_B                                                 | ±15V        |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| 24-Pin SSOP (derate 8mW/°C above +70°C)               | 640mW          |

| Operating Temperature Range                           | 0°C to +70°C   |

| Die Temperature                                       | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

|                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +5V \pm 5\%, V_{EE} = -5V \pm 5\%, T_A = 0^{\circ}C$  to  $70^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ ,  $V_{CC} = +5V$ ,  $V_{EE} = -5V$ , unless otherwise noted.)

| PARAMETER                                | SYMBOL                            | CONDITIONS                                                     | MIN | TYP | MAX | UNITS |

|------------------------------------------|-----------------------------------|----------------------------------------------------------------|-----|-----|-----|-------|

| DC CHARACTERISTICS                       |                                   |                                                                | 1   |     |     |       |

| V <sub>CC</sub> Supply Current           | Icc                               | All logic inputs = GND or V <sub>CC</sub>                      |     | 0.4 | 1.0 | mA    |

| TERMINATOR PINS                          |                                   |                                                                | •   |     |     |       |

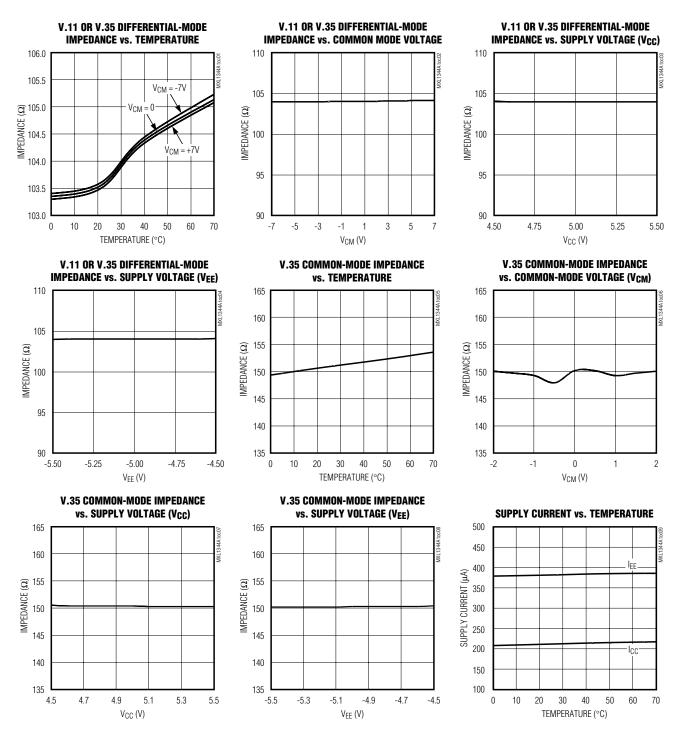

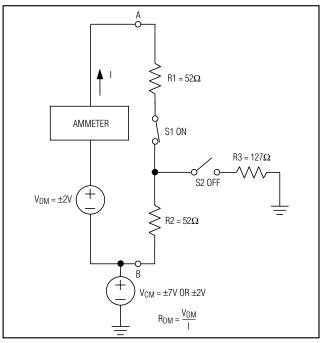

| Differential-Mode Impedance<br>V.35 Mode |                                   | -2V ≤ V <sub>CM</sub> ≤ +2V, all loads, Figure 1               | 90  | 104 | 110 | Ω     |

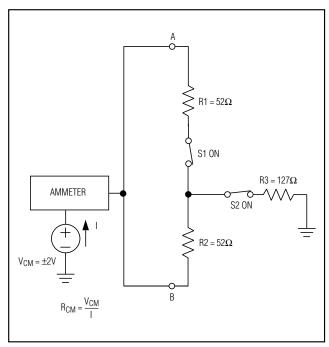

| Common-Mode Impedance<br>V.35 Mode       |                                   | -2V ≤ V <sub>CM</sub> ≤ +2V, all loads, Figure 2               | 135 | 153 | 165 | Ω     |

| Differential-Mode Impedance              |                                   | V <sub>CM</sub> = 0V, all loads                                | 100 | 104 | 110 | Ω     |

| V.11 Mode                                |                                   | -7V ≤ V <sub>CM</sub> ≤ +7V, all loads, T <sub>A</sub> = +25°C | 100 | 104 |     | \$2   |

| High-Impedance Leakage<br>Current        | IZ                                | -7V ≤ V <sub>CM</sub> ≤+7V, all loads                          |     |     | 50  | μA    |

| LOGIC INPUTS (M0, M1, M2, L              | ATCH, DCE/I                       | DTE)                                                           |     |     |     |       |

| Input High Voltage                       | VIH                               |                                                                | 2.0 |     | •   | V     |

| Input Low Voltage                        | V <sub>I</sub> L                  |                                                                |     |     | 0.8 | V     |

| Logic Input Current                      | I <sub>IH</sub> , I <sub>IL</sub> | V <sub>IN</sub> = V <sub>CC</sub> or GND                       |     |     | ±10 | μΑ    |

# **Typical Operating Characteristics**

(V<sub>CC</sub> = +5V, V<sub>EE</sub> = -5V,  $T_A$  = +25°C, unless otherwise noted.)

### **Pin Description**

| PIN    | NAME            | FUNCTION                                                                                                                                                                              |  |  |  |  |  |  |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1      | MO              | Mode-Select Pin (Table 1)                                                                                                                                                             |  |  |  |  |  |  |

| 2      | VEE             | Negative Supply Voltage (typically connected to VEE of MXL1543*). Bypass to GND with a $0.1 \mu F$ capacitor.                                                                         |  |  |  |  |  |  |

| 3      | R1C             | Load 1, Center Tap                                                                                                                                                                    |  |  |  |  |  |  |

| 4      | R1B             | Load 1, Node B                                                                                                                                                                        |  |  |  |  |  |  |

| 5      | R1A             | Load 1, Node A                                                                                                                                                                        |  |  |  |  |  |  |

| 6      | R2A             | Load 2, Node A                                                                                                                                                                        |  |  |  |  |  |  |

| 7      | R2B             | Load 2, Node B                                                                                                                                                                        |  |  |  |  |  |  |

| 8      | R2C             | Load 2, Center Tap                                                                                                                                                                    |  |  |  |  |  |  |

| 9      | R3A             | Load 3, Node A                                                                                                                                                                        |  |  |  |  |  |  |

| 10     | R3B             | Load 3, Node B                                                                                                                                                                        |  |  |  |  |  |  |

| 11     | R3C             | Load 3, Center Tap                                                                                                                                                                    |  |  |  |  |  |  |

| 12, 13 | GND             | Ground                                                                                                                                                                                |  |  |  |  |  |  |

| 14     | V <sub>CC</sub> | +5V Supply Voltage. Bypass to GND with a 0.1μF capacitor.                                                                                                                             |  |  |  |  |  |  |

| 15     | R4B             | Load 4, Node B                                                                                                                                                                        |  |  |  |  |  |  |

| 16     | R4A             | Load 4, Node A                                                                                                                                                                        |  |  |  |  |  |  |

| 17     | R5B             | Load 5, Node B                                                                                                                                                                        |  |  |  |  |  |  |

| 18     | R5A             | Load 5, Node A                                                                                                                                                                        |  |  |  |  |  |  |

| 19     | R6A             | Load 6, Node A                                                                                                                                                                        |  |  |  |  |  |  |

| 20     | R6B             | Load 6, Node B                                                                                                                                                                        |  |  |  |  |  |  |

| 21     | LATCH           | Latch Signal Input. When $\overline{\text{LATCH}}$ is LOW, the input latches are transparent. When $\overline{\text{LATCH}}$ is high, the data at the mode-select inputs are latched. |  |  |  |  |  |  |

| 22     | DCE/ DTE        | Logic Level HIGH selects DCE interface, (Table 1)                                                                                                                                     |  |  |  |  |  |  |

| 23     | M2              | Mode-Select Pin (Table 1)                                                                                                                                                             |  |  |  |  |  |  |

| 24     | M1              | Mode-Select Pin (Table 1)                                                                                                                                                             |  |  |  |  |  |  |

<sup>\*</sup>VEE is typically supplied by the charge pump of the MXL1543. The VEE input level varies with the mode of chipset operation as follows:

V.35/V.28 Modes:  $-6.50V \le V_{EE} \le -5.45V$ , in typical operation  $V_{EE} = -5.80V$  V.10/V.11 Modes:  $-4.60V \le V_{EE} \le -3.80V$ , in typical operation  $V_{EE} = -4.20V$

### **Detailed Description**

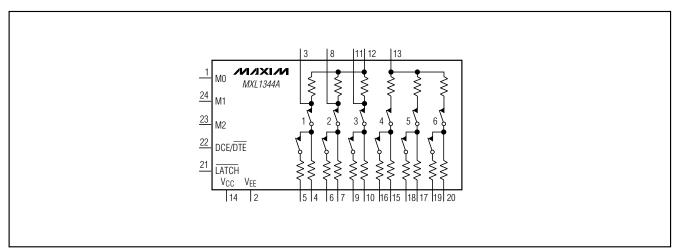

The MXL1344A contains six software-selectable multiprotocol cable termination networks (Figure 3). Each network is capable of terminating V.11 (RS-422, RS-530, RS-530A, RS-449, V.36 and X.21) with a  $100\Omega$  differential load, V.35 with a T-network load, or V.28 (RS-232) and V.10 (RS-423) with an open-circuit load for use with transceivers having on-chip termination. The termination protocol can be selected by the serial interface cable wiring or by software control. The MXL1344A replaces discrete resistor termination net-

works and expensive relays required for multiprotocol termination, saving space and cost.

The MXL1344A terminator is designed to form a complete +5V cable- or software-selectable multiprotocol DTE/DCE interface port when used with the MXL1543 and MXL1544/MAX3175 transceivers. The MXL1344A terminator can use the VEE power generated by the MXL1543 charge pump, simplifying system design. The MXL1344A, MXL1543, and MXL1544/MAX3175 are pinfor-pin compatible with the LTC1344A, LTC1543, and LTC1544, but for proper operation, the entire Maxim

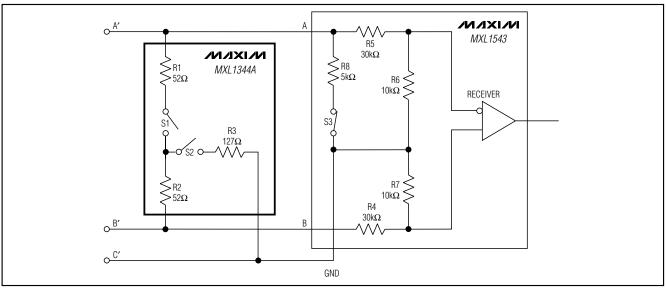

Figure 1. V.11 or V.35 Differential Impedance Measurement

Figure 2. V.35 Common-Mode Impedance Measurement

Figure 3. Block Diagram

chipset must be used without substituting other manufacturer's parts on a chip-by-chip basis.

#### **Termination Modes**

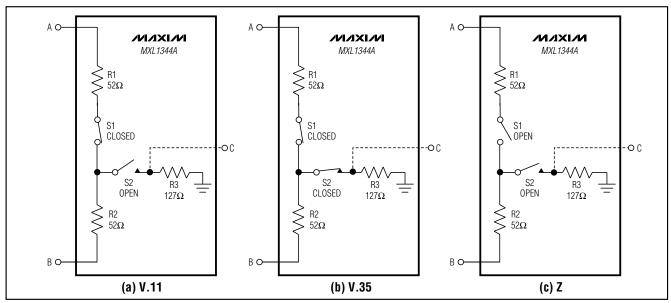

The termination networks in the MXL1344A can be set to one of three modes, V.11, V.35, or high impedance (high-Z). As shown in Figure 4, in V.11 mode, switch S1

is closed and switch S2 is open, presenting  $104\Omega$  across terminals A and B. In V.35 mode, switches S1 and S2 are both closed, presenting a T-network with  $104\Omega$  differential impedance and  $153\Omega$  common-mode impedance. In high-Z mode, switches S1 and S2 are both open, presenting a high impedance across terminals A and B suitable for V.28 and V.10 modes.

Figure 4. Termination Modes

**Table 1. Termination Mode Select Table**

| PROTOCOL    | DCE/ DTE | M2 | M1 | МО | R1   | R2   | R3   | R4   | R5   | R6   |

|-------------|----------|----|----|----|------|------|------|------|------|------|

| V.10/RS-423 | 0        | 0  | 0  | 0  | Z    | Z    | Z    | Z    | Z    | Z    |

| RS-530A     | 0        | 0  | 0  | 1  | Z    | Z    | Z    | V.11 | V.11 | V.11 |

| RS-530      | 0        | 0  | 1  | 0  | Z    | Z    | Z    | V.11 | V.11 | V.11 |

| X.21        | 0        | 0  | 1  | 1  | Z    | Z    | Z    | V.11 | V.11 | V.11 |

| V.35        | 0        | 1  | 0  | 0  | V.35 | V.35 | Z    | V.35 | V.35 | V.35 |

| RS-449/V.36 | 0        | 1  | 0  | 1  | Z    | Z    | Z    | V.11 | V.11 | V.11 |

| V.28/RS-232 | 0        | 1  | 1  | 0  | Z    | Z    | Z    | Z    | Z    | Z    |

| No Cable    | 0        | 1  | 1  | 1  | V.11 | V.11 | V.11 | V.11 | V.11 | V.11 |

| V.10/RS-423 | 1        | 0  | 0  | 0  | Z    | Z    | Z    | Z    | Z    | Z    |

| RS-530A     | 1        | 0  | 0  | 1  | Z    | Z    | Z    | Z    | V.11 | V.11 |

| RS-530      | 1        | 0  | 1  | 0  | Z    | Z    | Z    | Z    | V.11 | V.11 |

| X.21        | 1        | 0  | 1  | 1  | Z    | Z    | Z    | Z    | V.11 | V.11 |

| V.35        | 1        | 1  | 0  | 0  | V.35 | V.35 | V.35 | Z    | V.35 | V.35 |

| RS-449/V.36 | 1        | 1  | 0  | 1  | Z    | Z    | Z    | Z    | V.11 | V.11 |

| V.28/RS-232 | 1        | 1  | 1  | 0  | Z    | Z    | Ζ    | Z    | Z    | Z    |

| No Cable    | 1        | 1  | 1  | 1  | V.11 | V.11 | V.11 | V.11 | V.11 | V.11 |

Note: Z Indicates high impedance, 1 = high and 0 = low. Z, V.11, and V.35 refer to termination modes (Figure 4.)

The state of the MXL1344A's mode-select pins, M0, M1, M2, and DCE/DTE determines the mode of each of the six termination networks. Table 1 shows a cross-reference of termination mode and select pin state for

each of the six termination networks within the MXL1344A.

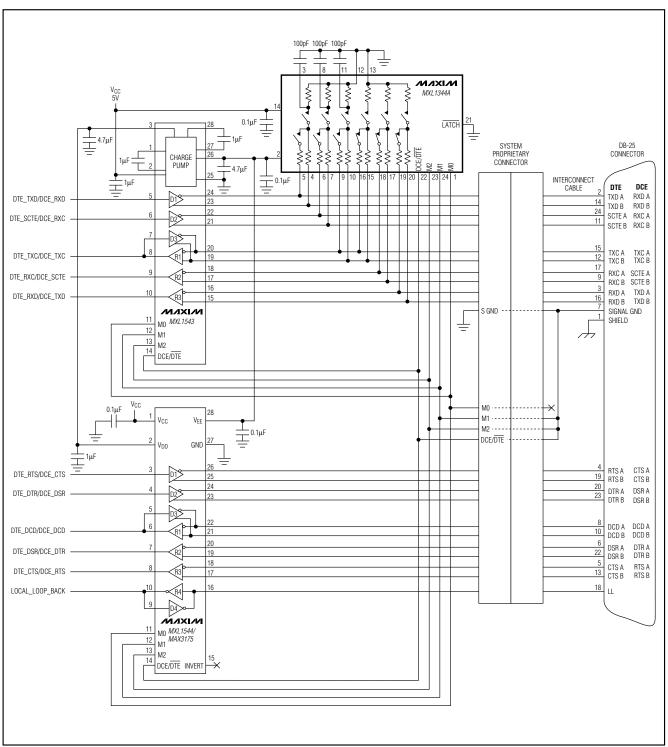

Figure 5. Cable-Selectable Multiprotocol DCE/DTE Serial Interface (Configured in RS-530A DTE Mode)

#### **No-Cable Mode**

The MXL1344A enters no-cable mode when the mode select inputs, M0, M1, and M2 are connected HIGH or left unconnected. In no-cable mode, all six termination networks are placed in V.11 mode, with S1 closed and S2 open (Figure 4).

### **Applications Information**

Older multiprotocol interface termination circuits have been constructed using expensive relays with discrete resistors, custom cables with built-in termination, or complex circuit-board configurations to route signals to

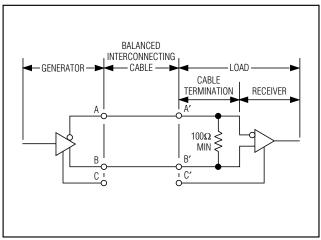

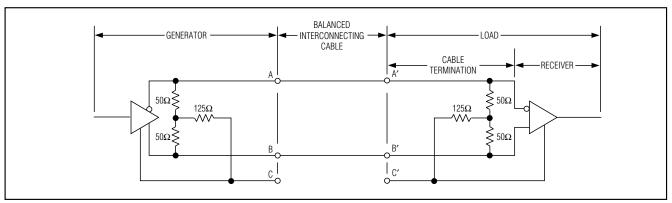

Figure 6. Typical V.11 Interface

the correct termination. The MXL1344A provides a simple solution to this termination problem. All required termination configurations are easily cable- or software-selectable using the four mode-control input pins M0, M1, M2, and DCE/DTE.

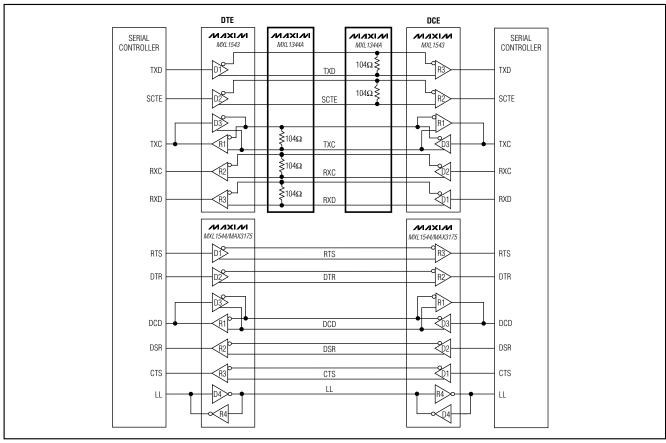

#### Using the MXL1344A in a Multiprotocol Serial Interface

The MXL1344A terminator is designed to form a complete +5V cable- or software-selectable multiprotocol DCE/DTE interface port when used with the MXL1543 and MXL1544/MAX3175 differential driver/receivers. The MXL1344A terminator is designed to use the VFF power generated by the MXL1543's charge pump and will meet all data sheet specifications when connected as illustrated in Figure 5. The mode-selection tables of all three devices are identical, allowing the M0, M1, M2, and DCE/DTE pins of each device to be connected to a single 4-wire control bus. The MXL1543 and MXL1544/ MAX3175 provide internal pullups for the four lines, forcing them to the logic high state if they are not grounded. This allows interface-mode configuration by simply strapping the appropriate pins to ground in the interconnect cable.

In Figure 5, M1, M2 and DCE/DTE are shorted to the cable ground, forcing logic LOW on these control lines. Input M0 is left floating and will be pulled HIGH by internal pullups on the MXL1543 and MXL1544/

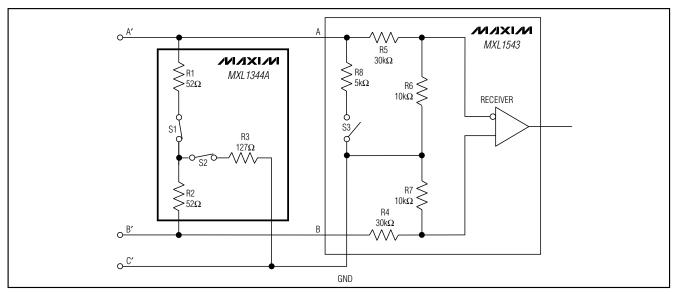

Figure 7. V.11 Termination and Internal Resistance Networks

Figure 8. Typical V.35 Interface

Figure 9. V.35 Termination and Internal Resistance Networks

MAX3175. With this cable wiring, the multiprotocol serial port is set in RS-530A DTE mode (Table 1).

#### V.11 Termination

A standard V.11 interface is shown in Figure 6. For high-speed data transmission, the V.11 specification recommends terminating the cable at the receiver with a  $100\Omega$  (min) resistor. The resistor, although not required, prevents reflections from corrupting transmitted data.

In Figure 7, the MXL1344A is used to terminate the V.11 receiver on the MXL1543. Internal to the MXL1344A, S1 is closed and S2 is open to present a  $104\Omega$  typical differential resistance and high-Z common-mode impedance. The MXL1543's internal V.28 termination is disabled by opening S3.

The V.11 specification allows for signals with common-mode variations of  $\pm 7 \text{V}$  and differential signal amplitudes from 2V to 6V with data rates as high as 10Mbps. The MXL1344A maintains termination impedance between  $100\Omega$  and  $110\Omega$  over these conditions.

#### V.35 Termination

Figure 8 shows a standard V.35 interface. The generator and the load must both present a  $100\Omega \pm 10\Omega$  differential impedance and a  $150\Omega \pm 15\Omega$  common-mode impedance. The V.35 driver generates a current output ( $\pm 11\text{mA}$  typ) that develops an output voltage between 440mV and 660mV across the load termination networks.

In Figure 9, the MXL1344A is used to implement the resistive T-network that is needed to properly terminate

the V.35 receiver. Internal to the MXL1344A, S1 and S2 are closed to connect the T-network resistors to the circuit.

The V.35 specification allows for ±4V of ground difference between the V.35 generator and V.35 load, with data rates as high as 10Mbps. The MXL1344A maintains correct termination impedance over these conditions.

#### V.35 EMI reduction

For applications where EMI reduction is especially important, the MXL1344A termination networks provide a pin for shunting common-mode driver currents to GND. Mismatches between the driver A and B output propagation delays can create a common-mode disturbance on the cable. This common-mode energy can be shunted to GND by placing a 100pF capacitor to GND from the center tap of the T-network termination (R1C, R2C and R3C as shown in Figure 5).

#### V.28 Termination

Most industry-standard V.28 receivers (including the MXL1543) do not require external termination because the receiver includes an internal  $5k\Omega$  termination resistor. When the MXL1344A is placed in V.28 mode, all six of the termination networks are placed in a high-Z mode. In high-Z mode, the MXL1344A termination networks will not interfere with the MXL1543's internal  $5k\Omega$  termination.

In Figure 10, the MXL1344A and MXL1543 are placed in V.28 mode. Switches S1 and S2 are opened on the MXL1344A to place the network in high-Z mode. Switch S3 is closed on the MXL1543 to enable the  $5k\Omega$  terminating resistor.

#### A Complete X.21 Interface

A complete DTE-to-DCE interface operating in X.21 mode is shown in Figure 11. The MXL1344A terminates the V.11 clock and data signals. The MXL1543 carries the clock and data signals, and the MXL1544/MAX3175 carries the control signals. The control signals generally do not require external termination.

### **Compliance Testing**

A European Standard EN 45001 test report for the MXL1543, MXL1544/MAX3175, and MXL1344A chipset will be available from Maxim upon completion of testing. Contact Maxim Quality Assurance for a copy of the report.

### **Chip Information**

TRANSISTOR COUNT: 1,054

PROCESS TECHNOLOGY: BICMOS

## **Pin Configuration**

Figure 10. V.28 Termination and Internal Resistance Networks

Figure 11. DTE-to-DCE X.21 Interface

# **Package Information**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

# AMEYA360 Components Supply Platform

# **Authorized Distribution Brand:**

# Website:

Welcome to visit www.ameya360.com

### Contact Us:

# > Address:

401 Building No.5, JiuGe Business Center, Lane 2301, Yishan Rd Minhang District, Shanghai , China

### > Sales:

Direct +86 (21) 6401-6692

Email amall@ameya360.com

QQ 800077892

Skype ameyasales1 ameyasales2

# Customer Service :

Email service@ameya360.com

# Partnership :

Tel +86 (21) 64016692-8333

Email mkt@ameya360.com