# **TDA18219HN**

# Silicon Tuner for terrestrial and cable digital TV reception

Rev. 01 — 3 February 2010

Objective data sheet

## 1. General description

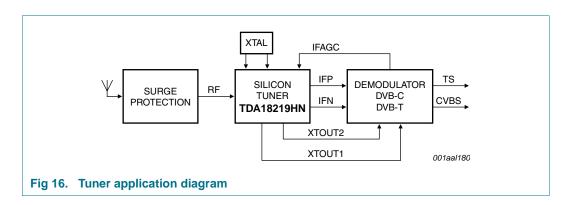

The TDA18219HN complies with most digital TV standards and delivers a LOW IF signal to a channel demodulator for digital TV. Standards that are covered include DVB-T, ISDB-T, DTMB and DVB-C.

The TDA18219HN facilitates design-ins as:

- Allowing easy on-board integration

- · Drastically reducing the size of the tuner function

- Providing flexibility in system solution development

#### 2. Features

- Fully integrated IF selectivity; eliminating the need for external SAW filters

- Fully integrated oscillators

- Alignment free

- Single 3.3 V supply voltage

- Low power consumption

- Integrated wideband gain control

- Crystal oscillator output buffer (16 MHz) for single crystal applications

- I<sup>2</sup>C-bus interface compatible with 3.3 V microcontrollers

- Easy programming

- 5 ms tuning time

- LOW IF channel center frequency output ranging from 3 MHz to 5 MHz

- 1.7 MHz, 6 MHz, 7 MHz and 8 MHz channel bandwidths

- Loop-Through (LT)

- RoHS compliant

# 3. Applications

- Digital TV for STB, PCTV, DVD-R and TV applications

- Digital (DVB-T/C/H, DTMB, ISDB-T) worldwide standards supported

- Targeted specification (based on channel decoder or demodulator capabilities):

- ◆ NorDig cable (EU)

- C-BOOK conformance (Cable, EU)

- ◆ NorDig 2.0 compliance (EU TV)

- ◆ E-BOOK and D-BOOK compliances

- ◆ ARIB STD-B21 for ISDB-T

# 4. Quick reference data

Table 1. Quick reference data

| Symbol               | Parameter                    | Conditions                                                                           | Min  | Тур | Max | Unit   |

|----------------------|------------------------------|--------------------------------------------------------------------------------------|------|-----|-----|--------|

| $f_{RF}$             | RF frequency                 | full range of RF input                                                               | 42   | -   | 870 | MHz    |

|                      |                              | center of channel                                                                    | 45   | -   | 866 | MHz    |

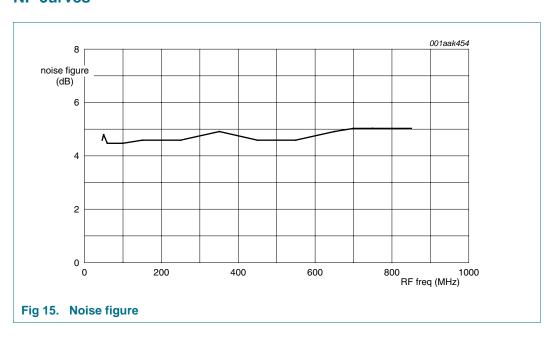

| NF <sub>tun</sub>    | tuner noise figure           | 75 $\Omega$ source; maximum gain                                                     | -    | 5.0 | 5.9 | dB     |

| Φjit                 | phase jitter                 | UHF; integrated from 1 kHz to 4 MHz                                                  | -    | 0.5 | 0.7 | degree |

| $lpha_{	ext{image}}$ | image rejection              | worst case for image rejection and<br>4 MHz IF frequency for levels above<br>–50 dBm | 57.5 | 63  | -   | dB     |

| ICP <sub>1dB</sub>   | 1 dB input compression point | at tuner input and minimum gain                                                      | 124  | -   | -   | dΒμV   |

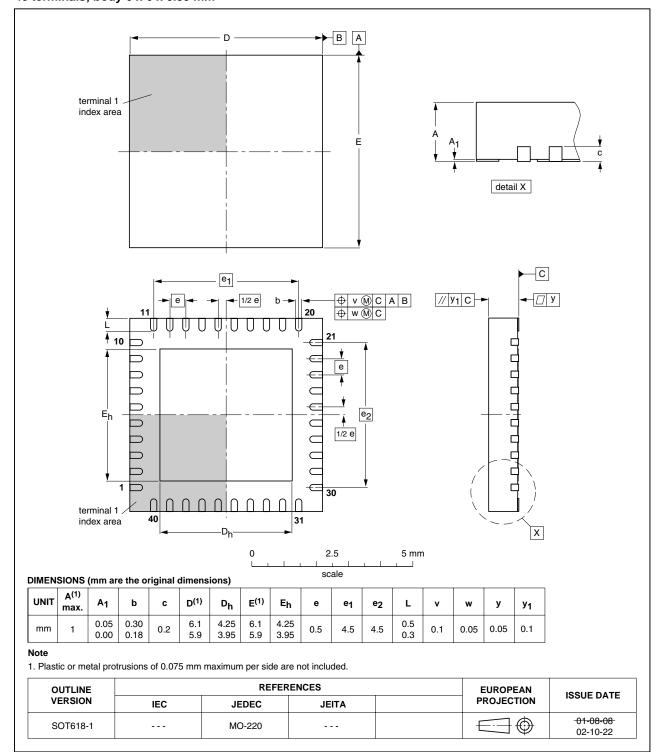

# 5. Ordering information

Table 2. Ordering information

| Type number   | Package |                                                                                                            |          |  |  |  |  |  |  |

|---------------|---------|------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|

|               | Name    | Description                                                                                                | Version  |  |  |  |  |  |  |

| TDA18219HN/C1 | HVQFN40 | plastic thermal enhanced very thin quad flat package; no leads; 40 terminals; body $6\times6\times0.85$ mm | SOT618-1 |  |  |  |  |  |  |

# 6. Marking

Table 3. Marking codes

| Type number   | Marking code |

|---------------|--------------|

| TDA18219HN/C1 | 18219HN      |

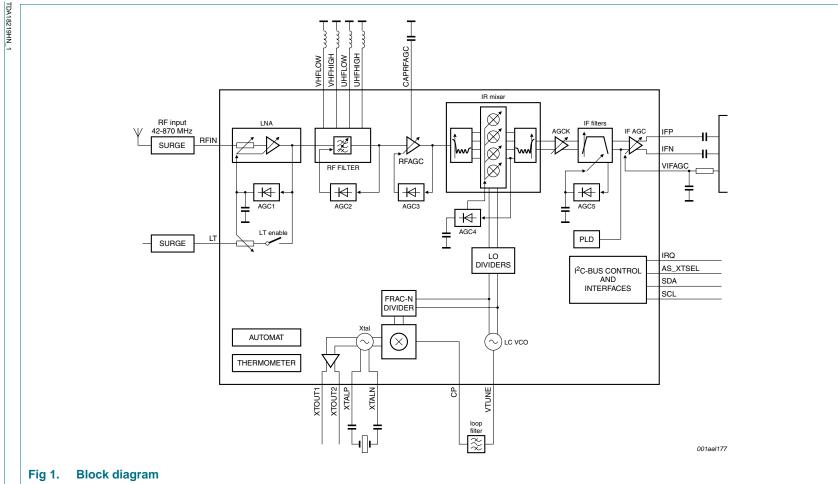

# Block diagram

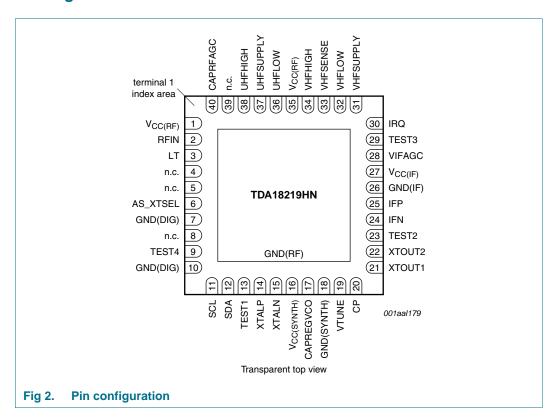

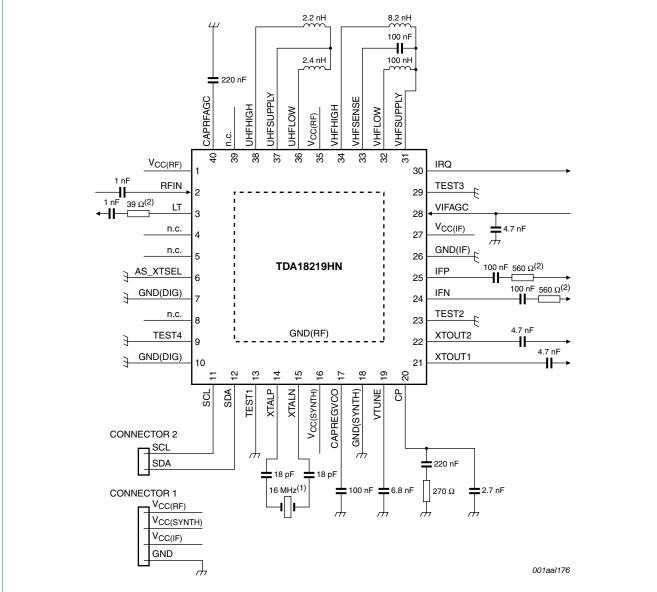

# 8. Pinning information

#### 8.1 Pinning

#### 8.2 Pin description

Table 4. Pin description

| Symbol       | Pin | Description                                                  |  |  |  |

|--------------|-----|--------------------------------------------------------------|--|--|--|

| $V_{CC(RF)}$ | 1   | RF supply voltage                                            |  |  |  |

| RFIN         | 2   | unbalanced RF input                                          |  |  |  |

| LT           | 3   | loop-through output                                          |  |  |  |

| n.c.         | 4   | not connected                                                |  |  |  |

| n.c.         | 5   | not connected                                                |  |  |  |

| AS_XTSEL     | 6   | I <sup>2</sup> C-bus address and XTOUT level selection input |  |  |  |

| GND(DIG)     | 7   | digital ground supply voltage                                |  |  |  |

| n.c.         | 8   | not connected                                                |  |  |  |

| TEST4        | 9   | test input 4, must be connected to ground                    |  |  |  |

| GND(DIG)     | 10  | digital ground supply voltage                                |  |  |  |

| SCL          | 11  | I <sup>2</sup> C-bus clock input                             |  |  |  |

| SDA          | 12  | I <sup>2</sup> C-bus data input/output                       |  |  |  |

| TEST1        | 13  | test input 1, must be connected to ground                    |  |  |  |

| XTALP        | 14  | crystal oscillator positive input                            |  |  |  |

| XTALN        | 15  | crystal oscillator negative input                            |  |  |  |

TDA18219HN\_1 © NXP B.V. 2010. All rights reserved.

Table 4.

Pin description ...continued

| Symbol                 | Pin     | Description                               |

|------------------------|---------|-------------------------------------------|

| V <sub>CC(SYNTH)</sub> | 16      | synthesizer supply voltage                |

| CAPREGVCO              | 17      | VCO regulator filtering input             |

| GND(SYNTH)             | 18      | synthesizer ground                        |

| VTUNE                  | 19      | VCO tuning voltage input                  |

| СР                     | 20      | charge pump output                        |

| XTOUT1                 | 21      | crystal oscillator buffer output 1        |

| XTOUT2                 | 22      | crystal oscillator buffer output 2        |

| TEST2                  | 23      | test input 2, must be connected to ground |

| IFN                    | 24      | IF negative output                        |

| IFP                    | 25      | IF positive output                        |

| GND(IF)                | 26      | IF ground                                 |

| V <sub>CC(IF)</sub>    | 27      | IF supply voltage                         |

| VIFAGC                 | 28      | IF gain control input                     |

| TEST3                  | 29      | test input 3, must be connected to ground |

| IRQ                    | 30      | interrupt request output                  |

| VHFSUPPLY              | 31      | RF filter VHF supply input                |

| VHFLOW                 | 32      | RF filter VHF LOW input                   |

| VHFSENSE               | 33      | RF filter VHF sense                       |

| VHFHIGH                | 34      | RF filter VHF HIGH input                  |

| $V_{CC(RF)}$           | 35      | RF filter supply voltage                  |

| UHFLOW                 | 36      | RF filter UHF LOW input                   |

| UHFSUPPLY              | 37      | RF filter UHF supply input                |

| UHFHIGH                | 38      | RF filter UHF HIGH input                  |

| n.c.                   | 39      | not connected                             |

| CAPRFAGC               | 40      | RF AGC filtering                          |

| GND(RF)                | die pad | RF ground                                 |

|                        |         |                                           |

# 9. Functional description

The Silicon Tuner is based on single down-conversion and LOW IF architecture (LIF) that allows full integration of selectivity and eliminates the need for external SAW filters.

The RF input signal is fed to the input splitter, built-out of a Low Noise Amplifier (LNA). It is followed by an alignment free RF tuned filter to protect the rest of the tuner function against strong unwanted signals.

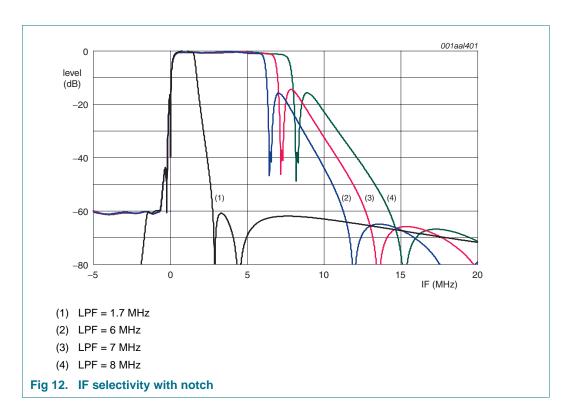

The LOW IF concept needs complex signals that highly suppress the N + 1 image channel thanks to image rejection calibration. The IF selectivity is performed by a complex filter and a IF filter which depends on IF frequency choice and channel bandwidth. The IF filter is built with a IF Low-Pass Filter (LPF), an IF notch filter which can be activated to suppress the residual adjacent N - 1 sound carrier and a programmable IF High-Pass Filter (HPF) for more flexibility on IF frequency.

#### Silicon Tuner for terrestrial and cable digital TV reception

Continuous gain control is performed after the RF filters and the IF selectivity. Stepped AGC is available at all stages (LNA, RF filter, mixer and IF LPF) in order to optimize the tuner signal-to-noise ratio. Gain settings of all stepped AGC and the RF AGC amplifier are controlled by internal broadband level detectors. The steps in the different stages are automatically compensated in IF with AGCK to keep a constant IF output level. The gain of the IF AGC amplifier is controlled by the demodulator to take advantage of the full ADC dynamic range.

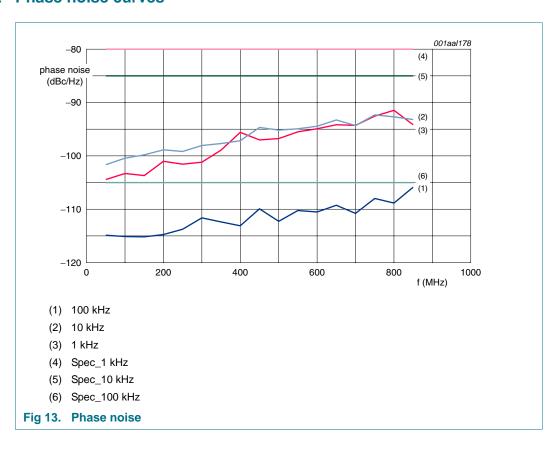

A single LC-VCO operating at 7 GHz is used within a fractional-N phase lock-loop to generate the LO frequency. The clock reference signal is provided by a crystal oscillator and can be provided to a demodulator through the crystal output buffer.

All the programming is done via I<sup>2</sup>C-bus transceiver. An embedded test tone generator is used for automatic calibration at power-on-reset.

The power level indicator can be used to indicate the RF input signal strengths of the received channel.

#### 9.1 RF filter

The RF filter block is an alignment free tunable band-pass filter. After self calibration at power-on to compensate for external and internal components spread, the center frequency is automatically tuned to the desired frequency set via I<sup>2</sup>C-bus to suppress the undesired interferers available on the broadband spectrum.

#### 9.2 Crystal output mode

Pins XTOUT1 and XTOUT2 deliver a symmetrical sine waveform to drive the channel demodulator. The load on these outputs should be made identical to ensure optimum performance matching. Hence, if only one crystal output is used, the unused output must be loaded by the same capacitance. The XTOUT output level can be set to either 400 mV (p-p) or 800 mV (p-p) single ended.

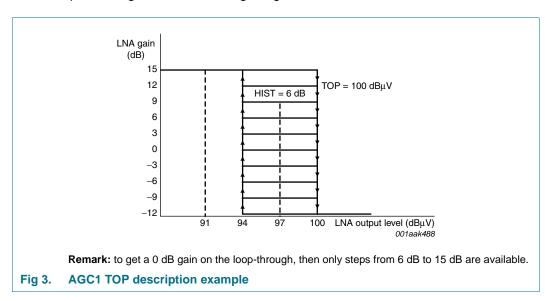

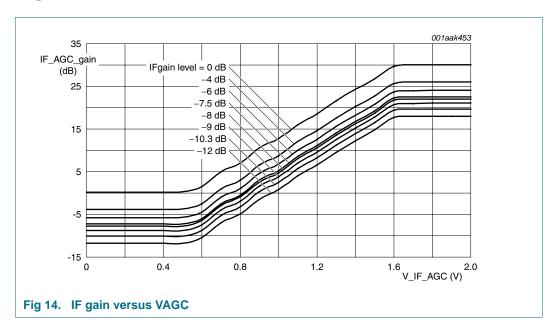

#### 9.3 AGC description

The tuner gain is composed of different variable gain stages spread according to block diagram. Using the different detectors at different stages, the gain is distributed to offer best linearity/noise compromise. The gain steps are 3 dB steps and in order to ensure gain continuity a specific stage called AGCK aims at compensating these internal steps to a minimum value. At the tuner output the gain variations appear to be continuous.

The tuner gain is externally controlled via IF AGC command (VIFAGC pin) provided to the tuner to make sure the following ADC are used full scale. The RF gain is set automatically, in accordance with the AGC TOP values.

The different stages gain values are then a combination of the following input parameters:

- Input signal

- TOP values set via I2C-bus

- IFAGC command

#### Silicon Tuner for terrestrial and cable digital TV reception

In the circuit, the Take Over Point (TOP) are programmable to offer the optimal noise/linearity compromise during reception. The TOP are carefully selected not to overload following stages nor to have too weak signal to noise ratio. They correspond to decision points where the gain distribution changes inside the tuner.

In order to avoid instability of gain chain while working around level decision point a hysteresis has been implemented to avoid gain toggling. This is the reason why there are different values for TOP-up / TOP-down. Its main purpose is to make sure gain switch occurs to prevent signal distortion along the gain chain.

The TOP values are considered as tuner settings and could cause performances degradations if wrongly set.

Table 5. AGC number / block correspondence

| AGC number | corresponding AGC block | comment                                    |  |  |  |  |  |  |  |

|------------|-------------------------|--------------------------------------------|--|--|--|--|--|--|--|

| AGC1       | LNA AGC                 |                                            |  |  |  |  |  |  |  |

| AGC2       | RF Filter AGC           | Not described, handled internally by tuner |  |  |  |  |  |  |  |

| AGC3       | RF AGC                  |                                            |  |  |  |  |  |  |  |

| AGC4       | Mixer AGC               |                                            |  |  |  |  |  |  |  |

| AGC5       | LPF AGC                 |                                            |  |  |  |  |  |  |  |

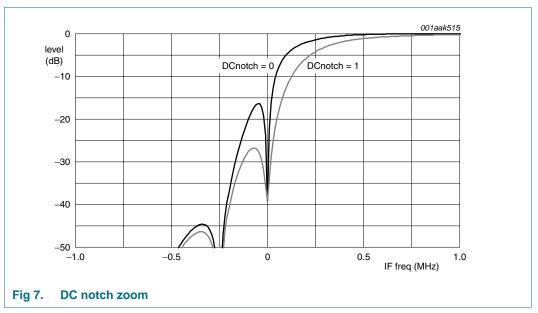

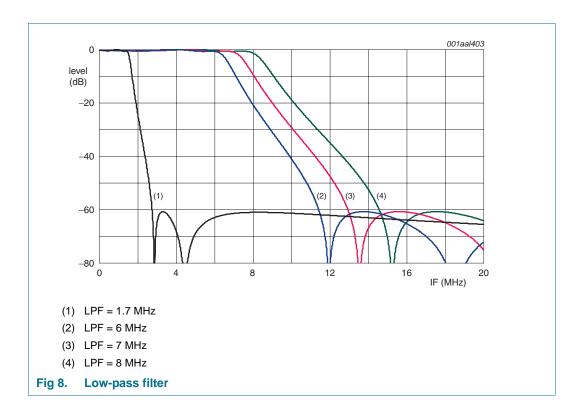

#### 9.4 Low-pass filter (LPF)

The programmable LPF avoids aliasing of demodulators Analog-to-Digital converters. In addition, it suppresses the remaining signals. The programming allows to receive signal bandwidth of 1.7 MHz, 6 MHz, 7 MHz and 8 MHz.

#### 9.5 High-pass filter (HPF)

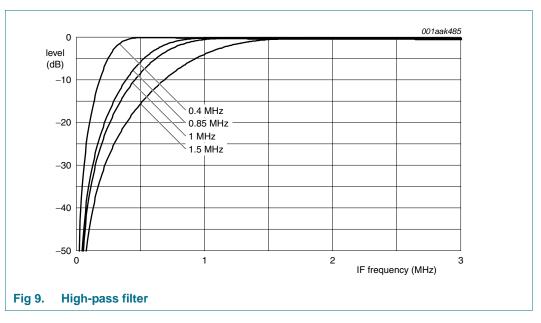

The HPF helps removing residual adjacent (N + 1) channel power after image rejection has been performed.

**TDA18219HN NXP Semiconductors**

#### Silicon Tuner for terrestrial and cable digital TV reception

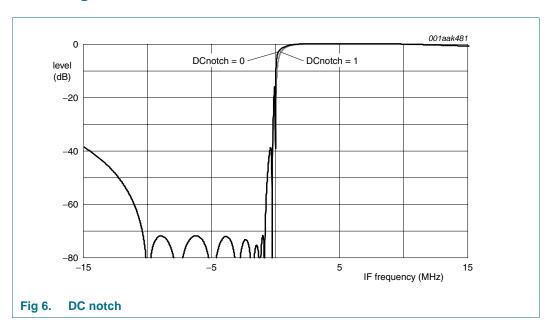

#### 9.6 Notch filter

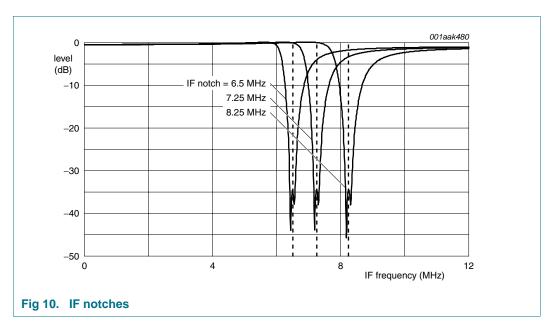

This block has been implemented in the IF filter to optionally provide additional robustness against adjacent analog channels. It reduces the adjacent channel sound carrier level to prevent overloading of IF output stage. The notch frequency is tracked with LPF settings.

#### 9.7 IR mixer

The LOW IF concept needs complex signals that highly suppress the N + 1 image channel thanks to image rejection calibration.

#### 9.8 LO generation

A single LC-VCO operating at 7 GHz is used within a fractional-N phase lock-loop to generate the LO frequency. The clock reference signal is provided by a crystal oscillator and can be provided to a demodulator through the crystal output buffer.

#### 9.9 Thermometer

The thermometer can be used to indicate the junction temperature of the IC via I<sup>2</sup>C-bus for soldering check. Refer to Section 10.1.2 for detailed description and operation.

#### 9.10 Power Level Detector (PLD)

The power level indicator can be used to indicate the RF input signal strengths of the received channel via I<sup>2</sup>C-bus. Refer to Section 10.1.4 for detailed description and operation.

#### 9.11 I<sup>2</sup>C-bus transceiver

The TDA18219HN is controlled via the two-wire I<sup>2</sup>C-bus. For programming, there is one device address (7-bit) and the R/W bit for selecting read or write mode. To be able to have flexibility in the addresses within the I<sup>2</sup>C-bus system, one of two possible addresses is selected depending on the voltage applied to address selection pin AS XTSEL (pin 6) see Table 28 "Pin AS\_XTSEL decoding".

NXP

Semiconductors

# 10.1 Register table description

Table 6. Register table description

| Table 6. | Register table description |                    |                 |            |        |                  |       |               |         |  |

|----------|----------------------------|--------------------|-----------------|------------|--------|------------------|-------|---------------|---------|--|

| SubAdd   | Name <sup>[1]</sup>        | D[7]               | D[6]            | D[5]       | D[4]   | D[3]             | D[2]  | D[1]          | D[0]    |  |

| 00h      | ID_byte_1                  | 1                  | 1 ident[14:8]   |            |        |                  |       |               |         |  |

| 01h      | ID_byte_2                  |                    | ident[7:0]      |            |        |                  |       |               |         |  |

| 02h      | ID_byte_3                  |                    | Major_r         | ev[3:0]    |        |                  | Minor | _rev[3:0]     |         |  |

| 03h      | Thermo_byte_1              | -                  |                 |            |        | TM_D[6:0]        |       |               |         |  |

| 04h      | Thermo_byte_2              | -                  | -               | -          | -      | -                | -     | -             | TM_ON   |  |

| 05h      | Power_state_byte_1         | -                  | -               | -          | -      | -                | -     | POR           | LO_Lock |  |

| 06h      | Power_state_byte_2         | -                  | -               | -          | -      | SM               | 0     | SM_LNA        | SM_XT   |  |

| 07h      | Input_Power_Level_byte     | -                  |                 |            |        | Power_Level[6:0  | 0]    |               |         |  |

| 08h      | IRQ_status                 | IRQ_status         | -               | -          | -      | -                | -     | -             | -       |  |

| 09h      | IRQ_enable                 | 1                  | -               | 0          | 0      | 0                | 0     | 0             | 0       |  |

| 0Ah      | IRQ_clear                  | IRQ_clear          | -               | 0          | 0      | 0                | 0     | 0             | 0       |  |

| 0Bh      | IRQ_set                    | 0                  | -               | 0          | 0      | 0                | 0     | 0             | 0       |  |

| 0Ch      | AGC1_byte_1                | LT_Enable          | AGC1_6_<br>15dB | -          | -      | AGC1_TOP[3:0]    |       |               |         |  |

| 0Dh      | AGC2_byte_1                | -                  | -               | -          | 0      | 1                | 1     | 1             | 1       |  |

| 0Eh      | AGCK_byte_1                | 0                  | 0               | 1          | 1      | 0                | 0     | 1             | 0       |  |

| 0Fh      | RF_AGC_byte_1              | PD_RFAGC<br>_Adapt | RFAGC_Adap      | t_TOP[1:0] | 1      | RF_Atten_<br>3dB |       | AGC3_Top[2:0  | )]      |  |

| 10h      | IR_MIXER_byte_1            | -                  | -               | -          | -      |                  | AGC4  | _Top[3:0]     |         |  |

| 11h      | AGC5_byte_1                | -                  | 0               | 0          | 0      |                  | AGC5  | _Top[3:0]     |         |  |

| 12h      | IF_AGC_byte                | -                  | -               | -          | -      | -                |       | IF_Level[2:0] |         |  |

| 13h      | IF_byte_1                  | IF_HP              | _Fc[1:0]        | IF_Notch   | LP_FC_ | Offset[1:0]      |       | LP_Fc[2:0]    |         |  |

| 14h      | Reference_byte             | 0                  | Digital_Clock   | -          | 0      | -                | -     | ХТо           | ut[1:0] |  |

| 15h      | IF_Frequency_byte          |                    |                 |            | IF_    | _Freq[7:0]       |       |               |         |  |

| 16h      | RF_Frequency_byte_1        | -                  | -               | -          | -      |                  | RF_Fr | req[19:16]    |         |  |

| 17h      | RF_Frequency_byte_2        |                    |                 |            | RF_    | Freq[15:8]       |       |               |         |  |

| 18h      | RF_Frequency_byte_3        |                    | RF_Freq[7:0]    |            |        |                  |       |               |         |  |

| Į, | Table 6. | Register | table o | lescript | ion | continued |

|----|----------|----------|---------|----------|-----|-----------|

|----|----------|----------|---------|----------|-----|-----------|

| SubAdd | Name <sup>[1]</sup>      | D[7]           | D[6]      | D[5]      | D[4]        | D[3]          | D[2] | D[1]          | D[0]       |

|--------|--------------------------|----------------|-----------|-----------|-------------|---------------|------|---------------|------------|

| 19h    | MSM_byte_1               | POWER_<br>Meas | RF_CAL_AV | RF_CAL    | IR_CAI      | <b>_[1:0]</b> | 0    | RC_CAL        | Calc_PLL   |

| 1Ah    | MSM_byte_2               | -              | -         | -         | -           | -             | -    | 0             | MSM_Launch |

| 1Bh    | PSM_byte_1               | 1              | 1         | VHFIII    | 1           | 1             | 1    | 1             | 1          |

| 1Ch    | DCC_byte_1               | 0              | 0         | 0         | 0           | -             | -    | -             | -          |

| 1Dh    | FLO_Max_byte             | -              | -         | 0         | 0           | 0             | 0    | 0             | 0          |

| 1Eh    | IR_Cal_byte_1            | 0              | 0         | 0         | 0           | 0             | 0    | 0             | 0          |

| 1Fh    | IR_Cal_byte_2            | 1              | 0         | 0         | 0           | 0             | 0    | 0             | 0          |

| 20h    | IR_Cal_byte_3            | -              | -         | -         | 0           | 0             | 0    | 0             | 0          |

| 21h    | IR_Cal_byte_4            | -              | -         | -         | 0           | 0             | 0    | 0             | 0          |

| 22h    | Vsync_Mgt_byte           | 0              | 0         | 0         | 0           | 0             | 0    | 0             | 1          |

| 23h    | IR_MIXER_byte_2          | 0              | 0         | 0         | -           | -             | -    | HI_Pass       | DC_NOTCH   |

| 24h    | AGC1_byte_2              | 0              | 0         | 0         | 0           | 1             | 0    | 0             | 1          |

| 25h    | AGC5_byte_2              | 0              | 0         | 0         | -           | 0             | -    | 0             | 1          |

| 26h    | RF_Cal_byte_1            | 0              | 0         | 0         | 0           | 0             | 0    | 0             | 0          |

| 27h    | RF_Cal_byte_2            | 0              | 0         | 0         | 0           | 0             | 0    | 0             | 0          |

| 28h    | RF_Cal_byte_3            | 0              | 0         | 0         | 0           | 0             | 0    | 0             | 0          |

| 29h    | RF_Cal_byte_4            | 0              | 0         | 0         | 0           | 0             | 0    | 0             | 0          |

| 2Ah    | RF_Cal_byte_5            | 0              | 0         | 0         | 0           | 0             | 0    | 0             | 0          |

| 2Bh    | RF_Cal_byte_6            | 0              | 0         | 0         | 0           | 0             | 0    | 0             | 0          |

| 2Ch    | RF_Filter_byte_1         | 0              | 0         | 0         | 0           | 1             | 0    | 1             | 1          |

| 2Dh    | RF_Filter_byte_2         | 0              | 0         | 0         | 0           | 0             | 0    | 0             | 0          |

| 2Eh    | RF_Filter_byte_3         | 0              | 0         | 0         | 0           | 0             | 0    | 0             | 0          |

| 2Fh    | RF_Band_Pass_Filter_byte | 0              | -         | -         | -           | -             | 1    | 1             | 0          |

| 30h    | CP_Current_byte          | -              | 1         | 0         | 0           | 0             | 1    | 1             | 1          |

| 31h    | AGC_Det_Out_byte         | Х              | Х         | Х         | X           | Χ             | Х    | X             | X          |

| 32h    | RF_AGC_Gain_byte_1       | -              | -         | RF_FILTER | R_GAIN[1:0] |               | LNA_ | GAIN[3:0]     |            |

| 33h    | RF_AGC_Gain_byte_2       | -              | -         | -         | -           | -             | 7    | TOP_Agc3_read | d[2:0]     |

| 34h    | IF_AGC_Gain_byte         | -              | -         | -         | LPF_GA      | IN[1:0]       |      | IR_MIXER[2:   | 0]         |

| 35h    | Power_byte_1             | Х              | Х         | Х         | Χ           | Х             | Х    | Х             | X          |

| 36h    | Power_byte_2             | -              | -         | 0         | X           | 1             | 1    | 1             | 0          |

NXP

Semiconductors

| 0.14.11 | Negister table description . |      | Droi | D.E.   | D. 41      | Droi | Droi | DIA  | Droi         |

|---------|------------------------------|------|------|--------|------------|------|------|------|--------------|

| SubAdd  | Name <sup>[1]</sup>          | D[7] | D[6] | D[5]   | D[4]       | D[3] | D[2] | D[1] | D[0]         |

| 37h     | Misc_byte_1                  | 1    | 1    | 0      | 0          | 1    | 0    | 0    | IRQ_Polarity |

| 38h     | rfcal_log_1                  | X    | Χ    | Χ      | X          | X    | X    | X    | X            |

| 39h     | rfcal_log_2                  | Х    | Χ    | Х      | X          | Х    | X    | X    | X            |

| 3Ah     | rfcal_log_3                  | Х    | Χ    | Х      | X          | Х    | X    | X    | X            |

| 3Bh     | rfcal_log_4                  | Х    | Χ    | Х      | X          | Х    | X    | X    | X            |

| 3Ch     | rfcal_log_5                  | Х    | Χ    | Х      | X          | Х    | X    | X    | X            |

| 3Dh     | rfcal_log_6                  | Х    | Χ    | Х      | X          | Х    | X    | X    | X            |

| 3Eh     | rfcal_log_6                  | Х    | Χ    | Х      | X          | Х    | X    | X    | X            |

| 3Fh     | rfcal_log_7                  | Х    | Χ    | Х      | X          | Х    | X    | X    | X            |

| 40h     | rfcal_log_8                  | Х    | X    | Х      | X          | Х    | X    | X    | X            |

| 41h     | rfcal_log_9                  | Х    | Χ    | Х      | X          | X    | X    | Х    | X            |

| 42h     | rfcal_log_10                 | Х    | Χ    | Х      | X          | X    | X    | Х    | X            |

| 43h     | rfcal_log_11                 | Х    | X    | Х      | X          | Х    | X    | X    | X            |

| 50h     |                              |      |      | FORBID | DEN ACCESS |      |      |      |              |

| 67h     |                              |      |      |        |            |      |      |      |              |

| FEh     |                              |      |      | FORBID | DEN ACCESS |      |      |      |              |

| FFh     | <del>-</del>                 |      |      |        |            |      |      |      |              |

<sup>[1]</sup> The settings optimization is bound to channel decoder or demodulator choice and has a high impact on the tuner performances within system environment. Refer to Application Note *AN1002* for optimal settings.

#### Remark:

- The values in <u>Table 6</u> must be written as described for normal operation of the tuner

- X means the value is provided by tuner and can be 0 or 1. Do not overwrite

- - means the value is undefined. No internal bit corresponds to this address.

#### 10.1.1 Device type address ID

Table 7. ID byte bit descriptions

| Address | Register  | Bit    | Symbol         | Access | Value | Description                 |

|---------|-----------|--------|----------------|--------|-------|-----------------------------|

| 00h     | ID_byte_1 | 6 to 0 | Ident[14:8]    | R      | 4724h | type number information     |

| 01h     | ID_byte_2 | 7 to 0 | Ident[7:0]     |        |       |                             |

| 02h     | ID_byte_3 | 7 to 4 | Major_rev[3:0] | R      |       | major releases; current = 1 |

|         |           | 3 to 0 | Minor_rev[3:0] | R      |       | minor releases; current = 1 |

#### **10.1.2 Temperature sensor**

Table 8. Temperature sensor bit descriptions

| Address | Register      | Bit    | Symbol    | Access | Value | Description                                                                                     |

|---------|---------------|--------|-----------|--------|-------|-------------------------------------------------------------------------------------------------|

| 03h     | Thermo_byte_1 | 6 to 0 | TM_D[6:0] | R      | -     | a junction temperature measurement ranging from 22 °C to 127 °C is indicated through these bits |

| 04h     | Thermo_byte_2 | 0      | TM_ON     | W      |       | temperature sensor ON or OFF                                                                    |

|         |               |        |           |        | 0     | temperature sensor switched off                                                                 |

|         |               |        |           |        | 1     | temperature sensor switched on                                                                  |

**Remark:** The thermometer value is updated each time a read is performed on the byte Thermo\_byte\_1, if TM\_ON is set to 1. Otherwise, temperature value is not updated.

#### 10.1.3 Power state

Table 9. Power state bit descriptions

| Address | Register           | Bit | Symbol  | Access | Value           | Description                                                                                                                                             |

|---------|--------------------|-----|---------|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05h     | Power_state_byte_1 | 1   | POR     | R      | -               | detects when the tuner supply voltage went<br>below POR threshold voltage. The tuner is then<br>reset to its original settings (tuner not initialized). |

|         |                    |     |         |        | 0               | once it has been read                                                                                                                                   |

|         |                    |     |         |        | 1               | the POR occurred on the tuner                                                                                                                           |

|         |                    | 0   | LO_Lock | R      |                 | LO lock flag                                                                                                                                            |

|         |                    |     |         |        | 0               | PLL unlocked                                                                                                                                            |

|         |                    |     |         |        | 1               | PLL locked                                                                                                                                              |

| 06h     | Power_state_byte_2 | 0   | SM_XT   | R/W    | see<br>Table 10 |                                                                                                                                                         |

|         |                    | 1   | SM_LNA  | R/W    | see<br>Table 10 |                                                                                                                                                         |

|         |                    | 3   | SM      | R/W    | see<br>Table 10 |                                                                                                                                                         |

Table 10. Mode selection

| SM[1] | SM_LNA[1] | SM_XT[1] | Mode                                 |

|-------|-----------|----------|--------------------------------------|

| 0     | 0         | 0        | Normal mode = ON                     |

| 1     | 0         | 0        | Standby mode with LT ON and XTOUT ON |

#### Silicon Tuner for terrestrial and cable digital TV reception

Table 10. Mode selection ... continued

| SM[1] | SM_LNA[1] | SM_XT[1] | Mode                                   |

|-------|-----------|----------|----------------------------------------|

| 1     | 0         | 1        | Standby mode with LT ON and XTOUT OFF  |

| 1     | 1         | 0        | Standby mode with LT OFF and XTOUT ON  |

| 1     | 1         | 1        | Standby mode with LT OFF and XTOUT OFF |

<sup>[1]</sup> All others values are forbidden.

#### 10.1.4 Power level detector

Table 11. Power level detector bit descriptions

| Address | Register               | Bit    | Symbol           | Access | Value | Description                                                                                                                                                                                  |

|---------|------------------------|--------|------------------|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07h     | Input_Power_Level_byte | 6 to 0 | Power_Level[6:0] | R      | -     | The power value is in the range from 40 dBμV (RMS) to 110 dBμV (RMS). Outside this range, Power_Level value <sup>[1]</sup> is computed as follows:  • power < 40 dBμV (RMS): Power_Level = 0 |

|         |                        |        |                  |        |       | <ul> <li>power &gt; 110 dBμV (RMS):</li> <li>Power_Level = 127</li> </ul>                                                                                                                    |

<sup>[1]</sup> Power\_Level value is updated only if requested via triggering of MSM\_byte\_1 and MSM\_byte\_2.

**Remark:** The power level measurement is not done continuously but only on request performed by using bytes MSM\_byte\_1 (19h) and MSM\_byte\_2 (1Ah):

- Set MSM\_byte\_1 to 80h to indicate a power measurement is required

- Trigger the measurement by writing 01h in MSM\_byte\_2

- Then read byte Input\_Power\_Level\_byte (07h) for result

**Remark:** This feature purpose is to ease antenna pointing when no picture is displayed on screen only. In case a power level detection is required while displaying a picture, refer to software procedure described in application note.

#### 10.1.5 IRQ

Table 12. IRQ bit descriptions

| Address | Register   | Bit | Symbol     | Access | Value | Description                                                                                     |

|---------|------------|-----|------------|--------|-------|-------------------------------------------------------------------------------------------------|

| 08h     | IRQ_status | 7   | IRQ_status | R/W    |       |                                                                                                 |

|         |            |     |            | 0      |       | IRQ_clear is set to 1                                                                           |

|         |            |     |            |        | 1     | all calibration sequences selected<br>by MSM_byte_1 and launched by<br>MSM_byte_2 are completed |

| 0Ah     | IRQ_clear  | 7   | IRQ_clear  | R/W    |       |                                                                                                 |

|         |            |     |            |        | 0     |                                                                                                 |

|         |            |     |            |        | 1     | drops the bit IRQ_status                                                                        |

**Remark:** An IRQ information is generated on IRQ pin (30) that reflects the IRQ\_status bit. The polarity of the pin can be selected with IRQ\_Polarity bit at address 0x37h. In Normal mode of operation, the IRQ status is then raised at the end of the calibration sequence selected via MSM\_byte\_1 and MSM\_byte\_2 and at each new channel.

# 10.1.6 AGC and Take Over Points (TOP)

Table 13. AGC and Take Over Points bit descriptions

| Address | Register            | Bit    | Symbol               | Access | Value           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|---------|---------------------|--------|----------------------|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0Ch     | AGC1_byte_1         | 7      | LT_Enable            | R/W    |                 | LT output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|         |                     |        |                      |        | 0               | disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|         |                     |        |                      |        | 1               | enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|         |                     | 6      | AGC1_6_15dB          | R/W    |                 | limits AGC1 gain range from +6 dB to +15 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|         |                     |        |                      |        | 0               | range is from -12 dB to +15 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|         |                     |        |                      |        | 1               | range is from +6 dB to +15 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|         |                     | 3 to 0 | AGC1_TOP[3:0]        | R/W    | see<br>Table 14 | set the TOP of the LNA detection loop (AGC1) in accordance with the reception standard or the system settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 0Fh     | RF_AGC_byte         | 7      | PD_RFAGC_Adapt       | R/W    |                 | RF AGC adapts algorithm power-down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|         | _1                  |        |                      |        | 0               | ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|         |                     |        |                      |        | 1               | OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|         |                     | 6 to 5 | RFAGC_Adapt_TOP[1:0] | R/W    | -               | "AGC3 Adapt" algorithm decreases the AGC3 TOP for low LPF gains. LPF gain is put to low value by AGC5 detector loop in the ACI (N) and (N – 1) reception cases. Decreasing the AGC3 TOP then limits signal C / N (Carrier / Noise) degradation caused by distortion in the RF stages. At opposite, LPF gain is put to high value by AGC5 detector loop in the ACI (N – X) and (N + X) reception cases. Increasing the AGC3 TOP then limits signal C / N degradation caused by noise from RF AGC stage. PD_RFAGC_Adapt allows disabling this algorithm. RFAGC_Adapt_TOP allows choosing the low AGC3 TOP value, the high one being chosen via the AGC3 TOP field. |  |

|         |                     | 3      | RF_Atten_3dB         | R/W    |                 | Adds 3 dB attenuation out of RF AGC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|         |                     |        |                      |        | 0               | OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|         |                     |        |                      |        | 1               | ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|         |                     | 2 to 0 | AGC3_TOP[2:0]        | R/W    | see<br>Table 15 | sets the RF AGC, MIXER and LPF blocks TOP. These bits must be set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 10h     | IR_MIXER_<br>byte_1 | 3 to 0 | AGC4_TOP[3:0]        | R/W    | see<br>Table 16 | according to the desired reception<br>standard and required desired<br>performances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 11h     | AGC5_byte_1         | 3 to 0 | AGC5_TOP[3:0]        | R/W    | see<br>Table 17 | ponomianoco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 12h     | IF_AGC_byte         | 2 to 0 | IF_Level[2:0]        | R/W    | see<br>Table 18 | sets the tuner desired maximum output<br>level. This will enable internal<br>computation of the best linearity/noise<br>compromise based on desired output<br>level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

Table 14. AGC1 TOP values

| AGC1_TOP[3:0] (dec)[1] | AGC1 TOP Down (dBμV) | AGC1 TOP Up (dBμV) |

|------------------------|----------------------|--------------------|

| 0                      | 95                   | 89                 |

| 5                      | 99                   | 93                 |

| 10                     | 100                  | 94                 |

| 15                     | 101                  | 95                 |

<sup>[1]</sup> All others values are forbidden.

Table 15. AGC3 TOP values

| AGC3_TOP[2:0] (dec) | AGC3 TOP (dBμV) |

|---------------------|-----------------|

| 0                   | 94              |

| 1                   | 96              |

| 2                   | 98              |

| 3                   | 100             |

| 4                   | 102             |

| 5                   | 104             |

| 6                   | 106             |

| 7                   | 107             |

Table 16. AGC4 TOP values

| AGC4_TOP[3:0] (dec)[1] | AGC4 TOP Down (dBμV) | AGC4 TOP Up (dBμV) |

|------------------------|----------------------|--------------------|

| 1                      | 105                  | 100                |

| 4                      | 107                  | 102                |

| 6                      | 108                  | 103                |

| 8                      | 109                  | 104                |

| 11                     | 110                  | 105                |

| 14                     | 112                  | 107                |

<sup>[1]</sup> All others values are forbidden.

Table 17. AGC5 TOP values

| AGC5_TOP[3:0] (dec)[1] | AGC5 TOP Down (dBμV) | AGC5 TOP Up (dBμV) |

|------------------------|----------------------|--------------------|

| 1                      | 105                  | 100                |

| 4                      | 107                  | 102                |

| 6                      | 108                  | 103                |

| 8                      | 109                  | 104                |

| 11                     | 110                  | 105                |

| 14                     | 112                  | 107                |

<sup>[1]</sup> All others values are forbidden.

Table 18. Tuner output level

| IF_Level[2:0] (hex) | Output level (V (p-p) differential)[1]) | Minimum gain (dB) | Maximum gain (dB) |

|---------------------|-----------------------------------------|-------------------|-------------------|

| 111                 | 0.5                                     | -12               | 18                |

| 110                 | 0.6                                     | -10.3             | 19.7              |

| 101                 | 0.7                                     | -9                | 21                |

| 100                 | 0.85                                    | -7.5              | 22.5              |

| 011                 | 0.8                                     | -8                | 22                |

| 010                 | 1                                       | -6                | 24                |

| 001                 | 1.25                                    | -4                | 26                |

| 000                 | 2                                       | 0                 | 30                |

<sup>[1]</sup> Output level depends on standard and ADC headroom

#### 10.1.7 IF Filtering

Table 19. IF Filtering bit descriptions

| Table 19.     | IF Filtering bit descriptions |        |                   |        |                      |                                                                            |                                                                 |

|---------------|-------------------------------|--------|-------------------|--------|----------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------|

| Address       | Register                      | Bit    | Symbol            | Access | Value                | Description                                                                |                                                                 |

| 13h IF_byte_1 | IF_byte_1                     | 7 to 6 | IF_HP_Fc[1:0]     | R/W    |                      |                                                                            | off frequency. The high-pass et in accordance with the candard. |

|               |                               |        |                   |        | high-pass frequency: |                                                                            |                                                                 |

|               |                               |        |                   | 00     | 0.4 MHz              |                                                                            |                                                                 |

|               |                               |        |                   |        | 01                   | 0.85 MHz                                                                   |                                                                 |

|               |                               |        |                   |        | 10                   | 1 MHz                                                                      |                                                                 |

|               |                               |        |                   |        | 11                   | 1.5 MHz                                                                    |                                                                 |

|               |                               | 5      | IF_Notch          | R/W    |                      | enables or disables a r<br>adjacent N – 1 sound of<br>frequency depends on | carrier suppression. The notch                                  |

|               |                               |        |                   | 0      | OFF                  |                                                                            |                                                                 |

|               |                               |        |                   |        | 1                    | ON                                                                         |                                                                 |

|               |                               | 4 to 3 | LP_FC_Offset[1:0] | R/W    |                      | enables offset to LPF of further adjacent chann                            | cut-off frequency providing el rejection                        |

|               |                               |        |                   |        | 00                   | 0                                                                          |                                                                 |

|               |                               |        |                   |        | 01                   | <b>-4</b> %                                                                |                                                                 |

|               |                               |        |                   |        | 10                   | <b>-8</b> %                                                                |                                                                 |

|               |                               |        |                   |        | 11                   | forbidden                                                                  |                                                                 |

|               |                               | 2 to 0 | to 0 LP_Fc[2:0]   | R/W    |                      | selects the IF LPF cut-<br>according to desired re                         | off frequency. It must be set eception standard.                |

|               |                               |        |                   |        |                      | LP cut-off frequency:                                                      | IF notch frequency                                              |

|               |                               |        |                   |        | 100                  | 1.7 MHz                                                                    | -                                                               |

|               |                               |        |                   |        | 000                  | 6 MHz                                                                      | 6.5 MHz                                                         |

|               |                               |        |                   |        | 001                  | 7 MHz                                                                      | 7.25 MHz                                                        |

|               |                               |        |                   |        | 010                  | 8 MHz                                                                      | 8.25 MHz                                                        |

|               |                               |        |                   |        | 011                  | forbidden                                                                  | forbidden                                                       |

|               |                               |        |                   |        | 101                  | forbidden                                                                  | forbidden                                                       |

|               |                               |        |                   |        | 11x                  | forbidden                                                                  | forbidden                                                       |

#### 10.1.8 XTOUT

Table 20. XTOUT bit descriptions

|         | 711001 2010                          | Ar of the decomptions |               |                                                              |       |                                                           |  |  |

|---------|--------------------------------------|-----------------------|---------------|--------------------------------------------------------------|-------|-----------------------------------------------------------|--|--|

| Address | Register                             | Bit                   | Symbol        | Access                                                       | Value | Description                                               |  |  |

| 14h     | Reference_byte 1 to 0 XTout[1:0] R/W |                       |               | provides 16 MHz reference signal on the XTOUT1, XTOUT2 pins. |       |                                                           |  |  |

|         |                                      |                       |               |                                                              |       | XTOUT mode:                                               |  |  |

|         |                                      |                       |               |                                                              | 00    | no signal                                                 |  |  |

|         |                                      |                       |               |                                                              | 01    | forbidden                                                 |  |  |

|         |                                      |                       | 10            | forbidden                                                    |       |                                                           |  |  |

|         |                                      | 6                     |               |                                                              | 11    | 16 MHz                                                    |  |  |

|         |                                      |                       | Digital_Clock | R/W                                                          |       | spreads digital clock power to improve tuner EMC behavior |  |  |

|         |                                      |                       |               |                                                              | 0     | OFF                                                       |  |  |

|         |                                      |                       |               |                                                              | 1     | ON                                                        |  |  |

## 10.1.9 IF and RF frequency

#### Table 21. IF and RF frequency bit descriptions

| Address | Register            | Bit    | Symbol         | Access | Value | Description                                                                                                                             |

|---------|---------------------|--------|----------------|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 15h     | IF_Frequency_byte   | 7 to 0 | IF_Freq[7:0]   | R/W    | -     | sets the tuner desired IF frequency by 50 kHz steps. For example, to set the IF frequency to 4 MHz, IF_Freq value must be 4000/50 = 80. |

| 16h     | RF_Frequency_byte_1 | 3 to 0 | RF_Freq[19:16] | R/W    | -     | sets the desired RF frequency expressed                                                                                                 |

| 17h     | RF_Frequency_byte_2 | 7 to 0 | RF_Freq[15:8]  |        |       | in kHz                                                                                                                                  |

| 18h     | RF_Frequency_byte_3 | 7 to 0 | RF_Freq[7:0]   |        |       |                                                                                                                                         |

#### 10.1.10 Calibration controls

Table 22. Calibration control bit descriptions

| Address | Register   | Bit    | Symbol      | Access | Value | Description                                                                |

|---------|------------|--------|-------------|--------|-------|----------------------------------------------------------------------------|

| 19h MSM | MSM_byte_1 | 7      | POWER_Meas  | R/W    | -     | these bits are used to control the                                         |

|         |            | 6      | RF_CAL_AV   | R/W    | -     | calibration and calculation automats embedded in the chip and must be used |

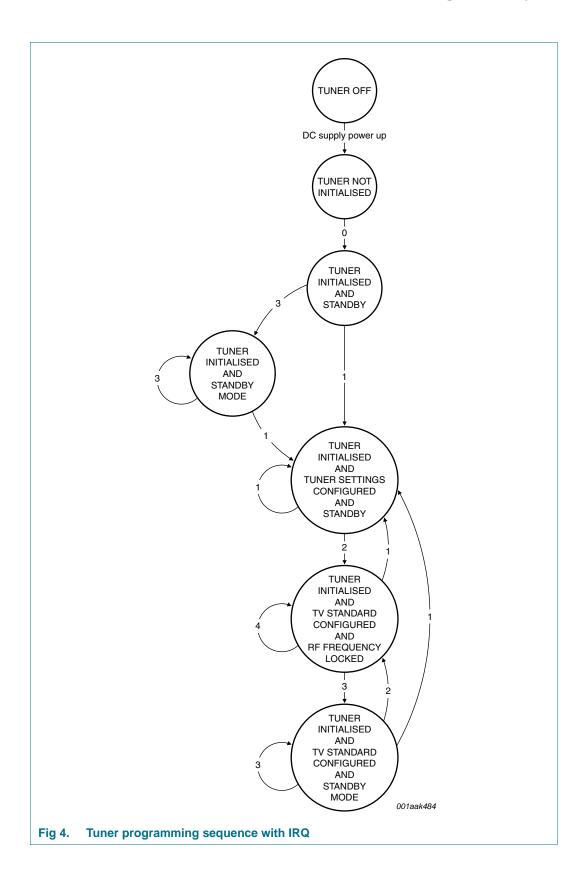

|         |            | 5      | RF_CAL      | R/W    | -     | according to the programming flowchart  Figure 4                           |

|         |            | 4 to 3 | IR_CAL[1:0] | R/W    | -     |                                                                            |

|         |            | 1      | RC_CAL      | R/W    | -     |                                                                            |

|         |            | 0      | Calc_PLL    | R/W    | -     |                                                                            |

| 1Ah     | MSM_byte_2 | 0      | MSM_Launch  | R/W    | -     |                                                                            |

|         |            |        |             |        |       |                                                                            |

#### 10.1.11 IF filtering options

#### Table 23. IR Mixer bit descriptions

| Address             | Register | Bit     | Symbol   | Access | Value                                   | Description                         |

|---------------------|----------|---------|----------|--------|-----------------------------------------|-------------------------------------|

| 23h IR_Mixer_byte_2 | 1        | HI_Pass | R/W      | -      | enables the high-pass frequency filter. |                                     |

|                     |          | 0       | DC_NOTCH | R/W    |                                         | controls a DC notch in the IR mixer |

|                     |          |         |          |        | 0                                       | OFF                                 |

|                     |          |         |          |        | 1                                       | ON                                  |

#### 10.1.12 Gain values

Table 24. AGC bit descriptions

| Address | Register           | Bit    | Symbol              | Access | Value      | Description              |

|---------|--------------------|--------|---------------------|--------|------------|--------------------------|

| 32h     | RF_AGC_Gain_byte_1 | 5 to 4 | RF_FILTER_GAIN[1:0] | R      |            | RF FILTER gain value     |

|         |                    |        |                     |        | 00         | –11 dB                   |

|         |                    |        |                     |        | 01         | −8 dB                    |

|         |                    |        |                     |        | 10         | −5 dB                    |

|         |                    |        |                     |        | 11         | −2 dB                    |

|         |                    | 3 to 0 | LNA_GAIN[3:0]       | R      | <u>[1]</u> | LNA gain value           |

|         |                    |        |                     |        | 0000       | –12 dB                   |

|         |                    |        |                     |        | 0001       | −9 dB                    |

|         |                    |        |                     |        | 0010       | −6 dB                    |

|         |                    |        |                     |        | 0011       | −3 dB                    |

|         |                    |        |                     |        | 0100       | 0 dB                     |

|         |                    |        |                     |        | 0101       | 3 dB                     |

|         |                    |        |                     |        | 0110       | 6 dB                     |

|         |                    |        |                     |        | 0111       | 9 dB                     |

|         |                    |        |                     |        | 1000       | 12 dB                    |

|         |                    |        |                     |        | 1001       | 15 dB                    |

| 33h     | RF_AGC_Gain_byte_2 | 2 to 0 | TOP_Agc3_read[2:0]  | R      |            | gives the TOP_AGC3 value |

|         |                    |        |                     |        | 000        | 94 dBμVrms               |

|         |                    |        |                     |        | 001        | 96 dBμVrms               |

|         |                    |        |                     |        | 010        | 98 dBμVrms               |

|         |                    |        |                     |        | 011        | 100 dBμVrms              |

|         |                    |        |                     |        | 100        | 102 dBμVrms              |

|         |                    |        |                     |        | 101        | 104 dBμVrms              |

|         |                    |        |                     |        | 110        | 106 dBμVrms              |

|         |                    |        |                     |        | 111        | 107 dBμVrms              |

| 34h     | IF_AGC_Gain_byte   | 4 to 3 | LPF_GAIN[1:0]       | R      |            | LPF gain value           |

|         |                    |        |                     |        | 00         | 0 dB                     |

|         |                    |        |                     |        | 01         | 3 dB                     |

|         |                    |        |                     |        | 10         | 6 dB                     |

|         |                    |        |                     |        | 11         | 9 dB                     |

|         |                    | 2 to 0 | IR_MIXER[2:0]       | R      | <u>[1]</u> | IR MIXER gain value      |

|         |                    |        |                     |        | 000        | 2 dB                     |

|         |                    |        |                     |        | 001        | 5 dB                     |

|         |                    |        |                     |        | 010        | 8 dB                     |

|         |                    |        |                     |        | 011        | 11 dB                    |

|         |                    |        |                     |        | 100        | 14 dB                    |

<sup>[1]</sup> Other values are forbidden.

18 of 49

#### **10.1.13** IRQ polarity

Table 25. IRQ polarity bit descriptions

| Address | Register    | Bit | Symbol       | Access | Value | Description                             |

|---------|-------------|-----|--------------|--------|-------|-----------------------------------------|

| 37h     | Misc_byte_1 | 0   | IRQ_Polarity | R/W    |       | selects the IRQ pin polarity            |

|         |             |     |              |        |       | IRQ pin output voltage when IRQ raised: |

|         |             |     |              |        | 0     | $V_{CC}$                                |

|         |             |     |              |        | 1     | 0                                       |

#### 10.1.14 rfcal\_log

These bytes are providing the outcome of the RF filter calibration. It can be used as an indicator regarding RF filter robustness implementation on PCB.

Table 26. rfcal\_log bit descriptions

|         | •           |        |        |        |       |                                                                               |

|---------|-------------|--------|--------|--------|-------|-------------------------------------------------------------------------------|

| Address | Register    | Bit    | Symbol | Access | Value | Description                                                                   |

| 38h     | rfcal_log1  | 7 to 0 |        | R      | -     | provides RF filter calibration results                                        |

| 39h     | rfcal_log2  | 7 to 0 |        | R      | -     | according to the following convention:                                        |

| 3Ah     | rfcal_log3  | 7 to 0 |        | R      | -     | <ul> <li>Bit [7] is set to 1 in case of calibration</li> <li>error</li> </ul> |

| 3Bh     | rfcal_log4  | 7 to 0 |        | R      | -     | Bit [6:0] is a signed number                                                  |

| 3Ch     | rfcal_log5  | 7 to 0 |        | R      | -     | indicating the number of switch                                               |

| 3Dh     | rfcal_log6  | 7 to 0 |        | R      | -     | capacitors                                                                    |

| 3Eh     | rfcal_log7  | 7 to 0 |        | R      | -     |                                                                               |

| 3Fh     | rfcal_log8  | 7 to 0 |        | R      | -     |                                                                               |

| 40h     | rfcal_log9  | 7 to 0 |        | R      | -     |                                                                               |

| 41h     | rfcal_log10 | 7 to 0 |        | R      | -     |                                                                               |

| 42h     | rfcal_log11 | 7 to 0 |        | R      | -     |                                                                               |

| 43h     | rfcal_log12 | 7 to 0 |        | R      | -     |                                                                               |

#### 10.1.15 Forbidden

Table 27. Forbidden bit descriptions

| Address    | Register | Bit    | Symbol | Access | Value | Description                                                          |

|------------|----------|--------|--------|--------|-------|----------------------------------------------------------------------|

| 50h to 67h | -        | 7 to 0 | -      | -      | -     | these bytes are forbidden and must not                               |

| FEh        | -        | 7 to 0 | -      | -      | -     | be written nor read                                                  |

| FFh        | -        | 7 to 0 | -      | -      | -     | Any modification of these bytes can lead to performance degradation. |

#### 10.2 Tuner programming sequences with fixed delays or using IRQ

#### 10.2.1 IRQ

In the following drawing,

- Transition 0 (initialisation):

- Power\_state\_byte\_2: wakes the tuner up

- MSN\_byte\_1 (3Bh)

- MSN\_byte\_2 (01h): launches tuner calibration

- IRQ is generated once operations are completed

**TDA18219HN**

- Reference\_byte (4Xh)

- Power\_byte\_2 (0Eh): sets clock mode

- Power\_state\_byte\_2: puts the tuner in Standby mode

- Transition 1 (standard selection):

- IF\_Frequency\_byte

- IF\_AGC\_byte

- IF\_byte\_1

- IR\_MIXER\_byte\_2

- AGC1\_byte\_1

- AGC2\_byte\_1

- AGCK\_byte\_1

- RF\_AGC\_byte\_1

- IR\_MIXER\_byte\_1

- AGC5\_byte\_1

- PSM\_byte\_1

- Configures the settings that depends on the chosen received TV standard (standard and demodulator dependant)