# XRT83SL28

### 8-CHANNEL E1 SHORT-HAUL LINE INTERFACE UNIT

APRIL 2005 REV. 1.0.0

### **GENERAL DESCRIPTION**

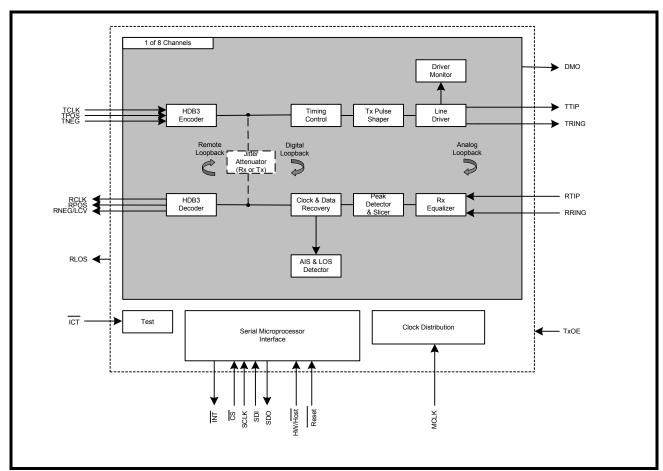

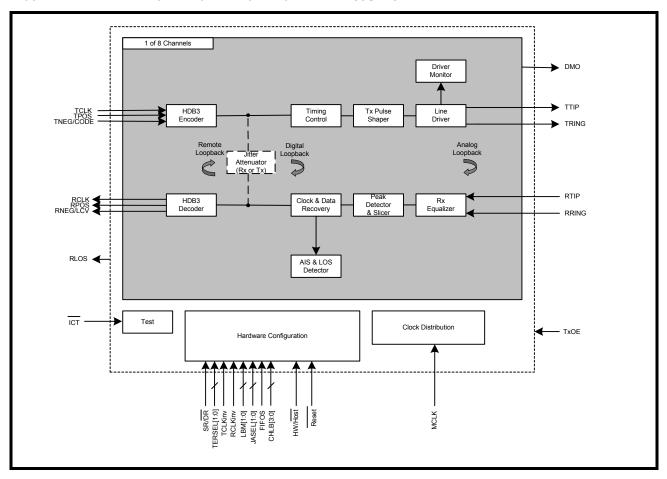

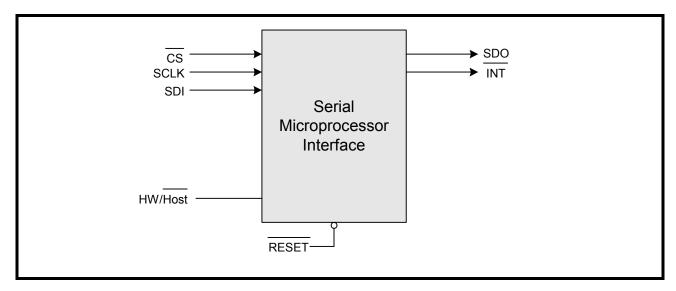

The XRT83SL28 is a fully integrated 8-channel E1 short-haul LIU which optimizes system cost and performance by offering key design features. The XRT83SL28 operates from a single 3.3V power supply. The LIU features are programmed through a standard serial microprocessor interface or hardware control. EXAR's LIU has patented high impedance circuits that allow the transmitter outputs and receiver inputs to be high impedance when experiencing a power failure or when the LIU is powered off. Key design features within the LIU optimize 1:1 or 1+1 redundancy and non-intrusive monitoring applications to ensure reliability without using relays.

Additional features include TAOS for transmit and receive, RLOS, LCV, AIS, DMO, and diagnostic loopback modes.

#### **APPLICATIONS**

- ISDN Primary Rate Interface

- CSU/DSU E1 Interface

- E1 LAN/WAN Routers

- Public Switching Systems and PBX Interfaces

- E1 Multiplexer and Channel Banks

- Integrated Multi-Service Access Platforms (IMAPs)

- Integrated Access Devices (IADs)

- Inverse Multiplexing for ATM (IMA) Wireless Base Stations

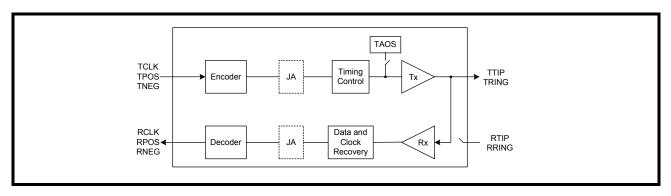

FIGURE 1. HOST MODE BLOCK DIAGRAM OF THE XRT83SL28

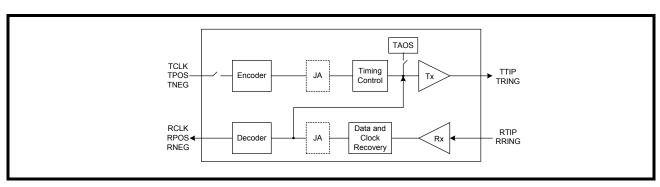

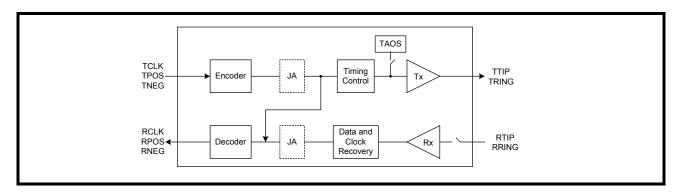

FIGURE 2. HARDWARE MODE BLOCK DIAGRAM OF THE XRT83SL28

#### **FEATURES**

- Fully integrated 8-Channel short haul transceivers for E1 (2.048MHz) applications.

- Internal Impedance matching on both receive and transmit for  $75\Omega$  (E1) or  $120\Omega$  (E1) applications.

- Tri-State on a per channel basis for the transmit selection.

- On-Chip transmit short-circuit protection and limiting protects line drivers from damage on a per channel basis.

- Independent Crystal-Less digital jitter attenuators (JA) with 32-Bit or 64-Bit FIFO for the receive or transmit paths

- Driver failure monitor output (DMO) alerts of possible system or external component problems.

- Transmit outputs and receive inputs may be "High" impedance for protection or redundancy applications on a per channel basis.

- Support for automatic protection switching.

- 1:1 and 1+1 protection without relays.

- RLOS/AIS according to ITU-T G.775 or ETSI-300-233.

- On-Chip HDB3 encoder/decoder for each channel.

- On-Chip digital clock recovery circuit for high input jitter tolerance.

- Line code error and bipolar violation detection.

- Transmit all ones (TAOS) for the Transmit and Receive Outputs.

- Supports local analog, remote, and digital loopback modes.

- Supports gapped clocks for mapper/multiplexer applications.

- Low Power dissipation

- Single 3.3V supply operation (3V to 5V I/O tolerant).

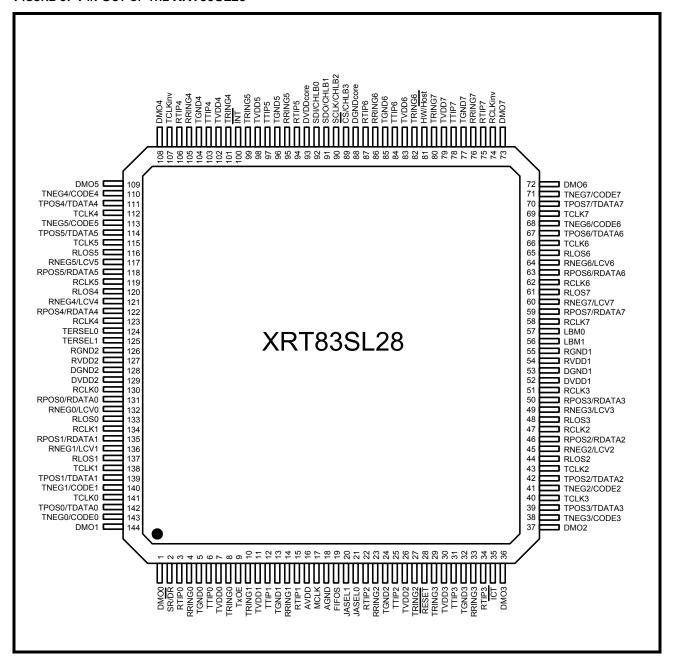

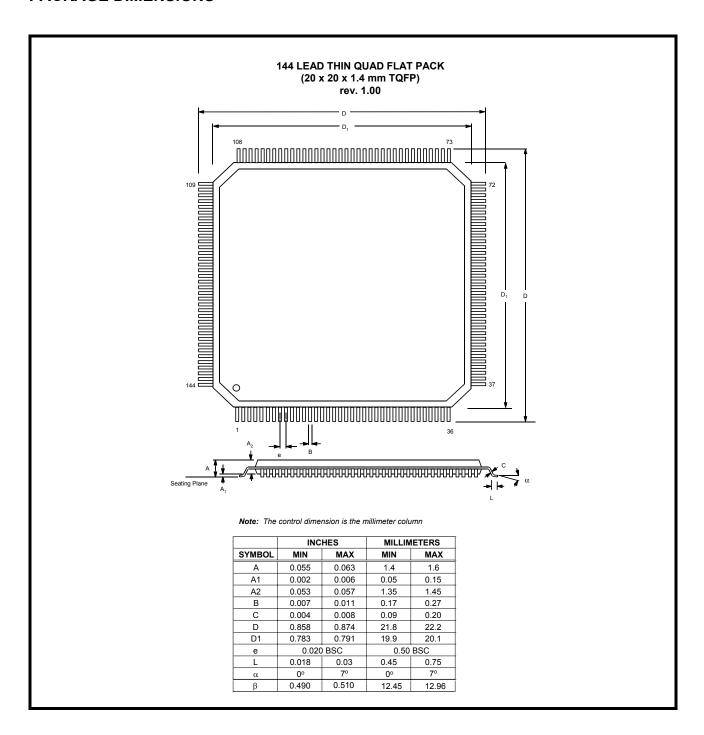

- 144-Pin TQFP package

- -40°C to +85°C Temperature Range

#### PRODUCT ORDERING INFORMATION

| PRODUCT NUMBER | PACKAGE TYPE  | OPERATING TEMPERATURE RANGE |  |  |  |

|----------------|---------------|-----------------------------|--|--|--|

| XRT83SL28IV    | 144 Lead TQFP | -40°C to +85°C              |  |  |  |

FIGURE 3. PIN OUT OF THE XRT83SL28

## **TABLE OF CONTENTS**

| GENERAL DESCRIPTION                                                                  | 1  |

|--------------------------------------------------------------------------------------|----|

| APPLICATIONS                                                                         | 1  |

| FIGURE 1. HOST MODE BLOCK DIAGRAM OF THE XRT83SL28                                   |    |

| FIGURE 2. HARDWARE MODE BLOCK DIAGRAM OF THE XRT83SL28                               |    |

| FEATURES                                                                             |    |

| PRODUCT ORDERING INFORMATION                                                         |    |

| Figure 3. Pin Out of the XRT83SL28                                                   |    |

| TABLE OF CONTENTS                                                                    |    |

| PIN DESCRIPTIONS                                                                     | 5  |

| SERIAL MICROPROCESSOR INTERFACE                                                      |    |

| RECEIVER SECTION                                                                     |    |

| TRANSMITTER SECTION                                                                  |    |

| CONTROL FUNCTION                                                                     |    |

| POWER AND GROUND (HOST AND HARDWARE MODES)                                           |    |

|                                                                                      |    |

| HARDWARE MODE INTERFACE                                                              |    |

| 1.0 RECEIVE PATH LINE INTERFACE                                                      |    |

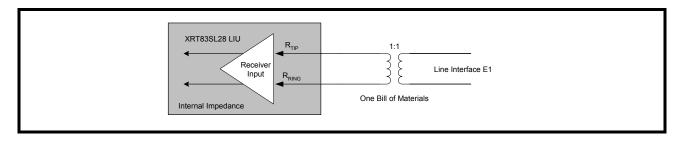

| FIGURE 4. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE PATH LINE TERMINATION (RTIP/RRING) |    |

| 1.1 INTERNAL TERMINATION                                                             |    |

| TABLE 1: SELECTING THE INTERNAL IMPEDANCE                                            |    |

| 1.2 PEAK DETECTOR/DATA SLICER                                                        |    |

| 1.3 CLOCK AND DATA RECOVERY                                                          |    |

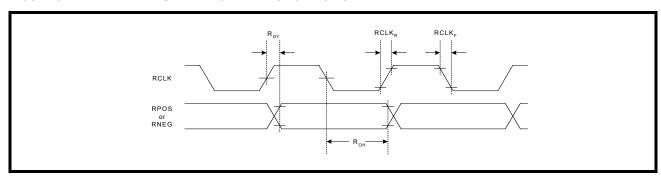

| Figure 6. Receive Data Updated on the Rising Edge of RCLK                            |    |

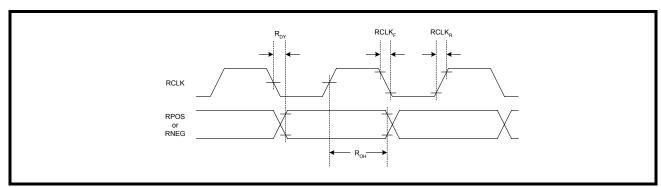

| FIGURE 7. RECEIVE DATA UPDATED ON THE FALLING EDGE OF RCLK                           |    |

| TABLE 2: TIMING SPECIFICATIONS FOR RCLK/RPOS/RNEG                                    |    |

| 1.4 RECEIVE SENSITIVITY                                                              |    |

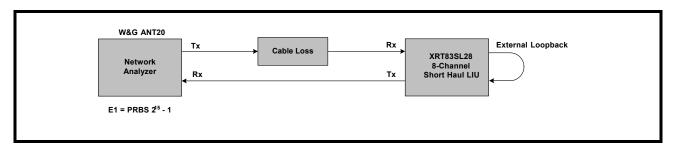

| FIGURE 8. TEST CONFIGURATION FOR MEASURING RECEIVE SENSITIVITY                       |    |

| 1.5 GENERAL ALARM DETECTION AND INTERRUPT GENERATION                                 |    |

| 1.5.1 RLOS (RECEIVER LOSS OF SIGNAL)                                                 |    |

| 1.5.2 AIS (ALARM INDICATION SIGNAL)                                                  |    |

| 1.6 RECEIVE JITTER ATTENUATOR                                                        |    |

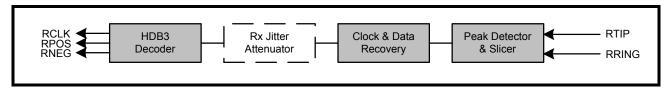

| 1.7 HDB3 DECODER                                                                     |    |

| 1.8 ARAOS (AUTOMATIC RECEIVE ALL ONES)                                               |    |

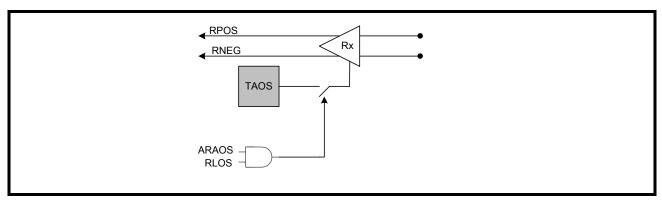

| Figure 9. Simplified Block Diagram of the ARAOS Function                             | 18 |

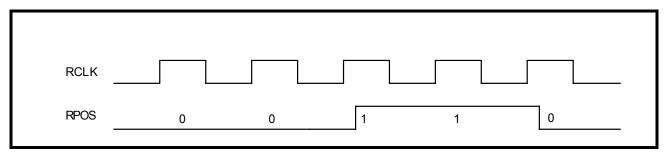

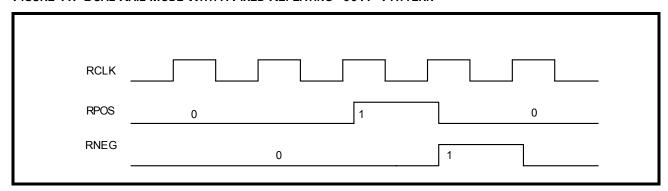

| 1.9 RPOS/RNEG/RCLK                                                                   | 18 |

| Figure 10. Single Rail Mode With a Fixed Repeating "0011" Pattern                    |    |

| Figure 11. Dual Rail Mode With a Fixed Repeating "0011" Pattern                      |    |

| 2.0 TRANSMIT PATH LINE INTERFACE                                                     |    |

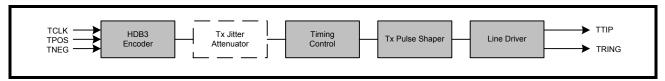

| FIGURE 12. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT PATH                             |    |

| 2.1 TCLK/TPOS/TNEG DIGITAL INPUTS                                                    |    |

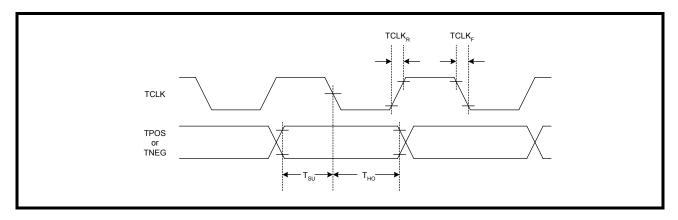

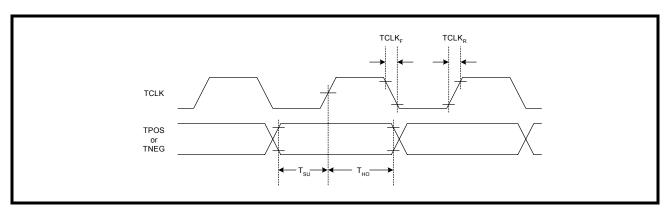

| FIGURE 13. TRANSMIT DATA SAMPLED ON FALLING EDGE OF TCLK                             |    |

| FIGURE 14. I RANSMIT DATA SAMPLED ON RISING EDGE OF TCLK                             |    |

| 2.2 HDB3 ENCODER                                                                     |    |

| TABLE 4: EXAMPLES OF HDB3 ENCODING                                                   |    |

| 2.3 TRANSMIT JITTER ATTENUATOR                                                       |    |

| TABLE 5: MAXIMUM GAP WIDTH FOR MULTIPLEXER/MAPPER APPLICATIONS                       |    |

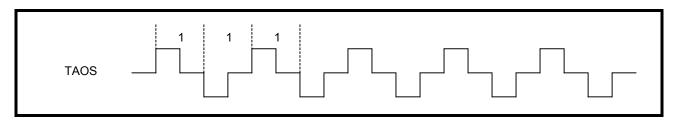

| 2.4 TAOS (TRANSMIT ALL ONES)                                                         | 22 |

| FIGURE 15. TAOS (TRANSMIT ALL ONES)ATAOS (AUTOMATIC TRANSMIT ALL ONES)               |    |

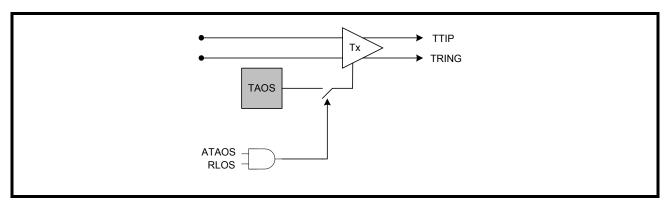

| 2.5 ATAOS (AUTOMATIC TRANSMIT ALL ONES)                                              |    |

| FIGURE 16. SIMPLIFIED BLOCK DIAGRAM OF THE ATAOS FUNCTION                            |    |

| 2.6 TRANSMITTER POWER DOWN IN HARDWARE MODE                                          |    |

| 2.7 DMO (DRIVER MONITOR OUTPUT)                                                      |    |

| 2.8 LINE TERMINATION (TTIP/TRING)                                                    |    |

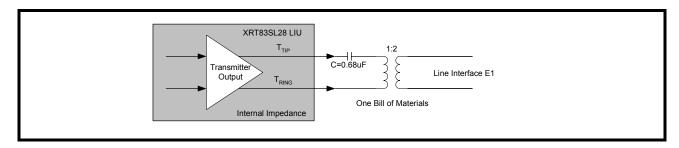

| FIGURE 17. TYPICAL CONNECTION DIAGRAM USING INTERNAL TERMINATION                     |    |

| 3.0 E1 APPLICATIONS                                                                  |    |

| 3.1 LOOPBACK DIAGNOSTICS                                                             | 24 |

| REV | , | 1 | O. |

|-----|---|---|----|

|     |   |   |    |

| FIGURE 18. SIMPLIFIED BLOCK DIAGRAM OF LOCAL ANALOG LOOPBACK.   24     3.12 REMOTE LOOPBACK.   24     FIGURE 19. SIMPLIFIED BLOCK DIAGRAM OF REMOTE LOOPBACK.   25     FIGURE 20. SIMPLIFIED BLOCK DIAGRAM OF DIGITAL LOOPBACK.   25     S. LINE CARD REDUNDANCY   26     3.2.1 LINE OARD REDUNDANCY   26     3.2.1 LI AND 1-11 REDUNDANCY WITHOUT RELAYS.   26     3.2.1 LI AND 1-11 REDUNDANCY WITHOUT RELAYS.   26     3.2.2 TRANSMIT INTERFACE WITH 1:1 AND 1-11 REDUNDANCY   26     3.2.3 RECEIVE INTERFACE WITH 1:1 AND 1-11 REDUNDANCY   27     FIGURE 22. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR 1:1 AND 1-11 REDUNDANCY   27     3.2.4 N+1 REDUNDANCY USING EXTERNAL RELAYS   27     3.2.5 TRANSMIT INTERFACE WITH 1-11 REDUNDANCY   27     3.2.5 TRANSMIT INTERFACE WITH N-11 REDUNDANCY   27     3.2.5 TRANSMIT INTERFACE WITH N-11 REDUNDANCY   28     3.2.6 RECEIVE INTERFACE WITH N-11 REDUNDANCY   28     3.2.6 RECEIVE INTERFACE WITH N-11 REDUNDANCY   29     FIGURE 23. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N-1 REDUNDANCY   29     FIGURE 24. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR N-1 REDUNDANCY   29     3.3 POWER FAILURE PROTECTION   30     3.4 OVERVOLTAGE AND OVERCURRENT PROTECTION   30     3.5 NON-INTRUSIVE MONITORING   30     FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION   30     4.0 SERIAL MICROPROCESSOR INTERFACE BLOCK   31     FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE SERIAL MICROPROCESSOR INTERFACE   31     A SERIAL TIMING INFORMATION   32     4.1 SERIAL TIMING INFORMATION   32     4.2 (1-5) (ISCLK2 - SCLK7)   32     4.3 8-BIT SERIAL DATA OUTPUT DESCRIPTION   36      |     |       | 3.1.1  | LOCAL ANALOG LOOPBACK                                | 24 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------|------------------------------------------------------|----|

| FIGURE 19. SIMPLIFIED BLOCK DIAGRAM OF REMOTE LOOPBACK.   24 3.13. DIGITAL LOOPBACK.   25 FIGURE 20. SIMPLIFIED BLOCK DIAGRAM OF DIGITAL LOOPBACK.   25 3.2 LINE CARD REDUNDANCY   26 3.2.1. 11: AND 1+1 REDUNDANCY WITHOUT RELAYS   26 3.2.1. 11: AND 1+1 REDUNDANCY WITHOUT RELAYS   26 3.2.2. TRANSMIT INTERFACE WITH 1:1 AND 1+1 REDUNDANCY   26 FIGURE 21. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR 1:1 AND 1+1 REDUNDANCY   27 FIGURE 22. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR 1:1 AND 1+1 REDUNDANCY   27 3.2.4 N+1 REDUNDANCY USING EXTERNAL RELAYS   27 3.2.5 TRANSMIT INTERFACE WITH 1+1 AND 1+1 REDUNDANCY   28 FIGURE 23. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY   28 3.2.6 RECEIVE INTERFACE WITH N+1 REDUNDANCY   29 7. FIGURE 23. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 24. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE SECRET INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE SECRET INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE SECRET INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE SECRET INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE SECRET INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE SECRET INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE SECRET INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE SECRET INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE SECRET INTERFACE FOR N+1 REDUNDANCY   29 7. FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE SE   |     | Fig   | GURE 1 | 8. SIMPLIFIED BLOCK DIAGRAM OF LOCAL ANALOG LOOPBACK | 24 |

| 3.13 DIGITAL LOOPBACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |       |        |                                                      |    |

| FIGURE 20. SIMPLIFIED BLOCK DIAGRAM OF DIGITAL LOOPBACK.   26   3.2.1 LINA CARD REDUNDANCY   26   3.2.1 1:1 AND 1+1 REDUNDANCY WITHOUT RELAYS.   26   3.2.2 TRANSMIT INTERFACE WITH 1:1 AND 1+1 REDUNDANCY.   26   FIGURE 21. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR 1:1 AND 1+1 REDUNDANCY.   26   3.2.3 RECEIVE INTERFACE WITH 1:1 AND 1+1 REDUNDANCY.   27   FIGURE 22. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR 1:1 AND 1+1 REDUNDANCY.   27   3.2.4 N+1 REDUNDANCY USING EXTERNAL RELAYS.   27   3.2.5 TRANSMIT INTERFACE WITH N+1 REDUNDANCY.   28   FIGURE 23. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N-1 REDUNDANCY.   28   3.2.6 RECEIVE INTERFACE WITH N+1 REDUNDANCY.   29   FIGURE 24. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY.   29   3.3 POWER FAILURE PROTECTION.   30   3.4 OVERVOLTAGE AND OVERCURRENT PROTECTION.   30   3.5 NON-INTRUSIVE MONITORING.   30   3.5 NON-INTRUSIVE MONITORING.   30   4.0 SERIAL MICROPROCESSOR INTERFACE BLOCK.   314   FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE SERIAL MICROPROCESSOR INTERFACE.   31   4.1 SERIAL MICROPROCESSOR INTERFACE BLOCK.   31   FIGURE 26. SIMPLIFIED BLOCK DIAGRAM OF THE SERIAL MICROPROCESSOR INTERFACE.   31   4.2 16-BIT SERIAL DATA INPUT DESCRIPTION.   32   4.2.1 AW (SCLK1).   32   4.2.2 A[5:0] (SCLK2 - SCLKT).   32   4.2.3 X (DUMMY BIT SCLK8).   32   4.2.4 D[7:0] (SCLK9 - SCLK16).   32   4.2.4 D[7:0] (SCLK9 - SCLK16).   32   4.2.4 D[7:0] (SCLK9 - SCLK16).   36   TABLE 17. MICROPROCESSOR REGISTER DESCRIPTION.   36   TABLE 17. MICROPROCESSOR REGISTER BIT D   |     |       |        |                                                      |    |

| 3.2 LINE CARD REDUNDANCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |       |        |                                                      |    |

| 3.2.1 1:1 AND 1+1 REDINDANCY WITHOUT RELAYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |       |        |                                                      |    |

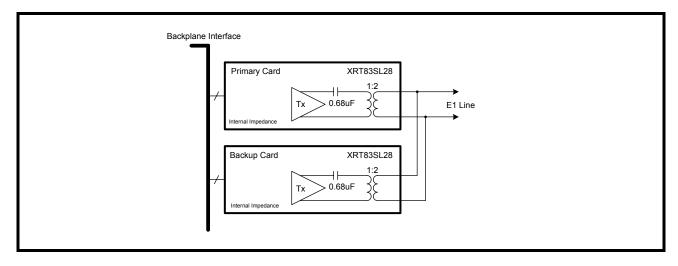

| 3.2.2 TRANSMIT INTERFACE WITH 1:1 AND 1+1 REDUNDANCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |       |        |                                                      |    |

| FIGURE 21. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR 1:1 AND 1+1 REDUNDANCY 27   FIGURE 22. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR 1:1 AND 1+1 REDUNDANCY 27   3.2.4 N+1 REDUNDANCY USING EXTERNAL RELAYS 27   3.2.5 TRANSMIT INTERFACE WITH N+1 REDUNDANCY 28   FIGURE 23. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N:1 AND 1+1 REDUNDANCY 28   FIGURE 24. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY 29   FIGURE 24. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR N+1 REDUNDANCY 29   3.3 POWER FAILLURE PROTECTION 30   3.4 OVERVOLTAGE AND OVERCURRENT PROTECTION 30   3.5 NON-INTRUSIVE MONITORING 30   FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION. 30   4.0 SERIAL MICROPROCESSOR INTERFACE BLOCK 31   FIGURE 26. SIMPLIFIED BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION. 30   4.1 SERIAL TIMING INFORMATION 31   4.2 IGENIAL TIMING INFORMATION 31   FIGURE 27. TIMING DIAGRAM FOR THE SERIAL MICROPROCESSOR INTERFACE 31   4.2 IGENIAL TIMING INFORMATION 32   4.2.1 (F.0) (SCLK1) 32   4.2.2 (JE.0) (SCLK2 - SCLK7) 32   4.2.3 X (DUMMY BIT SCLK8) 32   4.2.3 X (DUMMY BIT SCLK8) 32   4.2.4 (JE.0) (SCLK9 - SCLK16) 32   4.2.3 X (DUMMY BIT SCLK8) 32   4.2.4 (JE.0) (SCLK9 - SCLK16) 32   4.3 BBIT SERIAL DATA OUTPUT DESCRIPTION 32   4.3 BIT SERIAL DATA OUTPUT DESCRIPTION 36   TABLE 6: MICROPROCESSOR REGISTER BIT DESCRIPTION 36   TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION 36   TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION 36   TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION 36   TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION 36   TABLE 14: ABSOLUTE MAXIMUM RATINGS 41   TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS 41   TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS 41   TABLE 16: ACCOUNTER AND OUTPUT ELECTRICAL CHARACTERISTICS 41   TABLE 16: ACCOUNTER AND OUTPUT ELECTRICAL CHARACTERISTICS 42   CORDER OF MATTER AND OUTPUT ELECTRICAL CHARACTERISTICS 42   CORDER OF MATTER AND OUTPUT ELECT   |     |       |        |                                                      |    |

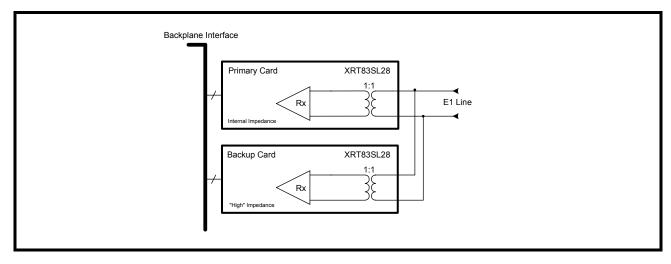

| 3.2.3 RECEIVE INTERFACE WITH 1:1 AND 1+1 REDUNDANCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |       |        |                                                      |    |

| FIGURE 22. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR 1:1 AND 1+1 REDUNDANCY   27   3.2.4 N+1 REDUNDANCY USING EXTERNAL RELAYS   27   3.2.5 TRANSMIT INTERFACE WITH N+1 REDUNDANCY   28   FIGURE 23. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY   28   3.2.6 RECEIVE INTERFACE WITH N+1 REDUNDANCY   29   FIGURE 24. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY   29   3.3 POWER FAILURE PROTECTION   30   3.4 OVERVOLTAGE AND OVERCURRENT PROTECTION   30   3.5 NON-INTRUSIVE MONITORING   30   3.5 NON-INTRUSIVE MONITORING   30   3.5 NON-INTRUSIVE MONITORING   30   3.5 NON-INTRUSIVE MONITORING   30   3.6 NON-INTRUSIVE MONITORING   30   4.0 SERIAL MICROPROCESSOR INTERFACE BLOCK   31   FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE SERIAL MICROPROCESSOR INTERFACE   31   4.1 SERIAL TIMING INFORMATION   31   4.2 SERIAL TIMING INFORMATION   31   4.2 I6-BIT SERIAL DATA INPUT DESCRIPTION   32   4.2.1 (F.0) (SCLK2 - SCLKT)   32   4.2.2 A[5:0) (SCLK2 - SCLKT)   32   4.2.3 X (DUMMY BIT SCLK8)   32   4.2.3 X (DUMMY BIT SCLK8)   32   4.2.4 D[7:0) (SCLK2 - SCLK16)   32   4.2.4 D[7:0) (SCLK2 - SCLK16)   32   4.2.4 D[7:0) (SCLK3 - SCLK16)   32   4.2.5 MICROPROCESSOR REGISTER DISCRIPTION   36   7 ABLE 6: MICROPROCESSOR REGISTER DISCRIPTION   36   7 ABLE 6: MICROPROCESSOR REGISTER DISCRIPTION   36   7 ABLE 19: MICROPROCESSOR REGISTER BIT DESCRIPTION   37 ABLE 19: MICROPROCESSOR REGISTER BIT DESCRIPTION   37 ABLE 19: MICROPROCESSOR REGISTER BIT DESCRIPTION   37 ABLE 19: MICROPROCESSOR    |     |       |        |                                                      |    |

| 3.2.4 N+1 REDUNDANCY USING EXTERNAL RELAYS 3.2.5 TRANSMIT INTERFACE WITH N+1 REDUNDANCY 28 FIGURE 23. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY 29 FIGURE 24. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY 29 3.3 POWER FAILURE PROTECTION 30 3.4 OVERVOLTAGE AND OVERCURRENT PROTECTION 30 3.5 NON-INTRUSIVE MONITORING 30 5. SIMPLIFIED BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION. 30 4.0 SERIAL MICROPROCESSOR INTERFACE BLOCK 31 FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION. 30 FIGURE 26. SIMPLIFIED BLOCK DIAGRAM OF THE SERIAL MICROPROCESSOR INTERFACE 31 FIGURE 27. TIMING INFORMATION 31 FIGURE 27. TIMING DIAGRAM FOR THE SERIAL MICROPROCESSOR INTERFACE 31 4.2 16-BIT SERIAL DATA INPUT DESCRIPTION 32 4.2.1 RW (SCLK1) 32 4.2.2 A[5:0] (SCLK2 - SCLK7) 32 4.2.3 X (DUMNY BIT SCLK8) 32 4.2.4 D[7:0] (SCLK2 - SCLK7) 32 4.2.4 B-BIT SERIAL DATA OUTPUT DESCRIPTION 32 TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION 32 7ABLE 6: MICROPROCESSOR REGISTER DESCRIPTION 35 TABLE 7: MICROPROCESSOR REGISTER DESCRIPTION 36 TABLE 10: MICROPROCESSOR REGISTER DESCRIPTION 36 TABLE 10: MICROPROCESSOR REGISTER DESCRIPTION 36 TABLE 10: MICROPROCESSOR REGISTER DESCRIPTION 36 TABLE 11: MICROPROCESSOR REGISTER DID SESCRIPTION 36 TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION 36 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION 37 TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION 38 TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION 39 ELECTRICAL CHARACTERISTICS 41 TABLE 14: ABSOLUTE MAXIMUM RATINGS 41 TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS 41 TABLE 16: AC ELECTRICAL CHARACTERISTICS 41 TABLE 17: POWER CONSUMPTION. 41 TABLE 18: ERCENVER ELECTRICAL CHARACTERISTICS 41 TABLE 19: ETTRANSMITTER ELECTRICAL CHARACTERISTICS 42 TABLE 19: ETTRANSMITTER ELECTRICAL CHARACTERISTICS 43 ORDERING INFORMATION                                                                                                                                                      |     |       |        |                                                      |    |

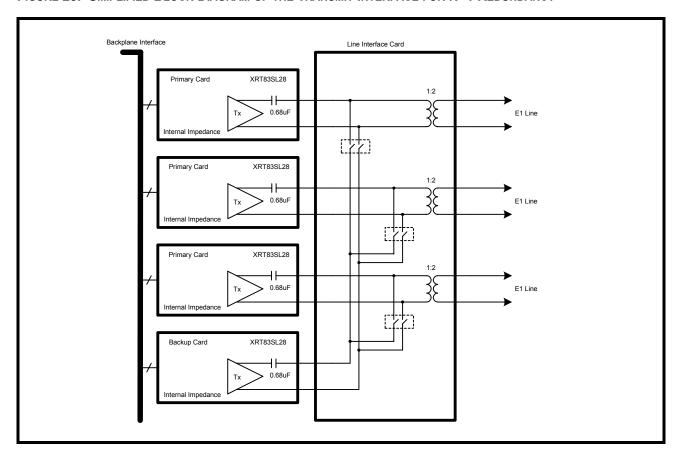

| 3.2.5 TRANSMIT INTERFACE WITH N+1 REDUNDANCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |       |        |                                                      |    |

| FIGURE 23 SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |       |        |                                                      |    |

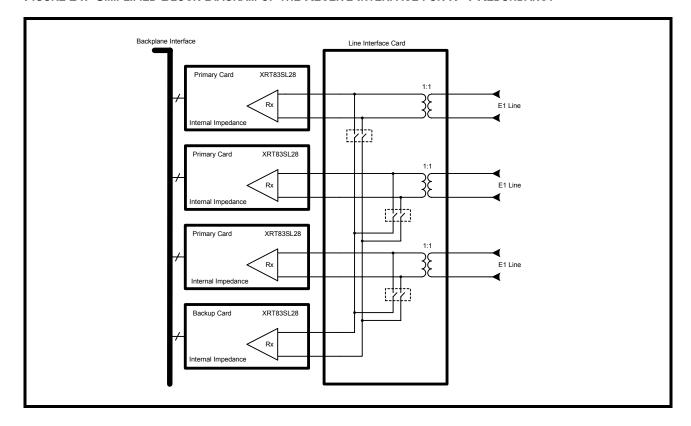

| 3.2.6 RECEIVE INTERFACE WITH N+1 REDUNDANCY  FIGURE 24. SIMPLIPIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR N+1 REDUNDANCY  3.3 POWER FAILURE PROTECTION  3.0  3.4 OVERVOLTAGE AND OVERCURRENT PROTECTION  3.5. NON-INTRUSIVE MONITORING  3.6. FIGURE 25. SIMPLIPIED BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION.  3.7 FIGURE 25. SIMPLIPIED BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION.  3.8 FIGURE 25. SIMPLIPIED BLOCK DIAGRAM OF THE SERIAL MICROPROCESSOR INTERFACE  3.1 FIGURE 26. SIMPLIPIED BLOCK DIAGRAM OF THE SERIAL MICROPROCESSOR INTERFACE  3.1 4.1 SERIAL TIMING INFORMATION  3.1 FIGURE 27. TIMING DIAGRAM FOR THE SERIAL MICROPROCESSOR INTERFACE  3.1 4.2 16-BIT SERIAL DATA INPUT DESCRIPTION  3.2 4.2.1 RW (SCLK1).  3.2 4.2.1 RW (SCLK1).  3.2 4.2.2 A[5:0] (SCLK2 - SCLK7).  3.2 4.2.3 X (DUMMY BIT SCLK8).  3.2 4.2.4 D[7:0] (SCLK9 - SCLK16).  3.3 ABJET SERIAL DATA OUTPUT DESCRIPTION  3.2 TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION  3.3 TABLE 7: MICROPROCESSOR REGISTER DESCRIPTION  3.4 A.3 8-BIT SERIAL DATA OUTPUT DESCRIPTION  3.5 TABLE 8: MICROPROCESSOR REGISTER DID DESCRIPTION  3.6 TABLE 9: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.7 ABJET 1: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.8 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.9 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.0 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.1 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.2 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.3 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.4 TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.5 TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.6 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.7 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.8 TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.9 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.0 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.0 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.0 TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION  3.0 T |     |       |        |                                                      |    |

| FIGURE 24. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR N+1 REDUNDANCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |       |        |                                                      |    |

| 3.3 POWER FAILURE PROTECTION 30 3.4 OVERVOLTAGE AND OVERCURRENT PROTECTION 30 3.5 NON-INTRUSIVE MONITORING 30 3.5 NON-INTRUSIVE MONITORING 30 4.0 SERIAL MICROPROCESSOR INTERFACE BLOCK 31 Figure 25. Simplified BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION. 30 4.0 SERIAL MICROPROCESSOR INTERFACE BLOCK 31 Figure 26. Simplified BLOCK DIAGRAM OF THE SERIAL MICROPROCESSOR INTERFACE 31 4.1 SERIAL TIMING INFORMATION 31 1. Figure 27. TIMING DIAGRAM FOR THE SERIAL MICROPROCESSOR INTERFACE 31 4.2 16-BIT SERIAL DATA INPUT DESCRIPTION 32 4.2.1 RW (SCLKI) 32 4.2.2 A[5:0] (SCLK2 - SCLK7) 32 4.2.3 X (DUMMY BIT SCLK8) 32 4.2.4 D[7:0] (SCLK2 - SCLK6) 32 4.2.3 X (DUMMY BIT SCLK8) 32 4.3 8-BIT SERIAL DATA OUTPUT DESCRIPTION 32 TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION 32 TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION 35 TABLE 6: MICROPROCESSOR REGISTER OXOOH BIT DESCRIPTION 36 TABLE 9: MICROPROCESSOR REGISTER OXOOH BIT DESCRIPTION 36 TABLE 9: MICROPROCESSOR REGISTER BIT DESCRIPTION 36 TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION 36 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION 36 TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION 36 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION 36 TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION 36 TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION 36 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION 36 TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION 36 TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION 36 TABLE 14: ABSOLUTE MAXIMUM RATINGS 41 TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS 41 TABLE 16: AC ELECTRICAL CHARACTERISTICS 41 TABLE 17: POWER CONSUMPTION 41 TABLE 18: RECEIVER ELECTRICAL CHARACTERISTICS 42 TABLE 19: E1 TRANSMITTER ELECTRICAL CHARACTERISTICS 42                     |     |       |        |                                                      |    |

| 3.4 OVERVOLTAGE AND OVERCURRENT PROTECTION 3.5 NON-INTRUSIVE MONITORING 30 3.5 NON-INTRUSIVE MONITORING 30 4.0 SERIAL MICROPROCESSOR INTERFACE BLOCK 31 FIGURE 26. SIMPLIFIED BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION. 31 4.1 SERIAL TIMING INFORMATION 31 FIGURE 27. TIMING DIAGRAM FOR THE SERIAL MICROPROCESSOR INTERFACE 31 4.2 16-BIT SERIAL DATA INPUT DESCRIPTION 32 4.2.1 RIW (SCLK1). 32 4.2.2 A[5:0] (SCLK2 - SCLK7). 32 4.2.3 X (DUMMY BIT SCLK8). 32 4.2.4 D[7:0] (SCLK9 - SCLK7). 32 4.2.5 A.8-BIT SERIAL DATA OUTPUT DESCRIPTION 32 TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION. 32 TABLE 6: MICROPROCESSOR REGISTER OXOTH BIT DESCRIPTION. 35 TABLE 8: MICROPROCESSOR REGISTER DESCRIPTION. 36 TABLE 9: MICROPROCESSOR REGISTER BIT DESCRIPTION. 36 TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION. 36 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION. 37 TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION. 38 TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION. 39 ELECTRICAL CHARACTERISTICS. 41 TABLE 14: ABSOLUTE MAXIMUM RATINGS. 41 TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS. 41 TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS. 41 TABLE 11: RECEIVER ELECTRICAL CHARACTERISTICS. 41 TABLE 11: RECEIVER ELECTRICAL CHARACTERISTICS. 41 TABLE 11: RECEIVER ELECTRICAL CHARACTERISTICS. 42 TABLE 19: E1 TRANSMITTER ELECTRICAL CHARACTERISTICS. 43 ORDERING INFORMATION.                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |       |        |                                                      |    |

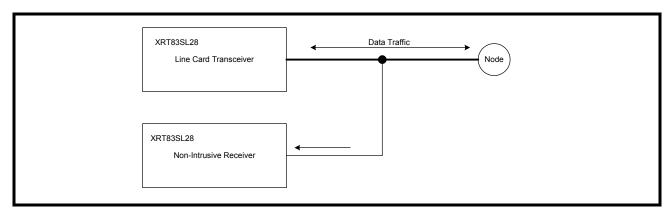

| 3.5 NON-INTRUSIVE MONITORING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |       |        |                                                      |    |

| FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |       |        |                                                      |    |

| 4.0 SERIAL MICROPROCESSOR INTERFACE BLOCK       31         Figure 26. Simplified BLOCK Diagram of the Serial Microprocessor Interface       31         4.1 SERIAL TIMING INFORMATION       31         Figure 27. Timing Diagram for the Serial Microprocessor Interface       31         4.2 16-BIT SERIAL DATA INPUT DESCRIPTION       32         4.2.1 RW (SCLK1)       32         4.2.2 A[5:0] (SCLK2 - SCLK7)       32         4.2.3 X (DUMMY BIT SCLK8)       32         4.2.4 D[7:0] (SCLK9 - SCLK16)       32         4.3 8-BIT SERIAL DATA OUTPUT DESCRIPTION       32         TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION       32         TABLE 8: MICROPROCESSOR REGISTER DESCRIPTION       35         TABLE 9: MICROPROCESSOR REGISTER OXO0H BIT DESCRIPTION       36         TABLE 9: MICROPROCESSOR REGISTER DIT DESCRIPTION       36         TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 14: ABSOLUTE MAXIMUM RATINGS.       41         TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |       |        |                                                      |    |

| FIGURE 26. SIMPLIFIED BLOCK DIAGRAM OF THE SERIAL MICROPROCESSOR INTERFACE   31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.0 |       |        |                                                      |    |

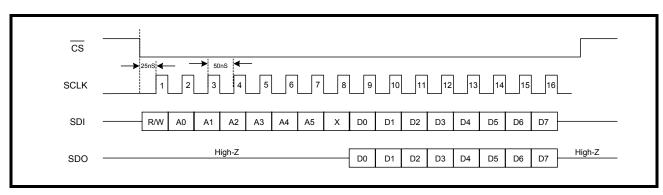

| 4.1 SERIAL TIMING INFORMATION       31         FIGURE 27. TIMING DIAGRAM FOR THE SERIAL MICROPROCESSOR INTERFACE       31         4.2 16-BIT SERIAL DATA INPUT DESCRIPTION       32         4.2.1 R/W (SCLK1)       32         4.2.2 A[5:0] (SCLK2 - SCLK7)       32         4.2.3 X (DUMMY BIT SCLK8)       32         4.2.4 D[7:0] (SCLK9 - SCLK16)       32         4.2.3 BIT SERIAL DATA OUTPUT DESCRIPTION       32         4.3 8-BIT SERIAL DATA OUTPUT DESCRIPTION       32         TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION       33         TABLE 7: MICROPROCESSOR REGISTER DESCRIPTION       35         TABLE 8: MICROPROCESSOR REGISTER OX00H BIT DESCRIPTION       36         TABLE 9: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 14: ABSOLUTE MAXIMUM RATINGS       41         TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS       41         TABLE 16: AC ELECTRICAL CHARACTERISTICS41         TABLE 17: POWER CONSUMPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.0 |       |        |                                                      |    |

| FIGURE 27. TIMING DIAGRAM FOR THE SERIAL MICROPROCESSOR INTERFACE   31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |       |        |                                                      |    |

| 4.2 16-BIT SERIAL DATA INPUT DESCRIPTION       32         4.2.1 RW (SCLK1)       32         4.2.2 A[5:0] (SCLK2 - SCLK7)       32         4.2.3 X (DUMMY BIT SCLK8)       32         4.2.4 D[7:0] (SCLK9 - SCLK16)       32         4.3 8-BIT SERIAL DATA OUTPUT DESCRIPTION       32         TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION       33         TABLE 7: MICROPROCESSOR REGISTER DESCRIPTION       35         TABLE 8: MICROPROCESSOR REGISTER 0X00H BIT DESCRIPTION       36         TABLE 9: MICROPROCESSOR REGISTER OX02H BIT DESCRIPTION       36         TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 14: ABSOLUTE MAXIMUM RATINGS.       41         TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS       41         TABLE 16: AC ELECTRICAL CHARACTERISTICS       41         TABLE 17: POWER CONSUMPTION       41         TABLE 18: RECEIVER ELECTRICAL CHARACTERISTICS       42         TABLE 19: E1 TRANSMITTER ELECTRICAL CHARACTERISTICS       42         TABLE 19: E1 TRANSMITT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |       |        |                                                      |    |

| 4.2.1 R/W (SCLK1)       32         4.2.2 A[5:0] (SCLK2 - SCLK7)       32         4.2.3 X (DUMMY BIT SCLK8)       32         4.2.4 D[7:0] (SCLK9 - SCLK16)       32         4.3 8-BIT SERIAL DATA OUTPUT DESCRIPTION       32         TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION       33         TABLE 7: MICROPROCESSOR REGISTER OX00H BIT DESCRIPTION       35         TABLE 8: MICROPROCESSOR REGISTER OX01H BIT DESCRIPTION       36         TABLE 9: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       39         ELECTRICAL CHARACTERISTICS       41         TABLE 14: ABSOLUTE MAXIMUM RATINGS       41         TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS       41         TABLE 16: AC ELECTRICAL CHARACTERISTICS       41         TABLE 17: POWER CONSUMPTION       41         TABLE 18: RECEIVER ELECTRICAL CHARACTERISTICS       42         TABLE 19: E1 TRANSMITTER ELECTRICA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |       |        |                                                      |    |

| 4.2.2 A[5:0] (SCLK2 - SCLK7)       32         4.2.3 X (DUMMY BIT SCLK8)       32         4.2.4 D[7:0] (SCLK9 - SCLK16)       32         4.3 8-BIT SERIAL DATA OUTPUT DESCRIPTION       32         TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION       33         TABLE 7: MICROPROCESSOR REGISTER 0X00H BIT DESCRIPTION       35         TABLE 8: MICROPROCESSOR REGISTER 0X01H BIT DESCRIPTION       36         TABLE 9: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       39         ELECTRICAL CHARACTERISTICS       41         TABLE 14: ABSOLUTE MAXIMUM RATINGS       41         TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS       41         TABLE 16: AC ELECTRICAL CHARACTERISTICS       41         TABLE 17: POWER CONSUMPTION       41         TABLE 18: RECEIVER ELECTRICAL CHARACTERISTICS       42         TABLE 19: E1 TRANSMITTER ELECTRICAL CHARACTERISTICS       43         ORDERING INFORMATION       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |       |        |                                                      |    |

| 4.2.3 X (DUMMY BIT SCLK8)       32         4.2.4 D[7:0] (SCLK9 - SCLK16)       32         4.3 8-BIT SERIAL DATA OUTPUT DESCRIPTION       32         TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION       33         TABLE 7: MICROPROCESSOR REGISTER 0x00H BIT DESCRIPTION       35         TABLE 8: MICROPROCESSOR REGISTER 0x01H BIT DESCRIPTION       36         TABLE 9: MICROPROCESSOR REGISTER 0x02H BIT DESCRIPTION       36         TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       39         ELECTRICAL CHARACTERISTICS       41         TABLE 14: ABSOLUTE MAXIMUM RATINGS       41         TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS       41         TABLE 16: AC ELECTRICAL CHARACTERISTICS       41         TABLE 17: POWER CONSUMPTION       41         TABLE 18: Receiver Electrical CHARACTERISTICS       42         TABLE 19: E1 TRANSMITTER ELECTRICAL CHARACTERISTICS       43         ORDERING INFORMATION       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |       | 4.2.1  | R/W (SCLKT)                                          | 32 |

| 4.2.4 D[7:0] (SCLK9 - SCLK16)       32         4.3 8-BIT SERIAL DATA OUTPUT DESCRIPTION       32         TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION       33         TABLE 7: MICROPROCESSOR REGISTER 0X00H BIT DESCRIPTION       35         TABLE 8: MICROPROCESSOR REGISTER 0X01H BIT DESCRIPTION       36         TABLE 9: MICROPROCESSOR REGISTER DIT DESCRIPTION       36         TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 14: MEROPROCESSOR REGISTER BIT DESCRIPTION       39         ELECTRICAL CHARACTERISTICS       41         TABLE 14: ABSOLUTE MAXIMUM RATINGS       41         TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS       41         TABLE 16: AC ELECTRICAL CHARACTERISTICS       41         TABLE 17: POWER CONSUMPTION       41         TABLE 18: RECEIVER ELECTRICAL CHARACTERISTICS       42         TABLE 19: E1 TRANSMITTER ELECTRICAL CHARACTERISTICS       43         ORDERING INFORMATION       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |       |        |                                                      |    |

| 4.3 8-BIT SERIAL DATA OUTPUT DESCRIPTION       32         TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION       33         TABLE 7: MICROPROCESSOR REGISTER 0x00H BIT DESCRIPTION       35         TABLE 8: MICROPROCESSOR REGISTER 0x01H BIT DESCRIPTION       36         TABLE 9: MICROPROCESSOR REGISTER DX02H BIT DESCRIPTION       36         TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       39         ELECTRICAL CHARACTERISTICS       41         TABLE 14: ABSOLUTE MAXIMUM RATINGS.       41         TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS       41         TABLE 16: AC ELECTRICAL CHARACTERISTICS       41         TABLE 17: POWER CONSUMPTION       41         TABLE 18: RECEIVER ELECTRICAL CHARACTERISTICS       42         TABLE 19: E1 TRANSMITTER ELECTRICAL CHARACTERISTICS       43         ORDERING INFORMATION       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |       |        |                                                      |    |

| TABLE 6: MICROPROCESSOR REGISTER DESCRIPTION       33         TABLE 7: MICROPROCESSOR REGISTER 0x00H BIT DESCRIPTION       35         TABLE 8: MICROPROCESSOR REGISTER 0x01H BIT DESCRIPTION       36         TABLE 9: MICROPROCESSOR REGISTER 0x02H BIT DESCRIPTION       36         TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       39         ELECTRICAL CHARACTERISTICS       41         TABLE 14: ABSOLUTE MAXIMUM RATINGS       41         TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS       41         TABLE 16: AC ELECTRICAL CHARACTERISTICS       41         TABLE 17: POWER CONSUMPTION       41         TABLE 18: RECEIVER ELECTRICAL CHARACTERISTICS       42         TABLE 19: E1 TRANSMITTER ELECTRICAL CHARACTERISTICS       43         ORDERING INFORMATION       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |       |        |                                                      |    |

| TABLE 7: MICROPROCESSOR REGISTER 0x00h Bit Description       35         TABLE 8: MICROPROCESSOR REGISTER 0x01h Bit Description       36         TABLE 9: MICROPROCESSOR REGISTER 0x02h Bit Description       36         TABLE 10: MICROPROCESSOR REGISTER Bit Description       36         TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       39         ELECTRICAL CHARACTERISTICS       41         TABLE 14: ABSOLUTE MAXIMUM RATINGS       41         TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS       41         TABLE 16: AC ELECTRICAL CHARACTERISTICS       41         TABLE 17: POWER CONSUMPTION       41         TABLE 18: RECEIVER ELECTRICAL CHARACTERISTICS       42         TABLE 19: E1 TRANSMITTER ELECTRICAL CHARACTERISTICS       43         ORDERING INFORMATION       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |       |        |                                                      |    |

| TABLE 8: MICROPROCESSOR REGISTER 0x01h Bit Description       36         TABLE 9: MICROPROCESSOR REGISTER 0x02h Bit Description       36         TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       39         ELECTRICAL CHARACTERISTICS       41         TABLE 14: ABSOLUTE MAXIMUM RATINGS       41         TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS       41         TABLE 16: AC ELECTRICAL CHARACTERISTICS       41         TABLE 17: POWER CONSUMPTION       41         TABLE 18: RECEIVER ELECTRICAL CHARACTERISTICS       42         TABLE 19: E1 TRANSMITTER ELECTRICAL CHARACTERISTICS       43         ORDERING INFORMATION       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |       |        |                                                      |    |

| TABLE 9: MICROPROCESSOR REGISTER 0x02h Bit Description       36         TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION       36         TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION       38         TABLE 13: MICROPROCESSOR REGISTER BIT DESCRIPTION       39         ELECTRICAL CHARACTERISTICS       41         TABLE 14: ABSOLUTE MAXIMUM RATINGS       41         TABLE 15: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS       41         TABLE 16: AC ELECTRICAL CHARACTERISTICS       41         TABLE 17: POWER CONSUMPTION       41         TABLE 18: RECEIVER ELECTRICAL CHARACTERISTICS       42         TABLE 19: E1 TRANSMITTER ELECTRICAL CHARACTERISTICS       43         ORDERING INFORMATION       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |       |        |                                                      |    |